# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-VDFN Exposed Pad                                                       |

| Supplier Device Package    | 8-DFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f629-e-md |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                                           | 7    |

|-------|-----------------------------------------------------------|------|

| 2.0   | Memory Organization                                       | 9    |

| 3.0   | GPIO Port                                                 | 21   |

| 4.0   | Timer0 Module                                             | . 29 |

| 5.0   | Timer1 Module with Gate Control                           | . 32 |

| 6.0   | Comparator Module                                         | . 37 |

| 7.0   | Analog-to-Digital Converter (A/D) Module (PIC12F675 only) | 43   |

| 8.0   | Data EEPROM Memory                                        | 49   |

| 9.0   | Special Features of the CPU                               |      |

| 10.0  | Instruction Set Summary                                   | 71   |

| 11.0  | Development Support                                       | 81   |

| 12.0  | Electrical Specifications                                 | 85   |

| 13.0  | DC and AC Characteristics Graphs and Tables               | 107  |

| 14.0  | Packaging Information                                     | 117  |

| Apper | ndix A: Data Sheet Revision History                       | 127  |

| Apper | ndix B: Device Differences                                | 127  |

| Apper | ndix C: Device Migrations                                 | 128  |

| Apper | ndix D: Migrating from other PIC <sup>®</sup> Devices     | 128  |

| Index |                                                           | 129  |

| On-Li | ne Support                                                | 133  |

| Syste | ns Information and Upgrade Hot Line                       | 133  |

| Reade | er Response                                               | 134  |

| Produ | ct Identification System                                  | 135  |

|       |                                                           |      |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# PIC12F629/675

NOTES:

#### 2.2.2.6 PCON Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Detect (BOD)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON Register bits are shown in Register 2-6.

#### REGISTER 2-6: PCON: POWER CONTROL REGISTER (ADDRESS: 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-x |

|-------|-----|-----|-----|-----|-----|-------|-------|

|       | —   | —   | —   | —   | _   | POR   | BOD   |

| bit 7 | •   |     |     |     |     |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-2 | Unimplemented: Read as '0'                                                                                                                              |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | POR: Power-on Reset Status bit                                                                                                                          |

|         | <ul> <li>1 = No Power-on Reset occurred</li> <li>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)</li> </ul>       |

| bit 0   | BOD: Brown-out Detect Status bit                                                                                                                        |

|         | <ul> <li>1 = No Brown-out Detect occurred</li> <li>0 = A Brown-out Detect occurred (must be set in software after a Brown-out Detect occurs)</li> </ul> |

#### 2.2.2.7 OSCCAL Register

The Oscillator Calibration register (OSCCAL) is used to calibrate the internal 4 MHz oscillator. It contains 6 bits to adjust the frequency up or down to achieve 4 MHz.

The OSCCAL register bits are shown in Register 2-7.

#### REGISTER 2-7: OSCCAL: OSCILLATOR CALIBRATION REGISTER (ADDRESS: 90h)

|                                                             |         |                  |       |                                    | •     | ,                  |       |  |  |

|-------------------------------------------------------------|---------|------------------|-------|------------------------------------|-------|--------------------|-------|--|--|

| R/W-1                                                       | R/W-0   | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | U-0                | U-0   |  |  |

| CAL5                                                        | CAL4    | CAL3             | CAL2  | CAL1                               | CAL0  | _                  | _     |  |  |

| bit 7                                                       |         | ·                |       |                                    |       | ·                  | bit 0 |  |  |

|                                                             |         |                  |       |                                    |       |                    |       |  |  |

| Legend:                                                     |         |                  |       |                                    |       |                    |       |  |  |

| R = Readab                                                  | ole bit | W = Writable     | bit   | U = Unimplemented bit, read as '0' |       |                    |       |  |  |

| -n = Value a                                                | it POR  | '1' = Bit is set |       | '0' = Bit is cle                   | ared  | x = Bit is unknown |       |  |  |

|                                                             |         |                  |       |                                    |       |                    |       |  |  |

| bit 7-2 CAL5:CAL0: 6-bit Signed Oscillator Calibration bits |         |                  |       |                                    |       |                    |       |  |  |

|                                                             |         | aximum frequer   |       |                                    |       |                    |       |  |  |

| 100000 = | Center | frequency |  |

|----------|--------|-----------|--|

|          |        |           |  |

000000 = Minimum frequency

# bit 1-0 Unimplemented: Read as '0'

# PIC12F629/675

| U-0                                               | U-0                                                                                                                   | R/W-1                                                                                                 | R/W-1                               | R-1                                | R/W-1            | R/W-1              | R/W-1   |  |  |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------|------------------|--------------------|---------|--|--|

| _                                                 |                                                                                                                       | TRISI05                                                                                               | TRISIO4                             | TRISIO3                            | TRISIO2          | TRISIO1            | TRISI00 |  |  |

| bit 7                                             | ·                                                                                                                     |                                                                                                       |                                     |                                    |                  |                    | bit     |  |  |

| Legend:                                           |                                                                                                                       |                                                                                                       |                                     |                                    |                  |                    |         |  |  |

| R = Readable                                      | e bit                                                                                                                 | W = Writable                                                                                          | bit                                 | U = Unimplen                       | nented bit, read | d as '0'           |         |  |  |

| -n = Value at                                     | POR                                                                                                                   | '1' = Bit is set                                                                                      |                                     | '0' = Bit is clea                  | ared             | x = Bit is unkr    | iown    |  |  |

| LH 7 0                                            |                                                                                                                       | ta di Danadara (i                                                                                     | .,                                  |                                    |                  |                    |         |  |  |

| bit 7-6                                           | -                                                                                                                     | ted: Read as '                                                                                        |                                     | ata Cantral hit                    |                  |                    |         |  |  |

| bit 5-0                                           |                                                                                                                       | : General Purp<br>configured as                                                                       |                                     |                                    |                  |                    |         |  |  |

|                                                   |                                                                                                                       | configured as                                                                                         |                                     | aleu)                              |                  |                    |         |  |  |

| Note: TR                                          | RISIO<3> always                                                                                                       | •                                                                                                     | anouput                             |                                    |                  |                    |         |  |  |

|                                                   |                                                                                                                       |                                                                                                       |                                     |                                    |                  |                    |         |  |  |

| REGISTER                                          | 3-3: WPU:                                                                                                             | WEAK PULL                                                                                             | -UP REGIS                           | FER (ADDRE                         | SS: 95h)         |                    |         |  |  |

| U-0                                               | U-0                                                                                                                   | R/W-1                                                                                                 | R/W-1                               | U-0                                | R/W-1            | R/W-1              | R/W-1   |  |  |

|                                                   |                                                                                                                       | WPU5                                                                                                  | WPU4                                |                                    | WPU2             | WPU1               | WPU0    |  |  |

| bit 7                                             |                                                                                                                       |                                                                                                       |                                     |                                    |                  |                    | bit     |  |  |

|                                                   |                                                                                                                       |                                                                                                       |                                     |                                    |                  |                    |         |  |  |

| Legend:                                           |                                                                                                                       |                                                                                                       |                                     |                                    |                  |                    |         |  |  |

| R = Readable                                      | e bit                                                                                                                 | W = Writable                                                                                          | bit                                 | U = Unimplemented bit, read as '0' |                  |                    |         |  |  |

| -n = Value at                                     | POR                                                                                                                   | '1' = Bit is set                                                                                      |                                     | '0' = Bit is cleared               |                  | x = Bit is unknown |         |  |  |

|                                                   |                                                                                                                       |                                                                                                       |                                     |                                    |                  |                    |         |  |  |

|                                                   | -                                                                                                                     | ted: Read as '                                                                                        |                                     |                                    |                  |                    |         |  |  |

| bit 7-6                                           | bit 5-4 WPU<5:4>: Weak Pull-up Register bit                                                                           |                                                                                                       |                                     |                                    |                  |                    |         |  |  |

|                                                   |                                                                                                                       | •                                                                                                     | cylater bit                         |                                    |                  |                    |         |  |  |

| bit 7-6<br>bit 5-4                                | 1 = Pull-up er                                                                                                        | nabled                                                                                                |                                     |                                    |                  |                    |         |  |  |

| bit 5-4                                           | 1 = Pull-up er<br>0 = Pull-up di                                                                                      | nabled<br>sabled                                                                                      | -                                   |                                    |                  |                    |         |  |  |

| bit 5-4<br>bit 3                                  | 1 = Pull-up er<br>0 = Pull-up di<br><b>Unimplemen</b>                                                                 | nabled<br>sabled<br>I <b>ted:</b> Read as 'i                                                          | ס'                                  |                                    |                  |                    |         |  |  |

| bit 5-4<br>bit 3                                  | 1 = Pull-up er<br>0 = Pull-up di<br>Unimplemen<br>WPU<2:0>: V                                                         | nabled<br>sabled<br>i <b>ted:</b> Read as 'i<br>Neak Pull-up R                                        | ס'                                  |                                    |                  |                    |         |  |  |

| bit 5-4<br>bit 3                                  | 1 = Pull-up er<br>0 = Pull-up di<br>Unimplemen<br>WPU<2:0>: V<br>1 = Pull-up er                                       | nabled<br>sabled<br>I <b>ted:</b> Read as 'i<br>Neak Pull-up R<br>nabled                              | ס'                                  |                                    |                  |                    |         |  |  |

| bit 5-4<br>bit 3<br>bit 2-0                       | 1 = Pull-up er<br>0 = Pull-up di<br><b>Unimplemen</b><br><b>WPU&lt;2:0&gt;:</b> V<br>1 = Pull-up er<br>0 = Pull-up di | nabled<br>sabled<br>I <b>ted:</b> Read as f<br>Weak Pull-up R<br>nabled<br>sabled                     | ⊃'<br>egister bit                   |                                    |                  |                    |         |  |  |

| bit 5-4<br>bit 3<br>bit 2-0<br><b>Note 1:</b> Glo | 1 = Pull-up er<br>0 = Pull-up di<br>Unimplemen<br>WPU<2:0>: V<br>1 = Pull-up er                                       | nabled<br>sabled<br>I <b>ted:</b> Read as f<br>Weak Pull-up R<br>nabled<br>sabled<br>it be enabled fo | י<br>egister bit<br>r individual pu | •                                  |                  |                    |         |  |  |

# REGISTER 3-2: TRISIO: GPIO TRI-STATE REGISTER (ADDRESS: 85h)

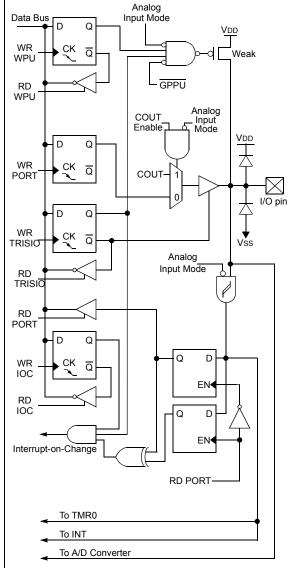

#### 3.3.3 GP2/AN2/T0CKI/INT/COUT

Figure 3-2 shows the diagram for this pin. The GP2 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the A/D (PIC12F675 only)

- the clock input for TMR0

- an external edge triggered interrupt

- · a digital output from the comparator

# FIGURE 3-2: BLOCK DIAGRAM OF GP2

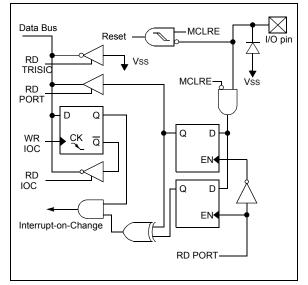

# 3.3.4 GP3/MCLR/VPP

Figure 3-3 shows the diagram for this pin. The GP3 pin is configurable to function as one of the following:

- a general purpose input

- as Master Clear Reset

#### FIGURE 3-3: BLOCK DIAGRAM OF GP3

### 5.1 Timer1 Modes of Operation

Timer1 can operate in one of three modes:

- 16-bit timer with prescaler

- 16-bit synchronous counter

- · 16-bit asynchronous counter

FIGURE 5-2:

In Timer mode, Timer1 is incremented on every instruction cycle. In Counter mode, Timer1 is incremented on the rising edge of the external clock input T1CKI. In addition, the Counter mode clock can be synchronized to the microcontroller system clock or run asynchronously.

In counter and timer modules, the counter/timer clock can be gated by the  $\overline{\text{T1G}}$  input.

If an external clock oscillator is needed (and the microcontroller is using the INTOSC w/o CLKOUT), Timer1 can use the LP oscillator as a clock source.

| Note: | In Counter mode, a falling edge must be      |

|-------|----------------------------------------------|

|       | registered by the counter prior to the first |

|       | incrementing rising edge.                    |

TIMER1 INCREMENTING EDGE

### 5.2 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit (PIR1<0>) is set. To enable the interrupt on rollover, you must set these bits:

- Timer1 interrupt Enable bit (PIE1<0>)

- PEIE bit (INTCON<6>)

- GIE bit (INTCON<7>).

The interrupt is cleared by clearing the TMR1IF in the Interrupt Service Routine.

Note: The TMR1H:TTMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

### 5.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4, or 8 divisions of the clock input. The T1CKPS bits (T1CON<5:4>) control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# T1CKI = 1 when TMR1 Enabled T1CKI = 0 when TMR1 Enabled Note 1: Arrows indicate counter increments. 2: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge of the clock.

### 5.4 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 5.4.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

Note: The ANSEL (9Fh) and CMCON (19h) registers must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'. The ANSEL register is defined for the PIC12F675.

# 5.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L, while the timer is running from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

# 5.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins OSC1 (input) and OSC2 (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator rated up to 37 kHz. It will continue to run during Sleep. It is primarily intended for a 32 kHz crystal. Table 9-2 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is shared with the system LP oscillator. Thus, Timer1 can use this mode only when the system clock is derived from the internal oscillator. As with the system LP oscillator, the user must provide a software time delay to ensure proper oscillator start-up.

While enabled, TRISIO4 and TRISIO5 are set. GP4 and GP5 read '0' and TRISIO4 and TRISIO5 are read '1'.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to enabling Timer1.

# 5.6 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To setup the timer to wake the device:

- Timer1 must be on (T1CON<0>)

- TMR1IE bit (PIE1<0>) must be set

- PEIE bit (INTCON<6>) must be set

The device will wake-up on an overflow. If the GIE bit (INTCON<7>) is set, the device will wake-up and jump to the Interrupt Service Routine on an overflow.

| TABLE 5-1. REGISTERS ASSOCIATED WITH HIMLERTAS A HIMLERCOUNTER |        |         |                                                                                                |         |         |         |        |        |        |               |      |      |                       |

|----------------------------------------------------------------|--------|---------|------------------------------------------------------------------------------------------------|---------|---------|---------|--------|--------|--------|---------------|------|------|-----------------------|

| Address                                                        | Name   | Bit 7   | Bit 6                                                                                          | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value<br>POR, |      | allo | e on<br>other<br>sets |

| 0Bh/8Bh                                                        | INTCON | GIE     | PEIE                                                                                           | T0IE    | INTE    | GPIE    | T0IF   | INTF   | GPIF   | 0000          | 0000 | 0000 | 000u                  |

| 0Ch                                                            | PIR1   | EEIF    | ADIF                                                                                           | _       | —       | CMIF    | —      | _      | TMR1IF | 00            | 00   | 00   | 00                    |

| 0Eh                                                            | TMR1L  | Holding | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register                    |         |         |         |        |        |        |               |      | uuuu | uuuu                  |

| 0Fh                                                            | TMR1H  | Holding | lolding Register for the Most Significant Byte of the 16-bit TMR1 Register xxxx xxxx uuuu uuuu |         |         |         |        |        |        |               |      |      |                       |

| 10h                                                            | T1CON  | _       | TMR1GE                                                                                         | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | -000          | 0000 | -uuu | uuuu                  |

| 8Ch                                                            | PIE1   | EEIE    | ADIE                                                                                           | _       | _       | CMIE    | _      | _      | TMR1IE | 00            | 00   | 00   | 00                    |

TABLE 5-1: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

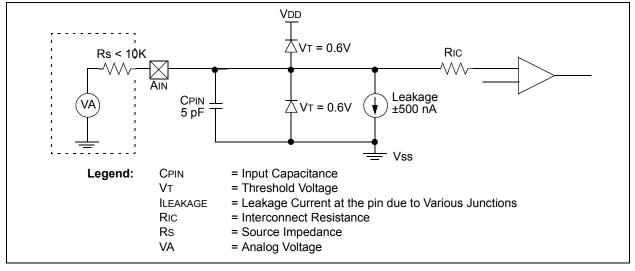

#### 6.3 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 6-3. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this

range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

#### FIGURE 6-3: ANALOG INPUT MODE

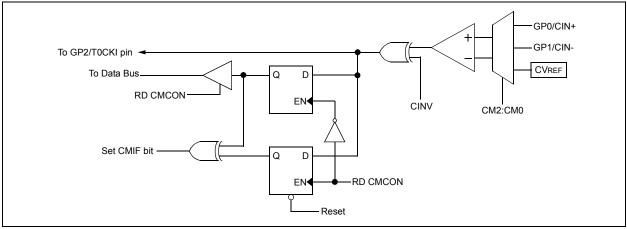

#### 6.4 Comparator Output

The comparator output, COUT, is read through the CMCON register. This bit is read-only. The comparator output may also be directly output to the GP2 pin in three of the eight possible modes, as shown in Figure 6-2. When in one of these modes, the output on GP2 is asynchronous to the internal clock. Figure 6-4 shows the comparator output block diagram.

The TRISIO<2> bit functions as an output enable/ disable for the GP2 pin while the comparator is in an Output mode.

- Note 1: When reading the GPIO register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the TTL input specification.

- 2: Analog levels on any pin that is defined as a digital input, may cause the input buffer to consume more current than is specified.

#### FIGURE 6-4: MODIFIED COMPARATOR OUTPUT BLOCK DIAGRAM

#### 6.5 Comparator Reference

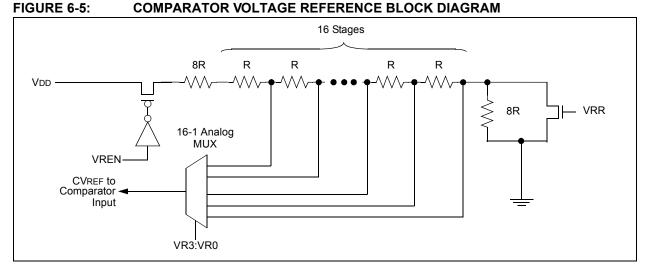

The comparator module also allows the selection of an internally generated voltage reference for one of the comparator inputs. The internal reference signal is used for four of the eight Comparator modes. The VRCON register, Register 6-2, controls the voltage reference module shown in Figure 6-5.

# 6.5.1 CONFIGURING THE VOLTAGE REFERENCE

The voltage reference can output 32 distinct voltage levels, 16 in a high range and 16 in a low range.

The following equations determine the output voltages:

VRR = 1 (low range): CVREF = (VR3:VR0 / 24) x VDD VRR = 0 (high range): CVREF = (VDD / 4) + (VR3:VR0 x VDD / 32)

#### 6.5.2 VOLTAGE REFERENCE ACCURACY/ERROR

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 6-5) keep CVREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the Comparator Voltage Reference can be found in **Section 12.0 "Electrical Specifications"**.

#### 6.6 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output is ensured to have a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (Table 12-7).

# 6.7 Operation During Sleep

Both the comparator and voltage reference, if enabled before entering Sleep mode, remain active during Sleep. This results in higher Sleep currents than shown in the power-down specifications. The additional current consumed by the comparator and the voltage reference is shown separately in the specifications. To minimize power consumption while in Sleep mode, turn off the comparator, CM2:CM0 = 111, and voltage refeence, VRCON<7> = 0. While the comparator is enabled during Sleep, an interrupt will wake-up the device. If the device wakes up from Sleep, the contents of the CMCON and VRCON registers are not affected.

# 6.8 Effects of a Reset

A device Reset forces the CMCON and VRCON registers to their Reset states. This forces the comparator module to be in the Comparator Reset mode, CM2:CM0 = 000 and the voltage reference to its off state. Thus, all potential inputs are analog inputs with the comparator and voltage reference disabled to consume the smallest current possible.

#### 9.4 Interrupts

The PIC12F629/675 has 7 sources of interrupt:

- External Interrupt GP2/INT

- TMR0 Overflow Interrupt

- · GPIO Change Interrupts

- Comparator Interrupt

- A/D Interrupt (PIC12F675 only)

- TMR1 Overflow Interrupt

- EEPROM Data Write Interrupt

The Interrupt Control register (INTCON) and Peripheral Interrupt register (PIR) record individual interrupt requests in flag bits. The INTCON register also has individual and Global Interrupt Enable (GIE) bits.

A Global Interrupt Enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register and PIE register. GIE is cleared on Reset.

The return from interrupt instruction, RETFIE, exits interrupt routine, as well as sets the GIE bit, which re-enables unmasked interrupts.

The following interrupt flags are contained in the INTCON register:

- INT pin interrupt

- · GP port change interrupt

- TMR0 overflow interrupt

The peripheral interrupt flags are contained in the special register PIR1. The corresponding interrupt enable bit is contained in special register PIE1.

The following interrupt flags are contained in the PIR register:

- EEPROM data write interrupt

- A/D interrupt

- · Comparator interrupt

- Timer1 overflow interrupt

- When an interrupt is serviced:

- The GIE is cleared to disable any further interrupt

- The return address is pushed onto the stack

- The PC is loaded with 0004h

Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid GP2/ INT recursive interrupts.

For external interrupt events, such as the INT pin, or GP port change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends upon when the interrupt event occurs (see Figure 9-11). The latency is the same for one or twocycle instructions. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

**Note 1:** Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

© 2010 Microchip Technology Inc.

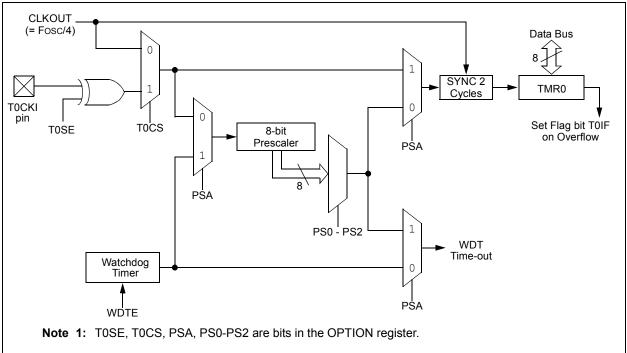

#### TABLE 9-9: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOD | Value on all<br>other<br>Resets |

|---------|--------------|-------|--------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| 81h     | OPTION_REG   | GPPU  | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111            | 1111 1111                       |

| 2007h   | Config. bits | CP    | BODEN  | MCLRE | PWRTE | WDTE  | F0SC2 | F0SC1 | F0SC0 | uuuu uuuu            | uuuu uuuu                       |

**Legend:** u = Unchanged, shaded cells are not used by the Watchdog Timer.

# **10.2** Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |  |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |  |  |  |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |  |  |  |  |  |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BCF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ADDWF            | Add W and f                                                                                                                                                        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                              |

| Status Affected: | C, DC, Z                                                                                                                                                           |

| Description:     | Add the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND Literal with W                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                             |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                         |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>2TCY instruction. |

| ANDWF            | AND W with f                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                   |

| Status Affected: | Z                                                                                                                                                           |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |

# 11.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

### 11.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

# 11.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

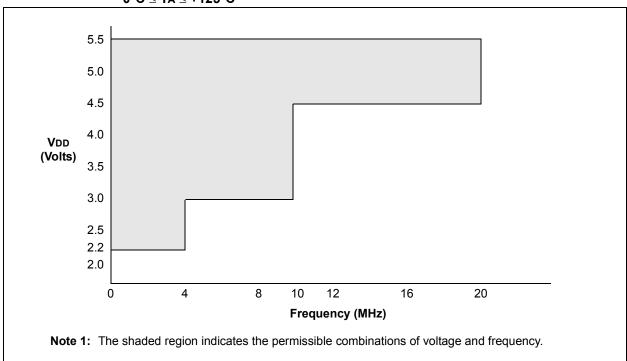

FIGURE 12-3: PIC12F675 WITH A/D ENABLED VOLTAGE-FREQUENCY GRAPH, 0°C  $\leq$  Ta  $\leq$  +125°C

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                              |     |      |      |       |            |                    |

|------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----|------|------|-------|------------|--------------------|

| Param                                                                                                                              | Param Device Characteristics |     | Typ† | Max  | Units | Conditions |                    |

| No.                                                                                                                                | Device Characteristics       | Min | iypi | WIAN | Units | VDD        | Note               |

| D010                                                                                                                               | Supply Current (IDD)         | _   | 9    | 16   | μA    | 2.0        | Fosc = 32 kHz      |

|                                                                                                                                    |                              | —   | 18   | 28   | μA    | 3.0        | LP Oscillator Mode |

|                                                                                                                                    |                              | —   | 35   | 54   | μA    | 5.0        |                    |

| D011                                                                                                                               |                              | —   | 110  | 150  | μA    | 2.0        | Fosc = 1 MHz       |

|                                                                                                                                    |                              | _   | 190  | 280  | μA    | 3.0        | XT Oscillator Mode |

|                                                                                                                                    |                              | _   | 330  | 450  | μA    | 5.0        |                    |

| D012                                                                                                                               |                              | —   | 220  | 280  | μA    | 2.0        | Fosc = 4 MHz       |

|                                                                                                                                    |                              | —   | 370  | 650  | μA    | 3.0        | XT Oscillator Mode |

|                                                                                                                                    |                              | —   | 0.6  | 1.4  | mA    | 5.0        |                    |

| D013                                                                                                                               |                              | —   | 70   | 110  | μA    | 2.0        | Fosc = 1 MHz       |

|                                                                                                                                    |                              | _   | 140  | 250  | μA    | 3.0        | EC Oscillator Mode |

|                                                                                                                                    |                              | _   | 260  | 390  | μA    | 5.0        |                    |

| D014                                                                                                                               |                              | —   | 180  | 250  | μA    | 2.0        | Fosc = 4 MHz       |

|                                                                                                                                    |                              | —   | 320  | 470  | μA    | 3.0        | EC Oscillator Mode |

|                                                                                                                                    |                              | _   | 580  | 850  | μA    | 5.0        |                    |

| D015                                                                                                                               |                              | _   | 340  | 450  | μA    | 2.0        | Fosc = 4 MHz       |

|                                                                                                                                    |                              | _   | 500  | 700  | μA    | 3.0        | INTOSC Mode        |

|                                                                                                                                    |                              | _   | 0.8  | 1.1  | mA    | 5.0        |                    |

| D016                                                                                                                               |                              | _   | 180  | 250  | μA    | 2.0        | Fosc = 4 MHz       |

|                                                                                                                                    |                              |     | 320  | 450  | μA    | 3.0        | EXTRC Mode         |

|                                                                                                                                    |                              | _   | 580  | 800  | μA    | 5.0        |                    |

| D017                                                                                                                               |                              | _   | 2.1  | 2.95 | mA    | 4.5        | Fosc = 20 MHz      |

|                                                                                                                                    |                              | _   | 2.4  | 3.0  | mA    | 5.0        | HS Oscillator Mode |

# 12.2 DC Characteristics: PIC12F629/675-I (Industrial)

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in Active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

# 12.9 AC CHARACTERISTICS: PIC12F629/675 (INDUSTRIAL, EXTENDED)

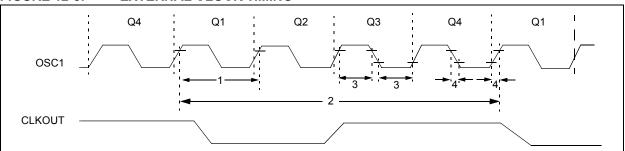

### FIGURE 12-5: EXTERNAL CLOCK TIMING

#### TABLE 12-1: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                          | Min   | Typ† | Max      | Units | Conditions                         |

|--------------|-------|-----------------------------------------|-------|------|----------|-------|------------------------------------|

|              | Fosc  | External CLKIN Frequency <sup>(1)</sup> | DC    | _    | 37       | kHz   | LP Osc mode                        |

|              |       |                                         | DC    | _    | 4        | MHz   | XT mode                            |

|              |       |                                         | DC    | _    | 20       | MHz   | HS mode                            |

|              |       |                                         | DC    | _    | 20       | MHz   | EC mode                            |

|              |       | Oscillator Frequency <sup>(1)</sup>     | 5     | _    | 37       | kHz   | LP Osc mode                        |

|              |       |                                         | —     | 4    | —        | MHz   | INTOSC mode                        |

|              |       |                                         | DC    | —    | 4        | MHz   | RC Osc mode                        |

|              |       |                                         | 0.1   | —    | 4        | MHz   | XT Osc mode                        |

|              |       |                                         | 1     | _    | 20       | MHz   | HS Osc mode                        |

| 1            | Tosc  | External CLKIN Period <sup>(1)</sup>    | 27    | _    | ×        | μS    | LP Osc mode                        |

|              |       |                                         | 50    | —    | $\infty$ | ns    | HS Osc mode                        |

|              |       |                                         | 50    | —    | $\infty$ | ns    | EC Osc mode                        |

|              |       |                                         | 250   | —    | $\infty$ | ns    | XT Osc mode                        |

|              |       | Oscillator Period <sup>(1)</sup>        | 27    |      | 200      | μS    | LP Osc mode                        |

|              |       |                                         | —     | 250  | —        | ns    | INTOSC mode                        |

|              |       |                                         | 250   | —    | —        | ns    | RC Osc mode                        |

|              |       |                                         | 250   | —    | 10,000   | ns    | XT Osc mode                        |

|              |       |                                         | 50    | —    | 1,000    | ns    | HS Osc mode                        |

| 2            | Тсү   | Instruction Cycle Time <sup>(1)</sup>   | 200   | TCY  | DC       | ns    | Tcy = 4/Fosc                       |

| 3            | TosL, | External CLKIN (OSC1) High              | 2*    | _    | —        | μS    | LP oscillator, Tosc L/H duty cycle |

|              | TosH  | External CLKIN Low                      | 20*   | —    | —        | ns    | HS oscillator, Tosc L/H duty       |

|              |       |                                         |       |      |          |       | cycle                              |

|              |       |                                         | 100 * | —    | —        | ns    | XT oscillator, Tosc L/H duty cycle |

| 4            | TosR, | External CLKIN Rise                     | —     | —    | 50*      | ns    | LP oscillator                      |

|              | TosF  | External CLKIN Fall                     | —     | —    | 25*      | ns    | XT oscillator                      |

|              |       |                                         | —     | —    | 15*      | ns    | HS oscillator                      |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the 'max' cycle time limit is "DC" (no clock) for all devices.

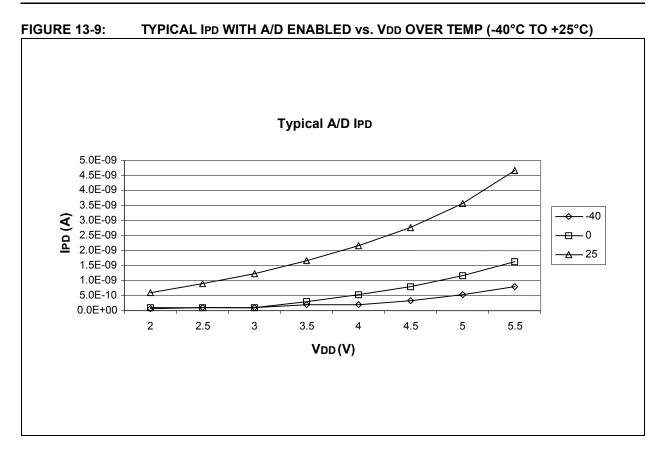

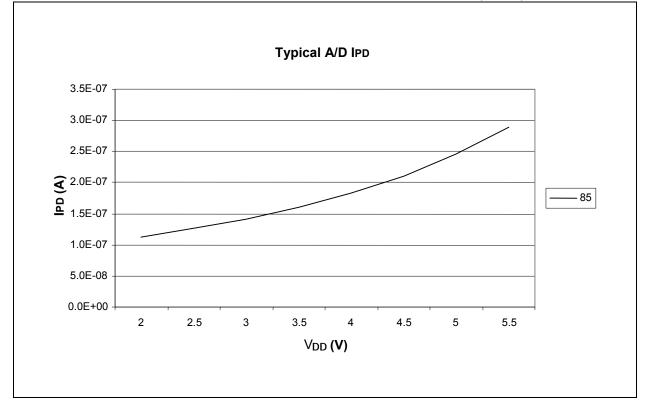

FIGURE 13-10: TYPICAL IPD WITH A/D ENABLED vs. VDD OVER TEMP (+85°C)

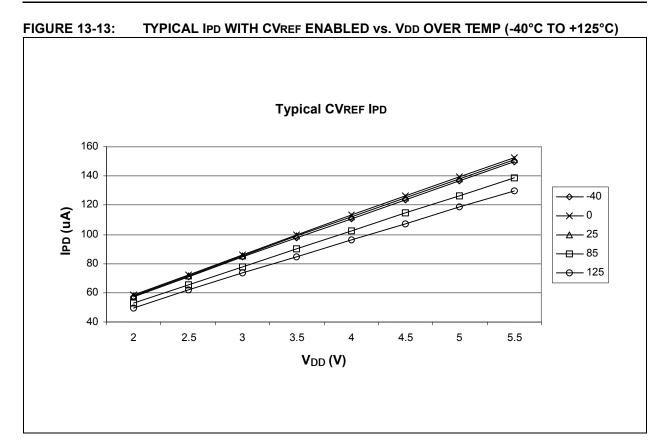

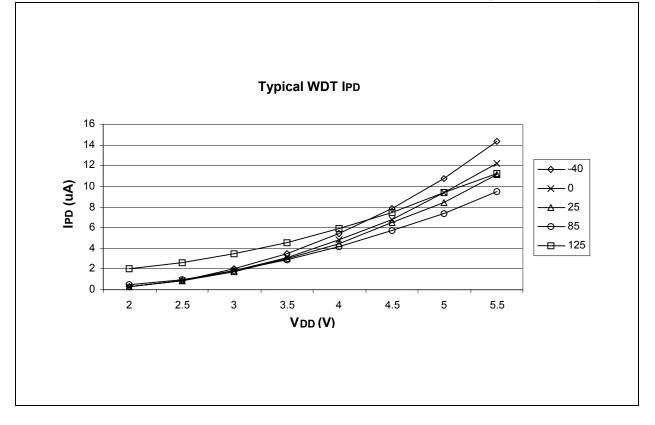

FIGURE 13-14: TYPICAL IPD WITH WDT ENABLED vs. VDD OVER TEMP (-40°C TO +125°C)

# APPENDIX C: DEVICE MIGRATIONS

This section is intended to describe the functional and electrical specification differences when migrating between functionally similar devices (such as from a PIC16C74A to a PIC16C74B).

#### Not Applicable

# APPENDIX D: MIGRATING FROM OTHER PIC<sup>®</sup> DEVICES

This discusses some of the issues in migrating from other PIC devices to the PIC12F6XX family of devices.

#### D.1 PIC12C67X to PIC12F6XX

| Feature             | PIC12C67X  | PIC12F6XX     |

|---------------------|------------|---------------|

| Max Operating Speed | 10 MHz     | 20 MHz        |

| Max Program Memory  | 2048 bytes | 1024 bytes    |

| A/D Resolution      | 8-bit      | 10-bit        |

| Data EEPROM         | 16 bytes   | 64 bytes      |

| Oscillator Modes    | 5          | 8             |

| Brown-out Detect    | N          | Y             |

| Internal Pull-ups   | GP0/1/3    | GP0/1/2/4/5   |

| Interrupt-on-change | GP0/1/3    | GP0/1/2/3/4/5 |

| Comparator          | Ν          | Y             |

| TABLE 1: | FEATURE COMPARISO | Ν |

|----------|-------------------|---|

|----------|-------------------|---|

| Note: | This device has been designed to perform<br>to the parameters of its data sheet. It has<br>been tested to an electrical specification<br>designed to determine its conformance<br>with these parameters. Due to process<br>differences in the manufacture of this<br>device, this device may have different<br>performance characteristics than its earlier<br>version. These differences may cause this<br>device to perform differently in your<br>application than the earlier version of this<br>device. |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Note: The user should verify that the device oscillator starts and performs as expected. Adjusting the loading capacitor values and/ or the oscillator mode may be required.

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com