# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorPICCore Size8-BitSpeed20MHzConnectivity-PeripheralsPOR, WDTNumber of I/O5Program Memory Size1.75KB (1K x 14)Program Memory TypeFLASHEPROM Size128 x 8Nutser of V/C2V ~ 5.5VData Converters-Ogerating Temperature4.0°C ~ 125°C (TA)Mounting TypeSurface MountProkage / Case8.0FDN Exposed PadSurface Mount5.0FDN Exposed PadProkage / Case8.0FDN Exposed PadSurface Race8.0FDN Exposed Pad< |                            |                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------|

| Core Size8-BitSpeed20MHzConnectivity-PeripheralsPOR, WDTNumber of I/O5Program Memory Size1.75KB (1K x 14)Program Memory TypeFLASHEEPROM Size128 x 8RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Product Status             | Active                                                                   |

| Speed20MHzConnectivity-PeripheralsPOR, WDTNumber of I/O5Program Memory Size1.75KB (1K x 14)Program Memory TypeFLASHEEPROM Size128 x 8RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case8-VDFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Core Processor             | PIC                                                                      |

| Connectivity-PeripheralsPOR, WDTNumber of I/O5Program Memory Size1.75KB (1K x 14)Program Memory TypeFLASHEEPROM Size128 x 8RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case8-VDFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Core Size                  | 8-Bit                                                                    |

| PeripheralsPOR, WDTNumber of I/O5Program Memory Size1.75KB (1K x 14)Program Memory TypeFLASHEEPROM Size128 x 8RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Speed                      | 20MHz                                                                    |

| Number of I/O5Program Memory Size1.75KB (1K × 14)Program Memory TypeFLASHEEPROM Size128 × 8RAM Size64 × 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case8-VDFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Connectivity               | ·                                                                        |

| Program Memory Size1.75KB (1K x 14)Program Memory TypeFLASHEEPROM Size128 x 8RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Peripherals                | POR, WDT                                                                 |

| Program Memory TypeFLASHEEPROM Size128 x 8RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case8-VDFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Number of I/O              | 5                                                                        |

| EEPROM Size128 x 8RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case8-VDFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Program Memory Size        | 1.75KB (1K x 14)                                                         |

| RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case8-VDFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Program Memory Type        | FLASH                                                                    |

| Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case8-VDFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EEPROM Size                | 128 x 8                                                                  |

| Data Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case8-VDFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RAM Size                   | 64 x 8                                                                   |

| Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case8-VDFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Operating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case8-VDFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Data Converters            | -                                                                        |

| Mounting Type     Surface Mount       Package / Case     8-VDFN Exposed Pad       Supplier Device Package     8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Oscillator Type            | Internal                                                                 |

| Package / Case     8-VDFN Exposed Pad       Supplier Device Package     8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Supplier Device Package 8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Mounting Type              | Surface Mount                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Package / Case             | 8-VDFN Exposed Pad                                                       |

| Purchase URL https://www.e-xfl.com/product-detail/microchip-technology/pic12f629-e-mf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Supplier Device Package    | 8-DFN-S (6x5)                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f629-e-mf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

#### ISBN: 978-1-60932-160-4

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# 8-Pin Flash-Based 8-Bit CMOS Microcontroller

### High-Performance RISC CPU:

- · Only 35 Instructions to Learn

- All single-cycle instructions except branches

- · Operating Speed:

- DC 20 MHz oscillator/clock input

- DC 200 ns instruction cycle

- Interrupt Capability

- 8-Level Deep Hardware Stack

- · Direct, Indirect, and Relative Addressing modes

### **Special Microcontroller Features:**

- Internal and External Oscillator Options

- Precision Internal 4 MHz oscillator factory calibrated to ±1%

- External Oscillator support for crystals and resonators

- 5 µs wake-up from Sleep, 3.0V, typical

- Power-Saving Sleep mode

- Wide Operating Voltage Range 2.0V to 5.5V

- Industrial and Extended Temperature Range

- Low-Power Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

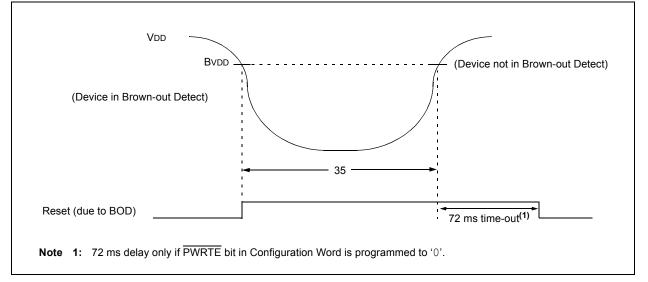

- · Brown-out Detect (BOD)

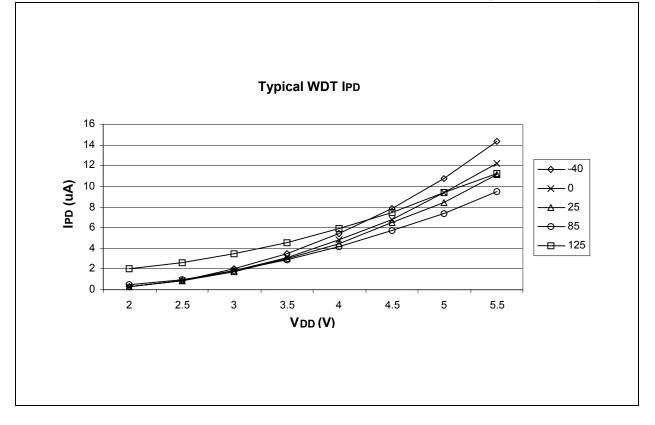

- Watchdog Timer (WDT) with Independent Oscillator for Reliable Operation

- Multiplexed MCLR/Input Pin

- Interrupt-on-Pin Change

- Individual Programmable Weak Pull-ups

- Programmable Code Protection

- High Endurance Flash/EEPROM Cell

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- Flash/Data EEPROM Retention: > 40 years

### Low-Power Features:

- Standby Current:

- 1 nA @ 2.0V, typical

- Operating Current:

- 8.5 μA @ 32 kHz, 2.0V, typical

- 100 μA @ 1 MHz, 2.0V, typical

- Watchdog Timer Current

300 nA @ 2.0V, typical

- 300 TA @ 2.00, typical

- Timer1 Oscillator Current:

- 4 μA @ 32 kHz, 2.0V, typical

### **Peripheral Features:**

- · 6 I/O Pins with Individual Direction Control

- High Current Sink/Source for Direct LED Drive

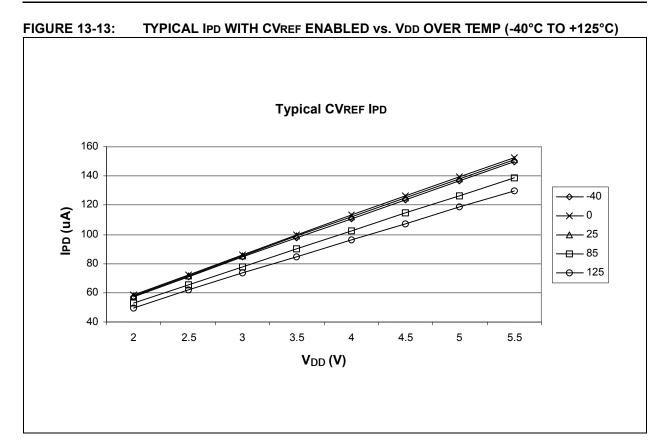

- Analog Comparator module with:

- One analog comparator

- Programmable on-chip comparator voltage reference (CVREF) module

- Programmable input multiplexing from device inputs

- Comparator output is externally accessible

- Analog-to-Digital Converter module (PIC12F675):

- 10-bit resolution

- Programmable 4-channel input

- Voltage reference input

- Timer0: 8-Bit Timer/Counter with 8-Bit Programmable Prescaler

- Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Gate Input mode

- Option to use OSC1 and OSC2 in LP mode as Timer1 oscillator, if INTOSC mode selected

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via two pins

| Device    | Program<br>Memory | Data Memory     |                   | I/O | 10-bit A/D | Comparators | Timers   |  |

|-----------|-------------------|-----------------|-------------------|-----|------------|-------------|----------|--|

| Device    | Flash<br>(words)  | SRAM<br>(bytes) | EEPROM<br>(bytes) | 1/0 | (ch)       | Comparators | 8/16-bit |  |

| PIC12F629 | 1024              | 64              | 128               | 6   | -          | 1           | 1/1      |  |

| PIC12F675 | 1024              | 64              | 128               | 6   | 4          | 1           | 1/1      |  |

\* 8-bit, 8-pin devices protected by Microchip's Low Pin Count Patent: U.S. Patent No. 5,847,450. Additional U.S. and foreign patents and applications may be issued or pending.

### **Table of Contents**

| 1.0   | Device Overview                                           | 7    |

|-------|-----------------------------------------------------------|------|

| 2.0   | Memory Organization                                       | 9    |

| 3.0   | GPIO Port                                                 | 21   |

| 4.0   | Timer0 Module                                             | . 29 |

| 5.0   | Timer1 Module with Gate Control                           | . 32 |

| 6.0   | Comparator Module                                         | . 37 |

| 7.0   | Analog-to-Digital Converter (A/D) Module (PIC12F675 only) | 43   |

| 8.0   | Data EEPROM Memory                                        | 49   |

| 9.0   | Special Features of the CPU                               |      |

| 10.0  | Instruction Set Summary                                   | 71   |

| 11.0  | Development Support                                       | 81   |

| 12.0  | Electrical Specifications                                 | 85   |

| 13.0  | DC and AC Characteristics Graphs and Tables               | 107  |

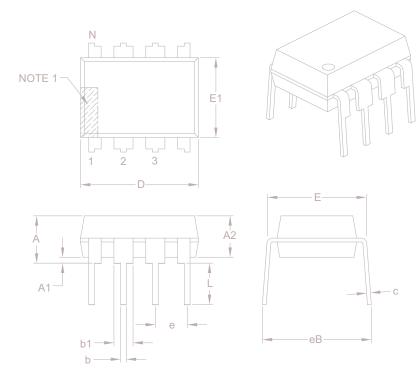

| 14.0  | Packaging Information                                     | 117  |

| Apper | ndix A: Data Sheet Revision History                       | 127  |

| Apper | ndix B: Device Differences                                | 127  |

| Apper | ndix C: Device Migrations                                 | 128  |

| Apper | ndix D: Migrating from other PIC <sup>®</sup> Devices     | 128  |

| Index |                                                           | 129  |

| On-Li | ne Support                                                | 133  |

| Syste | ns Information and Upgrade Hot Line                       | 133  |

| Reade | er Response                                               | 134  |

| Produ | ct Identification System                                  | 135  |

|       |                                                           |      |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (see Table 2-1). These registers are static RAM.

The special registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the "core" are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

### FIGURE 2-2: DATA MEMORY MAP OF THE PIC12F629/675

|                                                                                                                                        | THE F           | PIC12F629/675                 |                |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------|----------------|--|--|--|--|

| ,                                                                                                                                      | File<br>Address | A                             | File<br>ddress |  |  |  |  |

| Indirect addr. <sup>(1)</sup>                                                                                                          | 00h             | Indirect addr. <sup>(1)</sup> | 80h            |  |  |  |  |

| TMR0                                                                                                                                   | 01h             | OPTION_REG                    | 81h            |  |  |  |  |

| PCL                                                                                                                                    | 02h             | PCL                           | 82h            |  |  |  |  |

| STATUS                                                                                                                                 | 03h             | STATUS                        | 83h            |  |  |  |  |

| FSR                                                                                                                                    | 04h             | FSR                           | 84h            |  |  |  |  |

| GPIO                                                                                                                                   | 05h             | TRISIO                        | 85h            |  |  |  |  |

|                                                                                                                                        | 06h             |                               | 86h            |  |  |  |  |

|                                                                                                                                        | 07h             |                               | 87h            |  |  |  |  |

|                                                                                                                                        | 08h             |                               | 88h            |  |  |  |  |

|                                                                                                                                        | 09h             |                               | 89h            |  |  |  |  |

| PCLATH                                                                                                                                 | 0Ah             | PCLATH                        | 8Ah            |  |  |  |  |

| INTCON                                                                                                                                 | 0Bh             | INTCON                        | 8Bh            |  |  |  |  |

| PIR1                                                                                                                                   | 0Ch             | PIE1                          | 8Ch            |  |  |  |  |

|                                                                                                                                        | 0Dh             |                               | 8Dh            |  |  |  |  |

| TMR1L                                                                                                                                  | 0Eh             | PCON                          | 8Eh            |  |  |  |  |

| TMR1H                                                                                                                                  | 0Fh             |                               | 8Fh            |  |  |  |  |

| T1CON                                                                                                                                  | 10h             | OSCCAL                        | 90h            |  |  |  |  |

|                                                                                                                                        | 11h             |                               | 91h            |  |  |  |  |

|                                                                                                                                        | 12h             |                               | 92h            |  |  |  |  |

|                                                                                                                                        | 13h             |                               | 93h            |  |  |  |  |

|                                                                                                                                        | 14h             |                               | 94h            |  |  |  |  |

|                                                                                                                                        | 15h             | WPU                           | 95h            |  |  |  |  |

|                                                                                                                                        | 16h             | IOC                           | 96h            |  |  |  |  |

|                                                                                                                                        | 17h             |                               | 97h            |  |  |  |  |

|                                                                                                                                        | 18h             |                               | 98h            |  |  |  |  |

| CMCON                                                                                                                                  | 19h             | VRCON                         | 99h            |  |  |  |  |

|                                                                                                                                        | 1Ah             | EEDATA                        | 9Ah            |  |  |  |  |

|                                                                                                                                        | 1Bh             | EEADR                         | 9Bh            |  |  |  |  |

|                                                                                                                                        | 1Ch             | EECON1                        | 9Ch            |  |  |  |  |

|                                                                                                                                        | 1Dh             | EECON2 <sup>(1)</sup>         | 9Dh            |  |  |  |  |

| ADRESH <sup>(2)</sup>                                                                                                                  | 1Eh             | ADRESL <sup>(2)</sup>         | 9Eh            |  |  |  |  |

| ADCON0 <sup>(2)</sup>                                                                                                                  | 1Fh             | ANSEL <sup>(2)</sup>          | 9Fh            |  |  |  |  |

|                                                                                                                                        | 20h             |                               | A0h            |  |  |  |  |

| General<br>Purpose<br>Registers<br>64 Bytes                                                                                            |                 | accesses<br>20h-5Fh           |                |  |  |  |  |

|                                                                                                                                        | 5Fh             |                               | DFh            |  |  |  |  |

|                                                                                                                                        | 60h             |                               | E0h            |  |  |  |  |

|                                                                                                                                        |                 |                               |                |  |  |  |  |

|                                                                                                                                        |                 |                               |                |  |  |  |  |

|                                                                                                                                        | 754             |                               | FFL            |  |  |  |  |

| Bank 0                                                                                                                                 | 7Fh             | Bank 1                        | FFh            |  |  |  |  |

| Danko                                                                                                                                  |                 | Bank i                        |                |  |  |  |  |

| <ul> <li>Unimplemented data memory locations, read as '0'.</li> <li>1: Not a physical register.</li> <li>2: PIC12F675 only.</li> </ul> |                 |                               |                |  |  |  |  |

|                                                                                                                                        |                 |                               |                |  |  |  |  |

### 2.2.2.6 PCON Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Detect (BOD)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON Register bits are shown in Register 2-6.

### REGISTER 2-6: PCON: POWER CONTROL REGISTER (ADDRESS: 8Eh)

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-x |

|-------------|-----|-----|-----|-----|-----|-------|-------|

|             | —   | —   | —   | _   | —   | POR   | BOD   |

| bit 7 bit C |     |     |     |     |     |       |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-2 | Unimplemented: Read as '0'                                                                                                                              |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | POR: Power-on Reset Status bit                                                                                                                          |

|         | <ul> <li>1 = No Power-on Reset occurred</li> <li>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)</li> </ul>       |

| bit 0   | BOD: Brown-out Detect Status bit                                                                                                                        |

|         | <ul> <li>1 = No Brown-out Detect occurred</li> <li>0 = A Brown-out Detect occurred (must be set in software after a Brown-out Detect occurs)</li> </ul> |

### 2.2.2.7 OSCCAL Register

The Oscillator Calibration register (OSCCAL) is used to calibrate the internal 4 MHz oscillator. It contains 6 bits to adjust the frequency up or down to achieve 4 MHz.

The OSCCAL register bits are shown in Register 2-7.

### REGISTER 2-7: OSCCAL: OSCILLATOR CALIBRATION REGISTER (ADDRESS: 90h)

|                                               |         |                  |       |                                         | •     | ,   |       |  |  |

|-----------------------------------------------|---------|------------------|-------|-----------------------------------------|-------|-----|-------|--|--|

| R/W-1                                         | R/W-0   | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | U-0 | U-0   |  |  |

| CAL5                                          | CAL4    | CAL3             | CAL2  | CAL1                                    | CAL0  | _   | _     |  |  |

| bit 7                                         |         | ·                |       |                                         |       | ·   | bit 0 |  |  |

|                                               |         |                  |       |                                         |       |     |       |  |  |

| Legend:                                       |         |                  |       |                                         |       |     |       |  |  |

| R = Readab                                    | ole bit | W = Writable     | bit   | U = Unimplemented bit, read as '0'      |       |     |       |  |  |

| -n = Value a                                  | it POR  | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |     |       |  |  |

|                                               |         |                  |       |                                         |       |     |       |  |  |

| bit 7-2 CAL5:CAL0: 6-bit Signed Oscillator Ca |         |                  |       | oration bits                            |       |     |       |  |  |

|                                               |         | aximum frequer   |       |                                         |       |     |       |  |  |

| 100000 = | Center | frequency |  |

|----------|--------|-----------|--|

|          |        |           |  |

000000 = Minimum frequency

### bit 1-0 Unimplemented: Read as '0'

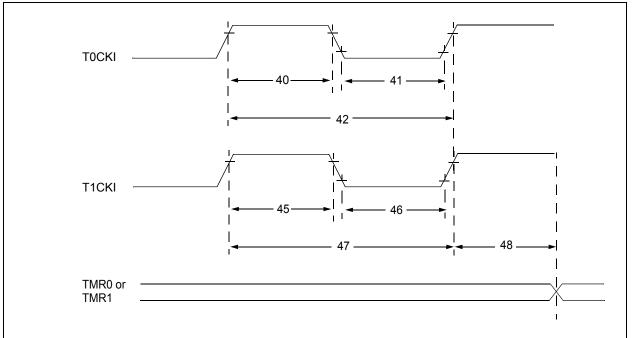

### 5.1 Timer1 Modes of Operation

Timer1 can operate in one of three modes:

- 16-bit timer with prescaler

- 16-bit synchronous counter

- · 16-bit asynchronous counter

FIGURE 5-2:

In Timer mode, Timer1 is incremented on every instruction cycle. In Counter mode, Timer1 is incremented on the rising edge of the external clock input T1CKI. In addition, the Counter mode clock can be synchronized to the microcontroller system clock or run asynchronously.

In counter and timer modules, the counter/timer clock can be gated by the  $\overline{\text{T1G}}$  input.

If an external clock oscillator is needed (and the microcontroller is using the INTOSC w/o CLKOUT), Timer1 can use the LP oscillator as a clock source.

| Note: | In Counter mode, a falling edge must be      |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|

|       | registered by the counter prior to the first |  |  |  |  |  |

|       | incrementing rising edge.                    |  |  |  |  |  |

TIMER1 INCREMENTING EDGE

### 5.2 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit (PIR1<0>) is set. To enable the interrupt on rollover, you must set these bits:

- Timer1 interrupt Enable bit (PIE1<0>)

- PEIE bit (INTCON<6>)

- GIE bit (INTCON<7>).

The interrupt is cleared by clearing the TMR1IF in the Interrupt Service Routine.

Note: The TMR1H:TTMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

### 5.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4, or 8 divisions of the clock input. The T1CKPS bits (T1CON<5:4>) control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# T1CKI = 1 when TMR1 Enabled T1CKI = 0 when TMR1 Enabled Note 1: Arrows indicate counter increments. 2: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge of the clock.

### 5.4 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 5.4.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

Note: The ANSEL (9Fh) and CMCON (19h) registers must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'. The ANSEL register is defined for the PIC12F675.

# 5.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L, while the timer is running from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

### 5.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins OSC1 (input) and OSC2 (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator rated up to 37 kHz. It will continue to run during Sleep. It is primarily intended for a 32 kHz crystal. Table 9-2 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is shared with the system LP oscillator. Thus, Timer1 can use this mode only when the system clock is derived from the internal oscillator. As with the system LP oscillator, the user must provide a software time delay to ensure proper oscillator start-up.

While enabled, TRISIO4 and TRISIO5 are set. GP4 and GP5 read '0' and TRISIO4 and TRISIO5 are read '1'.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to enabling Timer1.

### 5.6 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To setup the timer to wake the device:

- Timer1 must be on (T1CON<0>)

- TMR1IE bit (PIE1<0>) must be set

- PEIE bit (INTCON<6>) must be set

The device will wake-up on an overflow. If the GIE bit (INTCON<7>) is set, the device will wake-up and jump to the Interrupt Service Routine on an overflow.

| IADEL (                                                                              | ABLE 5-1. REGISTERS ASSOCIATED WITH HIMLERTAS A HIMLERCOUNTER |         |              |              |               |             |           |            |        |               |      |      |                       |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------|---------|--------------|--------------|---------------|-------------|-----------|------------|--------|---------------|------|------|-----------------------|

| Address                                                                              | Name                                                          | Bit 7   | Bit 6        | Bit 5        | Bit 4         | Bit 3       | Bit 2     | Bit 1      | Bit 0  | Value<br>POR, |      | allo | e on<br>other<br>sets |

| 0Bh/8Bh                                                                              | INTCON                                                        | GIE     | PEIE         | T0IE         | INTE          | GPIE        | T0IF      | INTF       | GPIF   | 0000          | 0000 | 0000 | 000u                  |

| 0Ch                                                                                  | PIR1                                                          | EEIF    | ADIF         | _            | —             | CMIF        | —         | _          | TMR1IF | 00            | 00   | 00   | 00                    |

| 0Eh                                                                                  | TMR1L                                                         | Holding | g Register f | or the Least | t Significant | Byte of the | 16-bit TM | R1 Registe | r      | XXXX          | XXXX | uuuu | uuuu                  |

| 0Fh TMR1H Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |                                                               |         |              |              |               |             |           | XXXX       | XXXX   | uuuu          | uuuu |      |                       |

| 10h                                                                                  | T1CON                                                         | _       | TMR1GE       | T1CKPS1      | T1CKPS0       | T1OSCEN     | T1SYNC    | TMR1CS     | TMR10N | -000          | 0000 | -uuu | uuuu                  |

| 8Ch                                                                                  | PIE1                                                          | EEIE    | ADIE         | _            | _             | CMIE        | _         | _          | TMR1IE | 00            | 00   | 00   | 00                    |

TABLE 5-1: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

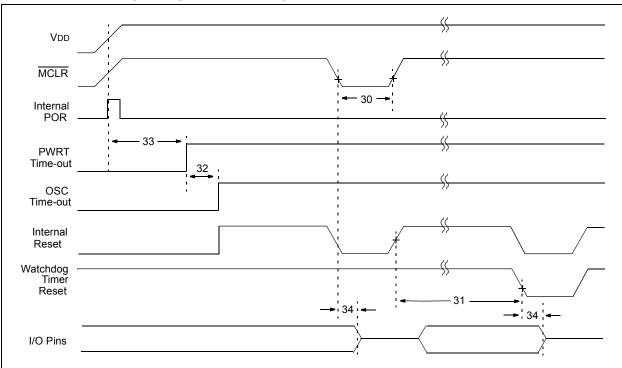

| TABLE 9-7: INITIALIZATION CONDITION FOR REGISTERS |         |                   |                                                                                                                                                        |                                                                                                                   |  |  |

|---------------------------------------------------|---------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|

| Register                                          | Address | Power-on<br>Reset | <ul> <li>MCLR Reset during<br/>normal operation</li> <li>MCLR Reset during Sleep</li> <li>WDT Reset</li> <li>Brown-out Detect<sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from Sleep<br/>through interrupt</li> <li>Wake-up from Sleep<br/>through WDT Time-out</li> </ul> |  |  |

| W                                                 |         | XXXX XXXX         | นนนน นนนน                                                                                                                                              | սսսս սսսս                                                                                                         |  |  |

| INDF                                              | 00h/80h | —                 | —                                                                                                                                                      | —                                                                                                                 |  |  |

| TMR0                                              | 01h     | XXXX XXXX         | นนนน นนนน                                                                                                                                              | นนนน นนนน                                                                                                         |  |  |

| PCL                                               | 02h/82h | 0000 0000         | 0000 0000                                                                                                                                              | PC + 1 <sup>(3)</sup>                                                                                             |  |  |

| STATUS                                            | 03h/83h | 0001 1xxx         | 000q quuu <sup>(4)</sup>                                                                                                                               | uuuq quuu <sup>(4)</sup>                                                                                          |  |  |

| FSR                                               | 04h/84h | XXXX XXXX         | սսսս սսսս                                                                                                                                              | սսսս սսսս                                                                                                         |  |  |

| GPIO                                              | 05h     | xx xxxx           | uu uuuu                                                                                                                                                | uu uuuu                                                                                                           |  |  |

| PCLATH                                            | 0Ah/8Ah | 0 0000            | 0 0000                                                                                                                                                 | u uuuu                                                                                                            |  |  |

| INTCON                                            | 0Bh/8Bh | 0000 0000         | 0000 000u                                                                                                                                              | uuuu uuqq <sup>(2)</sup>                                                                                          |  |  |

| PIR1                                              | 0Ch     | 00 00             | 00 00                                                                                                                                                  | qq qq <sup>(2,5)</sup>                                                                                            |  |  |

| T1CON                                             | 10h     | -000 0000         | -uuu uuuu                                                                                                                                              | -uuu uuuu                                                                                                         |  |  |

| CMCON                                             | 19h     | -0-0 0000         | -0-0 0000                                                                                                                                              | -u-u uuuu                                                                                                         |  |  |

| ADRESH                                            | 1Eh     | XXXX XXXX         | นนนน นนนน                                                                                                                                              | นนนน นนนน                                                                                                         |  |  |

| ADCON0                                            | 1Fh     | 00 0000           | 00 0000                                                                                                                                                | uu uuuu                                                                                                           |  |  |

| OPTION_REG                                        | 81h     | 1111 1111         | 1111 1111                                                                                                                                              | นนนน นนนน                                                                                                         |  |  |

| TRISIO                                            | 85h     | 11 1111           | 11 1111                                                                                                                                                | uu uuuu                                                                                                           |  |  |

| PIE1                                              | 8Ch     | 00 00             | 00 00                                                                                                                                                  | uu uu                                                                                                             |  |  |

| PCON                                              | 8Eh     | 0x                | (1,6)                                                                                                                                                  | uu                                                                                                                |  |  |

| OSCCAL                                            | 90h     | 1000 00           | 1000 00                                                                                                                                                | uuuu uu                                                                                                           |  |  |

| WPU                                               | 95h     | 11 -111           | 11 -111                                                                                                                                                | นนนน นนนน                                                                                                         |  |  |

| IOC                                               | 96h     | 00 0000           | 00 0000                                                                                                                                                | uu uuuu                                                                                                           |  |  |

| VRCON                                             | 99h     | 0-0- 0000         | 0-0- 0000                                                                                                                                              | u-u- uuuu                                                                                                         |  |  |

| EEDATA                                            | 9Ah     | 0000 0000         | 0000 0000                                                                                                                                              | սսսս սսսս                                                                                                         |  |  |

| EEADR                                             | 9Bh     | -000 0000         | -000 0000                                                                                                                                              | -uuu uuuu                                                                                                         |  |  |

| EECON1                                            | 9Ch     | x000              | q000                                                                                                                                                   | uuuu                                                                                                              |  |  |

| EECON2                                            | 9Dh     |                   |                                                                                                                                                        |                                                                                                                   |  |  |

| ADRESL                                            | 9Eh     | XXXX XXXX         | นนนน นนนน                                                                                                                                              | นนนน นนนน                                                                                                         |  |  |

| ANSEL                                             | 9Fh     | -000 1111         | -000 1111                                                                                                                                              | -uuu uuuu                                                                                                         |  |  |

TABLE 9-7: INITIALIZATION CONDITION FOR REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

**3:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 9-6 for Reset value for specific condition.

5: If wake-up was due to data EEPROM write completing, Bit 7 = 1; A/D conversion completing, Bit 6 = 1; Comparator input changing, bit 3 = 1; or Timer1 rolling over, bit 0 = 1. All other interrupts generating a wake-up will cause these bits to = u.

**6:** If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

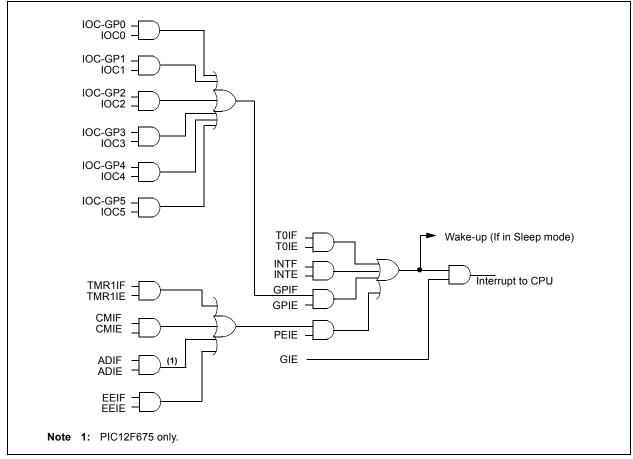

### FIGURE 9-10: INTERRUPT LOGIC

### 9.8 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

**Note:** The entire data EEPROM and Flash program memory will be erased when the code protection is turned off. The INTOSC calibration data is also erased. See PIC12F629/675 Programming Specification for more information.

### 9.9 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable during Program/Verify. Only the Least Significant 7 bits of the ID locations are used.

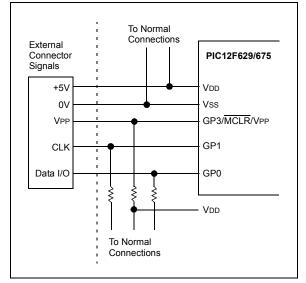

### 9.10 In-Circuit Serial Programming

The PIC12F629/675 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for:

- power

- ground

- programming voltage

This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the GP0 and GP1 pins low, while raising the  $\overline{\text{MCLR}}$  (VPP) pin from VIL to VIHH (see Programming Specification). GP0 becomes the programming data and GP1 becomes the programming clock. Both GP0 and GP1 are Schmitt Trigger inputs in this mode.

After Reset, to place the device into Programming/ Verify mode, the PC is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending on whether the command was a load or a read. For complete details of serial programming, please refer to the Programming Specifications.

A typical In-Circuit Serial Programming connection is shown in Figure 9-14.

### FIGURE 9-14:

### TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

### 9.11 In-Circuit Debugger

Since in-circuit debugging requires the loss of clock, data and MCLR pins, MPLAB<sup>®</sup> ICD 2 development with an 8-pin device is not practical. A special 14-pin PIC12F675-ICD device is used with MPLAB ICD 2 to provide separate clock, data and MCLR pins and frees all normally available pins to the user.

This special ICD device is mounted on the top of the header and its signals are routed to the MPLAB ICD 2 connector. On the bottom of the header is an 8-pin socket that plugs into the user's target via the 8-pin stand-off connector.

When the ICD pin on the PIC12F675-ICD device is held low, the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB ICD 2. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 9-10 shows which features are consumed by the background debugger:

### TABLE 9-10: DEBUGGER RESOURCES

| I/O pins       | ICDCLK, ICDDATA                     |  |  |  |  |

|----------------|-------------------------------------|--|--|--|--|

| Stack          | 1 level                             |  |  |  |  |

| Program Memory | Address 0h must be NOP<br>300h-3FEh |  |  |  |  |

For more information, see 8-Pin MPLAB ICD 2 Header Information Sheet (DS51292) available on Microchip's web site (www.microchip.com).

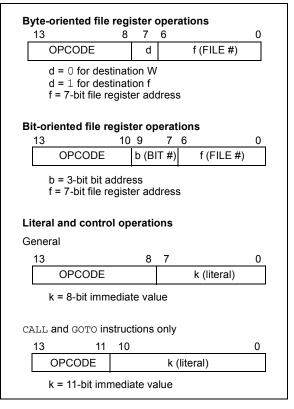

## 10.0 INSTRUCTION SET SUMMARY

The PIC12F629/675 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- · Literal and control operations

Each PIC12F629/675 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type, and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 10-1, while the various opcode fields are summarized in Table 10-1.

Table 10-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler. A complete description of each instruction is also available in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8bit or 11-bit constant, or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

| Note: | To maintain upward compatibility with  |  |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|--|

|       | future products, do not use the OPTION |  |  |  |  |  |  |

|       | and TRISIO instructions.               |  |  |  |  |  |  |

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

### 10.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register. For example, a CLRF GPIO instruction will read GPIO, clear all the data bits, then write the result back to GPIO. This example would have the unintended result that the condition that sets the GPIF flag would be cleared.

# TABLE 10-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |  |  |  |  |  |

| W     | Working register (accumulator)                                                                                                                                                    |  |  |  |  |  |

| b     | Bit address within an 8-bit file register                                                                                                                                         |  |  |  |  |  |

| k     | Literal field, constant data or label                                                                                                                                             |  |  |  |  |  |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |  |  |  |  |  |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                     |  |  |  |  |  |