# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                            |

| Supplier Device Package    | 8-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f629-e-sn |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

#### ISBN: 978-1-60932-160-4

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### 8-Pin Flash-Based 8-Bit CMOS Microcontroller

#### High-Performance RISC CPU:

- Only 35 Instructions to Learn

- All single-cycle instructions except branches

- · Operating Speed:

- DC 20 MHz oscillator/clock input

- DC 200 ns instruction cycle

- Interrupt Capability

- 8-Level Deep Hardware Stack

- · Direct, Indirect, and Relative Addressing modes

#### **Special Microcontroller Features:**

- Internal and External Oscillator Options

- Precision Internal 4 MHz oscillator factory calibrated to ±1%

- External Oscillator support for crystals and resonators

- 5 µs wake-up from Sleep, 3.0V, typical

- Power-Saving Sleep mode

- Wide Operating Voltage Range 2.0V to 5.5V

- Industrial and Extended Temperature Range

- Low-Power Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- · Brown-out Detect (BOD)

- Watchdog Timer (WDT) with Independent Oscillator for Reliable Operation

- Multiplexed MCLR/Input Pin

- Interrupt-on-Pin Change

- Individual Programmable Weak Pull-ups

- Programmable Code Protection

- High Endurance Flash/EEPROM Cell

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- Flash/Data EEPROM Retention: > 40 years

#### Low-Power Features:

- Standby Current:

- 1 nA @ 2.0V, typical

- Operating Current:

- 8.5 μA @ 32 kHz, 2.0V, typical

- 100 μA @ 1 MHz, 2.0V, typical

- Watchdog Timer Current

300 nA @ 2.0V, typical

- 300 TA @ 2.00, typical

- Timer1 Oscillator Current:

- 4 μA @ 32 kHz, 2.0V, typical

#### **Peripheral Features:**

- · 6 I/O Pins with Individual Direction Control

- High Current Sink/Source for Direct LED Drive

- Analog Comparator module with:

- One analog comparator

- Programmable on-chip comparator voltage reference (CVREF) module

- Programmable input multiplexing from device inputs

- Comparator output is externally accessible

- Analog-to-Digital Converter module (PIC12F675):

- 10-bit resolution

- Programmable 4-channel input

- Voltage reference input

- Timer0: 8-Bit Timer/Counter with 8-Bit Programmable Prescaler

- Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Gate Input mode

- Option to use OSC1 and OSC2 in LP mode as Timer1 oscillator, if INTOSC mode selected

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via two pins

| Device    | Program<br>Memory | Data N          | lemory            | I/O | 10-bit A/D | Comparators | Timers   |  |

|-----------|-------------------|-----------------|-------------------|-----|------------|-------------|----------|--|

| Device    | Flash<br>(words)  | SRAM<br>(bytes) | EEPROM<br>(bytes) | 1/0 | (ch)       | Comparators | 8/16-bit |  |

| PIC12F629 | 1024              | 64              | 128               | 6   | -          | 1           | 1/1      |  |

| PIC12F675 | 1024              | 64              | 128               | 6   | 4          | 1           | 1/1      |  |

\* 8-bit, 8-pin devices protected by Microchip's Low Pin Count Patent: U.S. Patent No. 5,847,450. Additional U.S. and foreign patents and applications may be issued or pending.

NOTES:

#### 4.4 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer. For simplicity, this counter will be referred to as "prescaler" throughout this Data Sheet. The prescaler assignment is controlled in software by the control bit PSA (OPTION\_REG<3>). Clearing the PSA bit will assign the prescaler to Timer0. Prescale values are selectable via the PS2:PS0 bits (OPTION\_REG<2:0>).

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x...etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer.

#### 4.4.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device Reset, the following instruction sequence (Example 4-1) must be executed when changing the prescaler assignment from Timer0 to WDT.

#### EXAMPLE 4-1: CHANGING PRESCALER (TIMER0→WDT)

| BCF<br>CLRWDT | STATUS, RPO        | ;Bank 0<br>;Clear WDT |

|---------------|--------------------|-----------------------|

|               | <b>T</b> N (T) (1) | ,                     |

| CLRF          | TMR0               | ;Clear TMR0 and       |

|               |                    | ; prescaler           |

| BSF           | STATUS, RPO        | ;Bank 1               |

|               |                    |                       |

| MOVLW         | b'00101111'        | ;Required if desired  |

| MOVWF         | OPTION REG         | ; PS2:PS0 is          |

| CLRWDT        | _                  | ; 000 or 001          |

|               |                    | ;                     |

| MOVLW         | b'00101xxx'        | ;Set postscaler to    |

| MOVWF         | OPTION REG         | ; desired WDT rate    |

| BCF           | STATUS, RPO        | ;Bank 0               |

|               |                    |                       |

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 4-2. This precaution must be taken even if the WDT is disabled.

#### EXAMPLE 4-2: CHANGING PRESCALER (WDT→TIMER0)

| CLRWDT       |                          | ;Clear WDT and                                     |

|--------------|--------------------------|----------------------------------------------------|

| BSF          | STATUS, RPO              | ; postscaler<br>;Bank 1                            |

| MOVLW        | b'xxxx0xxx'              | ;Select TMR0,<br>; prescale, and<br>; clock source |

| MOVWF<br>BCF | OPTION_REG<br>STATUS,RPO | ;<br>;Bank O                                       |

#### TABLE 4-1:REGISTERS ASSOCIATED WITH TIMER0

| Address | Name                        | Bit 7 | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1     | Bit 0     | Value on<br>POR, BOD | Value on<br>all other<br>Resets |

|---------|-----------------------------|-------|--------|---------|---------|---------|---------|-----------|-----------|----------------------|---------------------------------|

| 01h     | TMR0 Timer0 Module Register |       |        |         |         |         |         | XXXX XXXX | uuuu uuuu |                      |                                 |

| 0Bh/8Bh | INTCON                      | GIE   | PEIE   | TOIE    | INTE    | GPIE    | T0IF    | INTF      | GPIF      | 0000 0000            | 0000 000u                       |

| 81h     | OPTION_REG                  | GPPU  | INTEDG | TOCS    | T0SE    | PSA     | PS2     | PS1       | PS0       | 1111 1111            | 1111 1111                       |

| 85h     | TRISIO                      | —     | —      | TRISIO5 | TRISIO4 | TRISIO3 | TRISIO2 | TRISIO1   | TRISIO0   | 11 1111              | 11 1111                         |

**Legend:** — = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Timer0 module.

NOTES:

#### 6.0 COMPARATOR MODULE

The PIC12F629/675 devices have one analog comparator. The inputs to the comparator are multiplexed with the GP0 and GP1 pins. There is an on-chip Comparator Voltage Reference that can also be applied to an input of the comparator. In addition, GP2 can be configured as the comparator output.

The Comparator Control Register (CMCON), shown in Register 6-1, contains the bits to control the comparator.

#### **REGISTER 6-1:** CMCON: COMPARATOR CONTROL REGISTER (ADDRESS: 19h)

| U-0   | R-0  | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|------|-----|-------|-------|-------|-------|-------|

| —     | COUT | —   | CINV  | CIS   | CM2   | CM1   | CM0   |

| bit 7 |      |     |       |       |       |       | bit 0 |

|       |      |     |       |       |       |       |       |

|       |      |     |       |       |       |       |       |

| Legena:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                                     |

|---------|----------------------------------------------------------------|

| bit 6   | COUT: Comparator Output bit                                    |

|         | When CINV = 0:                                                 |

|         | 1 = VIN+ > VIN-                                                |

|         | 0 = VIN+ < VIN-                                                |

|         | When CINV = 1:                                                 |

|         | 1 = VIN+ < VIN-                                                |

|         | 0 = VIN + > VIN-                                               |

| bit 5   | Unimplemented: Read as '0'                                     |

| bit 4   | CINV: Comparator Output Inversion bit                          |

|         | 1 = Output inverted                                            |

|         | 0 = Output not inverted                                        |

| bit 3   | CIS: Comparator Input Switch bit                               |

|         | When CM2:CM0 = 110 or 101:                                     |

|         | 1 = VIN- connects to CIN+                                      |

|         | 0 = VIN- connects to CIN-                                      |

| bit 2-0 | CM2:CM0: Comparator Mode bits                                  |

|         | Figure 6-2 shows the Comparator modes and CM2:CM0 bit settings |

#### 6.1 Comparator Operation

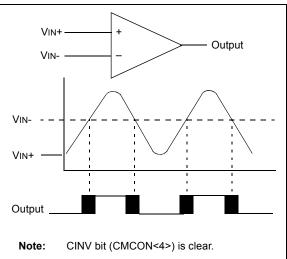

A single comparator is shown in Figure 6-1, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 6-1 represent the uncertainty due to input offsets and response time.

Note: To use CIN+ and CIN- pins as analog inputs, the appropriate bits must be programmed in the CMCON (19h) register.

The polarity of the comparator output can be inverted by setting the CINV bit (CMCON<4>). Clearing CINV results in a non-inverted output. A complete table showing the output state versus input conditions and the polarity bit is shown in Table 6-1.

#### TABLE 6-1: OUTPUT STATE VS. INPUT CONDITIONS

| Input Conditions | CINV | COUT |

|------------------|------|------|

| VIN- > VIN+      | 0    | 0    |

| VIN- < VIN+      | 0    | 1    |

| VIN- > VIN+      | 1    | 1    |

| VIN- < VIN+      | 1    | 0    |

SINGLE COMPARATOR

#### 6.2 Comparator Configuration

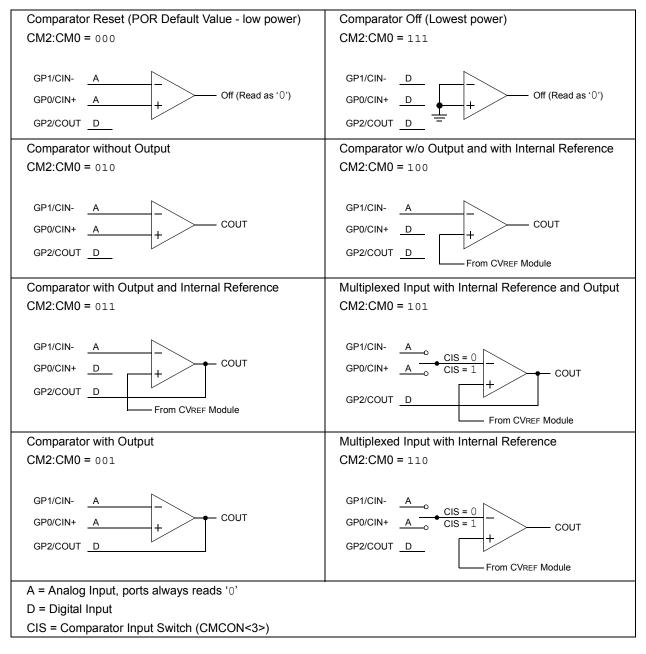

There are eight modes of operation for the comparator. The CMCON register, shown in Register 6-1, is used to select the mode. Figure 6-2 shows the eight possible modes. The TRISIO register controls the data direction of the comparator pins for each mode. If the Comparator mode is changed, the comparator output level may not be valid for a specified period of time. Refer to the specifications in **Section 12.0 "Electrical Specifications"**.

Note: Comparator interrupts should be disabled during a Comparator mode change. Otherwise, a false interrupt may occur.

#### FIGURE 6-2: COMPARATOR I/O OPERATING MODES

#### 6.5 Comparator Reference

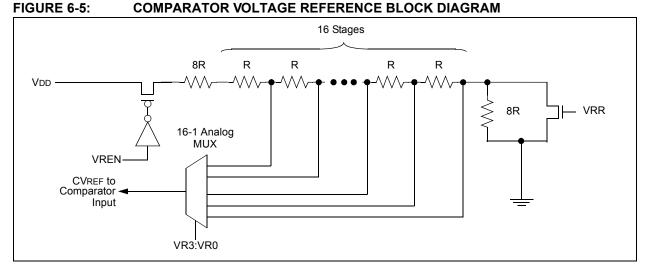

The comparator module also allows the selection of an internally generated voltage reference for one of the comparator inputs. The internal reference signal is used for four of the eight Comparator modes. The VRCON register, Register 6-2, controls the voltage reference module shown in Figure 6-5.

### 6.5.1 CONFIGURING THE VOLTAGE REFERENCE

The voltage reference can output 32 distinct voltage levels, 16 in a high range and 16 in a low range.

The following equations determine the output voltages:

VRR = 1 (low range): CVREF = (VR3:VR0 / 24) x VDD VRR = 0 (high range): CVREF = (VDD / 4) + (VR3:VR0 x VDD / 32)

#### 6.5.2 VOLTAGE REFERENCE ACCURACY/ERROR

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 6-5) keep CVREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the Comparator Voltage Reference can be found in **Section 12.0 "Electrical Specifications"**.

#### 6.6 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output is ensured to have a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (Table 12-7).

#### 6.7 Operation During Sleep

Both the comparator and voltage reference, if enabled before entering Sleep mode, remain active during Sleep. This results in higher Sleep currents than shown in the power-down specifications. The additional current consumed by the comparator and the voltage reference is shown separately in the specifications. To minimize power consumption while in Sleep mode, turn off the comparator, CM2:CM0 = 111, and voltage refeence, VRCON<7> = 0. While the comparator is enabled during Sleep, an interrupt will wake-up the device. If the device wakes up from Sleep, the contents of the CMCON and VRCON registers are not affected.

#### 6.8 Effects of a Reset

A device Reset forces the CMCON and VRCON registers to their Reset states. This forces the comparator module to be in the Comparator Reset mode, CM2:CM0 = 000 and the voltage reference to its off state. Thus, all potential inputs are analog inputs with the comparator and voltage reference disabled to consume the smallest current possible.

#### 7.3 A/D Operation During Sleep

The A/D converter module can operate during Sleep. This requires the A/D clock source to be set to the internal RC oscillator. When the RC clock source is selected, the A/D waits one instruction before starting the conversion. This allows the SLEEP instruction to be executed, thus eliminating much of the switching noise from the conversion. When the conversion is complete, the GO/DONE bit is cleared, and the result is loaded into the ADRESH:ADRESL registers. If the A/D interrupt is enabled, the device awakens from Sleep. If the A/D interrupt is not enabled, the A/D module is turned off, although the ADON bit remains set. When the A/D clock source is something other than RC, a SLEEP instruction causes the present conversion to be aborted, and the A/D module is turned off. The ADON bit remains set.

#### 7.4 Effects of Reset

A device Reset forces all registers to their Reset state. Thus the A/D module is turned off and any pending conversion is aborted. The ADRESH:ADRESL registers are unchanged.

| Address  | Name   | Bit 7       | Bit 6                                                                                        | Bit 5          | Bit 4         | Bit 3          | Bit 2        | Bit 1      | Bit 0   | Value on<br>POR,<br>BOD | Value on<br>all other<br>Resets |

|----------|--------|-------------|----------------------------------------------------------------------------------------------|----------------|---------------|----------------|--------------|------------|---------|-------------------------|---------------------------------|

| 05h      | GPIO   | —           | _                                                                                            | GPIO5          | GPIO4         | GPIO3          | GPIO2        | GPI01      | GPIO0   | xx xxxx                 | uu uuuu                         |

| 0Bh, 8Bh | INTCON | GIE         | PEIE                                                                                         | T0IE           | INTE          | GPIE           | T0IF         | INTF       | GPIF    | 0000 0000               | 0000 000u                       |

| 0Ch      | PIR1   | EEIF        | ADIF                                                                                         | —              |               | CMIF           | —            | _          | TMR1IF  | 00 00                   | 00 00                           |

| 1Eh      | ADRESH | Most Signif | icant 8 bits c                                                                               | of the Left Sh | ifted A/D res | sult or 2 bits | of the Right | Shifted Re | esult   | XXXX XXXX               | սսսս սսսս                       |

| 1Fh      | ADCON0 | ADFM        | VCFG                                                                                         | —              | -             | CHS1           | CHS0         | GO         | ADON    | 00 0000                 | 00 0000                         |

| 85h      | TRISIO | _           | _                                                                                            | TRISI05        | TRISIO4       | TRISIO3        | TRISIO2      | TRISIO1    | TRISI00 | 11 1111                 | 11 1111                         |

| 8Ch      | PIE1   | EEIE        | ADIE                                                                                         | —              | _             | CMIE           | —            | _          | TMR1IE  | 00 00                   | 00 00                           |

| 9Eh      | ADRESL | Least Signi | east Significant 2 bits of the Left Shifted A/D Result or 8 bits of the Right Shifted Result |                |               |                |              |            | Result  | XXXX XXXX               | uuuu uuuu                       |

| 9Fh      | ANSEL  | _           | ADCS2                                                                                        | ADCS1          | ADCS0         | ANS3           | ANS2         | ANS1       | ANS0    | -000 1111               | -000 1111                       |

|          |        |             |                                                                                              |                |               |                |              |            |         |                         |                                 |

#### TABLE 7-2: SUMMARY OF A/D REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D converter module.

# 9.0 SPECIAL FEATURES OF THE CPU

Certain special circuits that deal with the needs of real time applications are what sets a microcontroller apart from other processors. The PIC12F629/675 family has a host of such features intended to:

- maximize system reliability

- minimize cost through elimination of external components

- provide power saving operating modes and offer code protection

These features are:

- Oscillator selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Detect (BOD)

- Interrupts

- Watchdog Timer (WDT)

- Sleep

- Code protection

- ID Locations

- In-Circuit Serial Programming

The PIC12F629/675 has a Watchdog Timer that is controlled by Configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in Reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which can provide at least a 72 ms Reset. With these three functions on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low current Power-down mode. The user can wake-up from Sleep through:

- External Reset

- · Watchdog Timer wake-up

- An interrupt

Several oscillator options are also made available to allow the part to fit the application. The INTOSC option saves system cost while the LP crystal option saves power. A set of Configuration bits are used to select various options (see Register 9.2).

#### 9.4 Interrupts

The PIC12F629/675 has 7 sources of interrupt:

- External Interrupt GP2/INT

- TMR0 Overflow Interrupt

- · GPIO Change Interrupts

- Comparator Interrupt

- A/D Interrupt (PIC12F675 only)

- TMR1 Overflow Interrupt

- EEPROM Data Write Interrupt

The Interrupt Control register (INTCON) and Peripheral Interrupt register (PIR) record individual interrupt requests in flag bits. The INTCON register also has individual and Global Interrupt Enable (GIE) bits.

A Global Interrupt Enable bit, GIE (INTCON<7>) enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register and PIE register. GIE is cleared on Reset.

The return from interrupt instruction, RETFIE, exits interrupt routine, as well as sets the GIE bit, which re-enables unmasked interrupts.

The following interrupt flags are contained in the INTCON register:

- INT pin interrupt

- · GP port change interrupt

- TMR0 overflow interrupt

The peripheral interrupt flags are contained in the special register PIR1. The corresponding interrupt enable bit is contained in special register PIE1.

The following interrupt flags are contained in the PIR register:

- EEPROM data write interrupt

- A/D interrupt

- · Comparator interrupt

- Timer1 overflow interrupt

- When an interrupt is serviced:

- The GIE is cleared to disable any further interrupt

- The return address is pushed onto the stack

- The PC is loaded with 0004h

Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid GP2/ INT recursive interrupts.

For external interrupt events, such as the INT pin, or GP port change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends upon when the interrupt event occurs (see Figure 9-11). The latency is the same for one or twocycle instructions. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

Note 1: Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

© 2010 Microchip Technology Inc.

#### 9.8 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

**Note:** The entire data EEPROM and Flash program memory will be erased when the code protection is turned off. The INTOSC calibration data is also erased. See PIC12F629/675 Programming Specification for more information.

#### 9.9 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable during Program/Verify. Only the Least Significant 7 bits of the ID locations are used.

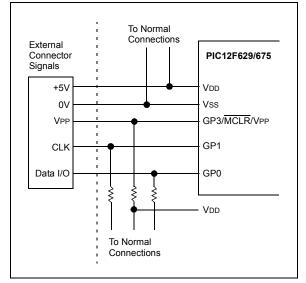

#### 9.10 In-Circuit Serial Programming

The PIC12F629/675 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for:

- power

- ground

- programming voltage

This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the GP0 and GP1 pins low, while raising the  $\overline{\text{MCLR}}$  (VPP) pin from VIL to VIHH (see Programming Specification). GP0 becomes the programming data and GP1 becomes the programming clock. Both GP0 and GP1 are Schmitt Trigger inputs in this mode.

After Reset, to place the device into Programming/ Verify mode, the PC is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending on whether the command was a load or a read. For complete details of serial programming, please refer to the Programming Specifications.

A typical In-Circuit Serial Programming connection is shown in Figure 9-14.

#### FIGURE 9-14:

#### TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

#### 9.11 In-Circuit Debugger

Since in-circuit debugging requires the loss of clock, data and MCLR pins, MPLAB<sup>®</sup> ICD 2 development with an 8-pin device is not practical. A special 14-pin PIC12F675-ICD device is used with MPLAB ICD 2 to provide separate clock, data and MCLR pins and frees all normally available pins to the user.

This special ICD device is mounted on the top of the header and its signals are routed to the MPLAB ICD 2 connector. On the bottom of the header is an 8-pin socket that plugs into the user's target via the 8-pin stand-off connector.

When the ICD pin on the PIC12F675-ICD device is held low, the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB ICD 2. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 9-10 shows which features are consumed by the background debugger:

#### TABLE 9-10: DEBUGGER RESOURCES

| I/O pins       | ICDCLK, ICDDATA                     |

|----------------|-------------------------------------|

| Stack          | 1 level                             |

| Program Memory | Address 0h must be NOP<br>300h-3FEh |

For more information, see 8-Pin MPLAB ICD 2 Header Information Sheet (DS51292) available on Microchip's web site (www.microchip.com).

NOTES:

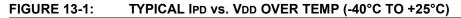

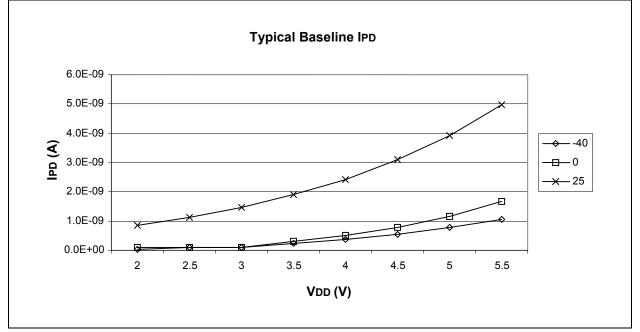

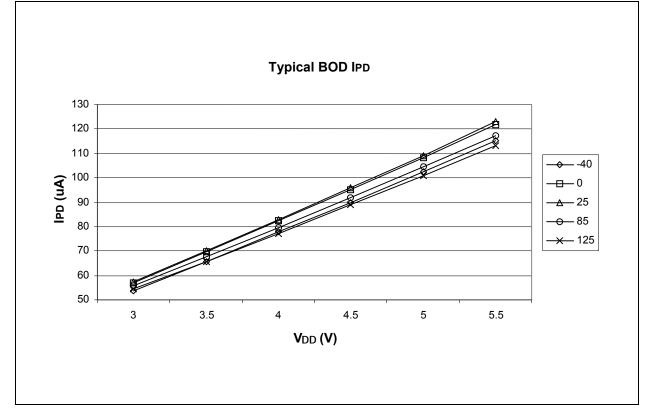

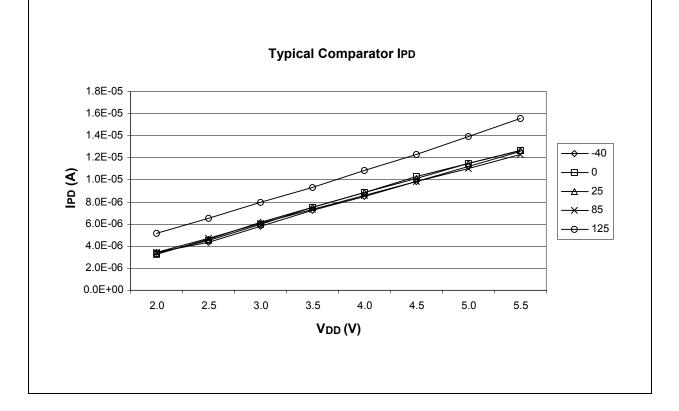

#### 13.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for design guidance and are not tested.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

The data presented in this section is a **statistical summary** of data collected on units from different lots over a period of time and matrix samples. "Typical" represents the mean of the distribution at 25°C. "Max" or "min" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation, over the whole temperature range.

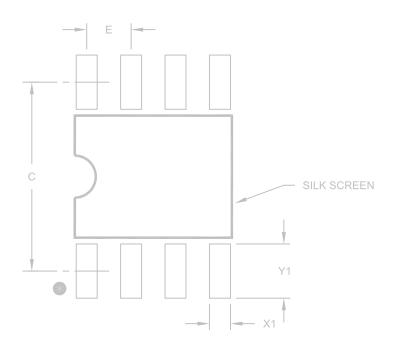

#### 8-Lead Plastic Small Outline (SN) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                         | Units | MILLIMETERS |      |      |  |

|-------------------------|-------|-------------|------|------|--|

| Dimensi                 | MIN   | NOM         | MAX  |      |  |

| Contact Pitch           | E     | 1.27 BSC    |      |      |  |

| Contact Pad Spacing     | С     |             | 5.40 |      |  |

| Contact Pad Width (X8)  | X1    |             |      | 0.60 |  |

| Contact Pad Length (X8) | Y1    |             |      | 1.55 |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A

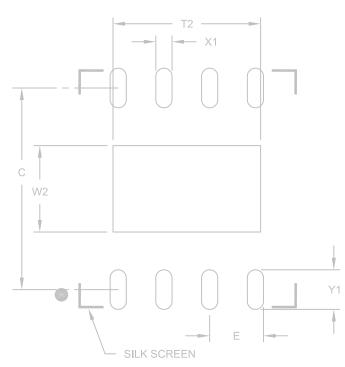

8-Lead Plastic Dual Flat, No Lead Package (MF) - 6x5 mm Body [DFN-S]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                            | Units |          | MILLIMETERS |      |  |

|----------------------------|-------|----------|-------------|------|--|

| Dimension Limits           |       | MIN      | NOM         | MAX  |  |

| Contact Pitch              | E     | 1.27 BSC |             |      |  |

| Optional Center Pad Width  | W2    |          |             | 2.40 |  |

| Optional Center Pad Length | T2    |          |             | 4.10 |  |

| Contact Pad Spacing        | С     |          | 5.60        |      |  |

| Contact Pad Width (X8)     | X1    |          |             | 0.45 |  |

| Contact Pad Length (X8)    | Y1    |          |             | 1.10 |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2122A

#### 8-Lead Plastic Dual Flat, No Lead Package (MD) – 4x4x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units | Units MILLIMETERS |          |      |  |

|------------------------|-------|-------------------|----------|------|--|

| Dimension Limits       |       | MIN               | NOM      | MAX  |  |

| Number of Pins         | N     | 8                 |          |      |  |

| Pitch                  | е     |                   | 0.80 BSC |      |  |

| Overall Height         | A     | 0.80              | 0.90     | 1.00 |  |

| Standoff               | A1    | 0.00              | 0.02     | 0.05 |  |

| Contact Thickness      | A3    | 0.20 REF          |          |      |  |

| Overall Length         | D     | 4.00 BSC          |          |      |  |

| Exposed Pad Width      | E2    | 2.60              | 2.70     | 2.80 |  |

| Overall Width          | E     |                   | 4.00 BSC |      |  |

| Exposed Pad Length     | D2    | 3.40              | 3.50     | 3.60 |  |

| Contact Width          | b     | 0.25              | 0.30     | 0.35 |  |

| Contact Length         | L     | 0.30              | 0.40     | 0.50 |  |

| Contact-to-Exposed Pad | К     | 0.20              | -        | -    |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-131E Sheet 2 of 2

NOTES: