# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-VDFN Exposed Pad                                                       |

| Supplier Device Package    | 8-DFN-S (6x5)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f629-i-mf |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                           | 7    |

|-------|-----------------------------------------------------------|------|

| 2.0   | Memory Organization                                       | 9    |

| 3.0   | GPIO Port                                                 | 21   |

| 4.0   | Timer0 Module                                             | . 29 |

| 5.0   | Timer1 Module with Gate Control                           | . 32 |

| 6.0   | Comparator Module                                         | . 37 |

| 7.0   | Analog-to-Digital Converter (A/D) Module (PIC12F675 only) | 43   |

| 8.0   | Data EEPROM Memory                                        | 49   |

| 9.0   | Special Features of the CPU                               |      |

| 10.0  | Instruction Set Summary                                   | 71   |

| 11.0  | Development Support                                       | 81   |

| 12.0  | Electrical Specifications                                 | 85   |

| 13.0  | DC and AC Characteristics Graphs and Tables               | 107  |

| 14.0  | Packaging Information                                     | 117  |

| Apper | ndix A: Data Sheet Revision History                       | 127  |

| Apper | ndix B: Device Differences                                | 127  |

| Apper | ndix C: Device Migrations                                 | 128  |

| Apper | ndix D: Migrating from other PIC <sup>®</sup> Devices     | 128  |

| Index |                                                           | 129  |

| On-Li | ne Support                                                | 133  |

| Syste | ns Information and Upgrade Hot Line                       | 133  |

| Reade | er Response                                               | 134  |

| Produ | ct Identification System                                  | 135  |

|       |                                                           |      |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

# Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

# **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 2.2.2.6 PCON Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Detect (BOD)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON Register bits are shown in Register 2-6.

## REGISTER 2-6: PCON: POWER CONTROL REGISTER (ADDRESS: 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-x |

|-------|-----|-----|-----|-----|-----|-------|-------|

|       | —   | —   | —   | _   | _   | POR   | BOD   |

| bit 7 | •   |     |     |     |     |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-2 | Unimplemented: Read as '0'                                                                                                                              |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | POR: Power-on Reset Status bit                                                                                                                          |

|         | <ul> <li>1 = No Power-on Reset occurred</li> <li>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)</li> </ul>       |

| bit 0   | BOD: Brown-out Detect Status bit                                                                                                                        |

|         | <ul> <li>1 = No Brown-out Detect occurred</li> <li>0 = A Brown-out Detect occurred (must be set in software after a Brown-out Detect occurs)</li> </ul> |

### 2.2.2.7 OSCCAL Register

The Oscillator Calibration register (OSCCAL) is used to calibrate the internal 4 MHz oscillator. It contains 6 bits to adjust the frequency up or down to achieve 4 MHz.

The OSCCAL register bits are shown in Register 2-7.

### REGISTER 2-7: OSCCAL: OSCILLATOR CALIBRATION REGISTER (ADDRESS: 90h)

|              |         |                  |       |                                         | •     | ,   |       |  |  |

|--------------|---------|------------------|-------|-----------------------------------------|-------|-----|-------|--|--|

| R/W-1        | R/W-0   | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | U-0 | U-0   |  |  |

| CAL5         | CAL4    | CAL3 CAL2        |       | CAL1                                    | CAL0  | _   | _     |  |  |

| bit 7        |         |                  |       |                                         |       | ·   | bit 0 |  |  |

|              |         |                  |       |                                         |       |     |       |  |  |

| Legend:      |         |                  |       |                                         |       |     |       |  |  |

| R = Readab   | ole bit | W = Writable     | bit   | U = Unimplemented bit, read as '0'      |       |     |       |  |  |

| -n = Value a | it POR  | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |     |       |  |  |

|              |         |                  |       |                                         |       |     |       |  |  |

| bit 7-2      |         | 6-bit Signed O   |       | oration bits                            |       |     |       |  |  |

|              |         | aximum frequer   |       |                                         |       |     |       |  |  |

| 100000 = | Center | frequency |  |

|----------|--------|-----------|--|

|          |        |           |  |

000000 = Minimum frequency

# bit 1-0 Unimplemented: Read as '0'

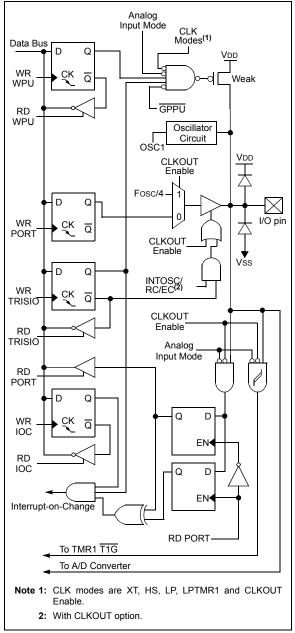

#### GP4/AN3/T1G/OSC2/CLKOUT 3.3.5

Figure 3-4 shows the diagram for this pin. The GP4 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the A/D (PIC12F675 only)

- a TMR1 gate input

- · a crystal/resonator connection

- · a clock output

#### FIGURE 3-4: **BLOCK DIAGRAM OF GP4**

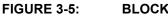

#### 3.3.6 GP5/T1CKI/OSC1/CLKIN

Figure 3-5 shows the diagram for this pin. The GP5 pin is configurable to function as one of the following:

- a general purpose I/O

- · a TMR1 clock input

- · a crystal/resonator connection

- · a clock input

#### **BLOCK DIAGRAM OF GP5**

# 6.0 COMPARATOR MODULE

The PIC12F629/675 devices have one analog comparator. The inputs to the comparator are multiplexed with the GP0 and GP1 pins. There is an on-chip Comparator Voltage Reference that can also be applied to an input of the comparator. In addition, GP2 can be configured as the comparator output.

The Comparator Control Register (CMCON), shown in Register 6-1, contains the bits to control the comparator.

## **REGISTER 6-1:** CMCON: COMPARATOR CONTROL REGISTER (ADDRESS: 19h)

| U-0   | R-0  | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|------|-----|-------|-------|-------|-------|-------|

| —     | COUT | —   | CINV  | CIS   | CM2   | CM1   | CM0   |

| bit 7 |      |     |       |       |       |       | bit 0 |

|       |      |     |       |       |       |       |       |

|       |      |     |       |       |       |       |       |

| Legena:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                                     |

|---------|----------------------------------------------------------------|

| bit 6   | COUT: Comparator Output bit                                    |

|         | When CINV = 0:                                                 |

|         | 1 = VIN+ > VIN-                                                |

|         | 0 = VIN+ < VIN-                                                |

|         | When CINV = 1:                                                 |

|         | 1 = VIN+ < VIN-                                                |

|         | 0 = VIN + > VIN-                                               |

| bit 5   | Unimplemented: Read as '0'                                     |

| bit 4   | CINV: Comparator Output Inversion bit                          |

|         | 1 = Output inverted                                            |

|         | 0 = Output not inverted                                        |

| bit 3   | CIS: Comparator Input Switch bit                               |

|         | When CM2:CM0 = 110 or 101:                                     |

|         | 1 = VIN- connects to CIN+                                      |

|         | 0 = VIN- connects to CIN-                                      |

| bit 2-0 | CM2:CM0: Comparator Mode bits                                  |

|         | Figure 6-2 shows the Comparator modes and CM2:CM0 bit settings |

| REGISTER      | 6-2: VRCO                       | N: VOLTAGE                                                                                                                                                          | REFEREN       | CE CONTRO        | L REGISTER      | R (ADDRESS:     | 99h)  |  |

|---------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|-----------------|-----------------|-------|--|

| R/W-0         | U-0                             | R/W-0                                                                                                                                                               | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0 |  |

| VREN          |                                 | VRR                                                                                                                                                                 | _             | VR3              | VR2             | VR1             | VR0   |  |

| bit 7         |                                 |                                                                                                                                                                     |               |                  |                 |                 | bit ( |  |

| Legend:       |                                 |                                                                                                                                                                     |               |                  |                 |                 |       |  |

| R = Readabl   | le bit                          | W = Writable                                                                                                                                                        | bit           | U = Unimplei     | mented bit, rea | d as '0'        |       |  |

| -n = Value at | t POR                           | '1' = Bit is set                                                                                                                                                    |               | '0' = Bit is cle | ared            | x = Bit is unki | nown  |  |

|               | 0 = CVREF cir                   | cuit powered o<br>cuit powered d                                                                                                                                    | own, no Idd o | drain            |                 |                 |       |  |

| bit 6         | Unimplemen                      | ted: Read as '                                                                                                                                                      | 0'            |                  |                 |                 |       |  |

| bit 5         | VRR: CVREF                      | Range Selection                                                                                                                                                     | on bit        |                  |                 |                 |       |  |

|               | 1 = Low range<br>0 = High range |                                                                                                                                                                     |               |                  |                 |                 |       |  |

| bit 4         | Unimplemen                      | ted: Read as '                                                                                                                                                      | 0'            |                  |                 |                 |       |  |

| bit 3-0       | When VRR =                      | <b>VR3:VR0:</b> CVREF value selection $0 \le VR$ [3:0] $\le 15$<br>When VRR = 1: CVREF = (VR3:VR0 / 24) * VDD<br>When VRR = 0: CVREF = VDD/4 + (VR3:VR0 / 32) * VDD |               |                  |                 |                 |       |  |

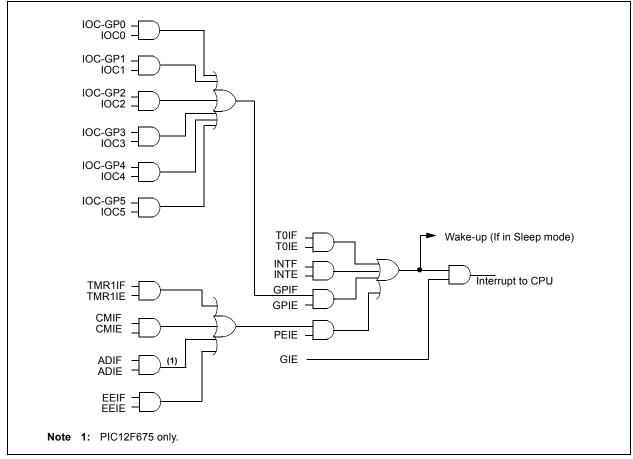

# 6.9 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of the comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<6>, to determine the actual change that has occurred. The CMIF bit, PIR1<3>, is the comparator interrupt flag. This bit must be reset in software by clearing it to '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<3>) and the PEIE bit (INT-CON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are cleared, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

Note: If a change in the CMCON register (COUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CMIF (PIR1<3>) interrupt flag may not get set.

| Address | Name   | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOD | Value on<br>all other<br>Resets |

|---------|--------|-------|-------|---------|---------|---------|---------|---------|---------|----------------------|---------------------------------|

| 0Bh/8Bh | INTCON | GIE   | PEIE  | T0IE    | INTE    | GPIE    | T0IF    | INTF    | GPIF    | 0000 0000            | 0000 000u                       |

| 0Ch     | PIR1   | EEIF  | ADIF  | _       | —       | CMIF    | _       | _       | TMR1IF  | 00 00                | 00 00                           |

| 19h     | CMCON  | _     | COUT  | —       | CINV    | CIS     | CM2     | CM1     | CM0     | -0-0 0000            | -0-0 0000                       |

| 8Ch     | PIE1   | EEIE  | ADIE  | —       | _       | CMIE    | _       | _       | TMR1IE  | 00 00                | 00 00                           |

| 85h     | TRISIO | _     | _     | TRISIO5 | TRISIO4 | TRISIO3 | TRISIO2 | TRISIO1 | TRISIO0 | 11 1111              | 11 1111                         |

| 99h     | VRCON  | VREN  | _     | VRR     |         | VR3     | VR2     | VR1     | VR0     | 0-0- 0000            | 0-0- 0000                       |

# TABLE 6-2: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the comparator module.

# 9.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1') to select various device configurations, as shown in Register 9.2. These bits are mapped in program memory location 2007h.

**Note:** Address 2007h is beyond the user program memory space. It belongs to the special configuration memory space (2000h-3FFFh), which can be accessed only during programming. See PIC12F629/675 Programming Specification for more information.

#### REGISTER 9-1: CONFIG: CONFIGURATION WORD (ADDRESS: 2007h)

| R/P-1  | R/P-1 | U-0 | U-0 | U-0 | R/P-1 |

|--------|-------|-----|-----|-----|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| BG1    | BG0   | Ι   | Ι   | _   | CPD   | CP    | BODEN | MCLRE | PWRTE | WDTE  | F0SC2 | F0SC1 | F0SC0 |

| bit 13 |       |     |     |     |       |       |       |       |       |       |       |       | bit 0 |

| Legend:                    |                |                     |                    |

|----------------------------|----------------|---------------------|--------------------|

| P = Programmed using ICSP™ |                |                     |                    |

| R = Readable bit           | Writable bit   | U = Unimplemented b | pit, read as '0'   |

| -n = Value at POR          | 1 = bit is set | 0 = bit is cleared  | x = bit is unknown |

| bit 13-12 | BG1:BG0: Bandgap Calibration bits for BOD and POR voltage <sup>(1)</sup><br>00 = Lowest bandgap voltage<br>11 = Highest bandgap voltage                                                                                                         |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| h:+ 44 O  |                                                                                                                                                                                                                                                 |

| bit 11-9  | Unimplemented: Read as '0'                                                                                                                                                                                                                      |

| bit 8     | <b>CPD:</b> Data Code Protection bit <sup>(2)</sup><br>1 = Data memory code protection is disabled<br>0 = Data memory code protection is enabled                                                                                                |

| bit 7     | $\overline{CP}$ : Code Protection bit <sup>(3)</sup>                                                                                                                                                                                            |

| Dit 7     | 1 = Program Memory code protection is disabled                                                                                                                                                                                                  |

|           | 0 = Program Memory code protection is enabled                                                                                                                                                                                                   |

| bit 6     | BODEN: Brown-out Detect Enable bit <sup>(4)</sup>                                                                                                                                                                                               |

|           | 1 = BOD enabled                                                                                                                                                                                                                                 |

|           | 0 = BOD disabled                                                                                                                                                                                                                                |

| bit 5     | MCLRE: GP3/MCLR Pin Function Select bit <sup>(5)</sup>                                                                                                                                                                                          |

|           | 1 = GP3/MCLR pin function is MCLR                                                                                                                                                                                                               |

|           | 0 = GP3/MCLR pin function is digital I/O, MCLR internally tied to VDD                                                                                                                                                                           |

| bit 4     | PWRTE: Power-up Timer Enable bit                                                                                                                                                                                                                |

|           | 1 = PWRT disabled                                                                                                                                                                                                                               |

|           | 0 = PWRT enabled                                                                                                                                                                                                                                |

| bit 3     | WDTE: Watchdog Timer Enable bit                                                                                                                                                                                                                 |

|           | 1 = WDT enabled<br>0 = WDT disabled                                                                                                                                                                                                             |

| 1.11 O O  |                                                                                                                                                                                                                                                 |

| bit 2-0   | <b>FOSC2:FOSC0</b> : Oscillator Selection bits<br>111 = RC oscillator: CLKOUT function on GP4/OSC2/CLKOUT pin, RC on GP5/OSC1/CLKIN                                                                                                             |

|           | 110 = RC oscillator: I/O function on GP4/OSC2/CLKOUT pin, RC on GP5/OSC1/CLKIN                                                                                                                                                                  |

|           | 101 = INTOSC oscillator: CLKOUT function on GP4/OSC2/CLKOUT pin, I/O function on GP5/OSC1/CLKIN                                                                                                                                                 |

|           | 100 = INTOSC oscillator: I/O function on GP4/OSC2/CLKOUT pin, I/O function on GP5/OSC1/CLKIN                                                                                                                                                    |

|           | 011 = EC: I/O function on GP4/OSC2/CLKOUT pin, CLKIN on GP5/OSC1/CLKIN                                                                                                                                                                          |

|           | 010 = HS oscillator: High speed crystal/resonator on GP4/OSC2/CLKOUT and GP5/OSC1/CLKIN                                                                                                                                                         |

|           | 001 = XT oscillator: Crystal/resonator on GP4/OSC2/CLKOUT and GP5/OSC1/CLKIN<br>000 = LP oscillator: Low-power crystal on GP4/OSC2/CLKOUT and GP5/OSC1/CLKIN                                                                                    |

| Note 1    |                                                                                                                                                                                                                                                 |

| Note 1    | : The Bandgap Calibration bits are factory programmed and must be read and saved prior to erasing the device as spec-<br>ified in the PIC12F629/675 Programming Specification. These bits are reflected in an export of the Configuration Word. |

|           | Microchip Development Tools maintain all Calibration bits to factory settings.                                                                                                                                                                  |

| 2         | The entire data EEPROM will be erased when the code protection is turned off.                                                                                                                                                                   |

| 3         | : The entire program memory will be erased, including OSCCAL value, when the code protection is turned off.                                                                                                                                     |

| 4         | Enabling Brown-out Detect does not automatically enable Power-up Timer.                                                                                                                                                                         |

|           |                                                                                                                                                                                                                                                 |

5: When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled.

#### 9.3 Reset

The PIC12F629/675 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- WDT Reset during Sleep C)

- MCLR Reset during normal operation d)

- e) MCLR Reset during Sleep

- Brown-out Detect (BOD) f)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- · Power-on Reset

- MCLR Reset

- · WDT Reset

- · WDT Reset during Sleep

- · Brown-out Detect (BOD) Reset

They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations as indicated in Table 9-4. These bits are used in software to determine the nature of the Reset. See Table 9-7 for a full description of Reset states of all registers.

A simplified block diagram of the on-chip Reset Circuit is shown in Figure 9-4.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See Table 12-4 in Electrical Specifications Section for pulse-width specification.

FIGURE 9-4: External Reset MCLR/ VPP pin SLEEF WDT WDT Module Time-out Reset VDD Rise Detect Power-on Reset סס Brown-out Detect S Q BODEN OST/PWRT OST Chip\_Reset 10-bit Ripple Counter Q R OSC1/ CLKIN pin PWRT On-chip<sup>(1</sup> 10-bit Ripple Counter RC OSC Enable PWRT See Table 9-3 for time-out situations. Enable OST Note 1: This is a separate oscillator from the INTOSC/EC oscillator.

#### SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

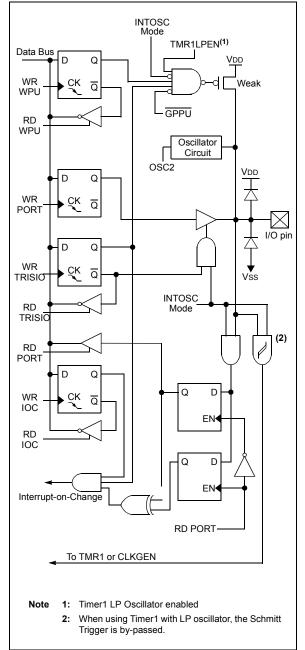

# 9.3.1 MCLR

It should be noted that a WDT Reset does not drive MCLR pin low.

The behavior of the ESD protection on the MCLR pin has been altered from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 9-5, is suggested.

An internal MCLR option is enabled by setting the MCLRE bit in the Configuration Word. When enabled, MCLR is internally tied to VDD. No internal pull-up option is available for the MCLR pin.

#### FIGURE 9-5: RECOMMENDED MCLR CIRCUIT

# 9.3.2 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, simply tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details (see Section 12.0 "Electrical Specifications"). If the BOD is enabled, the maximum rise time specification does not apply. The BOD circuitry will keep the device in Reset until VDD reaches VBOD (see Section 9.3.5 "Brown-Out Detect (BOD)").

| Note: | The POR circuit does not produce a | in |

|-------|------------------------------------|----|

|       | internal Reset when VDD declines.  |    |

When the device starts normal operation (exits the Reset condition), device operating parameters (i.e., voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

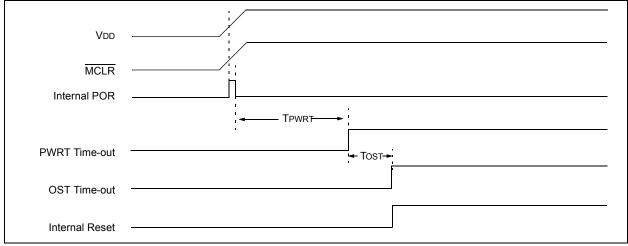

## 9.3.3 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from POR or Brown-out Detect. The Power-up Timer operates on an internal RC oscillator. The chip is kept in Reset as long as PWRT is active. The PWRT delay allows the <u>VDD to</u> rise to an acceptable level. A Configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should always be enabled when Brown-out Detect is enabled.

The Power-up Time delay will vary from chip to chip and due to:

- VDD variation

- Temperature variation

- · Process variation.

See DC parameters for details (Section 12.0 "Electrical Specifications").

## 9.3.4 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from Sleep.

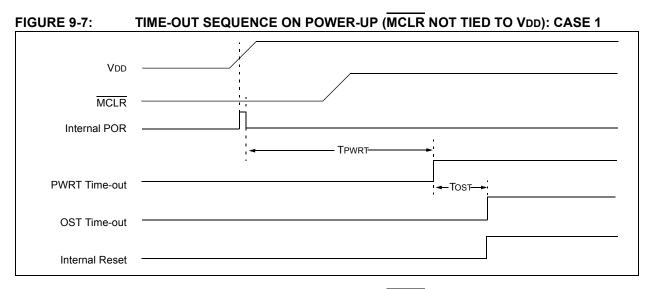

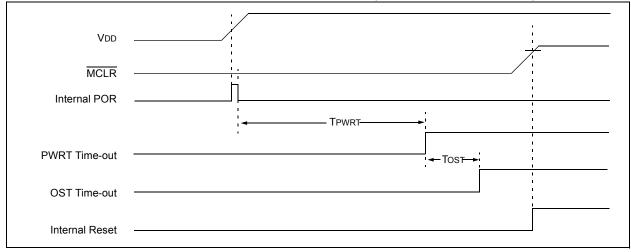

FIGURE 9-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

# FIGURE 9-10: INTERRUPT LOGIC

### TABLE 10-2: PIC12F629/675 INSTRUCTION SET

| Mnen     | nonic, | Decoviation                                        | Cycles     |        | 14-Bit | Opcode | Status | Notes    |       |

|----------|--------|----------------------------------------------------|------------|--------|--------|--------|--------|----------|-------|

| Operands |        | Description                                        |            | MSb    |        |        | LSb    | Affected | Notes |

|          |        | BYTE-ORIENTED FILE RE                              | GISTER OPE | RATIC  | NS     |        |        |          |       |

| ADDWF    | f, d   | Add W and f                                        | 1          | 00     | 0111   | dfff   | ffff   | C,DC,Z   | 1,2   |

| ANDWF    | f, d   | AND W with f                                       | 1          | 00     | 0101   | dfff   | ffff   | Z        | 1,2   |

| CLRF     | f      | Clear f                                            | 1          | 00     | 0001   | lfff   | ffff   | Z        | 2     |

| CLRW     | -      | Clear W                                            | 1          | 00     | 0001   | 0xxx   | xxxx   | Z        |       |

| COMF     | f, d   | Complement f                                       | 1          | 00     | 1001   | dfff   | ffff   | Z        | 1,2   |

| DECF     | f, d   | Decrement f                                        | 1          | 00     | 0011   | dfff   | ffff   | Z        | 1,2   |

| DECFSZ   | f, d   | Decrement f, Skip if 0                             | 1(2)       | 00     | 1011   | dfff   | ffff   |          | 1,2,3 |

| INCF     | f, d   | Increment f                                        | 1          | 00     | 1010   | dfff   | ffff   | Z        | 1,2   |

| INCFSZ   | f, d   | Increment f, Skip if 0                             | 1(2)       | 00     | 1111   | dfff   | ffff   |          | 1,2,3 |

| IORWF    | f, d   | Inclusive OR W with f                              | 1          | 00     | 0100   | dfff   | ffff   | Z        | 1,2   |

| MOVF     | f, d   | Move f                                             | 1          | 00     | 1000   | dfff   | ffff   | Z        | 1,2   |

| MOVWF    | f      | Move W to f                                        | 1          | 00     | 0000   | lfff   | ffff   |          |       |

| NOP      | -      | No Operation                                       | 1          | 00     | 0000   | 0xx0   | 0000   |          |       |

| RLF      | f, d   | Rotate Left f through Carry                        | 1          | 0.0    | 1101   |        | ffff   | С        | 1,2   |

| RRF      | f, d   | Rotate Right f through Carry                       | 1          | 00     | 1100   |        | ffff   | Ċ        | 1,2   |

| SUBWF    | f, d   | Subtract W from f                                  | 1          | 00     | 0010   |        | ffff   | C,DC,Z   | 1,2   |

| SWAPF    | f, d   | Swap nibbles in f                                  | 1          | 00     | 1110   |        | ffff   | 0,20,2   | 1,2   |

| XORWF    | f, d   | Exclusive OR W with f                              | 1          | 00     | 0110   | dfff   | ffff   | Z        | 1,2   |

|          | , -    | BIT-ORIENTED FILE REG                              |            | RATION |        |        |        |          | ,     |

| BCF      | f, b   | Bit Clear f                                        | 1          | 01     | 00bb   | bfff   | ffff   |          | 1,2   |

| BSF      | f, b   | Bit Set f                                          |            | 01     |        | bfff   |        |          | 1,2   |

| BTFSC    | f, b   | Bit Test f, Skip if Clear                          | 1 (2)      | 01     | 10bb   | bfff   | ffff   |          | 3     |

| BTFSS    | f, b   | Bit Test f, Skip if Set                            | 1 (2)      | 01     |        | bfff   |        |          | 3     |

| DIF33    | 1, 0   |                                                    | ( )        |        | ddil   | DIII   | LLLL   |          | 3     |

|          |        | -                                                  |            |        |        |        |        | 0.00.7   |       |

| ADDLW    | k      | Add literal and W                                  | 1          | 11     |        | kkkk   |        | C,DC,Z   |       |

| ANDLW    | k      | AND literal with W                                 | 1          | 11     | 1001   |        |        | Z        |       |

| CALL     | k      | Call subroutine                                    | 2          | 10     |        | kkkk   |        |          |       |

| CLRWDT   | -      | Clear Watchdog Timer                               | 1          | 00     | 0000   | 0110   | 0100   | TO,PD    |       |

| GOTO     | k      | Go to address                                      | 2          | 10     |        | kkkk   |        | -        |       |

| IORLW    | k      | Inclusive OR literal with W                        | 1          | 11     | 1000   |        | kkkk   | Z        |       |

| MOVLW    | k      | Move literal to W                                  | 1          | 11     |        | kkkk   |        |          |       |

| RETFIE   | -      | Return from interrupt                              | 2          | 00     | 0000   | 0000   | 1001   |          |       |

| RETLW    | k      | Return with literal in W                           | 2          | 11     |        | kkkk   |        |          |       |

| RETURN   | -      | Return from Subroutine                             | 2          | 00     | 0000   | 0000   | 1000   |          |       |

| SLEEP    | -      | Go into Standby mode                               | 1          | 00     | 0000   | 0110   | 0011   | TO,PD    |       |

| SUBLW    | k      | Subtract W from literal                            | 1          | 11     |        | kkkk   | kkkk   | C,DC,Z   |       |

| XORLW    | k      | Exclusive OR literal with W                        | 1          | 11     | 1010   | kkkk   | kkkk   | Z        |       |

| Note 1:  |        | /O register is modified as a function of itself (e |            |        |        |        |        |          |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF GPIO, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

3: If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**Note:** Additional information on the mid-range instruction set is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

| MOVF             | Move f                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Description:     | The contents of register f is<br>moved to a destination dependent<br>upon the status of d. If $d = 0$ ,<br>the destination is W register. If $d =$<br>1, the destination is file register f<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                              |  |  |  |  |  |  |

| MOVWF            | Move W to f                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                          |

| Operands:        | $0 \leq f \leq 127$                                                                               |

| Operation:       | $(W) \rightarrow (f)$                                                                             |

| Status Affected: | None                                                                                              |

| Description:     | Move data from W register to<br>register 'f'.                                                     |

| Words:           | 1                                                                                                 |

| Cycles:          | 1                                                                                                 |

| Example:         | MOVWF OPTION                                                                                      |

|                  | Before Instruction<br>OPTION = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION = 0x4F<br>W = 0x4F |

| MOVLW            | Move literal to W                                                                                   |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                            |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                   |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                                 |  |  |  |  |  |  |

| Status Affected: | None                                                                                                |  |  |  |  |  |  |

| Description:     | The eight-bit literal 'k' is loaded into<br>W register. The "don't cares" will<br>assemble as '0's. |  |  |  |  |  |  |

| Words:           | 1                                                                                                   |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                   |  |  |  |  |  |  |

| Example:         | MOVLW 0x5A                                                                                          |  |  |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                                       |  |  |  |  |  |  |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

# 12.0 ELECTRICAL SPECIFICATIONS

# Absolute Maximum Ratings†

| 40 to +125°C         |

|----------------------|

| 65°C to +150°C       |

| 0.3 to +6.5V         |

| 0.3 to +13.5V        |

| 0.3V to (VDD + 0.3V) |

| 800 mW               |

|                      |

| 250 mA               |

| ± 20 mA              |

| ± 20 mA              |

| 25 mA                |

| 25 mA                |

| 125 mA               |

| 125 mA               |

| -                    |

**Note 1:** Power dissipation is calculated as follows: PDIS = VDD x {IDD -  $\sum$  IOH} +  $\sum$  {(VDD-VOH) x IOH} +  $\sum$ (VOI x IOL).

**† NOTICE**: Stresses above those listed under 'Absolute Maximum Ratings' may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

**Note:** Voltage spikes below Vss at the  $\overline{MCLR}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100  $\Omega$  should be used when applying a "low" level to the  $\overline{MCLR}$  pin, rather than pulling this pin directly to Vss.

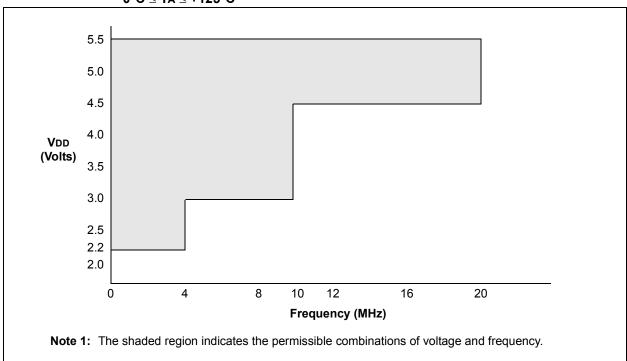

FIGURE 12-3: PIC12F675 WITH A/D ENABLED VOLTAGE-FREQUENCY GRAPH, 0°C  $\leq$  Ta  $\leq$  +125°C

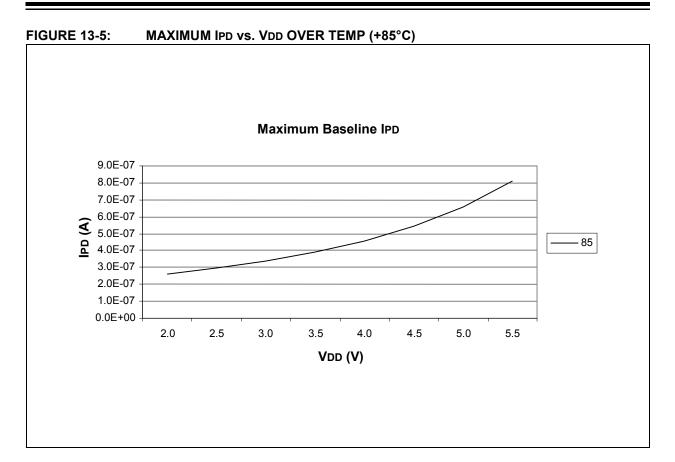

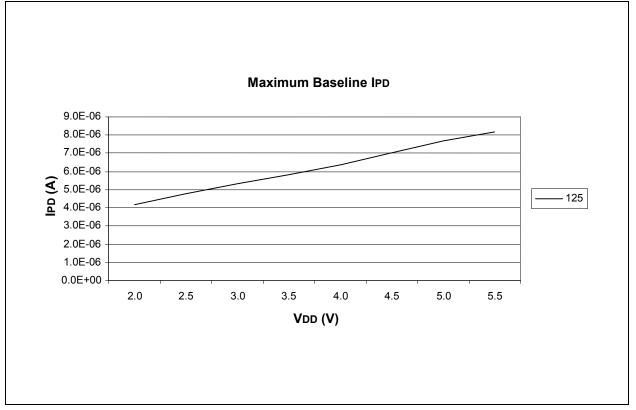

FIGURE 13-6: MAXIMUM IPD vs. VDD OVER TEMP (+125°C)

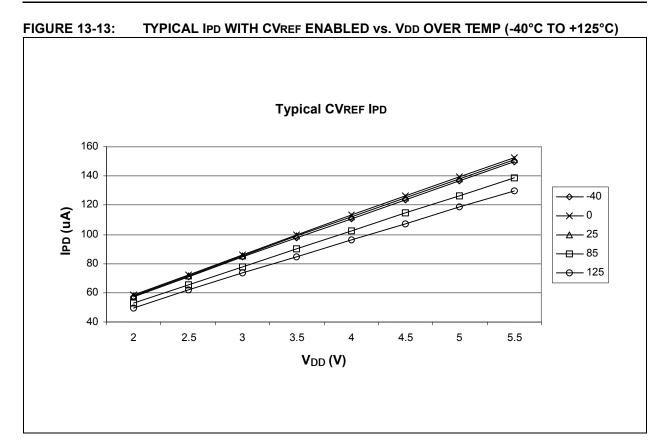

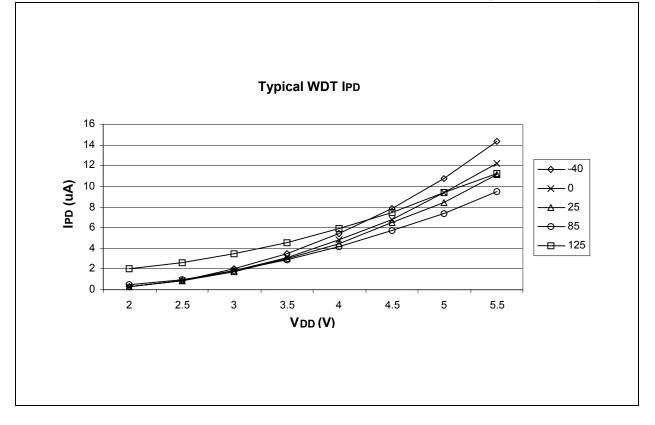

FIGURE 13-14: TYPICAL IPD WITH WDT ENABLED vs. VDD OVER TEMP (-40°C TO +125°C)

# 8-Lead Plastic Small Outline (SN) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

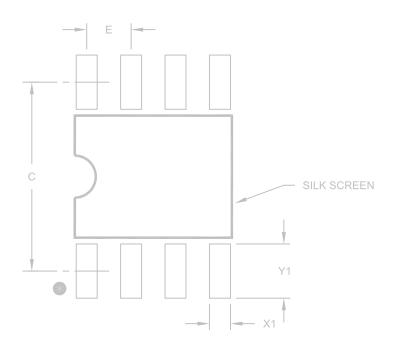

RECOMMENDED LAND PATTERN

|                         | Units |     |          | MILLIMETERS |  |  |  |  |

|-------------------------|-------|-----|----------|-------------|--|--|--|--|

| Dimensi                 | MIN   | NOM | MAX      |             |  |  |  |  |

| Contact Pitch           | E     |     | 1.27 BSC |             |  |  |  |  |

| Contact Pad Spacing     | С     |     | 5.40     |             |  |  |  |  |

| Contact Pad Width (X8)  | X1    |     |          | 0.60        |  |  |  |  |

| Contact Pad Length (X8) | Y1    |     |          | 1.55        |  |  |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A

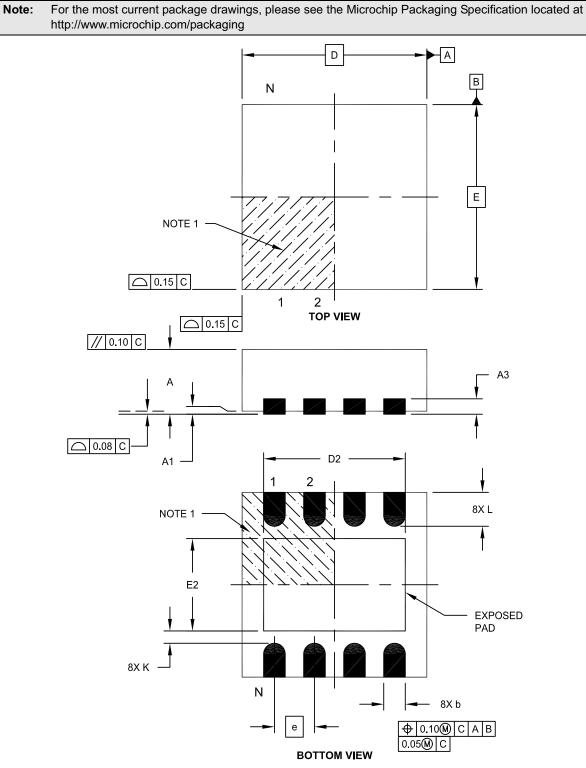

# 8-Lead Plastic Dual Flat, No Lead Package (MD) – 4x4x0.9 mm Body [DFN]

Microchip Technology Drawing C04-131E Sheet 1 of 2

# 8-Lead Plastic Dual Flat, No Lead Package (MD) – 4x4x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units  | MILLIMETERS |          |      |  |  |

|------------------------|--------|-------------|----------|------|--|--|

| Dimension              | Limits | MIN         | NOM      | MAX  |  |  |

| Number of Pins         | N      |             | 8        |      |  |  |

| Pitch                  | е      |             | 0.80 BSC |      |  |  |

| Overall Height         | A      | 0.80        | 0.90     | 1.00 |  |  |

| Standoff               | A1     | 0.00        | 0.02     | 0.05 |  |  |

| Contact Thickness      | A3     |             | 0.20 REF |      |  |  |

| Overall Length         | D      |             | 4.00 BSC |      |  |  |

| Exposed Pad Width      | E2     | 2.60        | 2.70     | 2.80 |  |  |

| Overall Width          | E      | 4.00 BSC    |          |      |  |  |

| Exposed Pad Length     | D2     | 3.40        | 3.50     | 3.60 |  |  |

| Contact Width          | b      | 0.25        | 0.30     | 0.35 |  |  |

| Contact Length         | L      | 0.30        | 0.40     | 0.50 |  |  |

| Contact-to-Exposed Pad | К      | 0.20        | -        | -    |  |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-131E Sheet 2 of 2

# APPENDIX A: DATA SHEET REVISION HISTORY

# **Revision A**

This is a new data sheet.

# **Revision B**

Added characterization graphs.

Updated specifications.

Added notes to indicate Microchip programmers maintain all Calibration bits to factory settings and the PIC12F675 ANSEL register must be initialized to configure pins as digital I/O.

Updated MLF-S package name to DFN-S.

## **Revision C**

## **Revision D (01/2007)**

Updated Package Drawings; Replace PICmicro with PIC; Revised Product ID example (b).

# Revision E (03/2007)

Replaced Package Drawings (Rev. AM); Replaced Development Support Section.

## **Revision F (09/2009)**

Updated Registers to new format; Added information to the "Package Marking Information" (8-Lead DFN) and "Package Details" sections (8-Lead Dual Flat, No Lead Package (MD) 4X4X0.9 mm Body (DFN)); Added Land Patterns for SOIC (SN) and DFN-S (MF) packages; Updated Register 3-2; Added MD Package to the Product identification System chapter; Other minor corrections.

### **Revision G (03/2010)**

Updated the Instruction Set Summary section, adding pages 76 and 77.

# APPENDIX B: DEVICE DIFFERENCES

The differences between the PIC12F629/675 devices listed in this data sheet are shown in Table B-1.

TABLE B-1: DEVICE DIFFERENCES

| Feature | PIC12F629 | PIC12F675 |

|---------|-----------|-----------|

| A/D     | No        | Yes       |