# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                            |

| Supplier Device Package    | 8-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f629-i-sn |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | Device Overview                                           | 7    |

|-------|-----------------------------------------------------------|------|

| 2.0   | Memory Organization                                       | 9    |

| 3.0   | GPIO Port                                                 | 21   |

| 4.0   | Timer0 Module                                             | . 29 |

| 5.0   | Timer1 Module with Gate Control                           | . 32 |

| 6.0   | Comparator Module                                         | . 37 |

| 7.0   | Analog-to-Digital Converter (A/D) Module (PIC12F675 only) | 43   |

| 8.0   | Data EEPROM Memory                                        | 49   |

| 9.0   | Special Features of the CPU                               |      |

| 10.0  | Instruction Set Summary                                   | 71   |

| 11.0  | Development Support                                       | 81   |

| 12.0  | Electrical Specifications                                 | 85   |

| 13.0  | DC and AC Characteristics Graphs and Tables               | 107  |

| 14.0  | Packaging Information                                     | 117  |

| Apper | ndix A: Data Sheet Revision History                       | 127  |

| Apper | ndix B: Device Differences                                | 127  |

| Apper | ndix C: Device Migrations                                 | 128  |

| Apper | ndix D: Migrating from other PIC <sup>®</sup> Devices     | 128  |

| Index |                                                           | 129  |

| On-Li | ne Support                                                | 133  |

| Syste | ns Information and Upgrade Hot Line                       | 133  |

| Reade | er Response                                               | 134  |

| Produ | ct Identification System                                  | 135  |

|       |                                                           |      |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

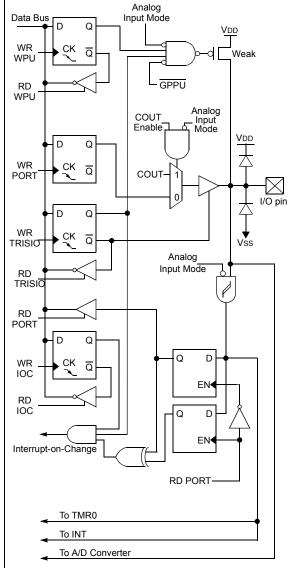

### 3.3.3 GP2/AN2/T0CKI/INT/COUT

Figure 3-2 shows the diagram for this pin. The GP2 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the A/D (PIC12F675 only)

- the clock input for TMR0

- an external edge triggered interrupt

- · a digital output from the comparator

# FIGURE 3-2: BLOCK DIAGRAM OF GP2

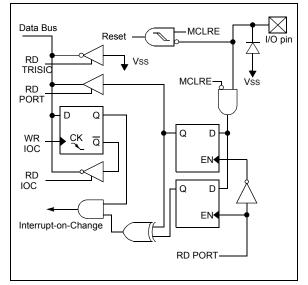

### 3.3.4 GP3/MCLR/VPP

Figure 3-3 shows the diagram for this pin. The GP3 pin is configurable to function as one of the following:

- a general purpose input

- as Master Clear Reset

#### FIGURE 3-3: BLOCK DIAGRAM OF GP3

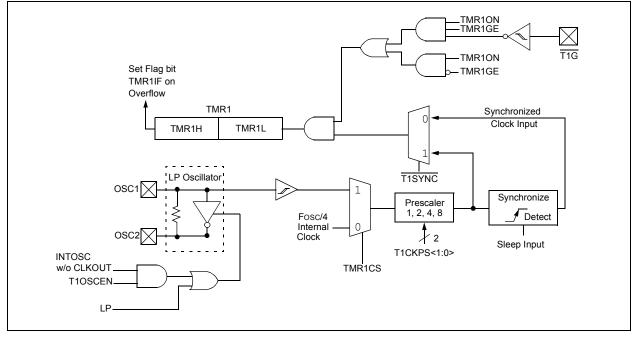

### 5.0 TIMER1 MODULE WITH GATE CONTROL

The PIC12F629/675 devices have a 16-bit timer. Figure 5-1 shows the basic block diagram of the Timer1 module. Timer1 has the following features:

- 16-bit timer/counter (TMR1H:TMR1L)

- · Readable and writable

- Internal or external clock selection

- Synchronous or asynchronous operation

- Interrupt on overflow from FFFFh to 0000h

- Wake-up upon overflow (Asynchronous mode)

- Optional external enable input (T1G)

- · Optional LP oscillator

### FIGURE 5-1: TIMER1 BLOCK DIAGRAM

The Timer1 Control register (T1CON), shown in Register 5.1, is used to enable/disable Timer1 and select the various features of the Timer1 module.

Note: Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

### 5.4 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 5.4.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

Note: The ANSEL (9Fh) and CMCON (19h) registers must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'. The ANSEL register is defined for the PIC12F675.

# 5.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L, while the timer is running from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

# 5.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins OSC1 (input) and OSC2 (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator rated up to 37 kHz. It will continue to run during Sleep. It is primarily intended for a 32 kHz crystal. Table 9-2 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is shared with the system LP oscillator. Thus, Timer1 can use this mode only when the system clock is derived from the internal oscillator. As with the system LP oscillator, the user must provide a software time delay to ensure proper oscillator start-up.

While enabled, TRISIO4 and TRISIO5 are set. GP4 and GP5 read '0' and TRISIO4 and TRISIO5 are read '1'.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to enabling Timer1.

## 5.6 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To setup the timer to wake the device:

- Timer1 must be on (T1CON<0>)

- TMR1IE bit (PIE1<0>) must be set

- PEIE bit (INTCON<6>) must be set

The device will wake-up on an overflow. If the GIE bit (INTCON<7>) is set, the device will wake-up and jump to the Interrupt Service Routine on an overflow.

| IADEL ( | ABEE 5-1. REGISTERS ASSOCIATED WITH HIMERTAS A HIMER COUNTER                     |         |              |              |               |             |           |            |        |               |      |      |                       |

|---------|----------------------------------------------------------------------------------|---------|--------------|--------------|---------------|-------------|-----------|------------|--------|---------------|------|------|-----------------------|

| Address | Name                                                                             | Bit 7   | Bit 6        | Bit 5        | Bit 4         | Bit 3       | Bit 2     | Bit 1      | Bit 0  | Value<br>POR, |      | allo | e on<br>other<br>sets |

| 0Bh/8Bh | INTCON                                                                           | GIE     | PEIE         | T0IE         | INTE          | GPIE        | T0IF      | INTF       | GPIF   | 0000          | 0000 | 0000 | 000u                  |

| 0Ch     | PIR1                                                                             | EEIF    | ADIF         | _            | —             | CMIF        | —         | _          | TMR1IF | 00            | 00   | 00   | 00                    |

| 0Eh     | TMR1L                                                                            | Holding | g Register f | or the Least | t Significant | Byte of the | 16-bit TM | R1 Registe | r      | XXXX          | XXXX | uuuu | uuuu                  |

| 0Fh     | TMR1H Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |         |              |              |               |             |           |            |        | XXXX          | XXXX | uuuu | uuuu                  |

| 10h     | T1CON                                                                            | _       | TMR1GE       | T1CKPS1      | T1CKPS0       | T1OSCEN     | T1SYNC    | TMR1CS     | TMR10N | -000          | 0000 | -uuu | uuuu                  |

| 8Ch     | PIE1                                                                             | EEIE    | ADIE         | _            | _             | CMIE        | _         | _          | TMR1IE | 00            | 00   | 00   | 00                    |

TABLE 5-1: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

\_ \_ \_ \_ \_ \_

- -----

| REGISTER 7-     | 1: ADCO                                                      | N0: A/D CON                                             | TROL REG       | ISTER (ADD       | RESS: 1Fh)      |                                    |       |

|-----------------|--------------------------------------------------------------|---------------------------------------------------------|----------------|------------------|-----------------|------------------------------------|-------|

| R/W-0           | R/W-0                                                        | U-0                                                     | U-0            | R/W-0            | R/W-0           | R/W-0                              | R/W-0 |

| ADFM            | VCFG                                                         | —                                                       |                | CHS1             | CHS0            | GO/DONE                            | ADON  |

| bit 7           |                                                              |                                                         |                |                  |                 |                                    | bit C |

| Legend:         |                                                              |                                                         |                |                  |                 |                                    |       |

| R = Readable b  | bit                                                          | W = Writable I                                          | oit            | U = Unimpler     | mented bit, rea | d as '0'                           |       |

| -n = Value at P | OR                                                           | '1' = Bit is set                                        |                | '0' = Bit is cle | eared           | x = Bit is unkno                   | own   |

|                 |                                                              |                                                         |                |                  |                 |                                    |       |

| bit 7           | ADFM: A/D R<br>1 = Right just<br>0 = Left justifi            |                                                         | Select bit     |                  |                 |                                    |       |

| bit 6           | VCFG: Voltag<br>1 = VREF pin<br>0 = VDD                      | e Reference bi                                          | t              |                  |                 |                                    |       |

| bit 5-4         | Unimplemen                                                   | ted: Read as 'o                                         | )'             |                  |                 |                                    |       |

| bit 3-2         | CHS1:CHS0:                                                   | Analog Chann                                            | el Select bits |                  |                 |                                    |       |

|                 | 00 = Channel<br>01 = Channel<br>10 = Channel<br>11 = Channel | 01 (AN1)<br>02 (AN2)                                    |                |                  |                 |                                    |       |

| bit 1           | GO/DONE: A                                                   | /D Conversion                                           | Status bit     |                  |                 |                                    |       |

|                 | This bit is                                                  | ersion cycle in p<br>automatically c<br>ersion complete | leared by ha   | rdware when th   |                 | version cycle.<br>ion has complete | ed.   |

| bit 0           | ADON: A/D C                                                  | conversion State                                        | us bit         |                  |                 |                                    |       |

|                 |                                                              | erter module is<br>erter is shut-off                    |                | es no operating  | g current       |                                    |       |

### 8.1 EEADR

The EEADR register can address up to a maximum of 128 bytes of data EEPROM. Only seven of the eight bits in the register (EEADR<6:0>) are required. The MSb (bit 7) is ignored.

The upper bit should always be '0' to remain upward compatible with devices that have more data EEPROM memory.

### 8.2 EECON1 and EECON2 Registers

EECON1 is the control register with four low-order bits physically implemented. The upper four bits are non-implemented and read as '0's.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion

of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit, clear it, and rewrite the location. The data and address will be cleared, therefore, the EEDATA and EEADR registers will need to be re-initialized.

Interrupt flag bit EEIF in the PIR1 register is set when write is complete. This bit must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence.

| REGISTER 0- | ). LLCO |     | CONTROL | REGISTER | (ADDRESS. 3 |       |       |

|-------------|---------|-----|---------|----------|-------------|-------|-------|

| U-0         | U-0     | U-0 | U-0     | R/W-x    | R/W-0       | R/S-0 | R/S-0 |

| —           |         | _   | —       | WRERR    | WREN        | WR    | RD    |

| bit 7       |         |     |         |          |             |       | bit 0 |

### **REGISTER 8-3: EECON1: EEPROM CONTROL REGISTER (ADDRESS: 9Ch)**

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                                                           |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | WRERR: EEPROM Error Flag bit                                                                                                                                                         |

|         | <ul> <li>1 = A write operation is prematurely terminated (any MCLR Reset, any WDT Reset during normal operation or BOD detect)</li> <li>0 = The write operation completed</li> </ul> |

| bit 2   | WREN: EEPROM Write Enable bit                                                                                                                                                        |

|         | 1 = Allows write cycles                                                                                                                                                              |

|         | 0 = Inhibits write to the data EEPROM                                                                                                                                                |

| bit 1   | WR: Write Control bit                                                                                                                                                                |

|         | <ul> <li>1 = Initiates a write cycle (The bit is cleared by hardware once write is complete. The WR bit can only<br/>be set, not cleared, in software.)</li> </ul>                   |

|         | 0 = Write cycle to the data EEPROM is complete                                                                                                                                       |

| bit 0   | RD: Read Control bit                                                                                                                                                                 |

|         | <ul> <li>1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bit can only<br/>be set, not cleared, in software).</li> </ul>                        |

|         | 0 = Does not initiate an EEPROM read                                                                                                                                                 |

### 8.7 Data EEPROM Operation During Code Protect

Data memory can be code protected by programming the CPD bit to '0'.

When the data memory is code protected, the CPU is able to read and write data to the data EEPROM. It is recommended to code protect the program memory when code protecting data memory. This prevents anyone from programming zeroes over the existing code (which will execute as NOPS) to reach an added routine, programmed in unused program memory, which outputs the contents of data memory. Programming unused locations to '0' will also help prevent data memory code protection from becoming breached.

| Address | Name                                | Bit 7  | Bit 6                  | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Valu<br>POR, | e on | Value<br>oth<br>Res | ner  |

|---------|-------------------------------------|--------|------------------------|------------|-------|-------|-------|-------|--------|--------------|------|---------------------|------|

| 0Ch     | PIR1                                | EEIF   | ADIF                   | _          |       | CMIF  | _     |       | TMR1IF | 00           | 00   | 00                  | 00   |

| 9Ah     | EEDATA                              | EEPROM | I Data Re              | gister     |       |       |       |       |        | 0000         | 0000 | 0000                | 0000 |

| 9Bh     | 9Bh EEADR — EEPROM Address Register |        |                        |            |       |       |       |       | -000   | 0000         | -000 | 0000                |      |

| 9Ch     | EECON1                              | _      | — — — WRERR WREN WR RD |            |       |       |       |       |        | x000         |      | q000                |      |

| 9Dh     | EECON2 <sup>(1)</sup>               | EEPROM | I Control F            | Register 2 |       |       |       |       |        |              |      |                     |      |

### TABLE 8-1: REGISTERS/BITS ASSOCIATED WITH DATA EEPROM

$\label{eq:logarder} \mbox{Legend: $x$ = unknown, $u$ = unchanged, - = unimplemented read as `0', $q$ = value depends upon condition. Shaded cells are not used by data EEPROM module.}$

**Note 1:** EECON2 is not a physical register.

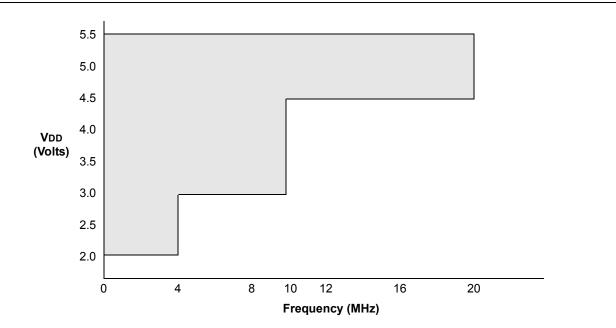

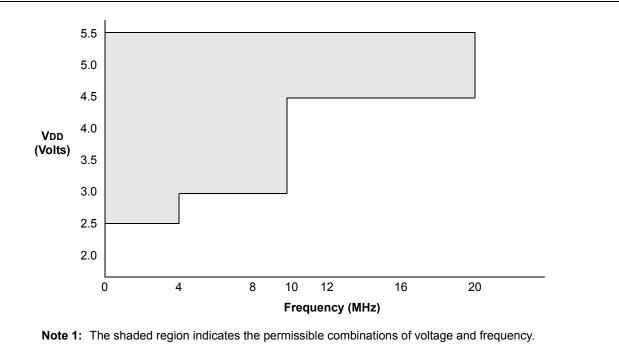

**Note 1:** The shaded region indicates the permissible combinations of voltage and frequency.

### 12.6 DC Characteristics: PIC12F629/675-I (Industrial), PIC12F629/675-E (Extended)

| DC CHA       | ARACT | ERISTICS                             |                |       | -40°C ≤ 1 | ГА ≤ +8 | <b>s otherwise stated)</b><br>5°C for industrial<br>25°C for extended |

|--------------|-------|--------------------------------------|----------------|-------|-----------|---------|-----------------------------------------------------------------------|

| Param<br>No. | Sym   | Characteristic                       | Min            | Тур†  | Max       | Units   | Conditions                                                            |

|              |       | Input Low Voltage                    |                |       |           |         |                                                                       |

|              | VIL   | I/O ports                            |                |       |           |         |                                                                       |

| D030         |       | with TTL buffer                      | Vss            | —     | 0.8       | V       | $4.5V \le VDD \le 5.5V$                                               |

| D030A        |       |                                      | Vss            |       | 0.15 Vdd  | V       | Otherwise                                                             |

| D031         |       | with Schmitt Trigger buffer          | Vss            | _     | 0.2 Vdd   | V       | Entire range                                                          |

| D032         |       | MCLR, OSC1 (RC mode)                 | Vss            |       | 0.2 Vdd   | V       |                                                                       |

| D033         |       | OSC1 (XT and LP modes)               | Vss            |       | 0.3       | V       | (Note 1)                                                              |

| D033A        |       | OSC1 (HS mode)                       | Vss            | _     | 0.3 Vdd   | V       | (Note 1)                                                              |

|              |       | Input High Voltage                   |                |       |           |         |                                                                       |

|              | Vін   | I/O ports                            |                | _     |           |         |                                                                       |

| D040         |       | with TTL buffer                      | 2.0            |       | Vdd       | V       | $4.5V \le VDD \le 5.5V$                                               |

| D040A        |       |                                      | (0.25 VDD+0.8) |       | Vdd       | V       | otherwise                                                             |

| D041         |       | with Schmitt Trigger buffer          | 0.8 Vdd        | —     | Vdd       |         | entire range                                                          |

| D042         |       | MCLR                                 | 0.8 Vdd        |       | Vdd       | V       |                                                                       |

| D043         |       | OSC1 (XT and LP modes)               | 1.6            |       | Vdd       | V       | (Note 1)                                                              |

| D043A        |       | OSC1 (HS mode)                       | 0.7 Vdd        | —     | Vdd       | V       | (Note 1)                                                              |

| D043B        |       | OSC1 (RC mode)                       | 0.9 Vdd        | —     | Vdd       | V       |                                                                       |

| D070         | Ipur  | GPIO Weak Pull-up Current            | 50*            | 250   | 400*      | μA      | VDD = 5.0V, VPIN = VSS                                                |

|              |       | Input Leakage Current <sup>(3)</sup> |                |       |           |         |                                                                       |

| D060         | lı∟   | I/O ports                            | —              | ± 0.1 | ± 1       | μA      | $Vss \le VPIN \le VDD,$ Pin at high-impedance                         |

| D060A        |       | Analog inputs                        | —              | ± 0.1 | ± 1       | μA      | $VSS \le VPIN \le VDD$                                                |

| D060B        |       | VREF                                 | —              | ± 0.1 | ± 1       | μA      | $VSS \le VPIN \le VDD$                                                |

| D061         |       | MCLR <sup>(2)</sup>                  | —              | ± 0.1 | ± 5       | μA      | $VSS \le VPIN \le VDD$                                                |

| D063         |       | OSC1                                 | —              | ± 0.1 | ± 5       | μA      | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration           |

|              |       | Output Low Voltage                   |                |       |           |         |                                                                       |

| D080         | Vol   | I/O ports                            | —              | —     | 0.6       | V       | IOL = 8.5 mA, VDD = 4.5V (Ind.)                                       |

| D083         |       | OSC2/CLKOUT (RC mode)                | —              | —     | 0.6       | V       | IOL = 1.6 mA, VDD = 4.5V (Ind.)<br>IOL = 1.2 mA, VDD = 4.5V (Ext.)    |

|              |       | Output High Voltage                  |                |       |           |         |                                                                       |

| D090         | Vон   | I/O ports                            | Vdd - 0.7      | —     | —         | V       | IOH = -3.0 mA, VDD = 4.5V (Ind.)                                      |

| D092         |       | OSC2/CLKOUT (RC mode)                | Vdd - 0.7      | _     | —         | V       | ІОН = -1.3 mA, VDD = 4.5V (Ind.)<br>ІОН = -1.0 mA, VDD = 4.5V (Ext.)  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

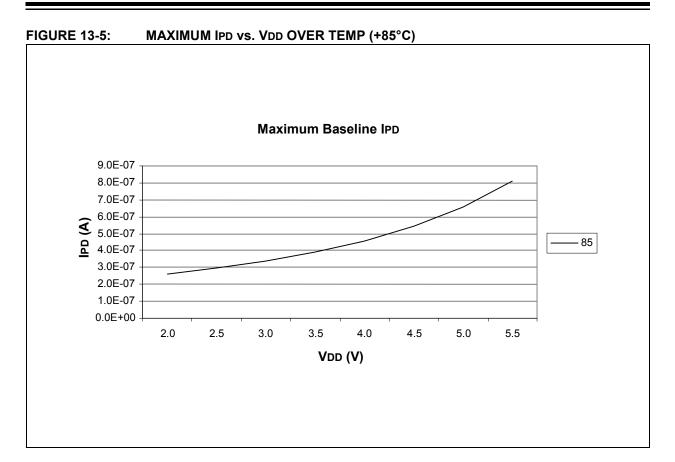

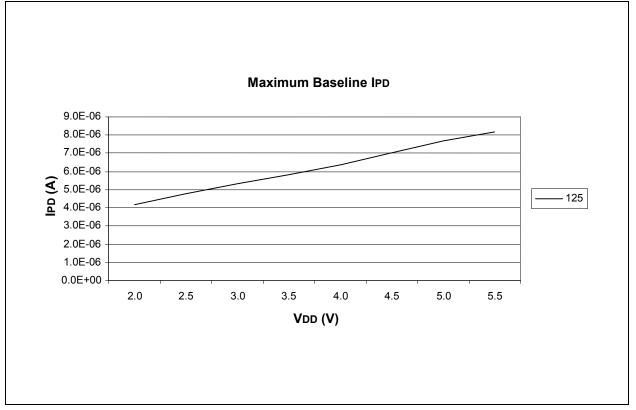

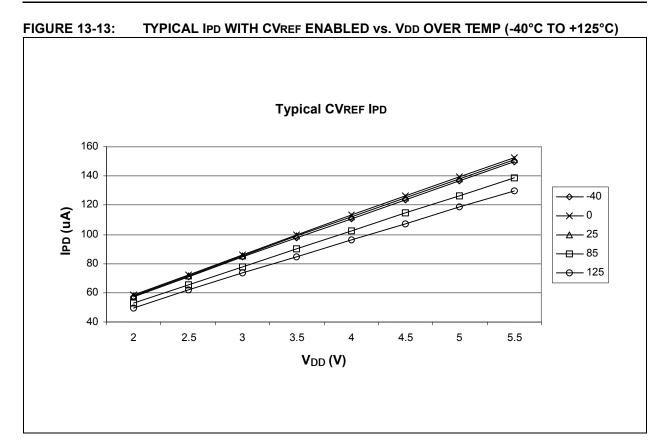

FIGURE 13-6: MAXIMUM IPD vs. VDD OVER TEMP (+125°C)

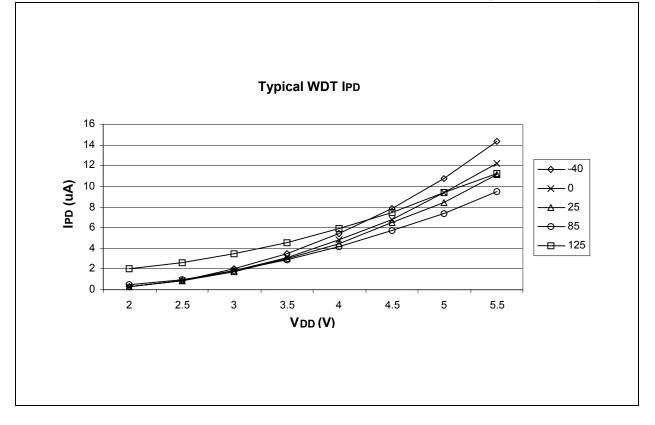

FIGURE 13-14: TYPICAL IPD WITH WDT ENABLED vs. VDD OVER TEMP (-40°C TO +125°C)

### 14.2 Package Details

The following sections give the technical details of the packages.

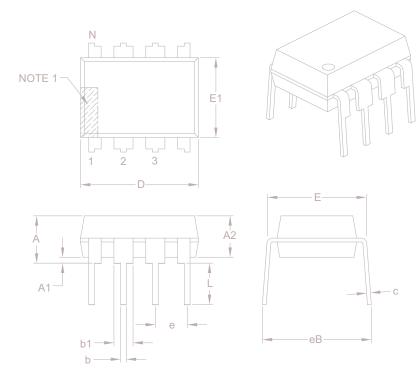

### 8-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            |      | INCHES   |      |

|----------------------------|------------------|------|----------|------|

|                            | Dimension Limits | MIN  | NOM      | MAX  |

| Number of Pins             | N                |      | 8        |      |

| Pitch                      | e                |      | .100 BSC |      |

| Top to Seating Plane       | A                | -    | -        | .210 |

| Molded Package Thickness   | A2               | .115 | .130     | .195 |

| Base to Seating Plane      | A1               | .015 | -        | -    |

| Shoulder to Shoulder Width | E                | .290 | .310     | .325 |

| Molded Package Width       | E1               | .240 | .250     | .280 |

| Overall Length             | D                | .348 | .365     | .400 |

| Tip to Seating Plane       | L                | .115 | .130     | .150 |

| Lead Thickness             | С                | .008 | .010     | .015 |

| Upper Lead Width           | b1               | .040 | .060     | .070 |

| Lower Lead Width           | b                | .014 | .018     | .022 |

| Overall Row Spacing §      | eB               | -    | -        | .430 |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located with the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-018B

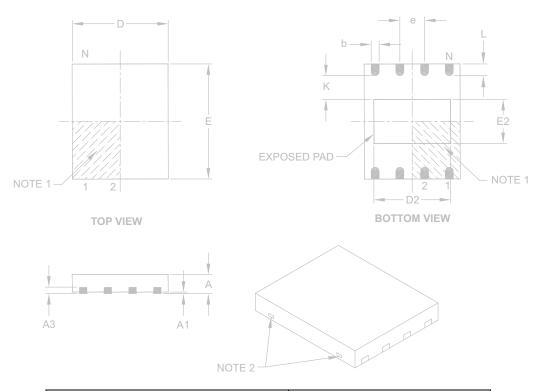

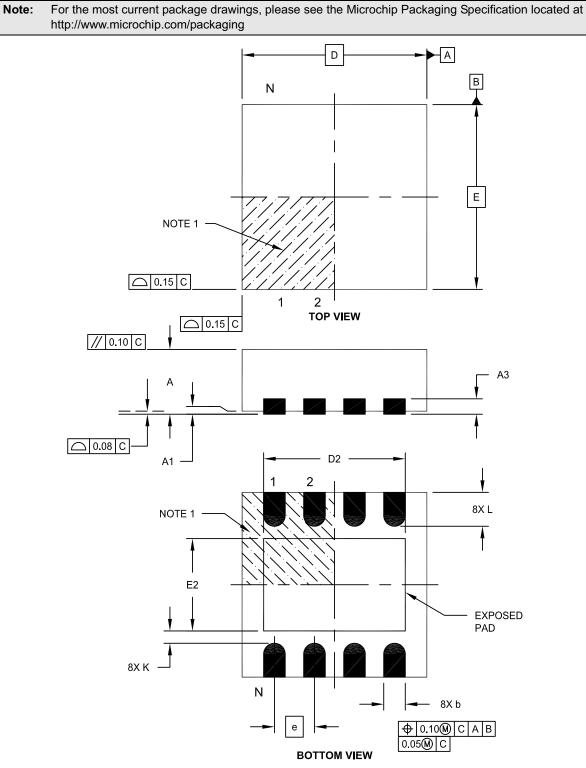

### 8-Lead Plastic Dual Flat, No Lead Package (MF) – 6x5 mm Body [DFN-S]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units        |          | MILLIMETERS |      |  |  |

|------------------------|--------------|----------|-------------|------|--|--|

| Dimer                  | nsion Limits | MIN      | NOM         | MAX  |  |  |

| Number of Pins         | Ν            |          | 8           |      |  |  |

| Pitch                  | е            |          | 1.27 BSC    |      |  |  |

| Overall Height         | Α            | 0.80     | 0.85        | 1.00 |  |  |

| Standoff               | A1           | 0.00     | 0.01        | 0.05 |  |  |

| Contact Thickness      | A3           | 0.20 REF |             |      |  |  |

| Overall Length         | D            | 5.00 BSC |             |      |  |  |

| Overall Width          | E            |          | 6.00 BSC    |      |  |  |

| Exposed Pad Length     | D2           | 3.90     | 4.00        | 4.10 |  |  |

| Exposed Pad Width      | E2           | 2.20     | 2.30        | 2.40 |  |  |

| Contact Width          | b            | 0.35     | 0.40        | 0.48 |  |  |

| Contact Length         | L            | 0.50     | 0.60        | 0.75 |  |  |

| Contact-to-Exposed Pad | K            | 0.20     | -           | -    |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-122B

### 8-Lead Plastic Dual Flat, No Lead Package (MD) – 4x4x0.9 mm Body [DFN]

Microchip Technology Drawing C04-131E Sheet 1 of 2

### APPENDIX A: DATA SHEET REVISION HISTORY

### **Revision A**

This is a new data sheet.

### **Revision B**

Added characterization graphs.

Updated specifications.

Added notes to indicate Microchip programmers maintain all Calibration bits to factory settings and the PIC12F675 ANSEL register must be initialized to configure pins as digital I/O.

Updated MLF-S package name to DFN-S.

### **Revision C**

### **Revision D (01/2007)**

Updated Package Drawings; Replace PICmicro with PIC; Revised Product ID example (b).

### Revision E (03/2007)

Replaced Package Drawings (Rev. AM); Replaced Development Support Section.

### **Revision F (09/2009)**

Updated Registers to new format; Added information to the "Package Marking Information" (8-Lead DFN) and "Package Details" sections (8-Lead Dual Flat, No Lead Package (MD) 4X4X0.9 mm Body (DFN)); Added Land Patterns for SOIC (SN) and DFN-S (MF) packages; Updated Register 3-2; Added MD Package to the Product identification System chapter; Other minor corrections.

#### **Revision G (03/2010)**

Updated the Instruction Set Summary section, adding pages 76 and 77.

### APPENDIX B: DEVICE DIFFERENCES

The differences between the PIC12F629/675 devices listed in this data sheet are shown in Table B-1.

TABLE B-1: DEVICE DIFFERENCES

| Feature | PIC12F629 | PIC12F675 |

|---------|-----------|-----------|

| A/D     | No        | Yes       |

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com