# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorPICCore Size8-BitSpeed20MHzConnectivity-PeripheralsPOR, WDTNumber of I/O5Porgam Memory Size1.75KB (1K × 14)Program Memory TypeFLASHERPOM Size128 × 8Voltage - Supply (Voc/Vd)2 ~ 5.5VData Converters.Organt Memory TypeInternalOrgant Memory Type-Back Once-Program Memory Type0.5 × 5.5VData Converters.Oscillator TypeInternalMunting TypeSurface MontPackage / CaseSurface MontPackage / Case8.10FN Exposed PadSupplier Pervice8.10FN Exposed PadPurchase URLMonter, eschlorupt-technology/pic12/629-Li-mf |                            |                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------|

| Core Size8-BitCore Size8-BitSpeed20MHzConnectivity-PeripheralsPOR, WDTNumber of I/O5Program Memory Size1.75KB (1K x 14)Program Memory TypeFLASHEEPROM Size128 x 8RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-DFN-S (6x5)                                                                                                                                                                                            | Product Status             | Active                                                                    |

| Speed20MHzConnectivity-PeripheralsPOR, WDTNumber of I/O5Program Memory Size1.75KB (1K × 14)Program Memory TypeFLASHEEPROM Size128 × 8RAM Size64 × 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-DFN-S (6x5)                                                                                                                                                                                                                        | Core Processor             | PIC                                                                       |

| Connectivity-Connectivity-PeripheralsPOR, WDTNumber of I/O5Program Memory Size1.75KB (1K x 14)Program Memory TypeFLASHEEPROM Size128 x 8RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VDFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                            | Core Size                  | 8-Bit                                                                     |

| PeripheralsPOR, WDTNumber of I/O5Program Memory Size1.75KB (1K x 14)Program Memory TypeFLASHEEPROM Size128 x 8RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type8-VDFN Exposed PadSuppler Device Package8-DFN-S (6x5)                                                                                                                                                                                                                                  | Speed                      | 20MHz                                                                     |

| Number of I/O5Program Memory Size1.75KB (1K x 14)Program Memory TypeFLASHEEPROM Size128 x 8RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VDFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                                                                         | Connectivity               | -                                                                         |

| Program Memory Size1.75KB (1K x 14)Program Memory TypeFLASHFLPROM Size128 x 8RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VDFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                                                                                       | Peripherals                | POR, WDT                                                                  |

| Program Memory TypeFLASHEEPROM Size128 x 8RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-DFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                                                                                                                           | Number of I/O              | 5                                                                         |

| EEPROM Size128 x 8RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VDFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                  | Program Memory Size        | 1.75KB (1K x 14)                                                          |

| RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VDFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                    | Program Memory Type        | FLASH                                                                     |

| Voltage - Supply (Vcc/Vdd)2V ~ 5.5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VDFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                  | EEPROM Size                | 128 x 8                                                                   |

| Data Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VDFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                     | RAM Size                   | 64 x 8                                                                    |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VDFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                     | Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Operating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case8-VDFN Exposed PadSupplier Device Package8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                            | Data Converters            | -                                                                         |

| Mounting Type     Surface Mount       Package / Case     8-VDFN Exposed Pad       Supplier Device Package     8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                                     | Oscillator Type            | Internal                                                                  |

| Package / Case     8-VDFN Exposed Pad       Supplier Device Package     8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Supplier Device Package 8-DFN-S (6x5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Mounting Type              | Surface Mount                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Package / Case             | 8-VDFN Exposed Pad                                                        |

| Purchase URL https://www.e-xfl.com/product-detail/microchip-technology/pic12f629t-i-mf                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Supplier Device Package    | 8-DFN-S (6x5)                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f629t-i-mf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 MEMORY ORGANIZATION

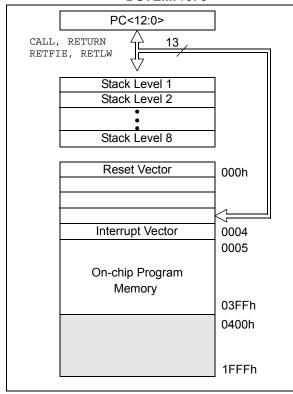

### 2.1 Program Memory Organization

The PIC12F629/675 devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 1K x 14 (0000h-03FFh) for the PIC12F629/675 devices is physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 1K x 14 space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 2-1).

#### FIGURE 2-1: PROGRAM MEMORY MAP AND STACK FOR THE DSTEMP/675

## 2.2 Data Memory Organization

The data memory (see Figure 2-2) is partitioned into two banks, which contain the General Purpose Registers and the Special Function Registers. The Special Function Registers are located in the first 32 locations of each bank. Register locations 20h-5Fh are General Purpose Registers, implemented as static RAM and are mapped across both banks. All other RAM is unimplemented and returns '0' when read. RP0 (STATUS<5>) is the bank select bit.

- RP0 = 0 Bank 0 is selected

- RP0 = 1 Bank 1 is selected

| Note: | The IRP and RP1 bits STATUS<7:6> are     |

|-------|------------------------------------------|

|       | reserved and should always be maintained |

|       | as '0's.                                 |

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 64 x 8 in the PIC12F629/675 devices. Each register is accessed, either directly or indirectly, through the File Select Register FSR (see Section 2.4 "Indirect Addressing, INDF and FSR Registers").

#### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, GPIO port change and external GP2/INT pin interrupts.

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER (ADDRESS: 0Bh OR 8Bh)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | PEIE  | TOIE  | INTE  | GPIE  | T0IF  | INTF  | GPIF  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | GIE: Global Interrupt Enable bit                                                                       |

|---------|--------------------------------------------------------------------------------------------------------|

|         | 1 = Enables all unmasked interrupts                                                                    |

|         | 0 = Disables all interrupts                                                                            |

| bit 6   | PEIE: Peripheral Interrupt Enable bit                                                                  |

|         | 1 = Enables all unmasked peripheral interrupts                                                         |

|         | 0 = Disables all peripheral interrupts                                                                 |

| bit 5   | TOIE: TMR0 Overflow Interrupt Enable bit                                                               |

|         | 1 = Enables the TMR0 interrupt                                                                         |

|         | 0 = Disables the TMR0 interrupt                                                                        |

| bit 4   | INTE: GP2/INT External Interrupt Enable bit                                                            |

|         | 1 = Enables the GP2/INT external interrupt                                                             |

|         | 0 = Disables the GP2/INT external interrupt                                                            |

| bit 3   | GPIE: Port Change Interrupt Enable bit <sup>(1)</sup>                                                  |

|         | 1 = Enables the GPIO port change interrupt                                                             |

|         | 0 = Disables the GPIO port change interrupt                                                            |

| bit 2   | <b>T0IF:</b> TMR0 Overflow Interrupt Flag bit <sup>(2)</sup>                                           |

|         | 1 = TMR0 register has overflowed (must be cleared in software)                                         |

|         | 0 = TMR0 register did not overflow                                                                     |

| bit 1   | INTF: GP2/INT External Interrupt Flag bit                                                              |

|         | 1 = The GP2/INT external interrupt occurred (must be cleared in software)                              |

|         | 0 = The GP2/INT external interrupt did not occur                                                       |

| bit 0   | GPIF: Port Change Interrupt Flag bit                                                                   |

|         | 1 = When at least one of the GP5:GP0 pins changed state (must be cleared in software)                  |

|         | 0 = None of the GP5:GP0 pins have changed state                                                        |

| Note 1: | IOC register must also be enabled to enable an interrupt-on-change.                                    |

| 0.      | TOLE bit is not when TIMERO calls are TIMERO is were served an Depart and should be initialized before |

2: T0IF bit is set when TIMER0 rolls over. TIMER0 is unchanged on Reset and should be initialized before clearing T0IF bit.

# 3.0 GPIO PORT

There are as many as six general purpose I/O pins available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

| Note: | Additional information on I/O ports may be        |

|-------|---------------------------------------------------|

|       | found in the PIC <sup>®</sup> Mid-Range Reference |

|       | Manual, (DS33023).                                |

## 3.1 GPIO and the TRISIO Registers

GPIO is an 6-bit wide, bidirectional port. The corresponding data direction register is TRISIO. Setting a TRISIO bit (= 1) will make the corresponding GPIO pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISIO bit (= 0) will make the corresponding GPIO pin an output (i.e., put the contents of the output latch on the selected pin). The exception is GP3, which is input-only and its TRISIO bit will always read as '1'. Example 3-1 shows how to initialize GPIO.

Reading the GPIO register reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified, and then written to the PORT data latch. GP3 reads '0' when MCLREN = 1.

The TRISIO register controls the direction of the GP pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISIO

register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

| N | lote: | The ANSEL (9Fh) and CMCON (19h)              |

|---|-------|----------------------------------------------|

|   |       | registers (9Fh) must be initialized to       |

|   |       | configure an analog channel as a digital     |

|   |       | input. Pins configured as analog inputs will |

|   |       | read '0'. The ANSEL register is defined for  |

|   |       | the PIC12F675.                               |

#### EXAMPLE 3-1: INITIALIZING GPIO

| BCF   | STATUS, RPO | ;Bank 0                |

|-------|-------------|------------------------|

| CLRF  | GPIO        | ;Init GPIO             |

| MOVLW | 07h         | ;Set GP<2:0> to        |

| MOVWF | CMCON       | ;digital IO            |

| BSF   | STATUS, RPO | ;Bank 1                |

| CLRF  | ANSEL       | ;Digital I/O           |

| MOVLW | 0Ch         | ;Set GP<3:2> as inputs |

| MOVWF | TRISIO      | ;and set GP<5:4,1:0>   |

|       |             | ;as outputs            |

|       |             |                        |

# 3.2 Additional Pin Functions

Every GPIO pin on the PIC12F629/675 has an interrupt-on-change option and every GPIO pin, except GP3, has a weak pull-up option. The next two sections describe these functions.

### 3.2.1 WEAK PULL-UP

Each of the GPIO pins, except GP3, has an individually configurable weak internal pull-up. Control bits WPUx enable or disable each pull-up. Refer to Register 3-3. Each weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset by the GPPU bit (OPTION<7>).

|       |     |       |       | ,     |       |       |       |

|-------|-----|-------|-------|-------|-------|-------|-------|

| U-0   | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

| —     | _   | GPIO5 | GPIO4 | GPIO3 | GPIO2 | GPIO1 | GPIO0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

|       |     |       |       |       |       |       |       |

REGISTER 3-1: GPIO: GPIO REGISTER (ADDRESS: 05h)

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **GPIO<5:0>**: General Purpose I/O pin 1 = Port pin is >VIH 0 = Port pin is <VIL

| U-0                                               | U-0                                                                                                                   | R/W-1                                                                                                  | R/W-1                               | R-1                  | R/W-1            | R/W-1              | R/W-1   |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------|------------------|--------------------|---------|

| _                                                 |                                                                                                                       | TRISI05                                                                                                | TRISIO4                             | TRISIO3              | TRISIO2          | TRISIO1            | TRISI00 |

| bit 7                                             | ·                                                                                                                     |                                                                                                        |                                     |                      |                  |                    | bit     |

| Legend:                                           |                                                                                                                       |                                                                                                        |                                     |                      |                  |                    |         |

| R = Readable                                      | e bit                                                                                                                 | W = Writable                                                                                           | bit                                 | U = Unimplen         | nented bit, read | d as '0'           |         |

| -n = Value at                                     | POR                                                                                                                   | '1' = Bit is set                                                                                       |                                     | '0' = Bit is clea    | ared             | x = Bit is unkr    | iown    |

| LH 7 0                                            |                                                                                                                       | ta di Danadara (i                                                                                      | .,                                  |                      |                  |                    |         |

| bit 7-6                                           | -                                                                                                                     | ted: Read as '                                                                                         |                                     | ata Cantral hit      |                  |                    |         |

| bit 5-0                                           |                                                                                                                       | : General Purp<br>configured as                                                                        |                                     |                      |                  |                    |         |

|                                                   |                                                                                                                       | configured as                                                                                          |                                     | aleu)                |                  |                    |         |

| Note: TR                                          | RISIO<3> always                                                                                                       | •                                                                                                      | anouput                             |                      |                  |                    |         |

|                                                   |                                                                                                                       |                                                                                                        |                                     |                      |                  |                    |         |

| REGISTER                                          | 3-3: WPU:                                                                                                             | WEAK PULL                                                                                              | -UP REGIS                           | FER (ADDRE           | SS: 95h)         |                    |         |

| U-0                                               | U-0                                                                                                                   | R/W-1                                                                                                  | R/W-1                               | U-0                  | R/W-1            | R/W-1              | R/W-1   |

|                                                   |                                                                                                                       | WPU5                                                                                                   | WPU4                                |                      | WPU2             | WPU1               | WPU0    |

| bit 7                                             |                                                                                                                       |                                                                                                        |                                     |                      |                  |                    | bit     |

|                                                   |                                                                                                                       |                                                                                                        |                                     |                      |                  |                    |         |

| Legend:                                           |                                                                                                                       |                                                                                                        |                                     |                      |                  |                    |         |

| R = Readable                                      | e bit                                                                                                                 | W = Writable                                                                                           | bit                                 | U = Unimplen         | nented bit, read | d as '0'           |         |

| -n = Value at                                     | POR                                                                                                                   | '1' = Bit is set                                                                                       |                                     | '0' = Bit is cleared |                  | x = Bit is unknown |         |

|                                                   |                                                                                                                       |                                                                                                        |                                     |                      |                  |                    |         |

|                                                   | -                                                                                                                     | ted: Read as '                                                                                         |                                     |                      |                  |                    |         |

| bit 7-6                                           | 14/0011 .00 4. 1                                                                                                      | Noak Dull up D                                                                                         | onistor hit                         |                      |                  |                    |         |

|                                                   | WPU<5:4>: \                                                                                                           | •                                                                                                      | cylater bit                         |                      |                  |                    |         |

| bit 7-6<br>bit 5-4                                | 1 = Pull-up er                                                                                                        | nabled                                                                                                 |                                     |                      |                  |                    |         |

| bit 5-4                                           | 1 = Pull-up er<br>0 = Pull-up di                                                                                      | nabled<br>sabled                                                                                       |                                     |                      |                  |                    |         |

| bit 5-4<br>bit 3                                  | 1 = Pull-up er<br>0 = Pull-up di<br><b>Unimplemen</b>                                                                 | nabled<br>sabled<br>I <b>ted:</b> Read as 'i                                                           | ס'                                  |                      |                  |                    |         |

| bit 5-4<br>bit 3                                  | 1 = Pull-up er<br>0 = Pull-up di<br>Unimplemen<br>WPU<2:0>: V                                                         | nabled<br>sabled<br>i <b>ted:</b> Read as 'i<br>Neak Pull-up R                                         | ס'                                  |                      |                  |                    |         |

| bit 5-4<br>bit 3                                  | 1 = Pull-up er<br>0 = Pull-up di<br>Unimplemen<br>WPU<2:0>: V<br>1 = Pull-up er                                       | nabled<br>sabled<br>I <b>ted:</b> Read as 'i<br>Neak Pull-up R<br>nabled                               | ס'                                  |                      |                  |                    |         |

| bit 5-4<br>bit 3<br>bit 2-0                       | 1 = Pull-up er<br>0 = Pull-up di<br><b>Unimplemen</b><br><b>WPU&lt;2:0&gt;:</b> V<br>1 = Pull-up er<br>0 = Pull-up di | nabled<br>sabled<br>I <b>ted:</b> Read as f<br>Weak Pull-up R<br>nabled<br>sabled                      | ⊃'<br>egister bit                   |                      |                  |                    |         |

| bit 5-4<br>bit 3<br>bit 2-0<br><b>Note 1:</b> Glo | 1 = Pull-up er<br>0 = Pull-up di<br>Unimplemen<br>WPU<2:0>: V<br>1 = Pull-up er                                       | nabled<br>sabled<br>I <b>ted:</b> Read as fi<br>Neak Pull-up R<br>nabled<br>sabled<br>it be enabled fo | י<br>egister bit<br>r individual pu | •                    |                  |                    |         |

# REGISTER 3-2: TRISIO: GPIO TRI-STATE REGISTER (ADDRESS: 85h)

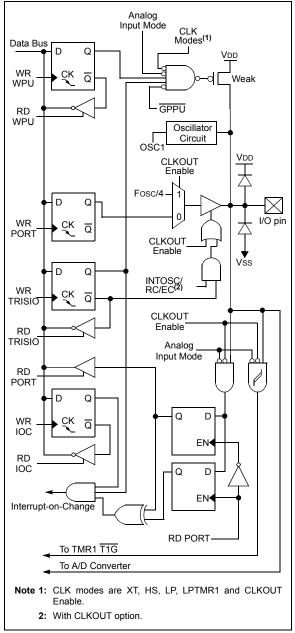

#### GP4/AN3/T1G/OSC2/CLKOUT 3.3.5

Figure 3-4 shows the diagram for this pin. The GP4 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the A/D (PIC12F675 only)

- a TMR1 gate input

- · a crystal/resonator connection

- · a clock output

#### FIGURE 3-4: **BLOCK DIAGRAM OF GP4**

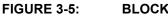

#### 3.3.6 GP5/T1CKI/OSC1/CLKIN

Figure 3-5 shows the diagram for this pin. The GP5 pin is configurable to function as one of the following:

- a general purpose I/O

- · a TMR1 clock input

- · a crystal/resonator connection

- · a clock input

#### **BLOCK DIAGRAM OF GP5**

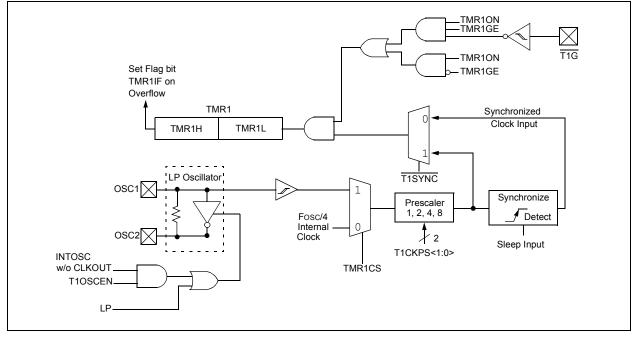

# 5.0 TIMER1 MODULE WITH GATE CONTROL

The PIC12F629/675 devices have a 16-bit timer. Figure 5-1 shows the basic block diagram of the Timer1 module. Timer1 has the following features:

- 16-bit timer/counter (TMR1H:TMR1L)

- · Readable and writable

- Internal or external clock selection

- Synchronous or asynchronous operation

- Interrupt on overflow from FFFFh to 0000h

- Wake-up upon overflow (Asynchronous mode)

- Optional external enable input (T1G)

- · Optional LP oscillator

#### FIGURE 5-1: TIMER1 BLOCK DIAGRAM

The Timer1 Control register (T1CON), shown in Register 5.1, is used to enable/disable Timer1 and select the various features of the Timer1 module.

Note: Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

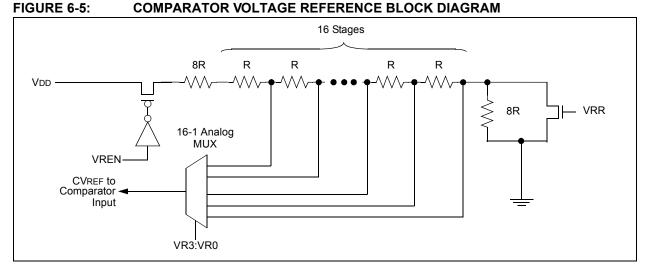

### 6.5 Comparator Reference

The comparator module also allows the selection of an internally generated voltage reference for one of the comparator inputs. The internal reference signal is used for four of the eight Comparator modes. The VRCON register, Register 6-2, controls the voltage reference module shown in Figure 6-5.

# 6.5.1 CONFIGURING THE VOLTAGE REFERENCE

The voltage reference can output 32 distinct voltage levels, 16 in a high range and 16 in a low range.

The following equations determine the output voltages:

VRR = 1 (low range): CVREF = (VR3:VR0 / 24) x VDD VRR = 0 (high range): CVREF = (VDD / 4) + (VR3:VR0 x VDD / 32)

### 6.5.2 VOLTAGE REFERENCE ACCURACY/ERROR

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 6-5) keep CVREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the Comparator Voltage Reference can be found in **Section 12.0 "Electrical Specifications"**.

### 6.6 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output is ensured to have a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (Table 12-7).

# 6.7 Operation During Sleep

Both the comparator and voltage reference, if enabled before entering Sleep mode, remain active during Sleep. This results in higher Sleep currents than shown in the power-down specifications. The additional current consumed by the comparator and the voltage reference is shown separately in the specifications. To minimize power consumption while in Sleep mode, turn off the comparator, CM2:CM0 = 111, and voltage refeence, VRCON<7> = 0. While the comparator is enabled during Sleep, an interrupt will wake-up the device. If the device wakes up from Sleep, the contents of the CMCON and VRCON registers are not affected.

# 6.8 Effects of a Reset

A device Reset forces the CMCON and VRCON registers to their Reset states. This forces the comparator module to be in the Comparator Reset mode, CM2:CM0 = 000 and the voltage reference to its off state. Thus, all potential inputs are analog inputs with the comparator and voltage reference disabled to consume the smallest current possible.

| REGISTER      | 6-2: VRCO                     | N: VOLTAGE                                         | REFEREN       | CE CONTRO        | L REGISTER      | R (ADDRESS:     | 99h)  |  |  |

|---------------|-------------------------------|----------------------------------------------------|---------------|------------------|-----------------|-----------------|-------|--|--|

| R/W-0         | U-0                           | R/W-0                                              | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0 |  |  |

| VREN          |                               | VRR                                                | _             | VR3              | VR2             | VR1             | VR0   |  |  |

| bit 7         |                               |                                                    |               |                  |                 |                 | bit ( |  |  |

| Legend:       |                               |                                                    |               |                  |                 |                 |       |  |  |

| R = Readabl   | le bit                        | W = Writable                                       | bit           | U = Unimplei     | mented bit, rea | d as '0'        |       |  |  |

| -n = Value at | t POR                         | '1' = Bit is set                                   |               | '0' = Bit is cle | ared            | x = Bit is unki | nown  |  |  |

|               | 0 = CVREF cir                 | cuit powered o<br>cuit powered d                   | own, no Idd o | drain            |                 |                 |       |  |  |

| bit 6         | Unimplemen                    | ted: Read as '                                     | 0'            |                  |                 |                 |       |  |  |

| bit 5         | VRR: CVREF                    | Range Selection                                    | on bit        |                  |                 |                 |       |  |  |

|               | 1 = Low rang<br>0 = High rang |                                                    |               |                  |                 |                 |       |  |  |

| bit 4         | Unimplemen                    | Unimplemented: Read as '0'                         |               |                  |                 |                 |       |  |  |

| bit 3-0       | When VRR =                    | /REF value sele<br>1: CVREF = (VI<br>0: CVREF = VD | R3:VR0 / 24)  | * VDD            |                 |                 |       |  |  |

### 6.9 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of the comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<6>, to determine the actual change that has occurred. The CMIF bit, PIR1<3>, is the comparator interrupt flag. This bit must be reset in software by clearing it to '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<3>) and the PEIE bit (INT-CON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are cleared, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

Note: If a change in the CMCON register (COUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CMIF (PIR1<3>) interrupt flag may not get set.

| Address | Name   | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOD | Value on<br>all other<br>Resets |

|---------|--------|-------|-------|---------|---------|---------|---------|---------|---------|----------------------|---------------------------------|

| 0Bh/8Bh | INTCON | GIE   | PEIE  | T0IE    | INTE    | GPIE    | T0IF    | INTF    | GPIF    | 0000 0000            | 0000 000u                       |

| 0Ch     | PIR1   | EEIF  | ADIF  | _       | —       | CMIF    | _       | _       | TMR1IF  | 00 00                | 00 00                           |

| 19h     | CMCON  | _     | COUT  | —       | CINV    | CIS     | CM2     | CM1     | CM0     | -0-0 0000            | -0-0 0000                       |

| 8Ch     | PIE1   | EEIE  | ADIE  | —       |         | CMIE    | —       | —       | TMR1IE  | 00 00                | 00 00                           |

| 85h     | TRISIO | _     | _     | TRISIO5 | TRISIO4 | TRISIO3 | TRISIO2 | TRISIO1 | TRISIO0 | 11 1111              | 11 1111                         |

| 99h     | VRCON  | VREN  | _     | VRR     |         | VR3     | VR2     | VR1     | VR0     | 0-0- 0000            | 0-0- 0000                       |

### TABLE 6-2: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the comparator module.

\_ \_ \_ \_ \_ \_

- -----

| REGISTER 7-1: ADCON0: A/D CONTROL REGISTER (ADDRESS: 1Fh) |                                                              |                                                         |                |                  |                 |                                    |       |  |  |

|-----------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------|----------------|------------------|-----------------|------------------------------------|-------|--|--|

| R/W-0                                                     | R/W-0                                                        | U-0                                                     | U-0            | R/W-0            | R/W-0           | R/W-0                              | R/W-0 |  |  |

| ADFM                                                      | VCFG                                                         | —                                                       |                | CHS1             | CHS0            | GO/DONE                            | ADON  |  |  |

| bit 7                                                     |                                                              |                                                         |                |                  |                 |                                    | bit C |  |  |

| Legend:                                                   |                                                              |                                                         |                |                  |                 |                                    |       |  |  |

| R = Readable b                                            | pit                                                          | W = Writable I                                          | oit            | U = Unimpler     | mented bit, rea | d as '0'                           |       |  |  |

| -n = Value at P                                           | OR                                                           | '1' = Bit is set                                        |                | '0' = Bit is cle | eared           | x = Bit is unkno                   | own   |  |  |

|                                                           |                                                              |                                                         |                |                  |                 |                                    |       |  |  |

| bit 7                                                     | ADFM: A/D R<br>1 = Right just<br>0 = Left justifi            |                                                         | Select bit     |                  |                 |                                    |       |  |  |

| bit 6                                                     | VCFG: Voltag<br>1 = VREF pin<br>0 = VDD                      | e Reference bi                                          | t              |                  |                 |                                    |       |  |  |

| bit 5-4                                                   | Unimplemen                                                   | ted: Read as 'o                                         | )'             |                  |                 |                                    |       |  |  |

| bit 3-2                                                   | CHS1:CHS0:                                                   | Analog Chann                                            | el Select bits |                  |                 |                                    |       |  |  |

|                                                           | 00 = Channel<br>01 = Channel<br>10 = Channel<br>11 = Channel | 01 (AN1)<br>02 (AN2)                                    |                |                  |                 |                                    |       |  |  |

| bit 1                                                     | GO/DONE: A                                                   | /D Conversion                                           | Status bit     |                  |                 |                                    |       |  |  |

|                                                           | This bit is                                                  | ersion cycle in p<br>automatically c<br>ersion complete | leared by ha   | rdware when th   |                 | version cycle.<br>ion has complete | ed.   |  |  |

| bit 0                                                     | ADON: A/D C                                                  | Conversion State                                        | us bit         |                  |                 |                                    |       |  |  |

|                                                           |                                                              | erter module is<br>erter is shut-off                    |                | es no operating  | g current       |                                    |       |  |  |

#### 9.4.1 GP2/INT INTERRUPT

External interrupt on GP2/INT pin is edge-triggered; either rising if INTEDG bit (OPTION<6>) is set, of falling, if INTEDG bit is clear. When a valid edge appears on the GP2/INT pin, the INTF bit (INT-CON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The GP2/INT interrupt can wake-up the processor from Sleep if the INTE bit was set prior to going into Sleep. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See **Section 9.7 "Power-Down Mode (Sleep)"** for details on Sleep and Figure 9-13 for timing of wake-up from Sleep through GP2/INT interrupt.

Note: The ANSEL (9Fh) and CMCON (19h) registers must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'. The ANSEL register is defined for the PIC12F675.

#### 9.4.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see **Section 4.0 "Timer0 Module"**.

#### 9.4.3 GPIO INTERRUPT

An input change on GPIO change sets the GPIF (INTCON<0>) bit. The interrupt can be enabled/ disabled by setting/clearing the GPIE (INTCON<3>) bit. Plus individual pins can be configured through the IOC register.

| Note: | If a change on the I/O pin should occur   |

|-------|-------------------------------------------|

|       | when the read operation is being executed |

|       | (start of the Q2 cycle), then the GPIF    |

|       | interrupt flag may not get set.           |

#### 9.4.4 COMPARATOR INTERRUPT

See **Section 6.9 "Comparator Interrupts"** for description of comparator interrupt.

#### 9.4.5 A/D CONVERTER INTERRUPT

After a conversion is complete, the ADIF flag (PIR<6>) is set. The interrupt can be enabled/disabled by setting or clearing ADIE (PIE<6>).

See Section 7.0 "Analog-to-Digital Converter (A/D) Module (PIC12F675 only)" for operation of the A/D converter interrupt.

|                          | Q1   Q2   Q3   Q4                     | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4   | Q1   Q2   Q3   Q4      | Q1   Q2   Q3   Q4 |

|--------------------------|---------------------------------------|-------------------|---------------------|------------------------|-------------------|

| OSC1 /                   |                                       |                   |                     |                        |                   |

| CLKOUT ③                 | (4)                                   |                   | 1/<br>¦             | \/                     |                   |

| INT pin                  |                                       | • ①               | 1<br>1<br>1         | 1<br>1<br>1            | <u> </u>          |

| INTF Flag<br>(INTCON<1>) | ,1 /5                                 |                   | Interrupt Latency 2 | 1<br>1<br>1<br>1       |                   |

| GIE bit<br>(INTCON<7>)   | , , , , , , , , , , , , , , , , , , , |                   |                     | 1<br>1<br><del>1</del> |                   |

| INSTRUCTION I            | FLOW                                  |                   | ₁ — — — — – -<br>'  | r — — — — — —<br>'     | · — — — — ¬       |

| PC                       | C PC                                  | PC + 1            | X PC + 1            | X 0004h                | X <u>0005h</u>    |

| Instruction (<br>Fetched | Inst (PC)                             | Inst (PC+1)       | -                   | Inst (0004h)           | Inst (0005h)      |

| Instruction {            | Inst (PC - 1)                         | Inst (PC)         | Dummy Cycle         | Dummy Cycle            | Inst (0004h)      |

#### FIGURE 9-11: INT PIN INTERRUPT TIMING

**Note 1:** INTF flag is sampled here (every Q1).

- 2: Asynchronous interrupt latency = 3-4 Tcy. Synchronous latency = 3 Tcy, where Tcy = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT is available only in RC Oscillator mode.

- **4:** For minimum width of INT pulse, refer to AC specs.

- **5:** INTF is enabled to be set any time during the Q4-Q1 cycles.

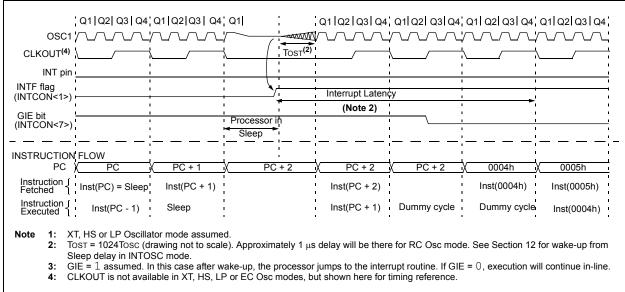

## 9.7 Power-Down Mode (Sleep)

The Power-down mode is entered by executing a SLEEP instruction.

If the Watchdog Timer is enabled:

- · WDT will be cleared but keeps running

- PD bit in the STATUS register is cleared

- TO bit is set

- Oscillator driver is turned off

- I/O ports maintain the status they had before Sleep was executed (driving high, low, or high-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD, or VSS, with no external circuitry drawing current from the I/O pin and the comparators and CVREF should be disabled. I/O pins that are high-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on GPIO should be considered.

The MCLR pin must be at a logic high level (VIHMC).

Note: It should be noted that a Reset generated by a WDT Time-out does not drive MCLR pin low.

#### 9.7.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- Interrupt from GP2/INT pin, GPIO change, or a peripheral interrupt.

The first event will cause a device Reset. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. TO bit is cleared if WDT Wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the SLEEP instruction of the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

Note: If the global interrupts are disabled (GIE is cleared), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from Sleep. The SLEEP instruction is completely executed.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

### FIGURE 9-13: WAKE-UP FROM SLEEP THROUGH INTERRUPT

## 9.8 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

**Note:** The entire data EEPROM and Flash program memory will be erased when the code protection is turned off. The INTOSC calibration data is also erased. See PIC12F629/675 Programming Specification for more information.

# 9.9 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable during Program/Verify. Only the Least Significant 7 bits of the ID locations are used.

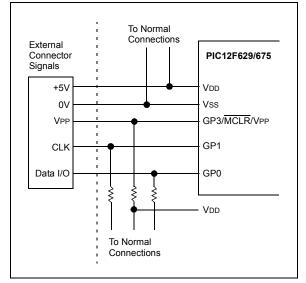

### 9.10 In-Circuit Serial Programming

The PIC12F629/675 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for:

- power

- ground

- programming voltage

This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the GP0 and GP1 pins low, while raising the  $\overline{\text{MCLR}}$  (VPP) pin from VIL to VIHH (see Programming Specification). GP0 becomes the programming data and GP1 becomes the programming clock. Both GP0 and GP1 are Schmitt Trigger inputs in this mode.

After Reset, to place the device into Programming/ Verify mode, the PC is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending on whether the command was a load or a read. For complete details of serial programming, please refer to the Programming Specifications.

A typical In-Circuit Serial Programming connection is shown in Figure 9-14.

#### FIGURE 9-14:

#### TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

# 9.11 In-Circuit Debugger

Since in-circuit debugging requires the loss of clock, data and MCLR pins, MPLAB<sup>®</sup> ICD 2 development with an 8-pin device is not practical. A special 14-pin PIC12F675-ICD device is used with MPLAB ICD 2 to provide separate clock, data and MCLR pins and frees all normally available pins to the user.

This special ICD device is mounted on the top of the header and its signals are routed to the MPLAB ICD 2 connector. On the bottom of the header is an 8-pin socket that plugs into the user's target via the 8-pin stand-off connector.

When the ICD pin on the PIC12F675-ICD device is held low, the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB ICD 2. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 9-10 shows which features are consumed by the background debugger:

### TABLE 9-10: DEBUGGER RESOURCES

| I/O pins       | ICDCLK, ICDDATA                     |

|----------------|-------------------------------------|

| Stack          | 1 level                             |

| Program Memory | Address 0h must be NOP<br>300h-3FEh |

For more information, see 8-Pin MPLAB ICD 2 Header Information Sheet (DS51292) available on Microchip's web site (www.microchip.com).

NOTES:

### 12.5 DC Characteristics: PIC12F629/675-E (Extended)

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                         |        |         |       |       |            |                                   |  |

|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------|---------|-------|-------|------------|-----------------------------------|--|

| Param Device Characteristics                                                                                                      |                         | Min    | Treat   | Мах   | Units | Conditions |                                   |  |

| No.                                                                                                                               | Device Gridiacteristics | IVIIII | Тур†    | IVIAX | Units | VDD        | Note                              |  |

| D020E                                                                                                                             | Power-down Base Current | _      | 0.00099 | 3.5   | μA    | 2.0        | WDT, BOD, Comparators, VREF,      |  |

|                                                                                                                                   | (IPD)                   |        | 0.0012  | 4.0   | μA    | 3.0        | and T1OSC disabled                |  |

|                                                                                                                                   |                         | _      | 0.0029  | 8.0   | μA    | 5.0        |                                   |  |

| D021E                                                                                                                             |                         | _      | 0.3     | 6.0   | μA    | 2.0        | WDT Current <sup>(1)</sup>        |  |

|                                                                                                                                   |                         | _      | 1.8     | 9.0   | μA    | 3.0        |                                   |  |

|                                                                                                                                   |                         | _      | 8.4     | 20    | μA    | 5.0        |                                   |  |

| D022E                                                                                                                             |                         | _      | 58      | 70    | μA    | 3.0        | BOD Current <sup>(1)</sup>        |  |

|                                                                                                                                   |                         | _      | 109     | 130   | μA    | 5.0        |                                   |  |

| D023E                                                                                                                             |                         |        | 3.3     | 10    | μA    | 2.0        | Comparator Current <sup>(1)</sup> |  |

|                                                                                                                                   |                         |        | 6.1     | 13    | μA    | 3.0        |                                   |  |

|                                                                                                                                   |                         |        | 11.5    | 24    | μA    | 5.0        |                                   |  |

| D024E                                                                                                                             |                         |        | 58      | 70    | μA    | 2.0        | CVREF Current <sup>(1)</sup>      |  |

|                                                                                                                                   |                         | _      | 85      | 100   | μA    | 3.0        |                                   |  |

|                                                                                                                                   |                         |        | 138     | 165   | μA    | 5.0        |                                   |  |

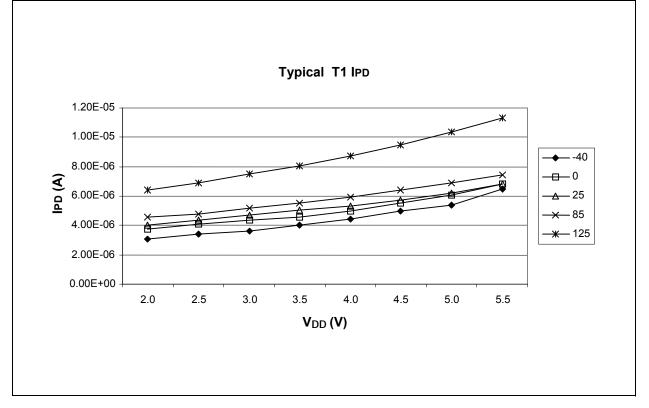

| D025E                                                                                                                             |                         | _      | 4.0     | 10    | μA    | 2.0        | T1 Osc Current <sup>(1)</sup>     |  |

|                                                                                                                                   |                         | _      | 4.6     | 12    | μA    | 3.0        |                                   |  |

|                                                                                                                                   |                         | _      | 6.0     | 20    | μA    | 5.0        |                                   |  |

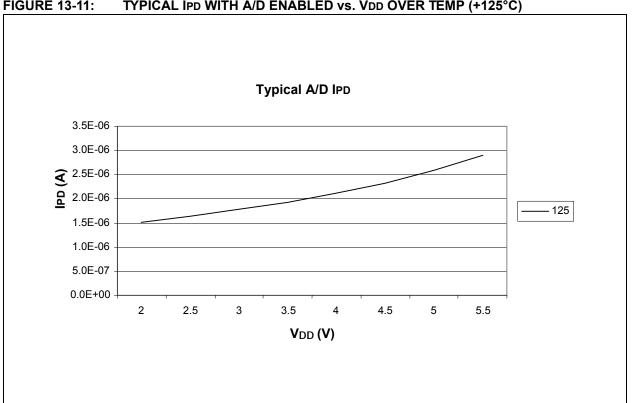

| D026E                                                                                                                             |                         | _      | 0.0012  | 6.0   | μA    | 3.0        | A/D Current <sup>(1)</sup>        |  |

|                                                                                                                                   |                         | _      | 0.0022  | 8.5   | μA    | 5.0        |                                   |  |

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

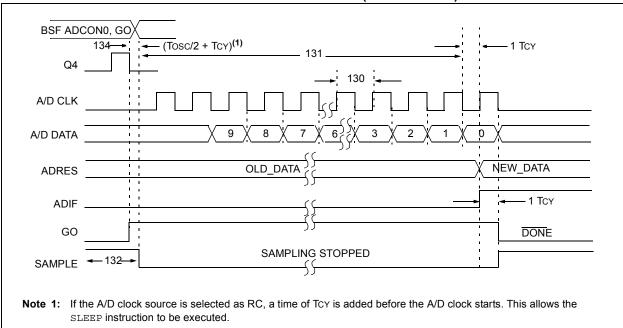

| FIGURE 12-11: | PIC12F675 A/D CONVERSION TIMING ( | SLEEP MODE) |

|---------------|-----------------------------------|-------------|

|               |                                   |             |

| Param<br>No. | Sym  | Characteristic                                                        | Min      | Тур†         | Max  | Units | Conditions                                                                                                                                                                                                                    |

|--------------|------|-----------------------------------------------------------------------|----------|--------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | Tad  | A/D Clock Period                                                      | 1.6      | —            | _    | μS    | $VREF \ge 3.0V$                                                                                                                                                                                                               |

|              |      |                                                                       | 3.0*     | —            |      | μS    | VREF full range                                                                                                                                                                                                               |

| 130          | Tad  | A/D Internal RC                                                       | 0.0*     |              | 0.0+ |       | ADCS<1:0> = 11 (RC mode)                                                                                                                                                                                                      |

|              |      | Oscillator Period                                                     | 3.0*     | 6.0          | 9.0* | μs    | At VDD = $2.5V$                                                                                                                                                                                                               |

|              |      |                                                                       | 2.0*     | 4.0          | 6.0* | μs    | At VDD = 5.0V                                                                                                                                                                                                                 |

| 131          | ΤΟΝΥ | Conversion Time<br>(not including<br>Acquisition Time) <sup>(1)</sup> | _        | 11           | _    | Tad   |                                                                                                                                                                                                                               |

| 132          | TACQ | Acquisition Time                                                      | (Note 2) | 11.5         | _    | μS    |                                                                                                                                                                                                                               |

|              |      |                                                                       | 5*       | _            | _    | μs    | The minimum time is the amplifier<br>settling time. This may be used if<br>the "new" input voltage has not<br>changed by more than 1 LSb (i.e.,<br>4.1 mV @ 4.096V) from the last<br>sampled voltage (as stored on<br>CHOLD). |

| 134          | TGO  | Q4 to A/D Clock<br>Start                                              |          | Tosc/2 + Tcy |      | _     | If the A/D clock source is selected<br>as RC, a time of TcY is added<br>before the A/D clock starts. This<br>allows the SLEEP instruction to be<br>executed.                                                                  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** ADRES register may be read on the following TCY cycle.

2: See Section 7.1 "A/D Configuration and Operation" for minimum conditions.

TYPICAL IPD WITH A/D ENABLED vs. VDD OVER TEMP (+125°C) FIGURE 13-11:

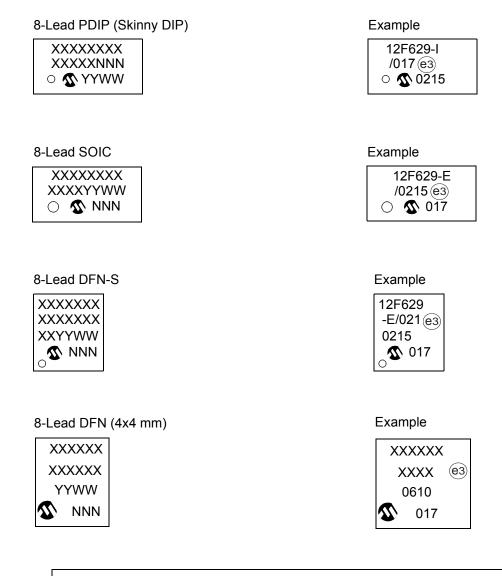

# 14.0 PACKAGING INFORMATION

# 14.1 Package Marking Information

| Legend | I: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|--------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carrie                                 | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>s for customer-specific information.                                                                                                                                                                                            |

# 8-Lead Plastic Small Outline (SN) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

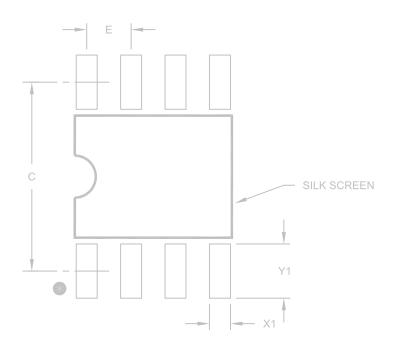

RECOMMENDED LAND PATTERN

|                         | Units      | MILLIMETERS |          |      |  |

|-------------------------|------------|-------------|----------|------|--|

| Dimens                  | ion Limits | MIN         | NOM      | MAX  |  |

| Contact Pitch           | E          |             | 1.27 BSC |      |  |

| Contact Pad Spacing     | С          |             | 5.40     |      |  |

| Contact Pad Width (X8)  | X1         |             |          | 0.60 |  |

| Contact Pad Length (X8) | Y1         |             |          | 1.55 |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A

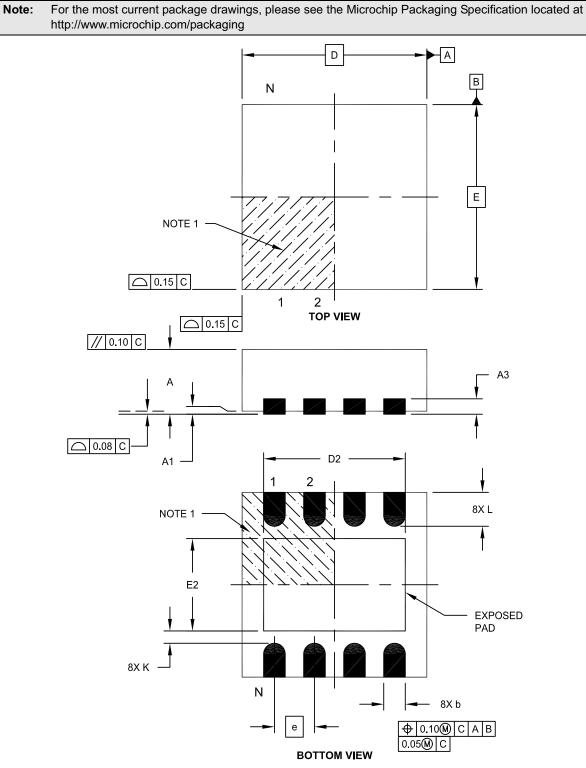

# 8-Lead Plastic Dual Flat, No Lead Package (MD) – 4x4x0.9 mm Body [DFN]

Microchip Technology Drawing C04-131E Sheet 1 of 2

NOTES: