# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 4x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-VDFN Exposed Pad                                                       |

| Supplier Device Package    | 8-DFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f675-e-md |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.2.2.6 PCON Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Detect (BOD)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON Register bits are shown in Register 2-6.

#### REGISTER 2-6: PCON: POWER CONTROL REGISTER (ADDRESS: 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-x |

|-------|-----|-----|-----|-----|-----|-------|-------|

|       | —   | —   | —   | —   | —   | POR   | BOD   |

| bit 7 | •   |     |     |     |     |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-2 | Unimplemented: Read as '0'                                                                                                                              |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | POR: Power-on Reset Status bit                                                                                                                          |

|         | <ul> <li>1 = No Power-on Reset occurred</li> <li>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)</li> </ul>       |

| bit 0   | BOD: Brown-out Detect Status bit                                                                                                                        |

|         | <ul> <li>1 = No Brown-out Detect occurred</li> <li>0 = A Brown-out Detect occurred (must be set in software after a Brown-out Detect occurs)</li> </ul> |

#### 2.2.2.7 OSCCAL Register

The Oscillator Calibration register (OSCCAL) is used to calibrate the internal 4 MHz oscillator. It contains 6 bits to adjust the frequency up or down to achieve 4 MHz.

The OSCCAL register bits are shown in Register 2-7.

#### REGISTER 2-7: OSCCAL: OSCILLATOR CALIBRATION REGISTER (ADDRESS: 90h)

|              |         |                  |       |                                         | •                | ,      |       |  |  |

|--------------|---------|------------------|-------|-----------------------------------------|------------------|--------|-------|--|--|

| R/W-1        | R/W-0   | R/W-0            | R/W-0 | R/W-0                                   | R/W-0            | U-0    | U-0   |  |  |

| CAL5         | CAL4    | CAL3             | CAL2  | CAL1                                    | CAL0             | _      | _     |  |  |

| bit 7        |         | ·                |       |                                         |                  | ·      | bit 0 |  |  |

|              |         |                  |       |                                         |                  |        |       |  |  |

| Legend:      |         |                  |       |                                         |                  |        |       |  |  |

| R = Readab   | ole bit | W = Writable     | bit   | U = Unimpler                            | nented bit, read | as '0' |       |  |  |

| -n = Value a | it POR  | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                  |        |       |  |  |

|              |         |                  |       |                                         |                  |        |       |  |  |

| bit 7-2      |         | 6-bit Signed O   |       | oration bits                            |                  |        |       |  |  |

|              |         | aximum frequer   |       |                                         |                  |        |       |  |  |

| 100000 = | Center | frequency |  |

|----------|--------|-----------|--|

|          |        |           |  |

000000 = Minimum frequency

## bit 1-0 Unimplemented: Read as '0'

| U-0                                               | U-0                                                                                                                   | R/W-1                                                                                                 | R/W-1                               | R-1                                     | R/W-1            | R/W-1           | R/W-1   |  |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------------------|------------------|-----------------|---------|--|

| _                                                 |                                                                                                                       | TRISI05                                                                                               | TRISIO4                             | TRISIO3                                 | TRISIO2          | TRISIO1         | TRISI00 |  |

| bit 7                                             | ·                                                                                                                     |                                                                                                       |                                     |                                         |                  |                 | bit     |  |

| Legend:                                           |                                                                                                                       |                                                                                                       |                                     |                                         |                  |                 |         |  |

| R = Readable                                      | e bit                                                                                                                 | W = Writable                                                                                          | bit                                 | U = Unimplen                            | nented bit, read | d as '0'        |         |  |

| -n = Value at                                     | POR                                                                                                                   | '1' = Bit is set                                                                                      |                                     | '0' = Bit is clea                       | ared             | x = Bit is unkr | iown    |  |

| LH 7 0                                            |                                                                                                                       | ta di Danadara (i                                                                                     | .,                                  |                                         |                  |                 |         |  |

| bit 7-6                                           | -                                                                                                                     | ted: Read as '                                                                                        |                                     | ata Cantral hit                         |                  |                 |         |  |

| bit 5-0                                           |                                                                                                                       | : General Purp<br>configured as                                                                       |                                     |                                         |                  |                 |         |  |

|                                                   |                                                                                                                       | configured as                                                                                         |                                     | aleu)                                   |                  |                 |         |  |

| Note: TR                                          | RISIO<3> always                                                                                                       | •                                                                                                     | anouput                             |                                         |                  |                 |         |  |

|                                                   |                                                                                                                       |                                                                                                       |                                     |                                         |                  |                 |         |  |

| REGISTER                                          | 3-3: WPU:                                                                                                             | WEAK PULL                                                                                             | -UP REGIS                           | FER (ADDRE                              | SS: 95h)         |                 |         |  |

| U-0                                               | U-0                                                                                                                   | R/W-1                                                                                                 | R/W-1                               | U-0                                     | R/W-1            | R/W-1           | R/W-1   |  |

|                                                   |                                                                                                                       | WPU5                                                                                                  | WPU4                                |                                         | WPU2             | WPU1            | WPU0    |  |

| bit 7                                             |                                                                                                                       |                                                                                                       |                                     |                                         |                  |                 | bit     |  |

|                                                   |                                                                                                                       |                                                                                                       |                                     |                                         |                  |                 |         |  |

| Legend:                                           |                                                                                                                       |                                                                                                       |                                     |                                         |                  |                 |         |  |

| R = Readable                                      | e bit                                                                                                                 | W = Writable                                                                                          | bit                                 | U = Unimplen                            | nented bit, read | d as '0'        |         |  |

| -n = Value at                                     | POR                                                                                                                   | '1' = Bit is set                                                                                      |                                     | '0' = Bit is cleared x = Bit is unknown |                  |                 |         |  |

|                                                   |                                                                                                                       |                                                                                                       |                                     |                                         |                  |                 |         |  |

|                                                   | -                                                                                                                     | ted: Read as '                                                                                        |                                     |                                         |                  |                 |         |  |

| bit 7-6                                           | 14/0011 .00 4. 1                                                                                                      | Noak Dull up D                                                                                        | onistor hit                         |                                         |                  |                 |         |  |

|                                                   | WPU<5:4>: \                                                                                                           | •                                                                                                     | cylater bit                         |                                         |                  |                 |         |  |

| bit 7-6<br>bit 5-4                                | 1 = Pull-up er                                                                                                        | nabled                                                                                                |                                     |                                         |                  |                 |         |  |

| bit 5-4                                           | 1 = Pull-up er<br>0 = Pull-up di                                                                                      | nabled<br>sabled                                                                                      |                                     |                                         |                  |                 |         |  |

| bit 5-4<br>bit 3                                  | 1 = Pull-up er<br>0 = Pull-up di<br><b>Unimplemen</b>                                                                 | nabled<br>sabled<br>I <b>ted:</b> Read as 'i                                                          | ס'                                  |                                         |                  |                 |         |  |

| bit 5-4<br>bit 3                                  | 1 = Pull-up er<br>0 = Pull-up di<br>Unimplemen<br>WPU<2:0>: V                                                         | nabled<br>sabled<br>i <b>ted:</b> Read as 'i<br>Neak Pull-up R                                        | ס'                                  |                                         |                  |                 |         |  |

| bit 5-4<br>bit 3                                  | 1 = Pull-up er<br>0 = Pull-up di<br>Unimplemen<br>WPU<2:0>: V<br>1 = Pull-up er                                       | nabled<br>sabled<br>I <b>ted:</b> Read as 'i<br>Neak Pull-up R<br>nabled                              | ס'                                  |                                         |                  |                 |         |  |

| bit 5-4<br>bit 3<br>bit 2-0                       | 1 = Pull-up er<br>0 = Pull-up di<br><b>Unimplemen</b><br><b>WPU&lt;2:0&gt;:</b> V<br>1 = Pull-up er<br>0 = Pull-up di | nabled<br>sabled<br>I <b>ted:</b> Read as f<br>Weak Pull-up R<br>nabled<br>sabled                     | ⊃'<br>egister bit                   |                                         |                  |                 |         |  |

| bit 5-4<br>bit 3<br>bit 2-0<br><b>Note 1:</b> Glo | 1 = Pull-up er<br>0 = Pull-up di<br>Unimplemen<br>WPU<2:0>: V<br>1 = Pull-up er                                       | nabled<br>sabled<br>I <b>ted:</b> Read as f<br>Weak Pull-up R<br>nabled<br>sabled<br>it be enabled fo | י<br>egister bit<br>r individual pu | •                                       |                  |                 |         |  |

## REGISTER 3-2: TRISIO: GPIO TRI-STATE REGISTER (ADDRESS: 85h)

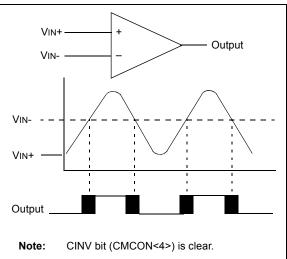

### 6.1 Comparator Operation

A single comparator is shown in Figure 6-1, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 6-1 represent the uncertainty due to input offsets and response time.

Note: To use CIN+ and CIN- pins as analog inputs, the appropriate bits must be programmed in the CMCON (19h) register.

The polarity of the comparator output can be inverted by setting the CINV bit (CMCON<4>). Clearing CINV results in a non-inverted output. A complete table showing the output state versus input conditions and the polarity bit is shown in Table 6-1.

## TABLE 6-1: OUTPUT STATE VS. INPUT CONDITIONS

| Input Conditions | CINV | COUT |

|------------------|------|------|

| VIN- > VIN+      | 0    | 0    |

| VIN- < VIN+      | 0    | 1    |

| VIN- > VIN+      | 1    | 1    |

| VIN- < VIN+      | 1    | 0    |

SINGLE COMPARATOR

| REGISTER      | 6-2: VRCO                     | N: VOLTAGE                                         | REFEREN       | CE CONTRO        | L REGISTER      | R (ADDRESS:     | 99h)  |

|---------------|-------------------------------|----------------------------------------------------|---------------|------------------|-----------------|-----------------|-------|

| R/W-0         | U-0                           | R/W-0                                              | R/W-0         | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

| VREN          |                               | VRR                                                | _             | VR3              | VR2             | VR1             | VR0   |

| bit 7         |                               |                                                    |               |                  |                 |                 | bit ( |

| Legend:       |                               |                                                    |               |                  |                 |                 |       |

| R = Readabl   | le bit                        | W = Writable                                       | bit           | U = Unimplei     | mented bit, rea | d as '0'        |       |

| -n = Value at | t POR                         | '1' = Bit is set                                   |               | '0' = Bit is cle | ared            | x = Bit is unki | nown  |

|               | 0 = CVREF cir                 | cuit powered o<br>cuit powered d                   | own, no Idd o | drain            |                 |                 |       |

| bit 6         | Unimplemen                    | ted: Read as '                                     | 0'            |                  |                 |                 |       |

| bit 5         | VRR: CVREF                    | Range Selection                                    | on bit        |                  |                 |                 |       |

|               | 1 = Low rang<br>0 = High rang |                                                    |               |                  |                 |                 |       |

| bit 4         | Unimplemen                    | ted: Read as '                                     | 0'            |                  |                 |                 |       |

| bit 3-0       | When VRR =                    | /REF value sele<br>1: CVREF = (VI<br>0: CVREF = VD | R3:VR0 / 24)  | * VDD            |                 |                 |       |

#### 6.9 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of the comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<6>, to determine the actual change that has occurred. The CMIF bit, PIR1<3>, is the comparator interrupt flag. This bit must be reset in software by clearing it to '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<3>) and the PEIE bit (INT-CON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are cleared, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

Note: If a change in the CMCON register (COUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CMIF (PIR1<3>) interrupt flag may not get set.

| Address | Name   | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOD | Value on<br>all other<br>Resets |

|---------|--------|-------|-------|---------|---------|---------|---------|---------|---------|----------------------|---------------------------------|

| 0Bh/8Bh | INTCON | GIE   | PEIE  | T0IE    | INTE    | GPIE    | T0IF    | INTF    | GPIF    | 0000 0000            | 0000 000u                       |

| 0Ch     | PIR1   | EEIF  | ADIF  | _       | —       | CMIF    | _       | _       | TMR1IF  | 00 00                | 00 00                           |

| 19h     | CMCON  | _     | COUT  | —       | CINV    | CIS     | CM2     | CM1     | CM0     | -0-0 0000            | -0-0 0000                       |

| 8Ch     | PIE1   | EEIE  | ADIE  | —       |         | CMIE    | —       | —       | TMR1IE  | 00 00                | 00 00                           |

| 85h     | TRISIO | _     | _     | TRISIO5 | TRISIO4 | TRISIO3 | TRISIO2 | TRISIO1 | TRISIO0 | 11 1111              | 11 1111                         |

| 99h     | VRCON  | VREN  | _     | VRR     |         | VR3     | VR2     | VR1     | VR0     | 0-0- 0000            | 0-0- 0000                       |

#### TABLE 6-2: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the comparator module.

### 9.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1') to select various device configurations, as shown in Register 9.2. These bits are mapped in program memory location 2007h.

**Note:** Address 2007h is beyond the user program memory space. It belongs to the special configuration memory space (2000h-3FFFh), which can be accessed only during programming. See PIC12F629/675 Programming Specification for more information.

#### REGISTER 9-1: CONFIG: CONFIGURATION WORD (ADDRESS: 2007h)

| R/P-1  | R/P-1 | U-0 | U-0 | U-0 | R/P-1 |

|--------|-------|-----|-----|-----|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| BG1    | BG0   | Ι   | Ι   | _   | CPD   | CP    | BODEN | MCLRE | PWRTE | WDTE  | F0SC2 | F0SC1 | F0SC0 |

| bit 13 |       |     |     |     |       |       |       |       |       |       |       |       | bit 0 |

| Legend:                    |                |                     |                    |

|----------------------------|----------------|---------------------|--------------------|

| P = Programmed using ICSP™ |                |                     |                    |

| R = Readable bit           | Writable bit   | U = Unimplemented b | pit, read as '0'   |

| -n = Value at POR          | 1 = bit is set | 0 = bit is cleared  | x = bit is unknown |

| bit 13-12 | BG1:BG0: Bandgap Calibration bits for BOD and POR voltage <sup>(1)</sup><br>00 = Lowest bandgap voltage<br>11 = Highest bandgap voltage                                                                                                         |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| h:+ 44 O  |                                                                                                                                                                                                                                                 |

| bit 11-9  | Unimplemented: Read as '0'                                                                                                                                                                                                                      |

| bit 8     | <b>CPD:</b> Data Code Protection bit <sup>(2)</sup><br>1 = Data memory code protection is disabled<br>0 = Data memory code protection is enabled                                                                                                |

| bit 7     | $\overline{CP}$ : Code Protection bit <sup>(3)</sup>                                                                                                                                                                                            |

| Dit 7     | 1 = Program Memory code protection is disabled                                                                                                                                                                                                  |

|           | 0 = Program Memory code protection is enabled                                                                                                                                                                                                   |

| bit 6     | BODEN: Brown-out Detect Enable bit <sup>(4)</sup>                                                                                                                                                                                               |

|           | 1 = BOD enabled                                                                                                                                                                                                                                 |

|           | 0 = BOD disabled                                                                                                                                                                                                                                |

| bit 5     | MCLRE: GP3/MCLR Pin Function Select bit <sup>(5)</sup>                                                                                                                                                                                          |

|           | 1 = GP3/MCLR pin function is MCLR                                                                                                                                                                                                               |

|           | 0 = GP3/MCLR pin function is digital I/O, MCLR internally tied to VDD                                                                                                                                                                           |

| bit 4     | PWRTE: Power-up Timer Enable bit                                                                                                                                                                                                                |

|           | 1 = PWRT disabled                                                                                                                                                                                                                               |

|           | 0 = PWRT enabled                                                                                                                                                                                                                                |

| bit 3     | WDTE: Watchdog Timer Enable bit                                                                                                                                                                                                                 |

|           | 1 = WDT enabled<br>0 = WDT disabled                                                                                                                                                                                                             |

|           |                                                                                                                                                                                                                                                 |

| bit 2-0   | <b>FOSC2:FOSC0</b> : Oscillator Selection bits<br>111 = RC oscillator: CLKOUT function on GP4/OSC2/CLKOUT pin, RC on GP5/OSC1/CLKIN                                                                                                             |

|           | 110 = RC oscillator: I/O function on GP4/OSC2/CLKOUT pin, RC on GP5/OSC1/CLKIN                                                                                                                                                                  |

|           | 101 = INTOSC oscillator: CLKOUT function on GP4/OSC2/CLKOUT pin, I/O function on GP5/OSC1/CLKIN                                                                                                                                                 |

|           | 100 = INTOSC oscillator: I/O function on GP4/OSC2/CLKOUT pin, I/O function on GP5/OSC1/CLKIN                                                                                                                                                    |

|           | 011 = EC: I/O function on GP4/OSC2/CLKOUT pin, CLKIN on GP5/OSC1/CLKIN                                                                                                                                                                          |

|           | 010 = HS oscillator: High speed crystal/resonator on GP4/OSC2/CLKOUT and GP5/OSC1/CLKIN                                                                                                                                                         |

|           | 001 = XT oscillator: Crystal/resonator on GP4/OSC2/CLKOUT and GP5/OSC1/CLKIN<br>000 = LP oscillator: Low-power crystal on GP4/OSC2/CLKOUT and GP5/OSC1/CLKIN                                                                                    |

| Note 1    |                                                                                                                                                                                                                                                 |

| Note 1    | : The Bandgap Calibration bits are factory programmed and must be read and saved prior to erasing the device as spec-<br>ified in the PIC12F629/675 Programming Specification. These bits are reflected in an export of the Configuration Word. |

|           | Microchip Development Tools maintain all Calibration bits to factory settings.                                                                                                                                                                  |

| 2         | The entire data EEPROM will be erased when the code protection is turned off.                                                                                                                                                                   |

| 3         | : The entire program memory will be erased, including OSCCAL value, when the code protection is turned off.                                                                                                                                     |

| 4         | Enabling Brown-out Detect does not automatically enable Power-up Timer.                                                                                                                                                                         |

|           |                                                                                                                                                                                                                                                 |

5: When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled.

### 9.3.1 MCLR

It should be noted that a WDT Reset does not drive MCLR pin low.

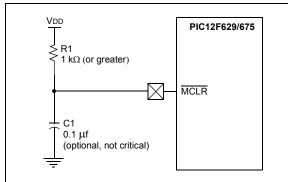

The behavior of the ESD protection on the MCLR pin has been altered from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 9-5, is suggested.

An internal MCLR option is enabled by setting the MCLRE bit in the Configuration Word. When enabled, MCLR is internally tied to VDD. No internal pull-up option is available for the MCLR pin.

#### FIGURE 9-5: RECOMMENDED MCLR CIRCUIT

#### 9.3.2 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, simply tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details (see Section 12.0 "Electrical Specifications"). If the BOD is enabled, the maximum rise time specification does not apply. The BOD circuitry will keep the device in Reset until VDD reaches VBOD (see Section 9.3.5 "Brown-Out Detect (BOD)").

| Note: | The POR circuit does not produce a | in |

|-------|------------------------------------|----|

|       | internal Reset when VDD declines.  |    |

When the device starts normal operation (exits the Reset condition), device operating parameters (i.e., voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

#### 9.3.3 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from POR or Brown-out Detect. The Power-up Timer operates on an internal RC oscillator. The chip is kept in Reset as long as PWRT is active. The PWRT delay allows the <u>VDD to</u> rise to an acceptable level. A Configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should always be enabled when Brown-out Detect is enabled.

The Power-up Time delay will vary from chip to chip and due to:

- VDD variation

- Temperature variation

- · Process variation.

See DC parameters for details (Section 12.0 "Electrical Specifications").

#### 9.3.4 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from Sleep.

#### 9.4.1 GP2/INT INTERRUPT

External interrupt on GP2/INT pin is edge-triggered; either rising if INTEDG bit (OPTION<6>) is set, of falling, if INTEDG bit is clear. When a valid edge appears on the GP2/INT pin, the INTF bit (INT-CON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The GP2/INT interrupt can wake-up the processor from Sleep if the INTE bit was set prior to going into Sleep. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See **Section 9.7 "Power-Down Mode (Sleep)"** for details on Sleep and Figure 9-13 for timing of wake-up from Sleep through GP2/INT interrupt.

Note: The ANSEL (9Fh) and CMCON (19h) registers must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'. The ANSEL register is defined for the PIC12F675.

#### 9.4.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see **Section 4.0 "Timer0 Module"**.

#### 9.4.3 GPIO INTERRUPT

An input change on GPIO change sets the GPIF (INTCON<0>) bit. The interrupt can be enabled/ disabled by setting/clearing the GPIE (INTCON<3>) bit. Plus individual pins can be configured through the IOC register.

| Note: | If a change on the I/O pin should occur   |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | when the read operation is being executed |  |  |  |  |  |  |  |

|       | (start of the Q2 cycle), then the GPIF    |  |  |  |  |  |  |  |

|       | interrupt flag may not get set.           |  |  |  |  |  |  |  |

#### 9.4.4 COMPARATOR INTERRUPT

See **Section 6.9 "Comparator Interrupts"** for description of comparator interrupt.

#### 9.4.5 A/D CONVERTER INTERRUPT

After a conversion is complete, the ADIF flag (PIR<6>) is set. The interrupt can be enabled/disabled by setting or clearing ADIE (PIE<6>).

See Section 7.0 "Analog-to-Digital Converter (A/D) Module (PIC12F675 only)" for operation of the A/D converter interrupt.

|                          | Q1   Q2   Q3   Q4                                                                           | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4   | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4 |

|--------------------------|---------------------------------------------------------------------------------------------|-------------------|---------------------|-------------------|-------------------|

| OSC1 /                   |                                                                                             |                   |                     |                   |                   |

| CLKOUT ③                 | (4)                                                                                         |                   | 1/<br>¦             | \/                |                   |

| INT pin                  |                                                                                             | • ①               | 1<br>1<br>1         | 1<br>1<br>1       | 1 1<br>1 1        |

| INTF Flag<br>(INTCON<1>) | ,1 /5                                                                                       |                   | Interrupt Latency 2 | 1<br>1<br>1<br>1  |                   |

| GIE bit<br>(INTCON<7>)   | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- |                   |                     | ,<br>,<br>,<br>,  |                   |

| INSTRUCTION I            | FLOW                                                                                        |                   | · — — — — —         | - — — — — —<br>!  | · — — — —         |

| PC                       | C PC                                                                                        | X PC + 1          | X PC + 1            | X 0004h           | X <u>0005h</u>    |

| Instruction (<br>Fetched | Inst (PC)                                                                                   | Inst (PC+1)       | -                   | Inst (0004h)      | Inst (0005h)      |

| Instruction {            | Inst (PC - 1)                                                                               | Inst (PC)         | Dummy Cycle         | Dummy Cycle       | Inst (0004h)      |

#### FIGURE 9-11: INT PIN INTERRUPT TIMING

**Note 1:** INTF flag is sampled here (every Q1).

- 2: Asynchronous interrupt latency = 3-4 Tcy. Synchronous latency = 3 Tcy, where Tcy = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT is available only in RC Oscillator mode.

- **4:** For minimum width of INT pulse, refer to AC specs.

- **5:** INTF is enabled to be set any time during the Q4-Q1 cycles.

### 9.8 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

**Note:** The entire data EEPROM and Flash program memory will be erased when the code protection is turned off. The INTOSC calibration data is also erased. See PIC12F629/675 Programming Specification for more information.

### 9.9 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable during Program/Verify. Only the Least Significant 7 bits of the ID locations are used.

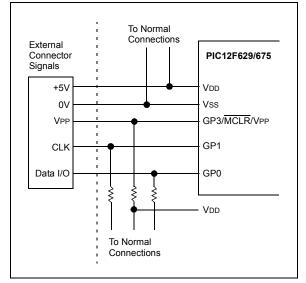

#### 9.10 In-Circuit Serial Programming

The PIC12F629/675 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for:

- power

- ground

- programming voltage

This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the GP0 and GP1 pins low, while raising the  $\overline{\text{MCLR}}$  (VPP) pin from VIL to VIHH (see Programming Specification). GP0 becomes the programming data and GP1 becomes the programming clock. Both GP0 and GP1 are Schmitt Trigger inputs in this mode.

After Reset, to place the device into Programming/ Verify mode, the PC is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending on whether the command was a load or a read. For complete details of serial programming, please refer to the Programming Specifications.

A typical In-Circuit Serial Programming connection is shown in Figure 9-14.

#### FIGURE 9-14:

#### TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

## 9.11 In-Circuit Debugger

Since in-circuit debugging requires the loss of clock, data and MCLR pins, MPLAB<sup>®</sup> ICD 2 development with an 8-pin device is not practical. A special 14-pin PIC12F675-ICD device is used with MPLAB ICD 2 to provide separate clock, data and MCLR pins and frees all normally available pins to the user.

This special ICD device is mounted on the top of the header and its signals are routed to the MPLAB ICD 2 connector. On the bottom of the header is an 8-pin socket that plugs into the user's target via the 8-pin stand-off connector.

When the ICD pin on the PIC12F675-ICD device is held low, the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB ICD 2. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 9-10 shows which features are consumed by the background debugger:

#### TABLE 9-10: DEBUGGER RESOURCES

| I/O pins       | ICDCLK, ICDDATA                     |

|----------------|-------------------------------------|

| Stack          | 1 level                             |

| Program Memory | Address 0h must be NOP<br>300h-3FEh |

For more information, see 8-Pin MPLAB ICD 2 Header Information Sheet (DS51292) available on Microchip's web site (www.microchip.com).

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                     |  |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                            |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.<br>If the result is 1, the next instruction is executed. If the result is 0, then a NOP is executed instead, making it a 2TCY instruction. |  |  |  |  |  |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                             |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                              |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>a NOP is executed instead, making<br>it a 2Tcy instruction. |  |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                              |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                           |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                              |  |  |  |  |  |

| Operation:       | k → PC<10:0><br>PCLATH<4:3> → PC<12:11>                                                                                                                                                           |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                              |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two-<br>cycle instruction. |  |  |  |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                               |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                       |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              |  |  |  |  |  |

| Status Affected: | Z                                                                                                                         |  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |  |  |  |  |  |

| INCF             | Increment f                                                                                                                                                            | IORWF            | Inclusive OR W with f                                                                                                                                       |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                              | Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                      | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                    | Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                    |

| Status Affected: | Z                                                                                                                                                                      | Status Affected: | Z                                                                                                                                                           |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. | Description:     | Inclusive OR the W register with register 'f'. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |

|       | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |        |      |      |       |     |                    |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|--------|------|------|-------|-----|--------------------|

| Param | Device Characteristics                                                                                                            | Min    | Typ† | Max  | Units |     | Conditions         |

| No.   | Device Characteristics                                                                                                            | IVIIII | iypi | WIAN | Units | VDD | Note               |

| D010E | Supply Current (IDD)                                                                                                              | -      | 9    | 16   | μA    | 2.0 | Fosc = 32 kHz      |

|       |                                                                                                                                   | —      | 18   | 28   | μA    | 3.0 | LP Oscillator Mode |

|       |                                                                                                                                   | _      | 35   | 54   | μA    | 5.0 |                    |

| D011E |                                                                                                                                   | -      | 110  | 150  | μA    | 2.0 | Fosc = 1 MHz       |

|       |                                                                                                                                   | _      | 190  | 280  | μA    | 3.0 | XT Oscillator Mode |

|       |                                                                                                                                   | _      | 330  | 450  | μA    | 5.0 |                    |

| D012E |                                                                                                                                   | -      | 220  | 280  | μA    | 2.0 | Fosc = 4 MHz       |

|       |                                                                                                                                   | —      | 370  | 650  | μA    | 3.0 | XT Oscillator Mode |

|       |                                                                                                                                   | _      | 0.6  | 1.4  | mA    | 5.0 |                    |

| D013E |                                                                                                                                   | -      | 70   | 110  | μA    | 2.0 | Fosc = 1 MHz       |

|       |                                                                                                                                   | —      | 140  | 250  | μA    | 3.0 | EC Oscillator Mode |

|       |                                                                                                                                   | —      | 260  | 390  | μA    | 5.0 |                    |

| D014E |                                                                                                                                   | —      | 180  | 250  | μA    | 2.0 | Fosc = 4 MHz       |

|       |                                                                                                                                   | —      | 320  | 470  | μA    | 3.0 | EC Oscillator Mode |

|       |                                                                                                                                   | —      | 580  | 850  | μA    | 5.0 |                    |

| D015E |                                                                                                                                   | —      | 340  | 450  | μA    | 2.0 | Fosc = 4 MHz       |

|       |                                                                                                                                   | —      | 500  | 780  | μA    | 3.0 | INTOSC Mode        |

|       |                                                                                                                                   | —      | 0.8  | 1.1  | mA    | 5.0 |                    |

| D016E |                                                                                                                                   |        | 180  | 250  | μA    | 2.0 | Fosc = 4 MHz       |

|       |                                                                                                                                   | _      | 320  | 450  | μA    | 3.0 | EXTRC Mode         |

|       |                                                                                                                                   | _      | 580  | 800  | μA    | 5.0 |                    |

| D017E |                                                                                                                                   | _      | 2.1  | 2.95 | mA    | 4.5 | Fosc = 20 MHz      |

|       |                                                                                                                                   | _      | 2.4  | 3.0  | mA    | 5.0 | HS Oscillator Mode |

#### 12.4 DC Characteristics: PIC12F629/675-E (Extended)

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in Active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

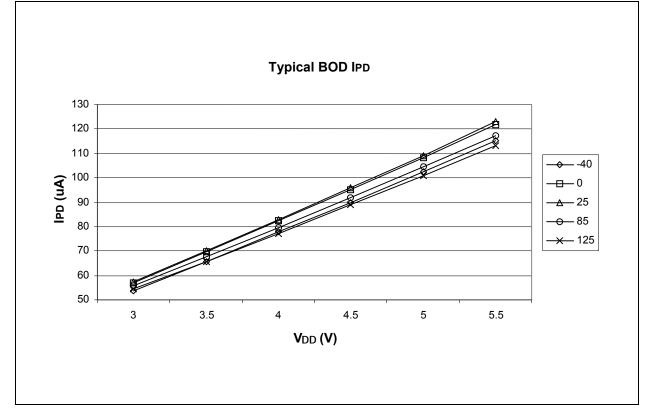

### 12.5 DC Characteristics: PIC12F629/675-E (Extended)

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                                            |       |         |      |       |     |                                   |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------|---------|------|-------|-----|-----------------------------------|

| Param                                                                                                                             | Device Characteristics                     | Min   | Typ†    | Мах  | Units |     | Conditions                        |

| No.                                                                                                                               | Device characteristics with Typ1 wax Onits | Units | VDD     | Note |       |     |                                   |

| D020E                                                                                                                             | Power-down Base Current                    | _     | 0.00099 | 3.5  | μA    | 2.0 | WDT, BOD, Comparators, VREF,      |

|                                                                                                                                   | (IPD)                                      |       | 0.0012  | 4.0  | μA    | 3.0 | and T1OSC disabled                |

|                                                                                                                                   |                                            | _     | 0.0029  | 8.0  | μA    | 5.0 |                                   |

| D021E                                                                                                                             |                                            | _     | 0.3     | 6.0  | μA    | 2.0 | WDT Current <sup>(1)</sup>        |

|                                                                                                                                   |                                            | _     | 1.8     | 9.0  | μA    | 3.0 |                                   |

|                                                                                                                                   |                                            | _     | 8.4     | 20   | μA    | 5.0 |                                   |

| D022E                                                                                                                             |                                            | _     | 58      | 70   | μA    | 3.0 | BOD Current <sup>(1)</sup>        |

|                                                                                                                                   |                                            | _     | 109     | 130  | μA    | 5.0 |                                   |

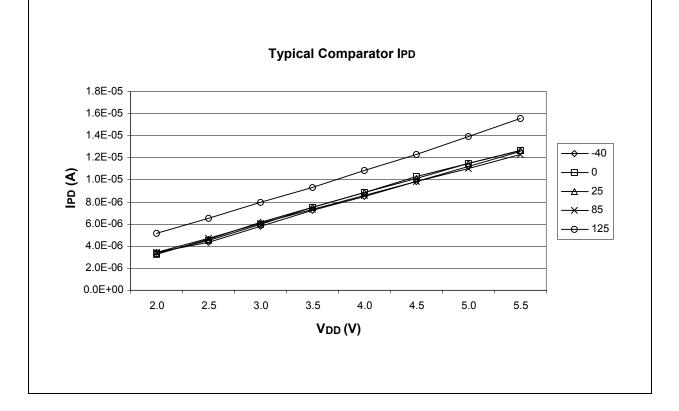

| D023E                                                                                                                             |                                            |       | 3.3     | 10   | μA    | 2.0 | Comparator Current <sup>(1)</sup> |

|                                                                                                                                   |                                            |       | 6.1     | 13   | μA    | 3.0 |                                   |

|                                                                                                                                   |                                            |       | 11.5    | 24   | μA    | 5.0 |                                   |

| D024E                                                                                                                             |                                            |       | 58      | 70   | μA    | 2.0 | CVREF Current <sup>(1)</sup>      |

|                                                                                                                                   |                                            | _     | 85      | 100  | μA    | 3.0 |                                   |

|                                                                                                                                   |                                            |       | 138     | 165  | μA    | 5.0 |                                   |

| D025E                                                                                                                             |                                            | _     | 4.0     | 10   | μA    | 2.0 | T1 Osc Current <sup>(1)</sup>     |

|                                                                                                                                   |                                            | _     | 4.6     | 12   | μA    | 3.0 |                                   |

|                                                                                                                                   |                                            | _     | 6.0     | 20   | μA    | 5.0 |                                   |

| D026E                                                                                                                             |                                            | _     | 0.0012  | 6.0  | μA    | 3.0 | A/D Current <sup>(1)</sup>        |

|                                                                                                                                   |                                            | _     | 0.0022  | 8.5  | μA    | 5.0 |                                   |

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

## 14.0 PACKAGING INFORMATION

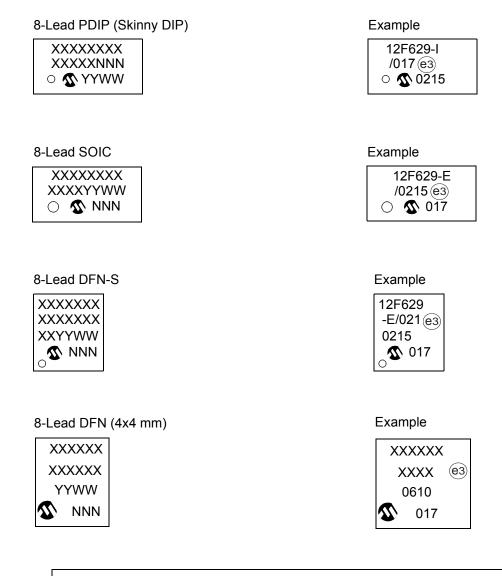

### 14.1 Package Marking Information

| Legend | I: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                    | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | In the event the full Microchip part number cannot be marked on one line, it wil<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                              |

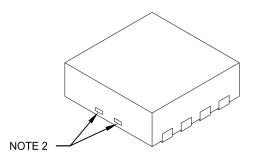

### 8-Lead Plastic Dual Flat, No Lead Package (MD) – 4x4x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                  |        | MILLIMETERS |          |      |

|------------------------|--------|-------------|----------|------|

| Dimension              | Limits | MIN         | NOM      | MAX  |

| Number of Pins         | N      |             | 8        |      |

| Pitch                  | е      | 0.80 BSC    |          |      |

| Overall Height         | A      | 0.80        | 0.90     | 1.00 |

| Standoff               | A1     | 0.00        | 0.02     | 0.05 |

| Contact Thickness      | A3     | 0.20 REF    |          |      |

| Overall Length         | D      | 4.00 BSC    |          |      |

| Exposed Pad Width      | E2     | 2.60        | 2.70     | 2.80 |

| Overall Width          | E      |             | 4.00 BSC |      |

| Exposed Pad Length     | D2     | 3.40        | 3.50     | 3.60 |

| Contact Width          | b      | 0.25        | 0.30     | 0.35 |

| Contact Length         | L      | 0.30        | 0.40     | 0.50 |

| Contact-to-Exposed Pad | К      | 0.20        | -        | -    |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-131E Sheet 2 of 2

| CLKOUT and I/O98                                 |  |  |  |  |  |

|--------------------------------------------------|--|--|--|--|--|

| External Clock96                                 |  |  |  |  |  |

| INT Pin Interrupt65                              |  |  |  |  |  |

| PIC12F675 A/D Conversion (Normal Mode) 104       |  |  |  |  |  |

| PIC12F675 A/D Conversion Timing                  |  |  |  |  |  |

| (SLEEP Mode)                                     |  |  |  |  |  |

| RESET, Watchdog Timer, Oscillator Start-up Timer |  |  |  |  |  |

| and Power-up Timer                               |  |  |  |  |  |

| Time-out Sequence on Power-up (MCLR not Tied to  |  |  |  |  |  |

| Vdd)/                                            |  |  |  |  |  |

| Case 1 62                                        |  |  |  |  |  |

| Case 2                                           |  |  |  |  |  |

| Time-out Sequence on Power-up                    |  |  |  |  |  |

| (MCLR Tied to VDD)62                             |  |  |  |  |  |

| Timer0 and Timer1 External Clock 101             |  |  |  |  |  |

| Timer1 Incrementing Edge                         |  |  |  |  |  |

| Timing Parameter Symbology95                     |  |  |  |  |  |

| TRISIO — GPIO Tri-state REGISTER (Address        |  |  |  |  |  |

| 85H)22                                           |  |  |  |  |  |

| V                                                |  |  |  |  |  |

| Voltage Reference Accuracy/Error41               |  |  |  |  |  |

| W                                                |  |  |  |  |  |

| Watchdog Timer                                   |  |  |  |  |  |

| Summary of Registers                             |  |  |  |  |  |

| Watchdog Timer (WDT)                             |  |  |  |  |  |

| WPU — Weak pull-up Register (ADDRESS             |  |  |  |  |  |

| 95h)                                             |  |  |  |  |  |

| WWW Address                                      |  |  |  |  |  |

| WWW, On-Line Support                             |  |  |  |  |  |

|                                                  |  |  |  |  |  |

## **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:          | Technical Publications Manager                                                | Total Pages Sent                                       |  |  |  |

|--------------|-------------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|

| RE:          | Reader Response                                                               |                                                        |  |  |  |