Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 5                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 128 x 8                                                                 |

| RAM Size                   | 64 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 4x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 8-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f675-e-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 8-Pin Flash-Based 8-Bit CMOS Microcontroller

#### High-Performance RISC CPU:

- · Only 35 Instructions to Learn

- All single-cycle instructions except branches

- · Operating Speed:

- DC 20 MHz oscillator/clock input

- DC 200 ns instruction cycle

- Interrupt Capability

- 8-Level Deep Hardware Stack

- · Direct, Indirect, and Relative Addressing modes

#### **Special Microcontroller Features:**

- Internal and External Oscillator Options

- Precision Internal 4 MHz oscillator factory calibrated to ±1%

- External Oscillator support for crystals and resonators

- 5 µs wake-up from Sleep, 3.0V, typical

- Power-Saving Sleep mode

- Wide Operating Voltage Range 2.0V to 5.5V

- Industrial and Extended Temperature Range

- Low-Power Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- · Brown-out Detect (BOD)

- Watchdog Timer (WDT) with Independent Oscillator for Reliable Operation

- Multiplexed MCLR/Input Pin

- Interrupt-on-Pin Change

- Individual Programmable Weak Pull-ups

- Programmable Code Protection

- High Endurance Flash/EEPROM Cell

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- Flash/Data EEPROM Retention: > 40 years

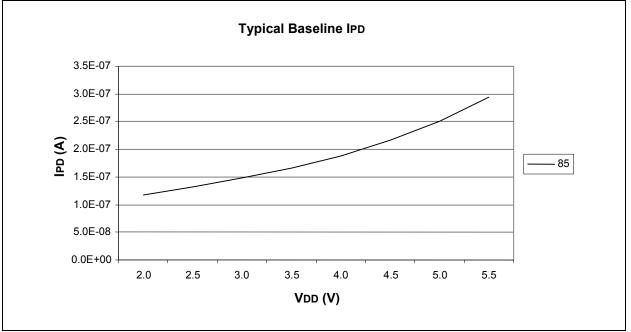

#### Low-Power Features:

- Standby Current:

- 1 nA @ 2.0V, typical

- Operating Current:

- 8.5 μA @ 32 kHz, 2.0V, typical

- 100 μA @ 1 MHz, 2.0V, typical

- Watchdog Timer Current

300 nA @ 2.0V, typical

- 300 TA @ 2.00, typical

- Timer1 Oscillator Current:

- 4 μA @ 32 kHz, 2.0V, typical

#### **Peripheral Features:**

- · 6 I/O Pins with Individual Direction Control

- High Current Sink/Source for Direct LED Drive

- Analog Comparator module with:

- One analog comparator

- Programmable on-chip comparator voltage reference (CVREF) module

- Programmable input multiplexing from device inputs

- Comparator output is externally accessible

- Analog-to-Digital Converter module (PIC12F675):

- 10-bit resolution

- Programmable 4-channel input

- Voltage reference input

- Timer0: 8-Bit Timer/Counter with 8-Bit Programmable Prescaler

- Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Gate Input mode

- Option to use OSC1 and OSC2 in LP mode as Timer1 oscillator, if INTOSC mode selected

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via two pins

| Device    | Program<br>Memory | Data Memory     |                   | I/O | 10-bit A/D | Comparators | Timers   |

|-----------|-------------------|-----------------|-------------------|-----|------------|-------------|----------|

|           | Flash<br>(words)  | SRAM<br>(bytes) | EEPROM<br>(bytes) | 1/0 | (ch)       | Comparators | 8/16-bit |

| PIC12F629 | 1024              | 64              | 128               | 6   | -          | 1           | 1/1      |

| PIC12F675 | 1024              | 64              | 128               | 6   | 4          | 1           | 1/1      |

\* 8-bit, 8-pin devices protected by Microchip's Low Pin Count Patent: U.S. Patent No. 5,847,450. Additional U.S. and foreign patents and applications may be issued or pending.

#### **Table of Contents**

| 1.0   | Device Overview                                           | 7    |

|-------|-----------------------------------------------------------|------|

| 2.0   | Memory Organization                                       | 9    |

| 3.0   | GPIO Port                                                 | 21   |

| 4.0   | Timer0 Module                                             | . 29 |

| 5.0   | Timer1 Module with Gate Control                           | . 32 |

| 6.0   | Comparator Module                                         | . 37 |

| 7.0   | Analog-to-Digital Converter (A/D) Module (PIC12F675 only) | 43   |

| 8.0   | Data EEPROM Memory                                        | 49   |

| 9.0   | Special Features of the CPU                               |      |

| 10.0  | Instruction Set Summary                                   | 71   |

| 11.0  | Development Support                                       | 81   |

| 12.0  | Electrical Specifications                                 | 85   |

| 13.0  | DC and AC Characteristics Graphs and Tables               | 107  |

| 14.0  | Packaging Information                                     | 117  |

| Apper | ndix A: Data Sheet Revision History                       | 127  |

| Apper | ndix B: Device Differences                                | 127  |

| Apper | ndix C: Device Migrations                                 | 128  |

| Apper | ndix D: Migrating from other PIC <sup>®</sup> Devices     | 128  |

| Index |                                                           | 129  |

| On-Li | ne Support                                                | 133  |

| Syste | ns Information and Upgrade Hot Line                       | 133  |

| Reade | er Response                                               | 134  |

| Produ | ct Identification System                                  | 135  |

|       |                                                           |      |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

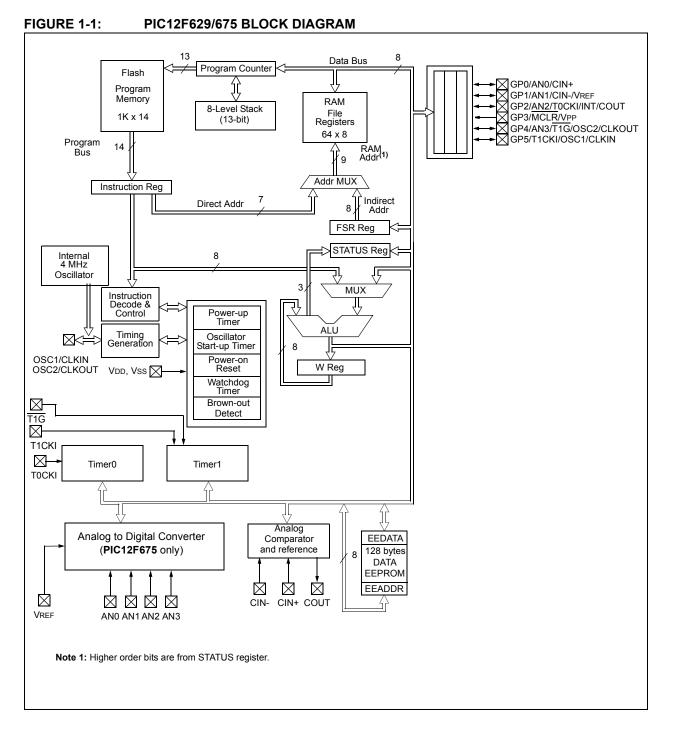

#### 1.0 DEVICE OVERVIEW

This document contains device specific information for the PIC12F629/675. Additional information may be found in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip web site. The Reference Manual should be considered a complementary document to this Data Sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

The PIC12F629 and PIC12F675 devices are covered by this Data Sheet. They are identical, except the PIC12F675 has a 10-bit A/D converter. They come in 8-pin PDIP, SOIC, MLF-S and DFN packages. Figure 1-1 shows a block diagram of the PIC12F629/ 675 devices. Table 1-1 shows the pinout description.

#### TABLE 1-1: PIC12F629/675 PINOUT DESCRIPTION

| Name                          | Function | Input<br>Type | Output<br>Type | Description                                                       |

|-------------------------------|----------|---------------|----------------|-------------------------------------------------------------------|

| GP0/AN0/CIN+/ICSPDAT          | GP0      | TTL           | CMOS           | Bidirectional I/O w/ programmable pull-up and interrupt-on-change |

|                               | AN0      | AN            |                | A/D Channel 0 input                                               |

|                               | CIN+     | AN            |                | Comparator input                                                  |

|                               | ICSPDAT  | TTL           | CMOS           | Serial programming I/O                                            |

| GP1/AN1/CIN-/VREF/<br>ICSPCLK | GP1      | TTL           | CMOS           | Bidirectional I/O w/ programmable pull-up and interrupt-on-change |

|                               | AN1      | AN            |                | A/D Channel 1 input                                               |

|                               | CIN-     | AN            |                | Comparator input                                                  |

|                               | VREF     | AN            |                | External voltage reference                                        |

|                               | ICSPCLK  | ST            |                | Serial programming clock                                          |

| GP2/AN2/T0CKI/INT/COUT        | GP2      | ST            | CMOS           | Bidirectional I/O w/ programmable pull-up and interrupt-on-change |

|                               | AN2      | AN            |                | A/D Channel 2 input                                               |

|                               | T0CKI    | ST            |                | TMR0 clock input                                                  |

|                               | INT      | ST            |                | External interrupt                                                |

|                               | COUT     |               | CMOS           | Comparator output                                                 |

| GP3/MCLR/Vpp                  | GP3      | TTL           |                | Input port w/ interrupt-on-change                                 |

|                               | MCLR     | ST            |                | Master Clear                                                      |

|                               | VPP      | HV            |                | Programming voltage                                               |

| GP4/AN3/T1G/OSC2/<br>CLKOUT   | GP4      | TTL           | CMOS           | Bidirectional I/O w/ programmable pull-up and interrupt-on-change |

|                               | AN3      | AN            |                | A/D Channel 3 input                                               |

|                               | T1G      | ST            |                | TMR1 gate                                                         |

|                               | OSC2     |               | XTAL           | Crystal/resonator                                                 |

|                               | CLKOUT   |               | CMOS           | Fosc/4 output                                                     |

| GP5/T1CKI/OSC1/CLKIN          | GP5      | TTL           | CMOS           | Bidirectional I/O w/ programmable pull-up and interrupt-on-change |

|                               | T1CKI    | ST            |                | TMR1 clock                                                        |

|                               | OSC1     | XTAL          |                | Crystal/resonator                                                 |

|                               | CLKIN    | ST            |                | External clock input/RC oscillator connection                     |

| Vss                           | Vss      | Power         |                | Ground reference                                                  |

| Vdd                           | Vdd      | Power         |                | Positive supply                                                   |

Legend: Shade = PIC12F675 only

TTL = TTL input buffer, ST = Schmitt Trigger input buffer

#### 2.2.2.4 PIE1 Register

The PIE1 register contains the interrupt enable bits, as shown in Register 2-4.

Note: Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

#### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1 (ADDRESS: 8Ch)

| R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | U-0 | U-0 | R/W-0  |

|-------|-------|-----|-----|-------|-----|-----|--------|

| EEIE  | ADIE  | —   | _   | CMIE  | —   | —   | TMR1IE |

| bit 7 |       |     |     |       |     |     | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7   | <b>EEIE:</b> EE Write Complete Interrupt Enable bit<br>1 = Enables the EE write complete interrupt<br>0 = Disables the EE write complete interrupt |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | <b>ADIE:</b> A/D Converter Interrupt Enable bit (PIC12F675 only)<br>1 = Enables the A/D converter interrupt                                        |

|         | 0 = Disables the A/D converter interrupt                                                                                                           |

| bit 5-4 | Unimplemented: Read as '0'                                                                                                                         |

| bit 3   | CMIE: Comparator Interrupt Enable bit                                                                                                              |

|         | 1 = Enables the comparator interrupt                                                                                                               |

|         | 0 = Disables the comparator interrupt                                                                                                              |

| bit 2-1 | Unimplemented: Read as '0'                                                                                                                         |

| bit 0   | TMR1IE: TMR1 Overflow Interrupt Enable bit                                                                                                         |

|         | <ul><li>1 = Enables the TMR1 overflow interrupt</li><li>0 = Disables the TMR1 overflow interrupt</li></ul>                                         |

|         |                                                                                                                                                    |

#### 2.2.2.6 PCON Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Detect (BOD)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON Register bits are shown in Register 2-6.

#### REGISTER 2-6: PCON: POWER CONTROL REGISTER (ADDRESS: 8Eh)

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-x |

|-------------|-----|-----|-----|-----|-----|-------|-------|

|             | —   | —   | —   | —   | —   | POR   | BOD   |

| bit 7 bit 0 |     |     |     |     |     |       |       |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7-2 | Unimplemented: Read as '0'                                                                                                                              |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | POR: Power-on Reset Status bit                                                                                                                          |

|         | <ul> <li>1 = No Power-on Reset occurred</li> <li>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)</li> </ul>       |

| bit 0   | BOD: Brown-out Detect Status bit                                                                                                                        |

|         | <ul> <li>1 = No Brown-out Detect occurred</li> <li>0 = A Brown-out Detect occurred (must be set in software after a Brown-out Detect occurs)</li> </ul> |

#### 2.2.2.7 OSCCAL Register

The Oscillator Calibration register (OSCCAL) is used to calibrate the internal 4 MHz oscillator. It contains 6 bits to adjust the frequency up or down to achieve 4 MHz.

The OSCCAL register bits are shown in Register 2-7.

#### REGISTER 2-7: OSCCAL: OSCILLATOR CALIBRATION REGISTER (ADDRESS: 90h)

|                              |       |                  |       |                                    | •     | ,                  |       |

|------------------------------|-------|------------------|-------|------------------------------------|-------|--------------------|-------|

| R/W-1                        | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | U-0                | U-0   |

| CAL5                         | CAL4  | CAL3             | CAL2  | CAL1                               | CAL0  | _                  | _     |

| bit 7                        |       | ·                |       |                                    |       | ·                  | bit 0 |

|                              |       |                  |       |                                    |       |                    |       |

| Legend:                      |       |                  |       |                                    |       |                    |       |

| R = Readable bit             |       | W = Writable     | bit   | U = Unimplemented bit, read as '0' |       |                    |       |

| -n = Value at POR            |       | '1' = Bit is set |       | '0' = Bit is cle                   | ared  | x = Bit is unknown |       |

|                              |       |                  |       |                                    |       |                    |       |

| bit 7-2 CAL5:CAL0: 6-bit Sig |       |                  |       | oration bits                       |       |                    |       |

|                              |       | aximum frequer   |       |                                    |       |                    |       |

| 100000 = | Center | frequency |  |

|----------|--------|-----------|--|

|          |        |           |  |

000000 = Minimum frequency

#### bit 1-0 Unimplemented: Read as '0'

NOTES:

#### 5.4 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 5.4.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

Note: The ANSEL (9Fh) and CMCON (19h) registers must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'. The ANSEL register is defined for the PIC12F675.

### 5.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L, while the timer is running from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

#### 5.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins OSC1 (input) and OSC2 (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low-power oscillator rated up to 37 kHz. It will continue to run during Sleep. It is primarily intended for a 32 kHz crystal. Table 9-2 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is shared with the system LP oscillator. Thus, Timer1 can use this mode only when the system clock is derived from the internal oscillator. As with the system LP oscillator, the user must provide a software time delay to ensure proper oscillator start-up.

While enabled, TRISIO4 and TRISIO5 are set. GP4 and GP5 read '0' and TRISIO4 and TRISIO5 are read '1'.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to enabling Timer1.

#### 5.6 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To setup the timer to wake the device:

- Timer1 must be on (T1CON<0>)

- TMR1IE bit (PIE1<0>) must be set

- PEIE bit (INTCON<6>) must be set

The device will wake-up on an overflow. If the GIE bit (INTCON<7>) is set, the device will wake-up and jump to the Interrupt Service Routine on an overflow.

| IADEL ( | ABEL 3-1. REGISTERS ASSOCIATED WITH HMERTAS A HMER/COUNTER |                                                                            |                                                                             |         |         |         |        |        |        |               |      |      |                       |

|---------|------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------|---------|---------|--------|--------|--------|---------------|------|------|-----------------------|

| Address | Name                                                       | Bit 7                                                                      | Bit 6                                                                       | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value<br>POR, |      | allo | e on<br>other<br>sets |

| 0Bh/8Bh | INTCON                                                     | GIE                                                                        | PEIE                                                                        | T0IE    | INTE    | GPIE    | T0IF   | INTF   | GPIF   | 0000          | 0000 | 0000 | 000u                  |

| 0Ch     | PIR1                                                       | EEIF                                                                       | ADIF                                                                        | _       | _       | CMIF    | —      | —      | TMR1IF | 00            | 00   | 00   | 00                    |

| 0Eh     | TMR1L                                                      | Holding                                                                    | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |         |         |         |        |        |        | XXXX          | XXXX | uuuu | uuuu                  |

| 0Fh     | TMR1H                                                      | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |                                                                             |         |         |         |        |        | XXXX   | XXXX          | uuuu | uuuu |                       |

| 10h     | T1CON                                                      |                                                                            | TMR1GE                                                                      | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | -000          | 0000 | -uuu | uuuu                  |

| 8Ch     | PIE1                                                       | EEIE                                                                       | ADIE                                                                        |         | _       | CMIE    | _      | _      | TMR1IE | 00            | 00   | 00   | 00                    |

TABLE 5-1: REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

#### 8.7 Data EEPROM Operation During Code Protect

Data memory can be code protected by programming the CPD bit to '0'.

When the data memory is code protected, the CPU is able to read and write data to the data EEPROM. It is recommended to code protect the program memory when code protecting data memory. This prevents anyone from programming zeroes over the existing code (which will execute as NOPS) to reach an added routine, programmed in unused program memory, which outputs the contents of data memory. Programming unused locations to '0' will also help prevent data memory code protection from becoming breached.

| Address | Name                  | Bit 7                   | Bit 6       | Bit 5      | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Valu<br>POR, | e on | Value<br>oth<br>Res | ner  |

|---------|-----------------------|-------------------------|-------------|------------|----------|-------|-------|-------|--------|--------------|------|---------------------|------|

| 0Ch     | PIR1                  | EEIF                    | ADIF        | _          |          | CMIF  | _     | —     | TMR1IF | 00           | 00   | 00                  | 00   |

| 9Ah     | EEDATA                | TA EEPROM Data Register |             |            |          |       |       | 0000  | 0000   | 0000         | 0000 |                     |      |

| 9Bh     | EEADR                 | _                       | EEPRON      | 1 Address  | Register |       |       |       |        | -000         | 0000 | -000                | 0000 |

| 9Ch     | EECON1                | _                       | —           | —          | —        | WRERR | WREN  | WR    | RD     |              | x000 |                     | q000 |

| 9Dh     | EECON2 <sup>(1)</sup> | EEPROM                  | I Control F | Register 2 |          |       |       |       |        |              |      |                     |      |

#### TABLE 8-1: REGISTERS/BITS ASSOCIATED WITH DATA EEPROM

$\label{eq:logarder} \mbox{Legend: $x$ = unknown, $u$ = unchanged, - = unimplemented read as `0', $q$ = value depends upon condition. Shaded cells are not used by data EEPROM module.}$

**Note 1:** EECON2 is not a physical register.

#### 9.2.3 EXTERNAL CLOCK IN

For applications where a clock is already available elsewhere, users may directly drive the PIC12F629/ 675 provided that this external clock source meets the AC/DC timing requirements listed in **Section 12.0 "Electrical Specifications"**. Figure 9-2 shows how an external clock circuit should be configured.

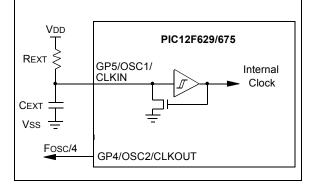

#### 9.2.4 RC OSCILLATOR

For applications where precise timing is not a requirement, the RC oscillator option is available. The operation and functionality of the RC oscillator is dependent upon a number of variables. The RC oscillator frequency is a function of:

- · Supply voltage

- Resistor (REXT) and capacitor (CEXT) values

- Operating temperature.

The oscillator frequency will vary from unit to unit due to normal process parameter variation. The difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to account for the tolerance of the external R and C components. Figure 9-3 shows how the R/C combination is connected.

Two options are available for this Oscillator mode which allow GP4 to be used as a general purpose I/O or to output Fosc/4.

#### FIGURE 9-3: RC OSCILLATOR MODE

#### 9.2.5 INTERNAL 4 MHz OSCILLATOR

When calibrated, the internal oscillator provides a fixed 4 MHz (nominal) system clock. See Electrical Specifications, **Section 12.0** "Electrical Specifications", for information on variation over voltage and temperature.

Two options are available for this Oscillator mode which allow GP4 to be used as a general purpose I/O or to output Fosc/4.

#### 9.2.5.1 Calibrating the Internal Oscillator

A calibration instruction is programmed into the last location of program memory. This instruction is a RETLW XX, where the literal is the calibration value. The literal is placed in the OSCCAL register to set the calibration of the internal oscillator. Example 9-1 demonstrates how to calibrate the internal oscillator. For best operation, decouple (with capacitance) VDD and Vss as close to the device as possible.

**Note:** Erasing the device will also erase the preprogrammed internal calibration value for the internal oscillator. The calibration value must be saved prior to erasing part as specified in the PIC12F629/675 Programming specification. Microchip Development Tools maintain all Calibration bits to factory settings.

#### EXAMPLE 9-1: CALIBRATING THE INTERNAL OSCILLATOR

|                         | cal value<br>e |

|-------------------------|----------------|

| BCF STATUS, RPO ;Bank O |                |

#### 9.2.6 CLKOUT

The PIC12F629/675 devices can be configured to provide a clock out signal in the INTOSC and RC oscillator modes. When configured, the oscillator frequency divided by four (Fosc/4) is output on the GP4/OSC2/CLKOUT pin. Fosc/4 can be used for test purposes or to synchronize other logic.

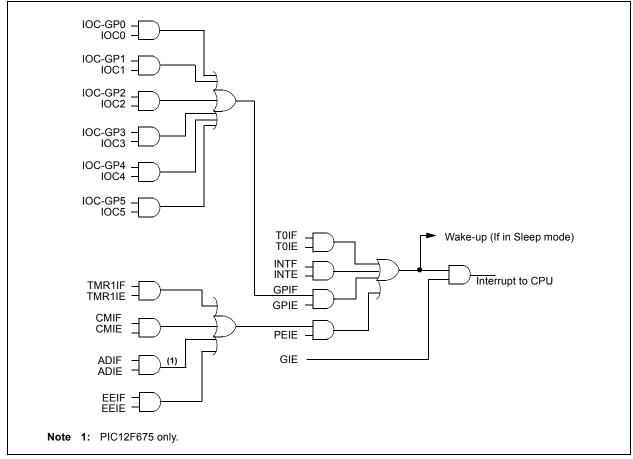

#### FIGURE 9-10: INTERRUPT LOGIC

#### TABLE 10-2: PIC12F629/675 INSTRUCTION SET

| Mnemonic,<br>Operands |      | Description                                        | Cycles     |        | 14-Bit | Opcode | Status | Notes    |       |

|-----------------------|------|----------------------------------------------------|------------|--------|--------|--------|--------|----------|-------|

|                       |      | Description                                        |            | MSb    |        |        | LSb    | Affected | Notes |

|                       |      | BYTE-ORIENTED FILE RE                              | GISTER OPE | RATIC  | NS     |        |        |          |       |

| ADDWF                 | f, d | Add W and f                                        | 1          | 00     | 0111   | dfff   | ffff   | C,DC,Z   | 1,2   |

| ANDWF                 | f, d | AND W with f                                       | 1          | 00     | 0101   | dfff   | ffff   | Z        | 1,2   |

| CLRF                  | f    | Clear f                                            | 1          | 00     | 0001   | lfff   | ffff   | Z        | 2     |

| CLRW                  | -    | Clear W                                            | 1          | 00     | 0001   | 0xxx   | xxxx   | Z        |       |

| COMF                  | f, d | Complement f                                       | 1          | 00     | 1001   | dfff   | ffff   | Z        | 1,2   |

| DECF                  | f, d | Decrement f                                        | 1          | 00     | 0011   | dfff   | ffff   | Z        | 1,2   |

| DECFSZ                | f, d | Decrement f, Skip if 0                             | 1(2)       | 00     | 1011   | dfff   | ffff   |          | 1,2,3 |

| INCF                  | f, d | Increment f                                        | 1          | 00     | 1010   | dfff   | ffff   | Z        | 1,2   |

| INCFSZ                | f, d | Increment f, Skip if 0                             | 1(2)       | 00     | 1111   | dfff   | ffff   |          | 1,2,3 |

| IORWF                 | f, d | Inclusive OR W with f                              | 1          | 00     | 0100   | dfff   | ffff   | Z        | 1,2   |

| MOVF                  | f, d | Move f                                             | 1          | 00     | 1000   | dfff   | ffff   | Z        | 1,2   |

| MOVWF                 | f    | Move W to f                                        | 1          | 00     | 0000   | lfff   | ffff   |          |       |

| NOP                   | -    | No Operation                                       | 1          | 00     | 0000   | 0xx0   | 0000   |          |       |

| RLF                   | f, d | Rotate Left f through Carry                        | 1          | 00     | 1101   |        | ffff   | С        | 1,2   |

| RRF                   | f, d | Rotate Right f through Carry                       | 1          | 00     | 1100   |        | ffff   | Ċ        | 1,2   |

| SUBWF                 | f, d | Subtract W from f                                  | 1          | 00     | 0010   |        | ffff   | C,DC,Z   | 1,2   |

| SWAPF                 | f, d | Swap nibbles in f                                  | 1          | 00     | 1110   |        | ffff   | 0,20,2   | 1,2   |

| XORWF                 | f, d | Exclusive OR W with f                              | 1          | 00     | 0110   | dfff   | ffff   | Z        | 1,2   |

| -                     | , -  | BIT-ORIENTED FILE REC                              |            | RATION |        |        |        |          | ,     |

| BCF                   | f, b | Bit Clear f                                        | 1          | 01     | 00bb   | bfff   | ffff   |          | 1,2   |

| BSF                   | f, b | Bit Set f                                          | 1          | 01     |        | bfff   |        |          | 1,2   |

| BTFSC                 | f, b | Bit Test f, Skip if Clear                          | 1 (2)      | 01     | 10bb   | bfff   | ffff   |          | 3     |

| BTFSS                 | f, b | Bit Test f, Skip if Set                            | 1 (2)      | 01     |        | bfff   |        |          | 3     |

| DIF33                 | Ι, Β | LITERAL AND CONTI                                  | ( )        |        | ddil   | DIII   | LLLL   |          | 3     |

| ADDLW                 | Ŀ    | Add literal and W                                  |            |        |        |        |        | C,DC,Z   |       |

|                       | k    |                                                    | 1          | 11     |        | kkkk   |        |          |       |

| ANDLW                 | k    | AND literal with W                                 |            | 11     | 1001   |        |        | Z        |       |

|                       | k    | Call subroutine                                    | 2          | 10     |        | kkkk   |        | TO,PD    |       |

| CLRWDT                | -    | Clear Watchdog Timer                               | 1          | 00     | 0000   | 0110   | 0100   | TO,PD    |       |

| GOTO                  | k    | Go to address                                      | 2          | 10     |        | kkkk   |        | -        |       |

| IORLW                 | k    | Inclusive OR literal with W                        | 1          | 11     | 1000   |        | kkkk   | Z        |       |

| MOVLW                 | k    | Move literal to W                                  | 1          | 11     |        | kkkk   |        |          |       |

| RETFIE                | -    | Return from interrupt                              | 2          | 00     | 0000   | 0000   | 1001   |          |       |

| RETLW                 | k    | Return with literal in W                           | 2          | 11     |        | kkkk   |        |          |       |

| RETURN                | -    | Return from Subroutine                             | 2          | 00     | 0000   | 0000   | 1000   |          |       |

| SLEEP                 | -    | Go into Standby mode                               | 1          | 00     | 0000   | 0110   | 0011   | TO,PD    |       |

| SUBLW                 | k    | Subtract W from literal                            | 1          | 11     |        | kkkk   | kkkk   | C,DC,Z   |       |

| XORLW                 | k    | Exclusive OR literal with W                        | 1          | 11     | 1010   | kkkk   | kkkk   | Z        |       |

| Note 1:               |      | /O register is modified as a function of itself (e |            |        |        |        |        |          |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF GPIO, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

3: If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**Note:** Additional information on the mid-range instruction set is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

NOTES:

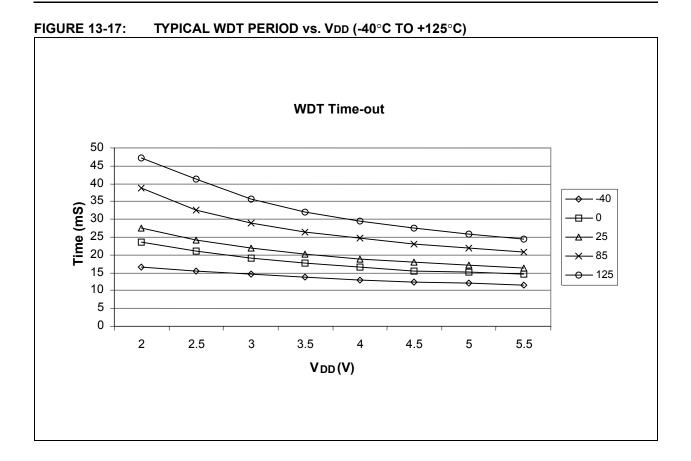

### TABLE 12-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT DETECT REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                                                 | Min        | Тур†      | Max         | Units    | Conditions                                       |

|--------------|-------|----------------------------------------------------------------|------------|-----------|-------------|----------|--------------------------------------------------|

| 30           | TMCL  | MCLR Pulse Width (low)                                         | 2<br>TBD   | <br>TBD   | <br>TBD     | μs<br>ms | VDD = 5V, -40°C to +85°C<br>Extended temperature |

| 31           | Twdt  | Watchdog Timer Time-out<br>Period<br>(No Prescaler)            | 10<br>10   | 17<br>17  | 25<br>30    | ms<br>ms | VDD = 5V, -40°C to +85°C<br>Extended temperature |

| 32           | Tost  | Oscillation Start-up Timer<br>Period                           | —          | 1024Tosc  | _           |          | Tosc = OSC1 period                               |

| 33*          | TPWRT | Power-up Timer Period                                          | 28*<br>TBD | 72<br>TBD | 132*<br>TBD | ms<br>ms | VDD = 5V, -40°C to +85°C<br>Extended Temperature |

| 34           | Tioz  | I/O High-impedance from<br>MCLR Low or Watchdog Timer<br>Reset | —          | _         | 2.0         | μS       |                                                  |

|              | BVDD  | Brown-out Detect Voltage                                       | 2.025      | —         | 2.175       | V        |                                                  |

|              |       | Brown-out Hysteresis                                           | TBD        | —         |             | —        |                                                  |

| 35           | TBOD  | Brown-out Detect Pulse Width                                   | 100*       |           | —           | μS       | $VDD \le BVDD$ (D005)                            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

SLEEP instruction to be executed.

| TABLE 12-9: | PIC12F675 A/D CONVERSION REQUIREMENTS |

|-------------|---------------------------------------|

|             |                                       |

| Param<br>No. | Sym  | Characteristic                                                        | Min      | Тур†   | Мах  | Units | Conditions                                                                                                                                                                                                                 |

|--------------|------|-----------------------------------------------------------------------|----------|--------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D Clock Period                                                      | 1.6      | —      | —    | μS    | Tosc based, VREF $\geq 3.0V$                                                                                                                                                                                               |

|              |      |                                                                       | 3.0*     | —      | —    | μS    | Tosc based, VREF full range                                                                                                                                                                                                |

| 130          | Tad  | A/D Internal RC<br>Oscillator Period                                  | 3.0*     | 6.0    | 9.0* | μs    | ADCS<1:0> = 11 (RC mode)<br>At VDD = 2.5V                                                                                                                                                                                  |

|              |      |                                                                       | 2.0*     | 4.0    | 6.0* | μS    | At VDD = 5.0V                                                                                                                                                                                                              |

| 131          | TCNV | Conversion Time<br>(not including<br>Acquisition Time) <sup>(1)</sup> | _        | 11     | _    | Tad   | Set GO bit to new data in A/D result register                                                                                                                                                                              |

| 132          | TACQ | Acquisition Time                                                      | (Note 2) | 11.5   | —    | μs    |                                                                                                                                                                                                                            |

|              |      |                                                                       | 5*       | _      | _    | μs    | The minimum time is the amplifier<br>settling time. This may be used if the<br>"new" input voltage has not changed<br>by more than 1 LSb (i.e., 4.1 mV @<br>4.096V) from the last sampled<br>voltage (as stored on CHOLD). |

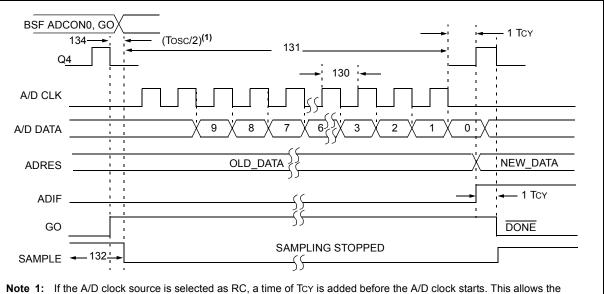

| 134          | TGO  | Q4 to A/D Clock<br>Start                                              | _        | Tosc/2 | _    | -     | If the A/D clock source is selected as RC, a time of TCY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                                           |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: ADRES register may be read on the following TCY cycle.

2: See Section 7.1 "A/D Configuration and Operation" for minimum conditions.

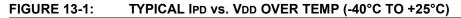

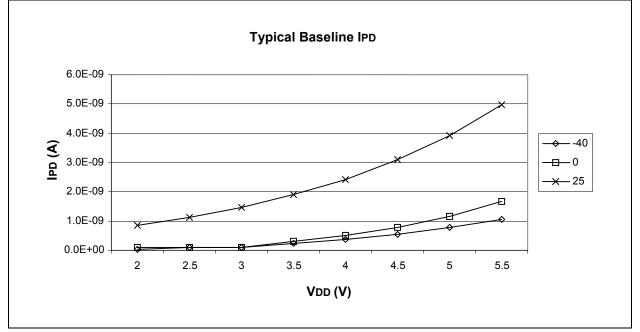

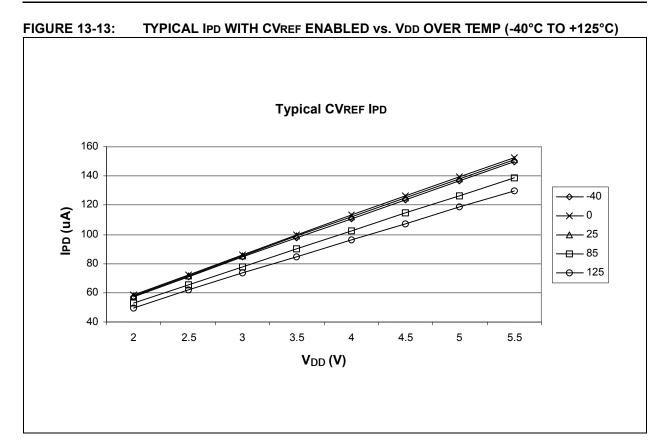

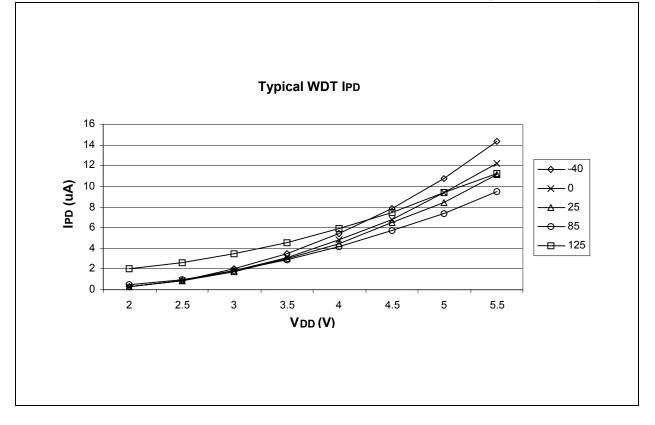

#### 13.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for design guidance and are not tested.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

The data presented in this section is a **statistical summary** of data collected on units from different lots over a period of time and matrix samples. "Typical" represents the mean of the distribution at 25°C. "Max" or "min" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation, over the whole temperature range.

FIGURE 13-14: TYPICAL IPD WITH WDT ENABLED vs. VDD OVER TEMP (-40°C TO +125°C)

#### 14.0 PACKAGING INFORMATION

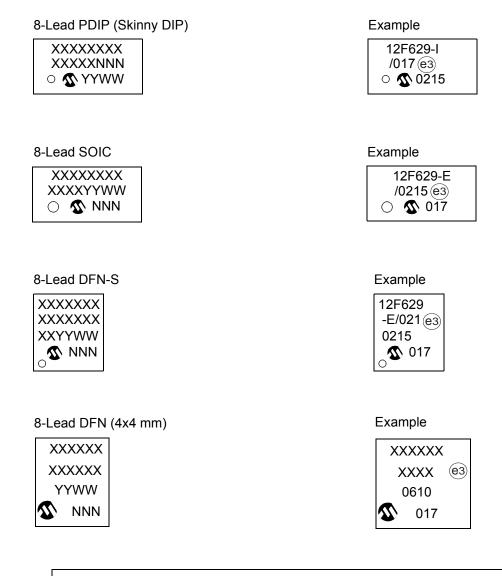

#### 14.1 Package Marking Information

| Legend | I: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|--------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carrie                                 | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>s for customer-specific information.                                                                                                                                                                                            |