Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 5                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 128 x 8                                                                 |

| RAM Size                   | 64 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 4x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 8-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f675-i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 8-Pin Flash-Based 8-Bit CMOS Microcontroller

#### High-Performance RISC CPU:

- Only 35 Instructions to Learn

- All single-cycle instructions except branches

- · Operating Speed:

- DC 20 MHz oscillator/clock input

- DC 200 ns instruction cycle

- Interrupt Capability

- 8-Level Deep Hardware Stack

- · Direct, Indirect, and Relative Addressing modes

#### **Special Microcontroller Features:**

- Internal and External Oscillator Options

- Precision Internal 4 MHz oscillator factory calibrated to ±1%

- External Oscillator support for crystals and resonators

- 5 µs wake-up from Sleep, 3.0V, typical

- Power-Saving Sleep mode

- Wide Operating Voltage Range 2.0V to 5.5V

- Industrial and Extended Temperature Range

- Low-Power Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- · Brown-out Detect (BOD)

- Watchdog Timer (WDT) with Independent Oscillator for Reliable Operation

- Multiplexed MCLR/Input Pin

- Interrupt-on-Pin Change

- Individual Programmable Weak Pull-ups

- Programmable Code Protection

- High Endurance Flash/EEPROM Cell

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- Flash/Data EEPROM Retention: > 40 years

### Low-Power Features:

- Standby Current:

- 1 nA @ 2.0V, typical

- Operating Current:

- 8.5 μA @ 32 kHz, 2.0V, typical

- 100 μA @ 1 MHz, 2.0V, typical

- Watchdog Timer Current

300 nA @ 2.0V, typical

- 300 TA @ 2.00, typical

- Timer1 Oscillator Current:

- 4 μA @ 32 kHz, 2.0V, typical

#### **Peripheral Features:**

- · 6 I/O Pins with Individual Direction Control

- High Current Sink/Source for Direct LED Drive

- Analog Comparator module with:

- One analog comparator

- Programmable on-chip comparator voltage reference (CVREF) module

- Programmable input multiplexing from device inputs

- Comparator output is externally accessible

- Analog-to-Digital Converter module (PIC12F675):

- 10-bit resolution

- Programmable 4-channel input

- Voltage reference input

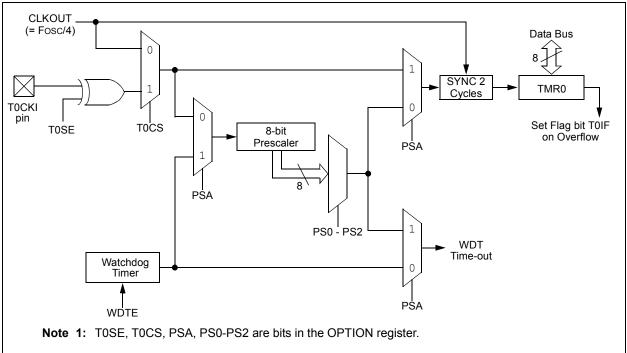

- Timer0: 8-Bit Timer/Counter with 8-Bit Programmable Prescaler

- Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Gate Input mode

- Option to use OSC1 and OSC2 in LP mode as Timer1 oscillator, if INTOSC mode selected

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via two pins

| Device    | Program<br>Memory | Data Memory     |             | I/O | 10-bit A/D | Comparators | Timers   |  |

|-----------|-------------------|-----------------|-------------|-----|------------|-------------|----------|--|

| Device    | Flash<br>(words)  | SRAM<br>(bytes) | SRAM EEPROM |     | (ch)       | Comparators | 8/16-bit |  |

| PIC12F629 | 1024              | 64              | 128         | 6   | -          | 1           | 1/1      |  |

| PIC12F675 | 1024              | 64              | 128         | 6   | 4          | 1           | 1/1      |  |

\* 8-bit, 8-pin devices protected by Microchip's Low Pin Count Patent: U.S. Patent No. 5,847,450. Additional U.S. and foreign patents and applications may be issued or pending.

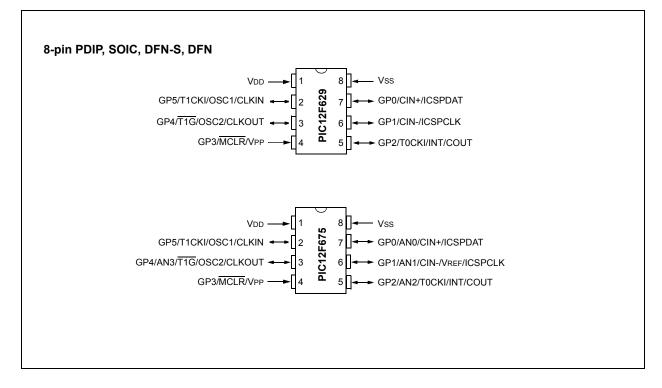

#### **Pin Diagrams**

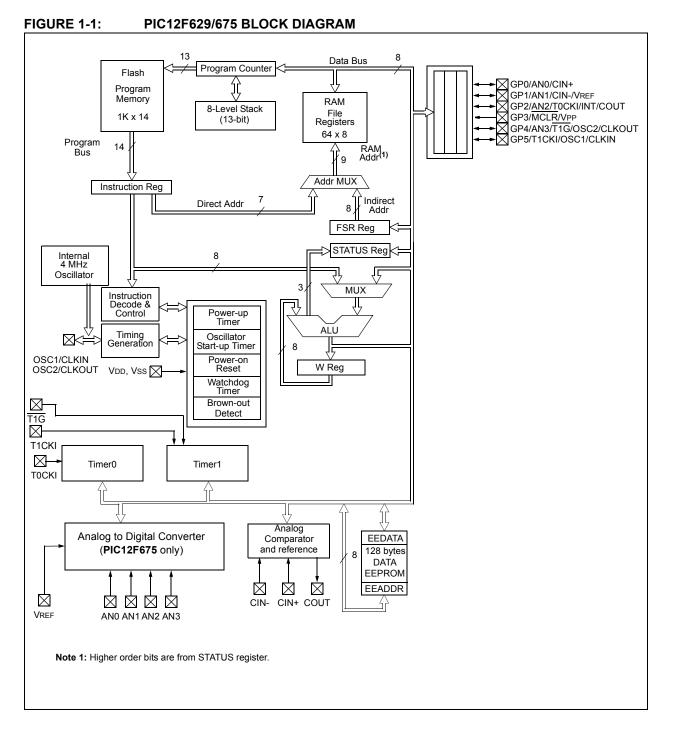

### 1.0 DEVICE OVERVIEW

This document contains device specific information for the PIC12F629/675. Additional information may be found in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip web site. The Reference Manual should be considered a complementary document to this Data Sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

The PIC12F629 and PIC12F675 devices are covered by this Data Sheet. They are identical, except the PIC12F675 has a 10-bit A/D converter. They come in 8-pin PDIP, SOIC, MLF-S and DFN packages. Figure 1-1 shows a block diagram of the PIC12F629/ 675 devices. Table 1-1 shows the pinout description.

| Address | Name                  | Bit 7              | Bit 6                    | Bit 5          | Bit 4         | Bit 3           | Bit 2          | Bit 1         | Bit 0   | Value on<br>POR, BOD | Page  |

|---------|-----------------------|--------------------|--------------------------|----------------|---------------|-----------------|----------------|---------------|---------|----------------------|-------|

| Bank 1  |                       |                    |                          |                |               |                 |                |               |         |                      |       |

| 80h     | INDF <sup>(1)</sup>   | Addressing         | this Location            | uses Conter    | nts of FSR to | Address Dat     | ta Memory      |               |         | 0000 0000            | 20,61 |

| 81h     | OPTION_REG            | GPPU               | INTEDG                   | TOCS           | TOSE          | PSA             | PS2            | PS1           | PS0     | 1111 1111            | 14,31 |

| 82h     | PCL                   | Program Co         | ounter's (PC)            | Least Signifi  | icant Byte    |                 |                |               |         | 0000 0000            | 19    |

| 83h     | STATUS                | IRP <sup>(2)</sup> | RP1 <sup>(2)</sup>       | RP0            | TO            | PD              | Z              | DC            | С       | 0001 1xxx            | 14    |

| 84h     | FSR                   | Indirect Data      | a Memory Ad              | dress Pointe   | er            |                 |                | •             |         | xxxx xxxx            | 20    |

| 85h     | TRISIO                | —                  | _                        | TRISI05        | TRISIO4       | TRISI03         | TRISIO2        | TRISIO1       | TRISIO0 | 11 1111              | 21    |

| 86h     | _                     | Unimpleme          | nted                     |                | •             | •               |                | •             | •       | —                    | _     |

| 87h     | _                     | Unimpleme          | nted                     |                |               |                 |                |               |         | _                    | _     |

| 88h     | _                     | Unimpleme          | nted                     |                |               |                 |                |               |         | _                    | _     |

| 89h     | _                     | Unimpleme          | nted                     |                |               |                 |                |               |         | _                    | _     |

| 8Ah     | PCLATH                | _                  | —                        | _              | Write Buffer  | for Upper 5     | bits of Progra | am Counter    |         | 0 0000               | 19    |

| 8Bh     | INTCON                | GIE                | PEIE                     | T0IE           | INTE          | GPIE            | T0IF           | INTF          | GPIF    | 0000 0000            | 15    |

| 8Ch     | PIE1                  | EEIE               | ADIE                     | —              | _             | CMIE            | _              | -             | TMR1IE  | 0000                 | 16    |

| 8Dh     | -                     | Unimpleme          | Jnimplemented            |                |               |                 |                |               |         | —                    | _     |

| 8Eh     | PCON                  | _                  | _                        | _              | _             | _               | _              | POR           | BOD     | 0x                   | 18    |

| 8Fh     | —                     | Unimpleme          | nted                     |                |               |                 |                |               |         | _                    | —     |

| 90h     | OSCCAL                | CAL5               | CAL4                     | CAL3           | CAL2          | CAL1            | CAL0           | _             | _       | 1000 00              | 18    |

| 91h     | —                     | Unimpleme          | nted                     |                |               |                 |                |               |         | —                    | —     |

| 92h     | —                     | Unimpleme          | nted                     |                |               |                 |                |               |         | —                    | —     |

| 93h     | —                     | Unimpleme          | nted                     |                |               |                 |                |               |         | —                    | —     |

| 94h     | —                     | Unimpleme          | nted                     |                |               |                 |                |               |         | —                    | —     |

| 95h     | WPU                   | —                  | —                        | WPU5           | WPU4          | —               | WPU2           | WPU1          | WPU0    | 11 -111              | 21    |

| 96h     | IOC                   | —                  | —                        | IOC5           | IOC4          | IOC3            | IOC2           | IOC1          | IOC0    | 00 0000              | 23    |

| 97h     | —                     | Unimpleme          | nted                     |                |               |                 |                |               |         | —                    | —     |

| 98h     | —                     | Unimpleme          | nted                     |                |               |                 |                |               |         | —                    | —     |

| 99h     | VRCON                 | VREN               | —                        | VRR            | _             | VR3             | VR2            | VR1           | VR0     | 0-0- 0000            | 42    |

| 9Ah     | EEDATA                | Data EEPR          | OM Data Reg              | gister         |               |                 |                |               |         | 0000 0000            | 49    |

| 9Bh     | EEADR                 | —                  | Data EEPR                | OM Address     | Register      |                 |                |               |         | -000 0000            | 49    |

| 9Ch     | EECON1                | _                  | — — — WRERR WREN WR RD   |                |               |                 |                |               |         | x000                 | 50    |

| 9Dh     | EECON2 <sup>(1)</sup> | EEPROM C           | EPROM Control Register 2 |                |               |                 |                |               |         |                      | 50    |

| 9Eh     | ADRESL <sup>(3)</sup> | Least Signif       | icant 2 bits o           | f the Left Shi | fted A/D Res  | ult of 8 bits o | r the Right S  | hifted Result |         | xxxx xxxx            | 44    |

| 9Fh     | ANSEL <sup>(3)</sup>  | _                  | ADCS2                    | ADCS1          | ADCS0         | ANS3            | ANS2           | ANS1          | ANS0    | -000 1111            | 46,61 |

### TABLE 2-1: SPECIAL FUNCTION REGISTERS SUMMARY (CONTINUED)

Legend: — = unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note 1:** This is not a physical register.

2: These bits are reserved and should always be maintained as '0'.

3: PIC12F675 only.

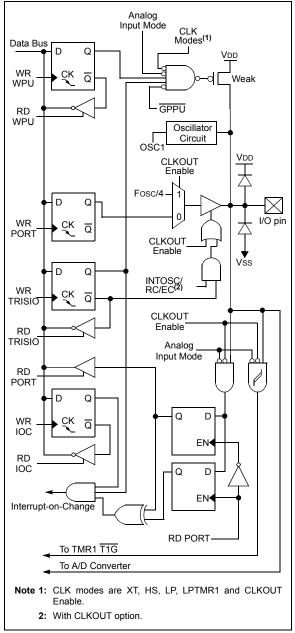

#### GP4/AN3/T1G/OSC2/CLKOUT 3.3.5

Figure 3-4 shows the diagram for this pin. The GP4 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the A/D (PIC12F675 only)

- a TMR1 gate input

- · a crystal/resonator connection

- · a clock output

#### FIGURE 3-4: **BLOCK DIAGRAM OF GP4**

#### 3.3.6 GP5/T1CKI/OSC1/CLKIN

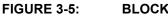

Figure 3-5 shows the diagram for this pin. The GP5 pin is configurable to function as one of the following:

- a general purpose I/O

- · a TMR1 clock input

- · a crystal/resonator connection

- · a clock input

#### **BLOCK DIAGRAM OF GP5**

NOTES:

### 7.3 A/D Operation During Sleep

The A/D converter module can operate during Sleep. This requires the A/D clock source to be set to the internal RC oscillator. When the RC clock source is selected, the A/D waits one instruction before starting the conversion. This allows the SLEEP instruction to be executed, thus eliminating much of the switching noise from the conversion. When the conversion is complete, the GO/DONE bit is cleared, and the result is loaded into the ADRESH:ADRESL registers. If the A/D interrupt is enabled, the device awakens from Sleep. If the A/D interrupt is not enabled, the A/D module is turned off, although the ADON bit remains set. When the A/D clock source is something other than RC, a SLEEP instruction causes the present conversion to be aborted, and the A/D module is turned off. The ADON bit remains set.

#### 7.4 Effects of Reset

A device Reset forces all registers to their Reset state. Thus the A/D module is turned off and any pending conversion is aborted. The ADRESH:ADRESL registers are unchanged.

| Address  | Name   | Bit 7                                                                                         | Bit 6          | Bit 5          | Bit 4         | Bit 3          | Bit 2        | Bit 1      | Bit 0   | Value on<br>POR,<br>BOD | Value on<br>all other<br>Resets |

|----------|--------|-----------------------------------------------------------------------------------------------|----------------|----------------|---------------|----------------|--------------|------------|---------|-------------------------|---------------------------------|

| 05h      | GPIO   | —                                                                                             | _              | GPIO5          | GPIO4         | GPIO3          | GPIO2        | GPI01      | GPIO0   | xx xxxx                 | uu uuuu                         |

| 0Bh, 8Bh | INTCON | GIE                                                                                           | PEIE           | T0IE           | INTE          | GPIE           | T0IF         | INTF       | GPIF    | 0000 0000               | 0000 000u                       |

| 0Ch      | PIR1   | EEIF                                                                                          | ADIF           | —              |               | CMIF           | —            | _          | TMR1IF  | 00 00                   | 00 00                           |

| 1Eh      | ADRESH | Most Signif                                                                                   | icant 8 bits c | of the Left Sh | ifted A/D res | sult or 2 bits | of the Right | Shifted Re | esult   | XXXX XXXX               | սսսս սսսս                       |

| 1Fh      | ADCON0 | ADFM                                                                                          | VCFG           | —              | -             | CHS1           | CHS0         | GO         | ADON    | 00 0000                 | 00 0000                         |

| 85h      | TRISIO | _                                                                                             | _              | TRISI05        | TRISIO4       | TRISIO3        | TRISIO2      | TRISIO1    | TRISI00 | 11 1111                 | 11 1111                         |

| 8Ch      | PIE1   | EEIE                                                                                          | ADIE           | —              | _             | CMIE           | —            | _          | TMR1IE  | 00 00                   | 00 00                           |

| 9Eh      | ADRESL | Least Significant 2 bits of the Left Shifted A/D Result or 8 bits of the Right Shifted Result |                |                |               |                |              |            |         | XXXX XXXX               | uuuu uuuu                       |

| 9Fh      | ANSEL  | _                                                                                             | ADCS2          | ADCS1          | ADCS0         | ANS3           | ANS2         | ANS1       | ANS0    | -000 1111               | -000 1111                       |

|          |        |                                                                                               |                |                |               |                |              |            |         |                         |                                 |

#### TABLE 7-2: SUMMARY OF A/D REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D converter module.

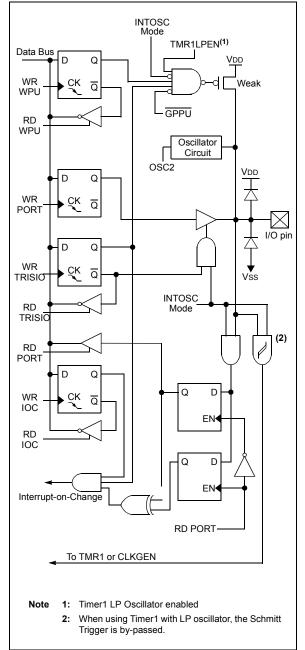

#### 9.2.3 EXTERNAL CLOCK IN

For applications where a clock is already available elsewhere, users may directly drive the PIC12F629/ 675 provided that this external clock source meets the AC/DC timing requirements listed in **Section 12.0 "Electrical Specifications"**. Figure 9-2 shows how an external clock circuit should be configured.

#### 9.2.4 RC OSCILLATOR

For applications where precise timing is not a requirement, the RC oscillator option is available. The operation and functionality of the RC oscillator is dependent upon a number of variables. The RC oscillator frequency is a function of:

- · Supply voltage

- Resistor (REXT) and capacitor (CEXT) values

- Operating temperature.

The oscillator frequency will vary from unit to unit due to normal process parameter variation. The difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to account for the tolerance of the external R and C components. Figure 9-3 shows how the R/C combination is connected.

Two options are available for this Oscillator mode which allow GP4 to be used as a general purpose I/O or to output Fosc/4.

#### FIGURE 9-3: RC OSCILLATOR MODE

#### 9.2.5 INTERNAL 4 MHz OSCILLATOR

When calibrated, the internal oscillator provides a fixed 4 MHz (nominal) system clock. See Electrical Specifications, **Section 12.0** "Electrical Specifications", for information on variation over voltage and temperature.

Two options are available for this Oscillator mode which allow GP4 to be used as a general purpose I/O or to output Fosc/4.

#### 9.2.5.1 Calibrating the Internal Oscillator

A calibration instruction is programmed into the last location of program memory. This instruction is a RETLW XX, where the literal is the calibration value. The literal is placed in the OSCCAL register to set the calibration of the internal oscillator. Example 9-1 demonstrates how to calibrate the internal oscillator. For best operation, decouple (with capacitance) VDD and Vss as close to the device as possible.

**Note:** Erasing the device will also erase the preprogrammed internal calibration value for the internal oscillator. The calibration value must be saved prior to erasing part as specified in the PIC12F629/675 Programming specification. Microchip Development Tools maintain all Calibration bits to factory settings.

#### EXAMPLE 9-1: CALIBRATING THE INTERNAL OSCILLATOR

| BSF<br>CALL<br>MOVWF | STATUS,<br>3FFh<br>OSCCAL |     | ;Bank 1<br>;Get the cal value<br>;Calibrate |

|----------------------|---------------------------|-----|---------------------------------------------|

| BCF                  | STATUS,                   | RP0 | ;Bank 0                                     |

|                      |                           |     |                                             |

#### 9.2.6 CLKOUT

The PIC12F629/675 devices can be configured to provide a clock out signal in the INTOSC and RC oscillator modes. When configured, the oscillator frequency divided by four (Fosc/4) is output on the GP4/OSC2/CLKOUT pin. Fosc/4 can be used for test purposes or to synchronize other logic.

#### 9.3 Reset

The PIC12F629/675 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- WDT Reset during Sleep C)

- MCLR Reset during normal operation d)

- e) MCLR Reset during Sleep

- Brown-out Detect (BOD) f)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- · Power-on Reset

- MCLR Reset

- · WDT Reset

- · WDT Reset during Sleep

- · Brown-out Detect (BOD) Reset

They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations as indicated in Table 9-4. These bits are used in software to determine the nature of the Reset. See Table 9-7 for a full description of Reset states of all registers.

A simplified block diagram of the on-chip Reset Circuit is shown in Figure 9-4.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See Table 12-4 in Electrical Specifications Section for pulse-width specification.

FIGURE 9-4: External Reset MCLR/ VPP pin SLEEF WDT WDT Module Time-out Reset VDD Rise Detect Power-on Reset סס Brown-out Detect S Q BODEN OST/PWRT OST Chip\_Reset 10-bit Ripple Counter Q R OSC1/ CLKIN pin PWRT On-chip<sup>(1</sup> 10-bit Ripple Counter RC OSC Enable PWRT See Table 9-3 for time-out situations. Enable OST Note 1: This is a separate oscillator from the INTOSC/EC oscillator.

#### SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

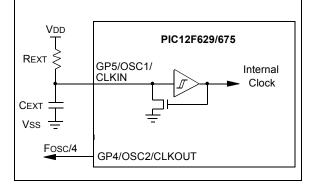

#### 9.3.1 MCLR

It should be noted that a WDT Reset does not drive MCLR pin low.

The behavior of the ESD protection on the MCLR pin has been altered from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 9-5, is suggested.

An internal MCLR option is enabled by setting the MCLRE bit in the Configuration Word. When enabled, MCLR is internally tied to VDD. No internal pull-up option is available for the MCLR pin.

#### FIGURE 9-5: RECOMMENDED MCLR CIRCUIT

#### 9.3.2 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, simply tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details (see Section 12.0 "Electrical Specifications"). If the BOD is enabled, the maximum rise time specification does not apply. The BOD circuitry will keep the device in Reset until VDD reaches VBOD (see Section 9.3.5 "Brown-Out Detect (BOD)").

| Note: | The POR circuit does not produce a | in |

|-------|------------------------------------|----|

|       | internal Reset when VDD declines.  |    |

When the device starts normal operation (exits the Reset condition), device operating parameters (i.e., voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

#### 9.3.3 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from POR or Brown-out Detect. The Power-up Timer operates on an internal RC oscillator. The chip is kept in Reset as long as PWRT is active. The PWRT delay allows the <u>VDD to</u> rise to an acceptable level. A Configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should always be enabled when Brown-out Detect is enabled.

The Power-up Time delay will vary from chip to chip and due to:

- VDD variation

- Temperature variation

- · Process variation.

See DC parameters for details (Section 12.0 "Electrical Specifications").

#### 9.3.4 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from Sleep.

#### TABLE 9-9: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOD | Value on all<br>other<br>Resets |

|---------|--------------|-------|--------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| 81h     | OPTION_REG   | GPPU  | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   | 1111 1111            | 1111 1111                       |

| 2007h   | Config. bits | CP    | BODEN  | MCLRE | PWRTE | WDTE  | F0SC2 | F0SC1 | F0SC0 | uuuu uuuu            | uuuu uuuu                       |

**Legend:** u = Unchanged, shaded cells are not used by the Watchdog Timer.

| XORLW            | Exclusive OR Literal with W                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |

| Status Affected: | Z                                                                                                                          |

| Description:     | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |

| XORWF            | Exclusive OR W with f                                                                                                                                                                   |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                              |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                      |  |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                               |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                       |  |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the<br>W register with register 'f'. If 'd' is<br>0, the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'. |  |  |  |  |  |  |

#### 11.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

#### 11.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

#### 11.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

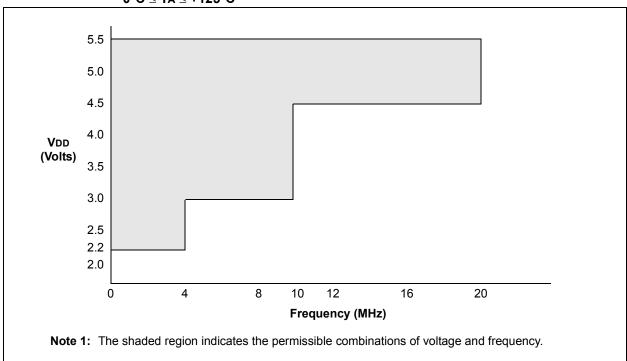

FIGURE 12-3: PIC12F675 WITH A/D ENABLED VOLTAGE-FREQUENCY GRAPH, 0°C  $\leq$  Ta  $\leq$  +125°C

#### DC Characteristics: PIC12F629/675-I (Industrial), PIC12F629/675-E (Extended) 12.1

| Param                                         |      |                                                                  | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array}$ |      |                                        |                  |                                                                                                                                                            |  |  |

|-----------------------------------------------|------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| No.                                           | Sym  | Characteristic                                                   | Min                                                                                                                                                                                                                                                        | Тур† | Max                                    | Units            | Conditions                                                                                                                                                 |  |  |

| V<br>D001<br>D001A<br>D001B<br>D001C<br>D001D | VDD  | Supply Voltage                                                   | 2.0<br>2.2<br>2.5<br>3.0<br>4.5                                                                                                                                                                                                                            |      | 5.5<br>5.5<br>5.5<br>5.5<br>5.5<br>5.5 | V<br>V<br>V<br>V | Fosc < = 4 MHz:<br>PIC12F629/675 with A/D off<br>PIC12F675 with A/D on, 0°C to +125°C<br>PIC12F675 with A/D on, -40°C to +125°C<br>4 MHz < Fosc < = 10 MHz |  |  |

| D002 V                                        | VDR  | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | 1.5*                                                                                                                                                                                                                                                       | —    | —                                      | V                | Device in Sleep mode                                                                                                                                       |  |  |

| D003 V                                        | VPOR | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | _                                                                                                                                                                                                                                                          | Vss  | _                                      | V                | See section on Power-on Reset for details                                                                                                                  |  |  |

| D004 S                                        | Svdd | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05*                                                                                                                                                                                                                                                      | _    | _                                      | V/ms             | See section on Power-on Reset for details                                                                                                                  |  |  |

| D005 V                                        | Vвор |                                                                  | —                                                                                                                                                                                                                                                          | 2.1  |                                        | V                |                                                                                                                                                            |  |  |

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

|       |                        |     |      | perating ( |       |            | <b>ss otherwise stated)</b><br>+85°C for industrial |  |

|-------|------------------------|-----|------|------------|-------|------------|-----------------------------------------------------|--|

| Param | Device Characteristics | Min | Typ† | Мах        | Units | Conditions |                                                     |  |

| No.   | Device Characteristics |     | iypi | WIAN       | Units | VDD        | Note                                                |  |

| D010  | Supply Current (IDD)   | _   | 9    | 16         | μA    | 2.0        | Fosc = 32 kHz                                       |  |

|       |                        | —   | 18   | 28         | μA    | 3.0        | LP Oscillator Mode                                  |  |

|       |                        | —   | 35   | 54         | μA    | 5.0        |                                                     |  |

| D011  |                        | —   | 110  | 150        | μA    | 2.0        | Fosc = 1 MHz                                        |  |

|       |                        | _   | 190  | 280        | μA    | 3.0        | XT Oscillator Mode                                  |  |

|       |                        | _   | 330  | 450        | μA    | 5.0        |                                                     |  |

| D012  |                        | —   | 220  | 280        | μA    | 2.0        | Fosc = 4 MHz                                        |  |

|       |                        | —   | 370  | 650        | μA    | 3.0        | XT Oscillator Mode                                  |  |

|       |                        | —   | 0.6  | 1.4        | mA    | 5.0        |                                                     |  |

| D013  |                        | —   | 70   | 110        | μA    | 2.0        | Fosc = 1 MHz                                        |  |

|       |                        | _   | 140  | 250        | μA    | 3.0        | EC Oscillator Mode                                  |  |

|       |                        | _   | 260  | 390        | μA    | 5.0        |                                                     |  |

| D014  |                        | —   | 180  | 250        | μA    | 2.0        | Fosc = 4 MHz                                        |  |

|       |                        | —   | 320  | 470        | μA    | 3.0        | EC Oscillator Mode                                  |  |

|       |                        | _   | 580  | 850        | μA    | 5.0        |                                                     |  |

| D015  |                        | _   | 340  | 450        | μA    | 2.0        | Fosc = 4 MHz                                        |  |

|       |                        |     | 500  | 700        | μA    | 3.0        | INTOSC Mode                                         |  |

|       |                        | _   | 0.8  | 1.1        | mA    | 5.0        |                                                     |  |

| D016  |                        | _   | 180  | 250        | μA    | 2.0        | Fosc = 4 MHz                                        |  |

|       |                        |     | 320  | 450        | μA    | 3.0        | EXTRC Mode                                          |  |

|       |                        | _   | 580  | 800        | μA    | 5.0        | 7                                                   |  |

| D017  |                        | _   | 2.1  | 2.95       | mA    | 4.5        | Fosc = 20 MHz                                       |  |

|       |                        | _   | 2.4  | 3.0        | mA    | 5.0        | HS Oscillator Mode                                  |  |

### 12.2 DC Characteristics: PIC12F629/675-I (Industrial)

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in Active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

#### 12.8 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| Z. TPPS |                                      |     |                |

|---------|--------------------------------------|-----|----------------|

| т       |                                      |     |                |

| F       | Frequency                            | Т   | Time           |

| Lowerc  | ase letters (pp) and their meanings: |     |                |

| рр      |                                      |     |                |

| сс      | CCP1                                 | osc | OSC1           |

| ck      | CLKOUT                               | rd  | RD             |

| CS      | CS                                   | rw  | RD or WR       |

| di      | SDI                                  | sc  | SCK            |

| do      | SDO                                  | SS  | SS             |

| dt      | Data in                              | tO  | TOCKI          |

| io      | I/O port                             | t1  | T1CKI          |

| mc      | MCLR                                 | wr  | WR             |

| Upperc  | ase letters and their meanings:      |     |                |

| S       |                                      |     |                |

| F       | Fall                                 | Р   | Period         |

| н       | High                                 | R   | Rise           |

| 1       | Invalid (High-Impedance)             | V   | Valid          |

| L       | Low                                  | Z   | High-Impedance |

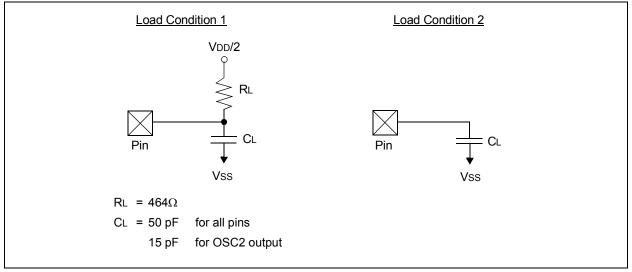

#### FIGURE 12-4: LOAD CONDITIONS

#### TABLE 12-6: COMPARATOR SPECIFICATIONS

| Comparator Specifications |                                           | Standard Operating Conditions<br>-40°C to +125°C (unless otherwise stated) |       |           |       |          |  |  |

|---------------------------|-------------------------------------------|----------------------------------------------------------------------------|-------|-----------|-------|----------|--|--|

| Sym                       | Characteristics                           | Min                                                                        | Тур   | Мах       | Units | Comments |  |  |

| Vos                       | Input Offset Voltage                      | _                                                                          | ± 5.0 | ± 10      | mV    |          |  |  |

| VCM                       | Input Common Mode Voltage                 | 0                                                                          |       | Vdd - 1.5 | V     |          |  |  |

| CMRR                      | Common Mode Rejection Ratio               | +55*                                                                       |       | —         | db    |          |  |  |

| Trt                       | Response Time <sup>(1)</sup>              | _                                                                          | 150   | 400*      | ns    |          |  |  |

| TMC2COV                   | Comparator Mode Change to<br>Output Valid | _                                                                          | _     | 10*       | μS    |          |  |  |

\* These parameters are characterized but not tested.

Note 1: Response time measured with one comparator input at (VDD - 1.5)/2 while the other input transitions from Vss to VDD - 1.5V.

#### TABLE 12-7: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| Voltage Reference Specifications |                              | Standard Operating Conditions<br>-40°C to +125°C (unless otherwise stated) |                   |                 |            |                                             |  |  |

|----------------------------------|------------------------------|----------------------------------------------------------------------------|-------------------|-----------------|------------|---------------------------------------------|--|--|

| Sym                              | Characteristics              | Min                                                                        | Тур               | Max             | Units      | Comments                                    |  |  |

|                                  | Resolution                   |                                                                            | VDD/24*<br>VDD/32 | _               | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |  |  |

|                                  | Absolute Accuracy            | _                                                                          | _                 | ± 1/2<br>± 1/2* | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |  |  |

|                                  | Unit Resistor Value (R)      | —                                                                          | 2k*               | _               | Ω          |                                             |  |  |

|                                  | Settling Time <sup>(1)</sup> | —                                                                          |                   | 10*             | μS         |                                             |  |  |

\* These parameters are characterized but not tested.

**Note 1:** Settling time measured while VRR = 1 and VR<3:0> transitions from 0000 to 1111.

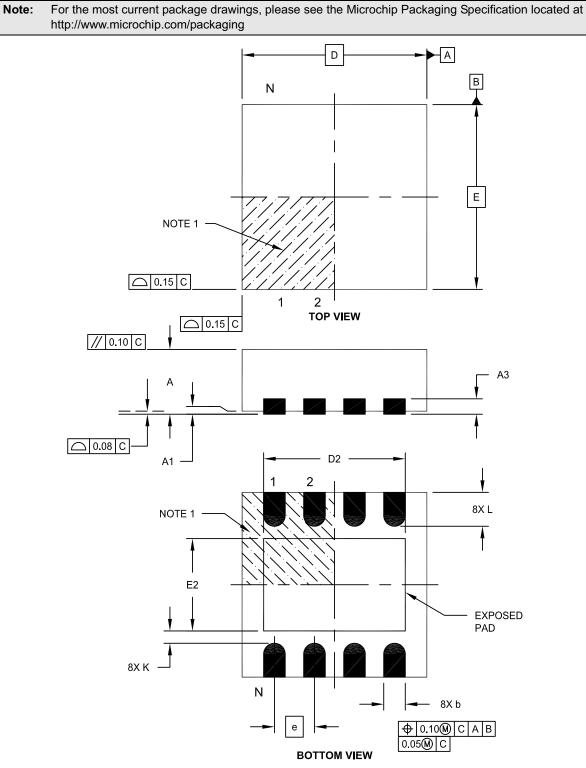

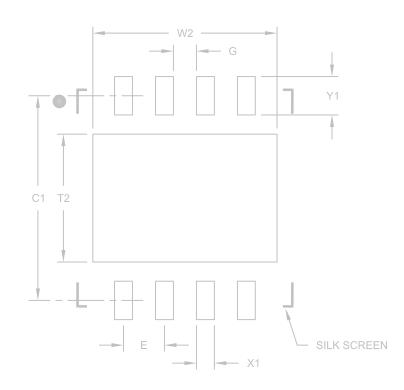

### 8-Lead Plastic Dual Flat, No Lead Package (MD) – 4x4x0.9 mm Body [DFN]

Microchip Technology Drawing C04-131E Sheet 1 of 2

### 8-Lead Plastic Dual Flat, No Lead Package (MD) – 4x4x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

| Units                      |    | MILLIMETERS |      |      |  |  |

|----------------------------|----|-------------|------|------|--|--|

| Dimension Limits           |    | MIN         | NOM  | MAX  |  |  |

| Contact Pitch              | E  | E 0.80 BSC  |      |      |  |  |

| Optional Center Pad Width  | W2 |             |      | 3.60 |  |  |

| Optional Center Pad Length | T2 |             |      | 2.50 |  |  |

| Contact Pad Spacing        | C1 |             | 4.00 |      |  |  |

| Contact Pad Width (X8)     | X1 |             |      | 0.35 |  |  |

| Contact Pad Length (X8)    | Y1 |             |      | 0.75 |  |  |

| Distance Between Pads      | G  | 0.45        |      |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2131B