# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 64 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-VDFN Exposed Pad                                                        |

| Supplier Device Package    | 8-DFN-S (6x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f675t-e-mf |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

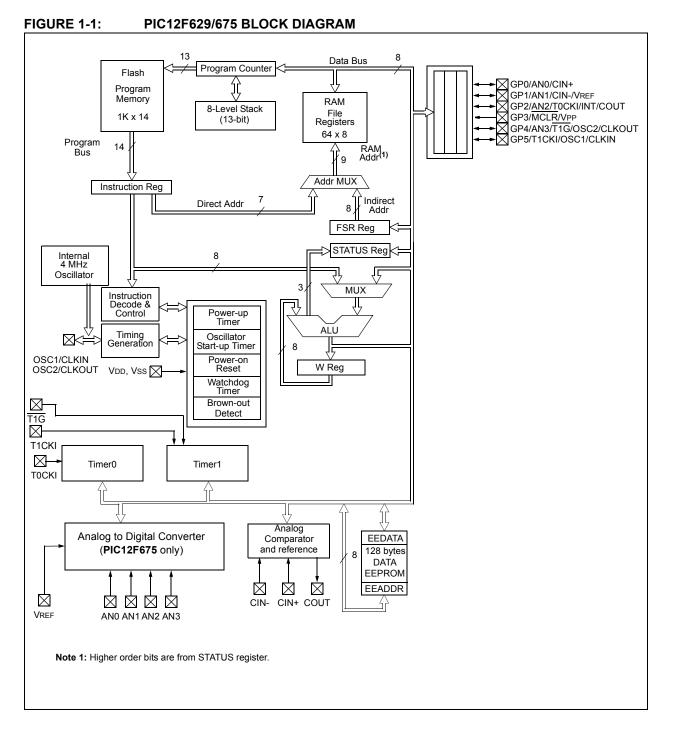

### 1.0 DEVICE OVERVIEW

This document contains device specific information for the PIC12F629/675. Additional information may be found in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip web site. The Reference Manual should be considered a complementary document to this Data Sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

The PIC12F629 and PIC12F675 devices are covered by this Data Sheet. They are identical, except the PIC12F675 has a 10-bit A/D converter. They come in 8-pin PDIP, SOIC, MLF-S and DFN packages. Figure 1-1 shows a block diagram of the PIC12F629/ 675 devices. Table 1-1 shows the pinout description.

### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (see Table 2-1). These registers are static RAM.

The special registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the "core" are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

#### FIGURE 2-2: DATA MEMORY MAP OF THE PIC12F629/675

|                                                       | THE F           | PIC12F629/675                 |                  |

|-------------------------------------------------------|-----------------|-------------------------------|------------------|

| ,                                                     | File<br>Address | A                             | File<br>ddress   |

| Indirect addr. <sup>(1)</sup>                         | 00h             | Indirect addr. <sup>(1)</sup> | 80h              |

| TMR0                                                  | 01h             | OPTION_REG                    | 81h              |

| PCL                                                   | 02h             | PCL                           | 82h              |

| STATUS                                                | 03h             | STATUS                        | 83h              |

| FSR                                                   | 04h             | FSR                           | 84h              |

| GPIO                                                  | 05h             | TRISIO                        | 85h              |

|                                                       | 06h             |                               | 86h              |

|                                                       | 07h             |                               | 87h              |

|                                                       | 08h             |                               | 88h              |

|                                                       | 09h             |                               | 89h              |

| PCLATH                                                | 0Ah             | PCLATH                        | 8Ah              |

| INTCON                                                | 0Bh             | INTCON                        | 8Bh              |

| PIR1                                                  | 0Ch             | PIE1                          | 8Ch              |

|                                                       | 0Dh             |                               | 8Dh              |

| TMR1L                                                 | 0Eh             | PCON                          | 8Eh              |

| TMR1H                                                 | 0Fh             |                               | 8Fh              |

| T1CON                                                 | 10h             | OSCCAL                        | 90h              |

|                                                       | 11h             |                               | 91h              |

|                                                       | 12h             |                               | 92h              |

|                                                       | 13h             |                               | 93h              |

|                                                       | 14h             |                               | 94h              |

|                                                       | 15h             | WPU                           | 95h              |

|                                                       | 16h             | IOC                           | 96h              |

|                                                       | 17h             |                               | 97h              |

|                                                       | 18h             |                               | 98h              |

| CMCON                                                 | 19h             | VRCON                         | 99h              |

|                                                       | 1Ah             | EEDATA                        | 9Ah              |

|                                                       | 1Bh             | EEADR                         | 9Bh              |

|                                                       | 1Ch             | EECON1                        | 9Ch              |

|                                                       | 1Dh             | EECON2 <sup>(1)</sup>         | 9Dh              |

| ADRESH <sup>(2)</sup>                                 | 1Eh             | ADRESL <sup>(2)</sup>         | 9Eh              |

| ADCON0 <sup>(2)</sup>                                 | 1Fh             | ANSEL <sup>(2)</sup>          | 9Fh              |

|                                                       | 20h             |                               | A0h              |

| General<br>Purpose<br>Registers<br>64 Bytes           |                 | accesses<br>20h-5Fh           |                  |

|                                                       | 5Fh             |                               | DFh              |

|                                                       | 60h             |                               | E0h              |

|                                                       |                 |                               |                  |

|                                                       |                 |                               |                  |

|                                                       | 754             |                               | FFL              |

| Bank 0                                                | 7Fh             | Bank 1                        | FFh              |

| Danko                                                 |                 | Bank i                        |                  |

| Unimplementer<br>1: Not a physical<br>2: PIC12F675 on | register.       | mory locations, rea           | <b>d as</b> '0'. |

|                                                       |                 |                               |                  |

#### 2.2.2.5 PIR1 Register

The PIR1 register contains the interrupt flag bits, as shown in Register 2-5.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-5: PIR1: PERIPHERAL INTERRUPT REGISTER 1 (ADDRESS: 0Ch)

| R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | U-0 | U-0 | R/W-0  |

|-------|-------|-----|-----|-------|-----|-----|--------|

| EEIF  | ADIF  | —   | _   | CMIF  | —   | —   | TMR1IF |

| bit 7 |       |     |     |       |     |     | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | <b>EEIF:</b> EEPROM Write Operation Interrupt Flag bit<br>1 = The write operation completed (must be cleared in software)<br>0 = The write operation has not completed or has not been started |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | ADIF: A/D Converter Interrupt Flag bit (PIC12F675 only)                                                                                                                                        |

|         | <ul><li>1 = The A/D conversion is complete (must be cleared in software)</li><li>0 = The A/D conversion is not complete</li></ul>                                                              |

| bit 5-4 | Unimplemented: Read as '0'                                                                                                                                                                     |

| bit 3   | CMIF: Comparator Interrupt Flag bit                                                                                                                                                            |

|         | <ul> <li>1 = Comparator input has changed (must be cleared in software)</li> <li>0 = Comparator input has not changed</li> </ul>                                                               |

| bit 2-1 | Unimplemented: Read as '0'                                                                                                                                                                     |

| bit 0   | TMR1IF: TMR1 Overflow Interrupt Flag bit                                                                                                                                                       |

|         | 1 = TMR1 register overflowed (must be cleared in software)                                                                                                                                     |

0 = TMR1 register did not overflow

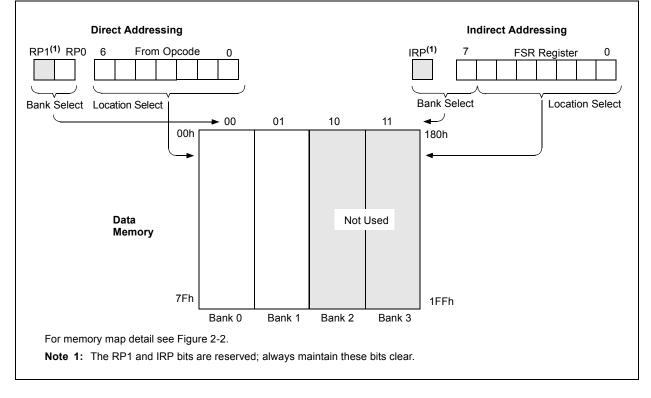

#### 2.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-2.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 2-1.

#### EXAMPLE 2-1: INDIRECT ADDRESSING

|          | MOVLW | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ;to RAM              |

| NEXT     | CLRF  | INDF  | ;clear INDF register |

|          | INCF  | FSR   | ;inc pointer         |

|          | BTFSS | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;no clear next       |

| CONTINUE |       |       | ;yes continue        |

|          |       |       |                      |

#### FIGURE 2-2: DIRECT/INDIRECT ADDRESSING PIC12F629/675

| Address | Name       | Bit 7 | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR,<br>BOD | Value on all<br>other<br>Resets |

|---------|------------|-------|--------|---------|---------|---------|---------|---------|---------|-------------------------|---------------------------------|

| 05h     | GPIO       |       | —      | GP5     | GP4     | GP3     | GP2     | GP1     | GP0     | xx xxxx                 | uu uuuu                         |

| 0Bh/8Bh | INTCON     | GIE   | PEIE   | T0IE    | INTE    | GPIE    | T0IF    | INTF    | GPIF    | 0000 0000               | 0000 000u                       |

| 19h     | CMCON      | _     | COUT   | _       | CINV    | CIS     | CM2     | CM1     | CM0     | -0-0 0000               | -0-0 0000                       |

| 81h     | OPTION_REG | GPPU  | INTEDG | TOCS    | T0SE    | PSA     | PS2     | PS1     | PS0     | 1111 1111               | 1111 1111                       |

| 85h     | TRISIO     | _     | —      | TRISIO5 | TRISIO4 | TRISIO3 | TRISIO2 | TRISIO1 | TRISI00 | 11 1111                 | 11 1111                         |

| 95h     | WPU        | _     | _      | WPU5    | WPU4    | _       | WPU2    | WPU1    | WPU0    | 11 -111                 | 11 -111                         |

| 96h     | IOC        | —     | _      | IOC5    | IOC4    | IOC3    | IOC2    | IOC1    | IOC0    | 00 0000                 | 00 0000                         |

| 9Fh     | ANSEL      | _     | ADCS2  | ADCS1   | ADCS0   | ANS3    | ANS2    | ANS1    | ANS0    | -000 1111               | -000 1111                       |

TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH GPIO

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by GPIO.

NOTES:

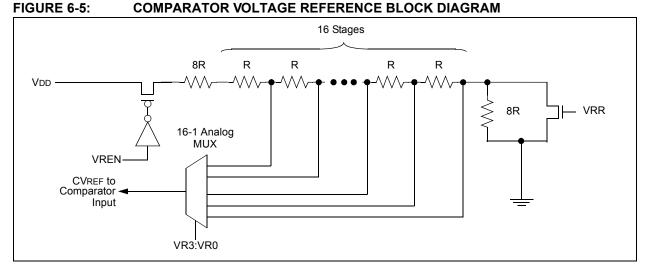

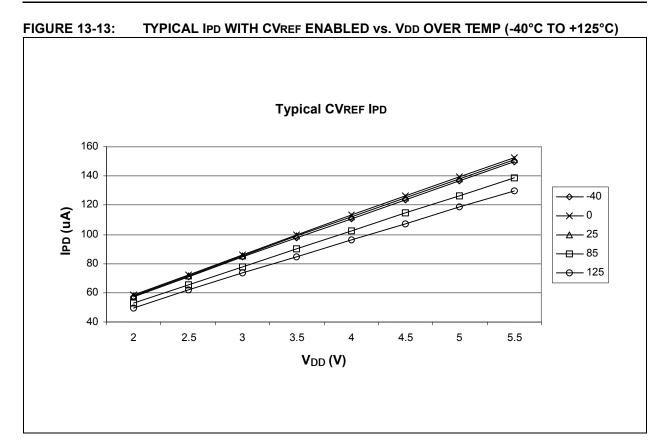

#### 6.5 Comparator Reference

The comparator module also allows the selection of an internally generated voltage reference for one of the comparator inputs. The internal reference signal is used for four of the eight Comparator modes. The VRCON register, Register 6-2, controls the voltage reference module shown in Figure 6-5.

## 6.5.1 CONFIGURING THE VOLTAGE REFERENCE

The voltage reference can output 32 distinct voltage levels, 16 in a high range and 16 in a low range.

The following equations determine the output voltages:

VRR = 1 (low range): CVREF = (VR3:VR0 / 24) x VDD VRR = 0 (high range): CVREF = (VDD / 4) + (VR3:VR0 x VDD / 32)

#### 6.5.2 VOLTAGE REFERENCE ACCURACY/ERROR

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 6-5) keep CVREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the Comparator Voltage Reference can be found in **Section 12.0 "Electrical Specifications"**.

#### 6.6 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output is ensured to have a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (Table 12-7).

### 6.7 Operation During Sleep

Both the comparator and voltage reference, if enabled before entering Sleep mode, remain active during Sleep. This results in higher Sleep currents than shown in the power-down specifications. The additional current consumed by the comparator and the voltage reference is shown separately in the specifications. To minimize power consumption while in Sleep mode, turn off the comparator, CM2:CM0 = 111, and voltage refeence, VRCON<7> = 0. While the comparator is enabled during Sleep, an interrupt will wake-up the device. If the device wakes up from Sleep, the contents of the CMCON and VRCON registers are not affected.

### 6.8 Effects of a Reset

A device Reset forces the CMCON and VRCON registers to their Reset states. This forces the comparator module to be in the Comparator Reset mode, CM2:CM0 = 000 and the voltage reference to its off state. Thus, all potential inputs are analog inputs with the comparator and voltage reference disabled to consume the smallest current possible.

#### TABLE 7-1: TAD vs. DEVICE OPERATING FREQUENCIES

| A/D Clock Source (TAD) |             | Device Frequency          |                           |                           |                           |  |  |

|------------------------|-------------|---------------------------|---------------------------|---------------------------|---------------------------|--|--|

| Operation              | ADCS2:ADCS0 | 20 MHz                    | 5 MHz                     | 4 MHz                     | 1.25 MHz                  |  |  |

| 2 Tosc                 | 000         | 100 ns <sup>(2)</sup>     | 400 ns <sup>(2)</sup>     | 500 ns <sup>(2)</sup>     | 1.6 μs                    |  |  |

| 4 Tosc                 | 100         | 200 ns <sup>(2)</sup>     | 800 ns <sup>(2)</sup>     | 1.0 μs <sup>(2)</sup>     | 3.2 μs                    |  |  |

| 8 Tosc                 | 001         | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 2.0 μs                    | 6.4 μs                    |  |  |

| 16 Tosc                | 101         | 800 ns <sup>(2)</sup>     | 3.2 μs                    | 4.0 μs                    | 12.8 μs <sup>(3)</sup>    |  |  |

| 32 Tosc                | 010         | 1.6 μs                    | 6.4 μs                    | 8.0 μs <sup>(3)</sup>     | 25.6 μs <sup>(3)</sup>    |  |  |

| 64 Tosc                | 110         | 3.2 μs                    | 12.8 μs <sup>(3)</sup>    | 16.0 μs <sup>(3)</sup>    | 51.2 μs <sup>(3)</sup>    |  |  |

| A/D RC                 | x11         | 2 - 6 μs <sup>(1,4)</sup> |  |  |

Legend: Shaded cells are outside of recommended range.

**Note 1:** The A/D RC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

- 2: These values violate the minimum required TAD time.

- 3: For faster conversion times, the selection of another clock source is recommended.

- 4: When the device frequency is greater than 1 MHz, the A/D RC clock source is only recommended if the conversion will be performed during Sleep.

#### 7.1.5 STARTING A CONVERSION

The A/D conversion is initiated by setting the GO/DONE bit (ADCON0<1>). When the conversion is complete, the A/D module:

- Clears the GO/DONE bit

- Sets the ADIF flag (PIR1<6>)

- Generates an interrupt (if enabled)

If the conversion must be aborted, the GO/DONE bit can be cleared in software. The ADRESH:ADRESL registers will not be updated with the partially complete A/D conversion sample. Instead, the ADRESH:ADRESL registers will retain the value of the

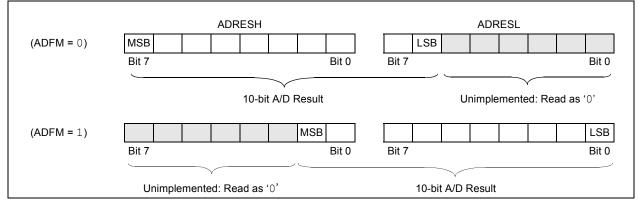

#### FIGURE 7-2: 10-BIT A/D RESULT FORMAT

previous conversion. After an aborted conversion, a 2 TAD delay is required before another acquisition can be initiated. Following the delay, an input acquisition is automatically started on the selected channel.

**Note:** The GO/DONE bit should not be set in the same instruction that turns on the A/D.

#### 7.1.6 CONVERSION OUTPUT

The A/D conversion can be supplied in two formats: left or right shifted. The ADFM bit (ADCON0<7>) controls the output format. Figure 7-2 shows the output formats.

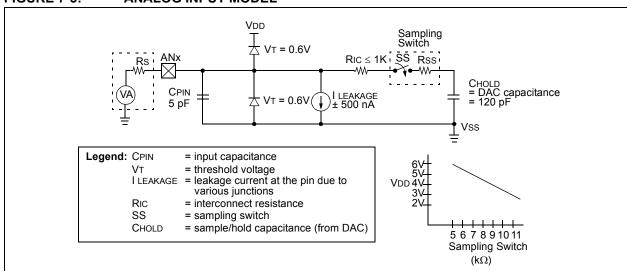

### 7.2 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 7-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 7-3. The maximum recommended impedance for analog sources is 10 k\Omega. As the impedance

#### EQUATION 7-1: ACQUISITION TIME

is decreased, the acquisition time may be decreased. After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 7-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

To calculate the minimum acquisition time, TACQ, see the  $PIC^{\textcircled{0}}$  Mid-Range Reference Manual (DS33023).

| TACQ | = Amplifier Settling Time +<br>Hold Capacitor Charging Time +<br>Temperature Coefficient                                                                                                      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Тс   | = TAMP + TC + TCOFF<br>= $2\mu s$ + TC + [(Temperature -25°C)(0.05 $\mu s$ /°C)]<br>= CHOLD (RIC + RSS + RS) In(1/2047)<br>= -120pF (1k $\Omega$ + 7k $\Omega$ + 10k $\Omega$ ) In(0.0004885) |

| TACQ | = $16.47\mu s$<br>= $2\mu s + 16.47\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$<br>= $19.72\mu s$                                                                              |

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- **2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 kΩ. This is required to meet the pin leakage specification.

#### 9.2.3 EXTERNAL CLOCK IN

For applications where a clock is already available elsewhere, users may directly drive the PIC12F629/ 675 provided that this external clock source meets the AC/DC timing requirements listed in **Section 12.0 "Electrical Specifications"**. Figure 9-2 shows how an external clock circuit should be configured.

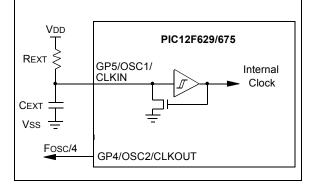

#### 9.2.4 RC OSCILLATOR

For applications where precise timing is not a requirement, the RC oscillator option is available. The operation and functionality of the RC oscillator is dependent upon a number of variables. The RC oscillator frequency is a function of:

- · Supply voltage

- Resistor (REXT) and capacitor (CEXT) values

- Operating temperature.

The oscillator frequency will vary from unit to unit due to normal process parameter variation. The difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to account for the tolerance of the external R and C components. Figure 9-3 shows how the R/C combination is connected.

Two options are available for this Oscillator mode which allow GP4 to be used as a general purpose I/O or to output Fosc/4.

#### FIGURE 9-3: RC OSCILLATOR MODE

#### 9.2.5 INTERNAL 4 MHz OSCILLATOR

When calibrated, the internal oscillator provides a fixed 4 MHz (nominal) system clock. See Electrical Specifications, **Section 12.0** "Electrical Specifications", for information on variation over voltage and temperature.

Two options are available for this Oscillator mode which allow GP4 to be used as a general purpose I/O or to output Fosc/4.

#### 9.2.5.1 Calibrating the Internal Oscillator

A calibration instruction is programmed into the last location of program memory. This instruction is a RETLW XX, where the literal is the calibration value. The literal is placed in the OSCCAL register to set the calibration of the internal oscillator. Example 9-1 demonstrates how to calibrate the internal oscillator. For best operation, decouple (with capacitance) VDD and Vss as close to the device as possible.

**Note:** Erasing the device will also erase the preprogrammed internal calibration value for the internal oscillator. The calibration value must be saved prior to erasing part as specified in the PIC12F629/675 Programming specification. Microchip Development Tools maintain all Calibration bits to factory settings.

#### EXAMPLE 9-1: CALIBRATING THE INTERNAL OSCILLATOR

| BSF<br>CALL<br>MOVWF | STATUS,<br>3FFh<br>OSCCAL |     | ;Bank 1<br>;Get the cal value<br>;Calibrate |

|----------------------|---------------------------|-----|---------------------------------------------|

| BCF                  | STATUS,                   | RP0 | ;Bank 0                                     |

|                      |                           |     |                                             |

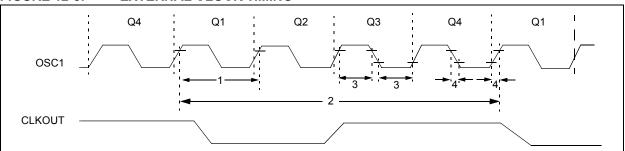

#### 9.2.6 CLKOUT

The PIC12F629/675 devices can be configured to provide a clock out signal in the INTOSC and RC oscillator modes. When configured, the oscillator frequency divided by four (Fosc/4) is output on the GP4/OSC2/CLKOUT pin. Fosc/4 can be used for test purposes or to synchronize other logic.

#### 9.3 Reset

The PIC12F629/675 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- WDT Reset during Sleep C)

- MCLR Reset during normal operation d)

- e) MCLR Reset during Sleep

- Brown-out Detect (BOD) f)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- · Power-on Reset

- MCLR Reset

- · WDT Reset

- · WDT Reset during Sleep

- · Brown-out Detect (BOD) Reset

They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations as indicated in Table 9-4. These bits are used in software to determine the nature of the Reset. See Table 9-7 for a full description of Reset states of all registers.

A simplified block diagram of the on-chip Reset Circuit is shown in Figure 9-4.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See Table 12-4 in Electrical Specifications Section for pulse-width specification.

FIGURE 9-4: External Reset MCLR/ VPP pin SLEEF WDT WDT Module Time-out Reset VDD Rise Detect Power-on Reset סס Brown-out Detect S Q BODEN OST/PWRT OST Chip\_Reset 10-bit Ripple Counter Q R OSC1/ CLKIN pin PWRT On-chip<sup>(1</sup> 10-bit Ripple Counter RC OSC Enable PWRT See Table 9-3 for time-out situations. Enable OST Note 1: This is a separate oscillator from the INTOSC/EC oscillator.

#### SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

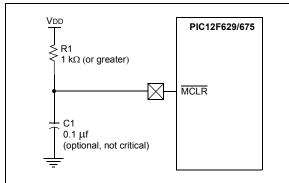

### 9.3.1 MCLR

It should be noted that a WDT Reset does not drive MCLR pin low.

The behavior of the ESD protection on the MCLR pin has been altered from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 9-5, is suggested.

An internal MCLR option is enabled by setting the MCLRE bit in the Configuration Word. When enabled, MCLR is internally tied to VDD. No internal pull-up option is available for the MCLR pin.

#### FIGURE 9-5: RECOMMENDED MCLR CIRCUIT

#### 9.3.2 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, simply tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details (see Section 12.0 "Electrical Specifications"). If the BOD is enabled, the maximum rise time specification does not apply. The BOD circuitry will keep the device in Reset until VDD reaches VBOD (see Section 9.3.5 "Brown-Out Detect (BOD)").

| Note: | The POR circuit does not produce a | in |

|-------|------------------------------------|----|

|       | internal Reset when VDD declines.  |    |

When the device starts normal operation (exits the Reset condition), device operating parameters (i.e., voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

#### 9.3.3 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from POR or Brown-out Detect. The Power-up Timer operates on an internal RC oscillator. The chip is kept in Reset as long as PWRT is active. The PWRT delay allows the <u>VDD to</u> rise to an acceptable level. A Configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should always be enabled when Brown-out Detect is enabled.

The Power-up Time delay will vary from chip to chip and due to:

- VDD variation

- Temperature variation

- · Process variation.

See DC parameters for details (Section 12.0 "Electrical Specifications").

#### 9.3.4 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from Sleep.

### 12.9 AC CHARACTERISTICS: PIC12F629/675 (INDUSTRIAL, EXTENDED)

#### FIGURE 12-5: EXTERNAL CLOCK TIMING

#### TABLE 12-1: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                          | Min   | Typ† | Max      | Units | Conditions                         |

|--------------|-------|-----------------------------------------|-------|------|----------|-------|------------------------------------|

|              | Fosc  | External CLKIN Frequency <sup>(1)</sup> | DC    | _    | 37       | kHz   | LP Osc mode                        |

|              |       |                                         | DC    | _    | 4        | MHz   | XT mode                            |

|              |       |                                         | DC    | _    | 20       | MHz   | HS mode                            |

|              |       |                                         | DC    | _    | 20       | MHz   | EC mode                            |

|              |       | Oscillator Frequency <sup>(1)</sup>     | 5     | _    | 37       | kHz   | LP Osc mode                        |

|              |       |                                         | —     | 4    | —        | MHz   | INTOSC mode                        |

|              |       |                                         | DC    | —    | 4        | MHz   | RC Osc mode                        |

|              |       |                                         | 0.1   | —    | 4        | MHz   | XT Osc mode                        |

|              |       |                                         | 1     | _    | 20       | MHz   | HS Osc mode                        |

| 1            | Tosc  | External CLKIN Period <sup>(1)</sup>    | 27    | _    | ×        | μS    | LP Osc mode                        |

|              |       |                                         | 50    | —    | $\infty$ | ns    | HS Osc mode                        |

|              |       |                                         | 50    | —    | $\infty$ | ns    | EC Osc mode                        |

|              |       |                                         | 250   | —    | $\infty$ | ns    | XT Osc mode                        |

|              |       | Oscillator Period <sup>(1)</sup>        | 27    |      | 200      | μS    | LP Osc mode                        |

|              |       |                                         | —     | 250  | —        | ns    | INTOSC mode                        |

|              |       |                                         | 250   | —    | —        | ns    | RC Osc mode                        |

|              |       |                                         | 250   | —    | 10,000   | ns    | XT Osc mode                        |

|              |       |                                         | 50    | —    | 1,000    | ns    | HS Osc mode                        |

| 2            | Тсү   | Instruction Cycle Time <sup>(1)</sup>   | 200   | TCY  | DC       | ns    | Tcy = 4/Fosc                       |

| 3            | TosL, | External CLKIN (OSC1) High              | 2*    | _    | —        | μS    | LP oscillator, Tosc L/H duty cycle |

|              | TosH  | External CLKIN Low                      | 20*   | —    | —        | ns    | HS oscillator, Tosc L/H duty       |

|              |       |                                         |       |      |          |       | cycle                              |

|              |       |                                         | 100 * | —    | —        | ns    | XT oscillator, Tosc L/H duty cycle |

| 4            | TosR, | External CLKIN Rise                     | —     | —    | 50*      | ns    | LP oscillator                      |

|              | TosF  | External CLKIN Fall                     | —     | —    | 25*      | ns    | XT oscillator                      |

|              |       |                                         | —     | —    | 15*      | ns    | HS oscillator                      |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to OSC1 pin. When an external clock input is used, the 'max' cycle time limit is "DC" (no clock) for all devices.

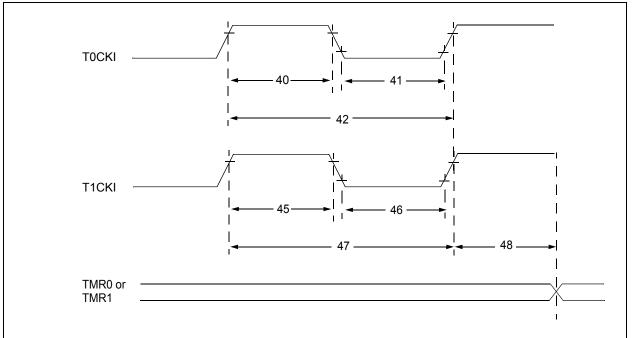

| Param<br>No. | Sym       | с                     | Characteristic                                    |                 | Min                                       | Тур† | Мах        | Units | Conditions                         |

|--------------|-----------|-----------------------|---------------------------------------------------|-----------------|-------------------------------------------|------|------------|-------|------------------------------------|

| 40*          | Tt0H      | T0CKI High Pulse      | OCKI High Pulse Width                             |                 | 0.5 Tcy + 20                              | —    | _          | ns    |                                    |

|              |           |                       |                                                   | With Prescaler  | 10                                        | —    |            | ns    |                                    |

| 41*          | Tt0L      | T0CKI Low Pulse Width |                                                   | No Prescaler    | 0.5 Tcy + 20                              | —    | _          | ns    |                                    |

|              |           |                       |                                                   | With Prescaler  | 10                                        | —    | _          | ns    |                                    |

| 42*          | TtOP      | T0CKI Period          |                                                   |                 | Greater of:<br>20 or <u>Tcy + 40</u><br>N | —    | _          | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H      | T1CKI High Time       | Synchronous, No Prescaler                         |                 | 0.5 Tcy + 20                              | _    | _          | ns    |                                    |

|              |           |                       | Synchronous,<br>with Prescaler                    |                 | 15                                        | —    |            | ns    |                                    |

|              |           |                       | Asynchronous                                      |                 | 30                                        | —    | _          | ns    |                                    |

| 46*          | Tt1L      | T1CKI Low Time        | Synchronous, No Prescaler                         |                 | 0.5 TCY + 20                              | —    | _          | ns    |                                    |

|              |           |                       | Synchronous,<br>with Prescaler                    |                 | 15                                        | -    | _          | ns    |                                    |

|              |           |                       | Asynchronous                                      |                 | 30                                        | —    |            | ns    |                                    |

| 47*          | Tt1P      | T1CKI Input<br>Period | Synchronous                                       |                 | Greater of:<br>30 or <u>Tcy + 40</u><br>N | -    | _          | ns    | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                       | Asynchronous                                      |                 | 60                                        | _    | _          | ns    |                                    |

|              | Ft1       |                       | nput frequency range<br>I by setting bit T1OSCEN) |                 | DC                                        | -    | 200*       | kHz   |                                    |

| 48           | TCKEZtmr1 | Delay from externa    | al clock edge to                                  | timer increment | 2 Tosc*                                   | —    | 7<br>Tosc* | —     |                                    |

These parameters are characterized but not tested.

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are t not tested.

| Param<br>No. | Sym  | Characteristic                                          | Min        | Тур†                      | Мах           | Units | Conditions                                                          |  |

|--------------|------|---------------------------------------------------------|------------|---------------------------|---------------|-------|---------------------------------------------------------------------|--|

| A01          | NR   | Resolution                                              | _          |                           | 10 bits       | bit   |                                                                     |  |

| A02          | Eabs | Total Absolute<br>Error*                                | _          | —                         | ±1            | LSb   | VREF = 5.0V                                                         |  |

| A03          | EIL  | Integral Error                                          |            | _                         | ±1            | LSb   | VREF = 5.0V                                                         |  |

| A04          | Edl  | Differential Error                                      | —          | —                         | ±1            | LSb   | No missing codes to 10 bits<br>VREF = 5.0V                          |  |

| A05          | Efs  | Full Scale Range                                        | 2.2*       | —                         | 5.5*          | V     |                                                                     |  |

| A06          | EOFF | Offset Error                                            | _          | —                         | ±1            | LSb   | VREF = 5.0V                                                         |  |

| A07          | Egn  | Gain Error                                              | _          | —                         | ±1            | LSb   | VREF = 5.0V                                                         |  |

| A10          | —    | Monotonicity                                            | _          | guaranteed <sup>(3)</sup> | —             | —     | $VSS \leq VAIN \leq VREF+$                                          |  |

| A20<br>A20A  | VREF | Reference Voltage                                       | 2.0<br>2.5 | _                         | <br>Vdd + 0.3 | V     | Absolute minimum to ensure 10-bit<br>accuracy                       |  |

| A21          | Vref | Reference V High<br>(VDD or VREF)                       | Vss        | —                         | Vdd           | V     |                                                                     |  |

| A25          | VAIN | Analog Input<br>Voltage                                 | Vss        | —                         | VREF          | V     |                                                                     |  |

| A30          | ZAIN | Recommended<br>Impedance of<br>Analog Voltage<br>Source | _          | _                         | 10            | kΩ    |                                                                     |  |

| A50          | IREF | VREF Input<br>Current <sup>(2)</sup>                    | 10         | -                         | 1000          | μA    | During VAIN acquisition.<br>Based on differential of VHOLD to VAIN. |  |

|              |      |                                                         |            | —                         | 10            | μA    | During A/D conversion cycle.                                        |  |

| TABLE 12-8: PIC12F6/5 A/D CONVERTER CHARACTERISTICS | <b>TABLE 12-8</b> : | PIC12F675 A/D CONVERTER CHARACTERISTICS: |

|-----------------------------------------------------|---------------------|------------------------------------------|

|-----------------------------------------------------|---------------------|------------------------------------------|

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from External VREF or VDD pin, whichever is selected as reference input.

3: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

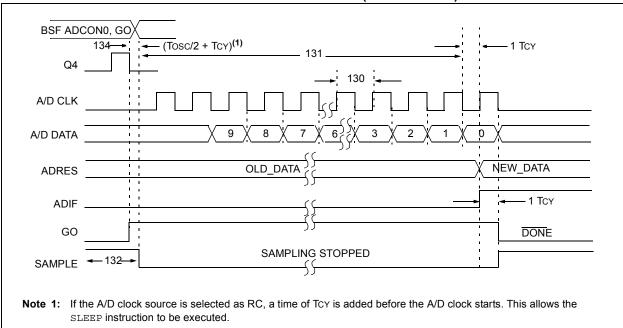

| FIGURE 12-11: | PIC12F675 A/D CONVERSION TIMING ( | SLEEP MODE) |

|---------------|-----------------------------------|-------------|

|               |                                   |             |

| Param<br>No. | Sym  | Characteristic                                                        | Min      | Тур†         | Max  | Units | Conditions                                                                                                                                                                                                                    |

|--------------|------|-----------------------------------------------------------------------|----------|--------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | Tad  | A/D Clock Period                                                      | 1.6      | —            | _    | μS    | $VREF \ge 3.0V$                                                                                                                                                                                                               |

|              |      |                                                                       | 3.0*     | —            |      | μS    | VREF full range                                                                                                                                                                                                               |

| 130          | Tad  | A/D Internal RC                                                       | 0.0*     |              | 0.0+ |       | ADCS<1:0> = 11 (RC mode)                                                                                                                                                                                                      |

|              |      | Oscillator Period                                                     | 3.0*     | 6.0          | 9.0* | μs    | At VDD = $2.5V$                                                                                                                                                                                                               |

|              |      |                                                                       | 2.0*     | 4.0          | 6.0* | μs    | At VDD = 5.0V                                                                                                                                                                                                                 |

| 131          | ΤΟΝΥ | Conversion Time<br>(not including<br>Acquisition Time) <sup>(1)</sup> | _        | 11           | _    | Tad   |                                                                                                                                                                                                                               |

| 132          | TACQ | Acquisition Time                                                      | (Note 2) | 11.5         | _    | μS    |                                                                                                                                                                                                                               |

|              |      |                                                                       | 5*       | _            | _    | μs    | The minimum time is the amplifier<br>settling time. This may be used if<br>the "new" input voltage has not<br>changed by more than 1 LSb (i.e.,<br>4.1 mV @ 4.096V) from the last<br>sampled voltage (as stored on<br>CHOLD). |

| 134          | TGO  | Q4 to A/D Clock<br>Start                                              |          | Tosc/2 + Tcy |      | _     | If the A/D clock source is selected<br>as RC, a time of TcY is added<br>before the A/D clock starts. This<br>allows the SLEEP instruction to be<br>executed.                                                                  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** ADRES register may be read on the following TCY cycle.

2: See Section 7.1 "A/D Configuration and Operation" for minimum conditions.

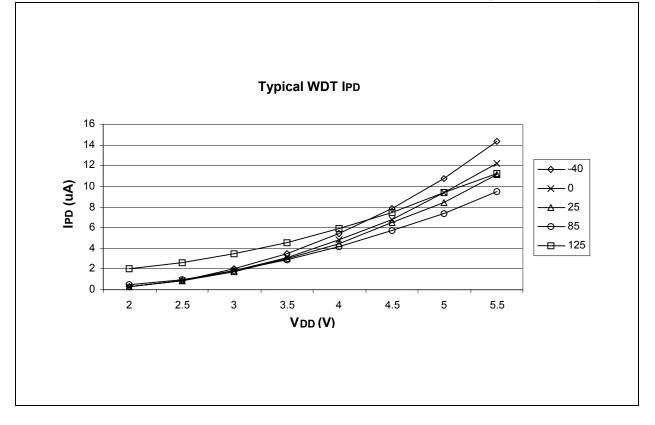

FIGURE 13-14: TYPICAL IPD WITH WDT ENABLED vs. VDD OVER TEMP (-40°C TO +125°C)

NOTES:

### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

### CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com, click on Customer Change Notification and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com

### **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:          | Technical Publications Manager         | Total Pages Sent                                       |

|--------------|----------------------------------------|--------------------------------------------------------|

| RE:          | Reader Response                        |                                                        |

| From         | n: Name                                |                                                        |

|              |                                        |                                                        |

|              | Address                                |                                                        |

|              | City / State / ZIP / Country           |                                                        |

|              | Telephone: ()                          | FAX: ()                                                |

| Appl         | ication (optional):                    |                                                        |

| Wou          | ld you like a reply?YN                 |                                                        |

| Devi         | ce: PIC12F629/675                      | Literature Number: DS41190G                            |

| Que          | stions:                                |                                                        |

| 1. \         | What are the best features of this do  | cument?                                                |

|              |                                        |                                                        |

| _            |                                        |                                                        |

| 2. ł         | How does this document meet your       | hardware and software development needs?               |

| _            |                                        |                                                        |

| -            |                                        |                                                        |

| 3. I         | Do you find the organization of this o | locument easy to follow? If not, why?                  |

| -            |                                        |                                                        |

| -            |                                        |                                                        |

| 4. \         | What additions to the document do y    | you think would enhance the structure and subject?     |

| -            |                                        |                                                        |

| -            |                                        |                                                        |

| 5. \         | What deletions from the document c     | ould be made without affecting the overall usefulness? |

| -            |                                        |                                                        |

| -            |                                        | aformation (what and what 10                           |

| 6. I         | s there any incorrect or misleading i  | nformation (what and where)?                           |

| -            |                                        |                                                        |

| -<br>7. I    | How would you improve this docume      | ant?                                                   |

| <i>ı</i> . 1 |                                        | ant :                                                  |

| -            |                                        |                                                        |

| -            |                                        |                                                        |