Welcome to **E-XFL.COM**

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 64 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

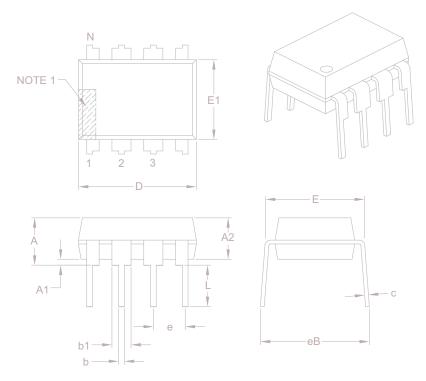

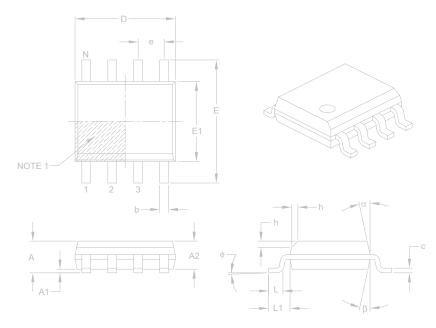

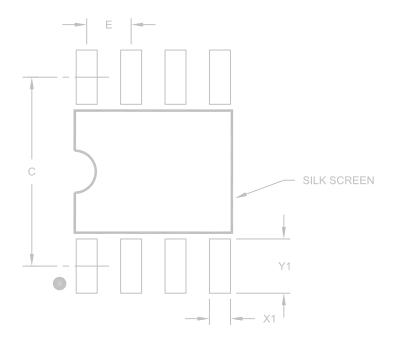

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                             |

| Supplier Device Package    | 8-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f675t-e-sn |

## 8-Pin Flash-Based 8-Bit CMOS Microcontroller

### **High-Performance RISC CPU:**

- · Only 35 Instructions to Learn

- All single-cycle instructions except branches

- · Operating Speed:

- DC 20 MHz oscillator/clock input

- DC 200 ns instruction cycle

- · Interrupt Capability

- · 8-Level Deep Hardware Stack

- · Direct, Indirect, and Relative Addressing modes

### **Special Microcontroller Features:**

- · Internal and External Oscillator Options

- Precision Internal 4 MHz oscillator factory calibrated to ±1%

- External Oscillator support for crystals and resonators

- 5 μs wake-up from Sleep, 3.0V, typical

- · Power-Saving Sleep mode

- Wide Operating Voltage Range 2.0V to 5.5V

- Industrial and Extended Temperature Range

- Low-Power Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Detect (BOD)

- Watchdog Timer (WDT) with Independent Oscillator for Reliable Operation

- Multiplexed MCLR/Input Pin

- · Interrupt-on-Pin Change

- · Individual Programmable Weak Pull-ups

- · Programmable Code Protection

- · High Endurance Flash/EEPROM Cell

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- Flash/Data EEPROM Retention: > 40 years

### **Low-Power Features:**

- · Standby Current:

- 1 nA @ 2.0V, typical

- · Operating Current:

- 8.5 μA @ 32 kHz, 2.0V, typical

- 100 μA @ 1 MHz, 2.0V, typical

- · Watchdog Timer Current

- 300 nA @ 2.0V, typical

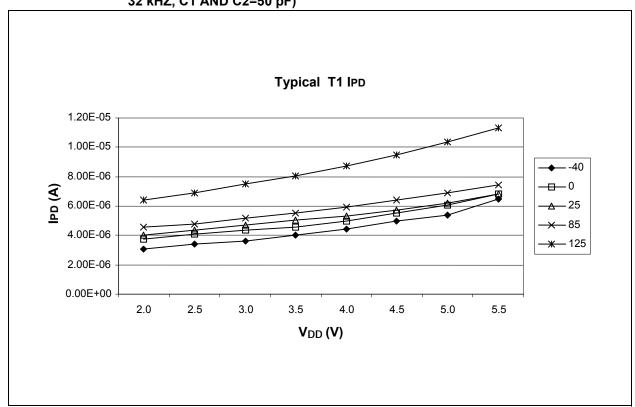

- · Timer1 Oscillator Current:

- 4 μA @ 32 kHz, 2.0V, typical

### **Peripheral Features:**

- · 6 I/O Pins with Individual Direction Control

- · High Current Sink/Source for Direct LED Drive

- · Analog Comparator module with:

- One analog comparator

- Programmable on-chip comparator voltage reference (CVREF) module

- Programmable input multiplexing from device inputs

- Comparator output is externally accessible

- Analog-to-Digital Converter module (PIC12F675):

- 10-bit resolution

- Programmable 4-channel input

- Voltage reference input

- Timer0: 8-Bit Timer/Counter with 8-Bit Programmable Prescaler

- · Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Gate Input mode

- Option to use OSC1 and OSC2 in LP mode as Timer1 oscillator, if INTOSC mode selected

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via two pins

| Device    | Program<br>Memory | Data Memory     |                   | - I/O | 10-bit A/D | Comparators | Timers   |

|-----------|-------------------|-----------------|-------------------|-------|------------|-------------|----------|

| Device    | Flash<br>(words)  | SRAM<br>(bytes) | EEPROM<br>(bytes) | 1/0   | (ch)       | Comparators | 8/16-bit |

| PIC12F629 | 1024              | 64              | 128               | 6     | _          | 1           | 1/1      |

| PIC12F675 | 1024              | 64              | 128               | 6     | 4          | 1           | 1/1      |

<sup>\* 8-</sup>bit, 8-pin devices protected by Microchip's Low Pin Count Patent: U.S. Patent No. 5,847,450. Additional U.S. and foreign patents and applications may be issued or pending.

### 2.2.2.3 INTCON Register

Legend:

R = Readable bit

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, GPIO port change and external GP2/INT pin interrupts.

Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER (ADDRESS: 0Bh OR 8Bh)

W = Writable bit

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | PEIE  | T0IE  | INTE  | GPIE  | T0IF  | INTF  | GPIF  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Note:

U = Unimplemented bit, read as '0'

| -n = Value | e at POR       | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | '0' = Bit is cleared              | x = Bit is unknown      |

|------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------|

|            |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   |                         |

| bit 7      |                | bal Interrupt Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                   |                         |

|            |                | bles all unmasked interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                   |                         |

| h:t C      |                | bles all interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                   |                         |

| bit 6      |                | eripheral Interrupt Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   |                         |

|            |                | ples all unmasked periphera<br>bles all peripheral interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                   |                         |

| bit 5      | TOIE: TN       | IR0 Overflow Interrupt Enab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ole bit                           |                         |

|            |                | oles the TMR0 interrupt bles the TMR0 interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   |                         |

| bit 4      | INTE: G        | P2/INT External Interrupt En                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nable bit                         |                         |

|            |                | bles the GP2/INT external ir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •                                 |                         |

|            |                | ables the GP2/INT external i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | '                                 |                         |

| bit 3      |                | ort Change Interrupt Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                   |                         |

|            |                | bles the GPIO port change in<br>ables the GPIO port change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •                                 |                         |

| bit 2      |                | 1R0 Overflow Interrupt Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •                                 |                         |

|            | 1 = TMF        | R0 register has overflowed (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | must be cleared in software)      |                         |

|            | 0 = TMF        | R0 register did not overflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                   |                         |

| bit 1      | INTF: G        | P2/INT External Interrupt Fla                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ag bit                            |                         |

|            |                | GP2/INT external interrupt of GP2/IN | occurred (must be cleared in a    | software)               |

| bit 0      |                | ort Change Interrupt Flag bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                   |                         |

| DIL U      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | :<br>iP0 pins changed state (must | he cleared in software) |

|            |                | e of the GP5:GP0 pins have                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                   | so dicarca in solwarc)  |

| Note 1:    | IOC register r | nust also be enabled to ena                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ble an interrupt-on-change.       |                         |

2: T0IF bit is set when TIMER0 rolls over. TIMER0 is unchanged on Reset and should be initialized before

clearing T0IF bit.

### 2.2.2.4 PIE1 Register

The PIE1 register contains the interrupt enable bits, as shown in Register 2-4.

**Note:** Bit PEIE (INTCON<6>) must be set to enable any peripheral interrupt.

### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1 (ADDRESS: 8Ch)

| R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | U-0 | U-0 | R/W-0  |

|-------|-------|-----|-----|-------|-----|-----|--------|

| EEIE  | ADIE  | _   | _   | CMIE  | _   | _   | TMR1IE |

| bit 7 |       |     |     |       |     |     | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7 **EEIE:** EE Write Complete Interrupt Enable bit 1 = Enables the EE write complete interrupt 0 = Disables the EE write complete interrupt ADIE: A/D Converter Interrupt Enable bit (PIC12F675 only) bit 6 1 = Enables the A/D converter interrupt 0 = Disables the A/D converter interrupt bit 5-4 Unimplemented: Read as '0' CMIE: Comparator Interrupt Enable bit bit 3 1 = Enables the comparator interrupt 0 = Disables the comparator interrupt bit 2-1 Unimplemented: Read as '0' bit 0 TMR1IE: TMR1 Overflow Interrupt Enable bit 1 = Enables the TMR1 overflow interrupt

0 = Disables the TMR1 overflow interrupt

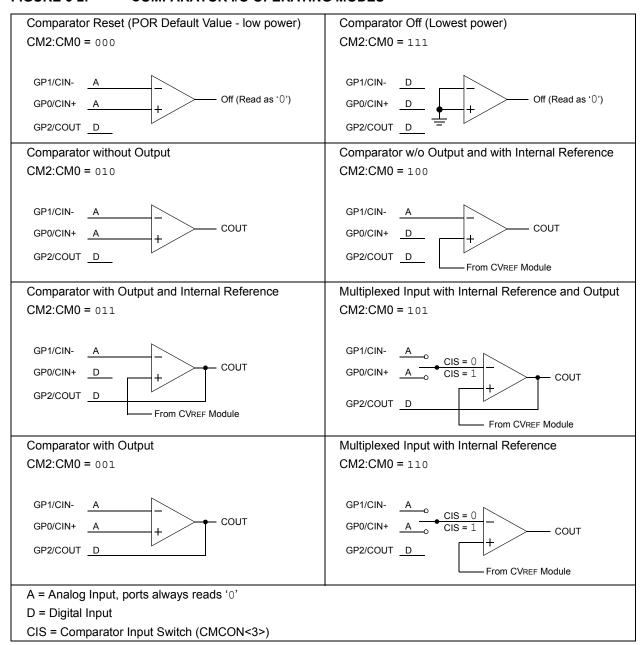

### 6.2 Comparator Configuration

There are eight modes of operation for the comparator. The CMCON register, shown in Register 6-1, is used to select the mode. Figure 6-2 shows the eight possible modes. The TRISIO register controls the data direction of the comparator pins for each mode. If the Comparator mode is changed, the comparator output level may not be valid for a specified period of time. Refer to the specifications in **Section 12.0 "Electrical Specifications"**.

Note: Comparator interrupts should be disabled during a Comparator mode change. Otherwise, a false interrupt may occur.

### FIGURE 6-2: COMPARATOR I/O OPERATING MODES

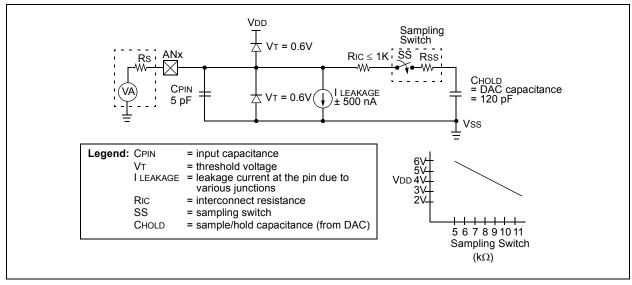

### 7.2 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 7-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 7-3. The maximum recommended impedance for analog sources is  $10~\mathrm{k}\Omega$ . As the impedance

is decreased, the acquisition time may be decreased. After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 7-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

To calculate the minimum acquisition time, TACQ, see the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

#### **EQUATION 7-1: ACQUISITION TIME**

Tacq = Amplifier Settling Time +

Hold Capacitor Charging Time +

Temperature Coefficient

= Tamp + Tc + Tcoff

=  $2\mu s + Tc + [(Temperature -25^{\circ}C)(0.05\mu s/^{\circ}C)]$ Tc = Chold (Ric + Rss + Rs) In(1/2047)

=  $-120pF (1k\Omega + 7k\Omega + 10k\Omega) In(0.0004885)$ =  $16.47\mu s$ Tacq =  $2\mu s + 16.47\mu s + [(50^{\circ}C -25^{\circ}C)(0.05\mu s/^{\circ}C)]$ =  $19.72\mu s$

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

### FIGURE 7-3: ANALOG INPUT MODEL

### 8.0 DATA EEPROM MEMORY

The EEPROM data memory is readable and writable during normal operation (full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers. There are four SFRs used to read and write this memory:

- EECON1

- EECON2 (not a physically implemented register)

- EEDATA

- EEADR

EEDATA holds the 8-bit data for read/write, and EEADR holds the address of the EEPROM location being accessed. PIC12F629/675 devices have 128 bytes of data EEPROM with an address range from 0h to 7Fh.

The EEPROM data memory allows byte read and write. A byte write automatically erases the location and writes the new data (erase before write). The EEPROM data memory is rated for high erase/write cycles. The write time is controlled by an on-chip timer. The write time will vary with voltage and temperature as well as from chip to chip. Please refer to AC Specifications for exact limits.

When the data memory is code-protected, the CPU may continue to read and write the data EEPROM memory. The device programmer can no longer access this memory.

Additional information on the data EEPROM is available in the  $PIC^{\$}$  Mid-Range Reference Manual, (DS33023).

### REGISTER 8-1: EEDAT: EEPROM DATA REGISTER (ADDRESS: 9Ah)

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| EEDAT7 | EEDAT6 | EEDAT5 | EEDAT4 | EEDAT3 | EEDAT2 | EEDAT1 | EEDAT0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 **EEDATn**: Byte value to write to or read from data EEPROM

### REGISTER 8-2: EEADR: EEPROM ADDRESS REGISTER (ADDRESS: 9Bh)

| U-0   | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| _     | EADR6 | EADR5 | EADR4 | EADR3 | EADR2 | EADR1 | EADR0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 **Unimplemented**: Should be set to '0'

bit 6-0 **EEADR**: Specifies one of 128 locations for EEPROM Read/Write Operation

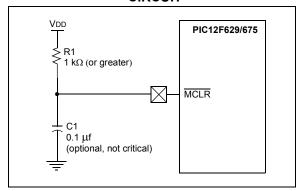

### 9.3.1 MCLR

PIC12F629/675 devices have a noise filter in the MCLR Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

The behavior of the ESD protection on the MCLR pin has been altered from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 9-5, is suggested.

An internal  $\overline{\text{MCLR}}$  option is enabled by setting the  $\underline{\text{MCLRE}}$  bit in the Configuration Word. When enabled,  $\underline{\text{MCLR}}$  is internally tied to  $\underline{\text{VDD}}$ . No internal pull-up option is available for the  $\underline{\text{MCLR}}$  pin.

FIGURE 9-5: RECOMMENDED MCLR CIRCUIT

### 9.3.2 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, simply tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details (see Section 12.0 "Electrical Specifications"). If the BOD is enabled, the maximum rise time specification does not apply. The BOD circuitry will keep the device in Reset until VDD reaches VBOD (see Section 9.3.5 "Brown-Out Detect (BOD)").

**Note:** The POR circuit does not produce an internal Reset when VDD declines.

When the device starts normal operation (exits the Reset condition), device operating parameters (i.e., voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

### 9.3.3 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from POR or Brown-out Detect. The Power-up Timer operates on an internal RC oscillator. The chip is kept in Reset as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A Configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should always be enabled when Brown-out Detect is enabled.

The Power-up Time delay will vary from chip to chip and due to:

- VDD variation

- Temperature variation

- · Process variation.

See DC parameters for details (Section 12.0 "Electrical Specifications").

## 9.3.4 OSCILLATOR START-UP TIMER (OST)

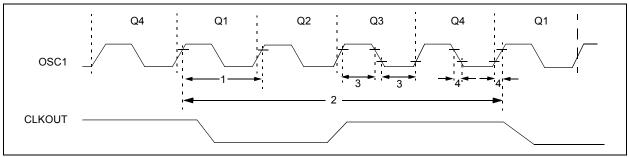

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from Sleep.

### 9.8 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

Note: The entire data EEPROM and Flash program memory will be erased when the code protection is turned off. The INTOSC calibration data is also erased. See PIC12F629/675 Programming Specification for more information.

### 9.9 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable during Program/Verify. Only the Least Significant 7 bits of the ID locations are used.

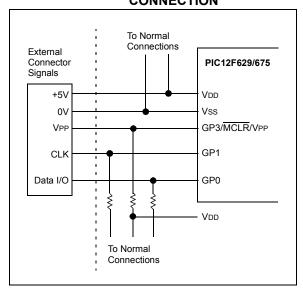

### 9.10 In-Circuit Serial Programming

The PIC12F629/675 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for:

- power

- · ground

- · programming voltage

This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the GP0 and GP1 pins low, while raising the MCLR (VPP) pin from VIL to VIHH (see Programming Specification). GP0 becomes the programming data and GP1 becomes the programming clock. Both GP0 and GP1 are Schmitt Trigger inputs in this mode.

After Reset, to place the device into Programming/ Verify mode, the PC is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending on whether the command was a load or a read. For complete details of serial programming, please refer to the Programming Specifications.

A typical In-Circuit Serial Programming connection is shown in Figure 9-14.

FIGURE 9-14: TYPICAL IN-CIRCUIT

SERIAL PROGRAMMING

CONNECTION

### 9.11 In-Circuit Debugger

Since in-circuit debugging requires the loss of clock, data and  $\overline{MCLR}$  pins, MPLAB® ICD 2 development with an 8-pin device is not practical. A special 14-pin PIC12F675-ICD device is used with MPLAB ICD 2 to provide separate clock, data and  $\overline{MCLR}$  pins and frees all normally available pins to the user.

This special ICD device is mounted on the top of the header and its signals are routed to the MPLAB ICD 2 connector. On the bottom of the header is an 8-pin socket that plugs into the user's target via the 8-pin stand-off connector.

When the ICD pin on the PIC12F675-ICD device is held low, the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB ICD 2. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 9-10 shows which features are consumed by the background debugger:

TABLE 9-10: DEBUGGER RESOURCES

| I/O pins       | ICDCLK, ICDDATA                  |

|----------------|----------------------------------|

| Stack          | 1 level                          |

| Program Memory | Address 0h must be NOP 300h-3FEh |

For more information, see 8-Pin MPLAB ICD 2 Header Information Sheet (DS51292) available on Microchip's web site (www.microchip.com).

## 10.2 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [/abe/] ADDLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                               |

| Operation:       | $(W) + k \rightarrow (W)$                                                                                         |

| Status Affected: | C, DC, Z                                                                                                          |

| Description:     | The contents of the W register are added to the eight-bit literal 'k' and the result is placed in the W register. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BCF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ADDWF            | Add W and f                                                                                                                                                        |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                 |

| Operation:       | $(W) + (f) \rightarrow (destination)$                                                                                                                              |

| Status Affected: | C, DC, Z                                                                                                                                                           |

| Description:     | Add the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| BSF              | Bit Set f                            |

|------------------|--------------------------------------|

| Syntax:          | [/abe/] BSF f,b                      |

| Operands:        | $0 \le f \le 127$<br>$0 \le b \le 7$ |

| Operation:       | $1 \rightarrow (f < b >)$            |

| Status Affected: | None                                 |

| Description:     | Bit 'b' in register 'f' is set.      |

|                  |                                      |

|                  |                                      |

| ANDLW            | AND Literal with W                                                                                            |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] ANDLW k                                                                                               |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                           |  |  |  |  |  |  |

| Operation:       | (W) .AND. $(k) \rightarrow (W)$                                                                               |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                             |  |  |  |  |  |  |

| Description:     | The contents of W register are AND'ed with the eight-bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |  |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] BTFSS f,b                                                                                                                                                                              |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                             |

| Operation:       | skip if $(f < b >) = 1$                                                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                           |

| Description:     | If bit 'b' in register 'f' is '0', the next instruction is executed.  If bit 'b' is '1', then the next instruction is discarded and a NOP is executed instead, making this a 2Tcy instruction. |

| ANDWF            | AND W with f                                                                                                                                       |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [/abe/] ANDWF f,d                                                                                                                                  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                 |  |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                          |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                  |  |  |  |  |  |  |

| Description:     | AND the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [ label ] MOVF f,d                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |