Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 × 8                                                                   |

| RAM Size                   | 64 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                             |

| Supplier Device Package    | 8-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f675t-i-sn |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

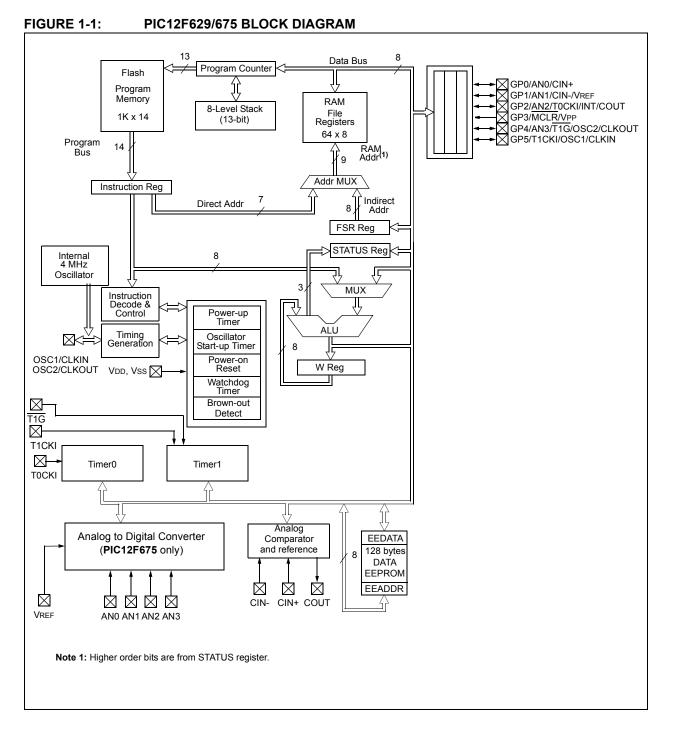

# 1.0 DEVICE OVERVIEW

This document contains device specific information for the PIC12F629/675. Additional information may be found in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip web site. The Reference Manual should be considered a complementary document to this Data Sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

The PIC12F629 and PIC12F675 devices are covered by this Data Sheet. They are identical, except the PIC12F675 has a 10-bit A/D converter. They come in 8-pin PDIP, SOIC, MLF-S and DFN packages. Figure 1-1 shows a block diagram of the PIC12F629/ 675 devices. Table 1-1 shows the pinout description.

# 2.2.2.2 OPTION Register

The OPTION register is a readable and writable register, which contains various control bits to configure:

- TMR0/WDT prescaler

- External GP2/INT interrupt

- TMR0

- · Weak pull-ups on GPIO

#### Note: To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT by setting PSA bit to '1' (OPTION<3>). See Section 4.4 "Prescaler".

## REGISTER 2-2: OPTION\_REG: OPTION REGISTER (ADDRESS: 81h)

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| GPPU  | INTEDG | TOCS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | <b>GPPU:</b> GPIO Pull-up Enable bit<br>1 = GPIO pull-ups are disabled<br>0 = GPIO pull-ups are enabled by individual PORT latch values                          |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | INTEDG: Interrupt Edge Select bit<br>1 = Interrupt on rising edge of GP2/INT pin<br>0 = Interrupt on falling edge of GP2/INT pin                                 |

| bit 5   | <b>TOCS:</b> TMR0 Clock Source Select bit<br>1 = Transition on GP2/T0CKI pin<br>0 = Internal instruction cycle clock (CLKOUT)                                    |

| bit 4   | <b>T0SE:</b> TMR0 Source Edge Select bit<br>1 = Increment on high-to-low transition on GP2/T0CKI pin<br>0 = Increment on low-to-high transition on GP2/T0CKI pin |

| bit 3   | <ul> <li>PSA: Prescaler Assignment bit</li> <li>1 = Prescaler is assigned to the WDT</li> <li>0 = Prescaler is assigned to the TIMER0 module</li> </ul>          |

| bit 2-0 | <b>PS2:PS0:</b> Prescaler Rate Select bits                                                                                                                       |

| Bit Value | TMR0 Rate | WDT Rate |

|-----------|-----------|----------|

|           |           |          |

| 000 | 1:2     | 1:1     |

|-----|---------|---------|

| 001 | 1:4     | 1:2     |

| 010 | 1:8     | 1:4     |

| 011 | 1:16    | 1:8     |

| 100 | 1:32    | 1:16    |

| 101 | 1:64    | 1:32    |

| 110 | 1 : 128 | 1:64    |

| 111 | 1 : 256 | 1 : 128 |

## 2.2.2.5 PIR1 Register

The PIR1 register contains the interrupt flag bits, as shown in Register 2-5.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## REGISTER 2-5: PIR1: PERIPHERAL INTERRUPT REGISTER 1 (ADDRESS: 0Ch)

| R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | U-0 | U-0 | R/W-0  |

|-------|-------|-----|-----|-------|-----|-----|--------|

| EEIF  | ADIF  | —   | _   | CMIF  | —   | —   | TMR1IF |

| bit 7 |       |     |     |       |     |     | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | <b>EEIF:</b> EEPROM Write Operation Interrupt Flag bit<br>1 = The write operation completed (must be cleared in software)<br>0 = The write operation has not completed or has not been started |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | ADIF: A/D Converter Interrupt Flag bit (PIC12F675 only)                                                                                                                                        |

|         | <ul><li>1 = The A/D conversion is complete (must be cleared in software)</li><li>0 = The A/D conversion is not complete</li></ul>                                                              |

| bit 5-4 | Unimplemented: Read as '0'                                                                                                                                                                     |

| bit 3   | CMIF: Comparator Interrupt Flag bit                                                                                                                                                            |

|         | <ul> <li>1 = Comparator input has changed (must be cleared in software)</li> <li>0 = Comparator input has not changed</li> </ul>                                                               |

| bit 2-1 | Unimplemented: Read as '0'                                                                                                                                                                     |

| bit 0   | TMR1IF: TMR1 Overflow Interrupt Flag bit                                                                                                                                                       |

|         | 1 = TMR1 register overflowed (must be cleared in software)                                                                                                                                     |

0 = TMR1 register did not overflow

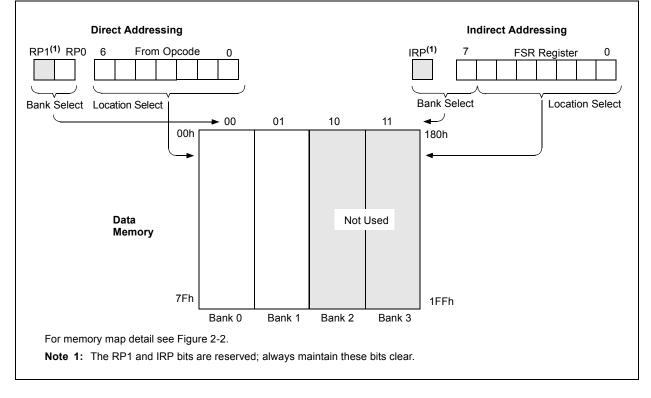

# 2.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-2.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 2-1.

# EXAMPLE 2-1: INDIRECT ADDRESSING

|          | MOVLW | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ;to RAM              |

| NEXT     | CLRF  | INDF  | ;clear INDF register |

|          | INCF  | FSR   | ;inc pointer         |

|          | BTFSS | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;no clear next       |

| CONTINUE |       |       | ;yes continue        |

|          |       |       |                      |

#### FIGURE 2-2: DIRECT/INDIRECT ADDRESSING PIC12F629/675

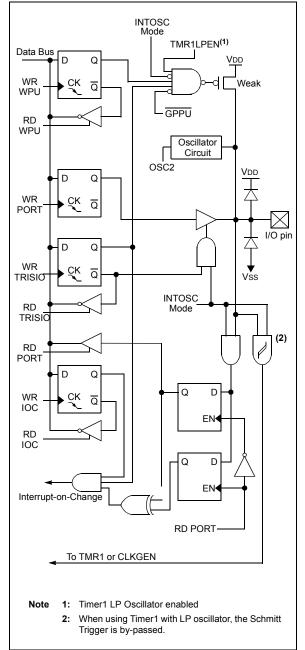

#### GP4/AN3/T1G/OSC2/CLKOUT 3.3.5

Figure 3-4 shows the diagram for this pin. The GP4 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the A/D (PIC12F675 only)

- a TMR1 gate input

- · a crystal/resonator connection

- · a clock output

#### FIGURE 3-4: **BLOCK DIAGRAM OF GP4**

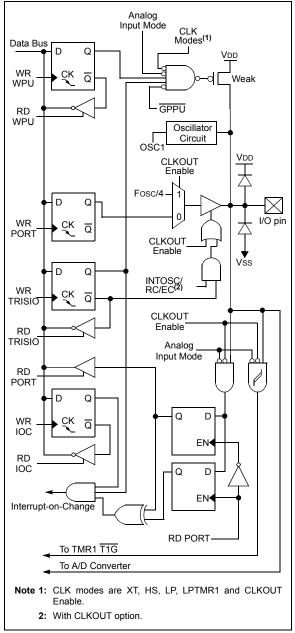

#### 3.3.6 GP5/T1CKI/OSC1/CLKIN

Figure 3-5 shows the diagram for this pin. The GP5 pin is configurable to function as one of the following:

- a general purpose I/O

- · a TMR1 clock input

- · a crystal/resonator connection

- · a clock input

#### **BLOCK DIAGRAM OF GP5**

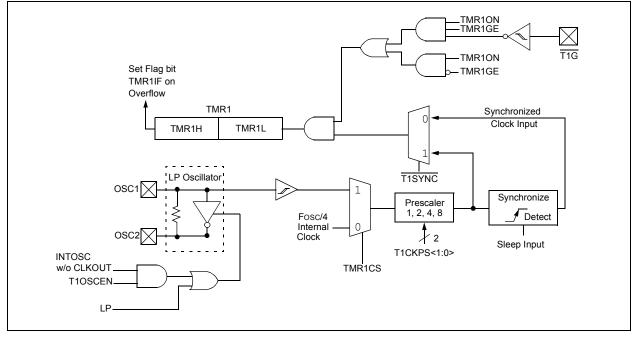

# 5.0 TIMER1 MODULE WITH GATE CONTROL

The PIC12F629/675 devices have a 16-bit timer. Figure 5-1 shows the basic block diagram of the Timer1 module. Timer1 has the following features:

- 16-bit timer/counter (TMR1H:TMR1L)

- · Readable and writable

- Internal or external clock selection

- Synchronous or asynchronous operation

- Interrupt on overflow from FFFFh to 0000h

- Wake-up upon overflow (Asynchronous mode)

- Optional external enable input (T1G)

- · Optional LP oscillator

## FIGURE 5-1: TIMER1 BLOCK DIAGRAM

The Timer1 Control register (T1CON), shown in Register 5.1, is used to enable/disable Timer1 and select the various features of the Timer1 module.

Note: Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

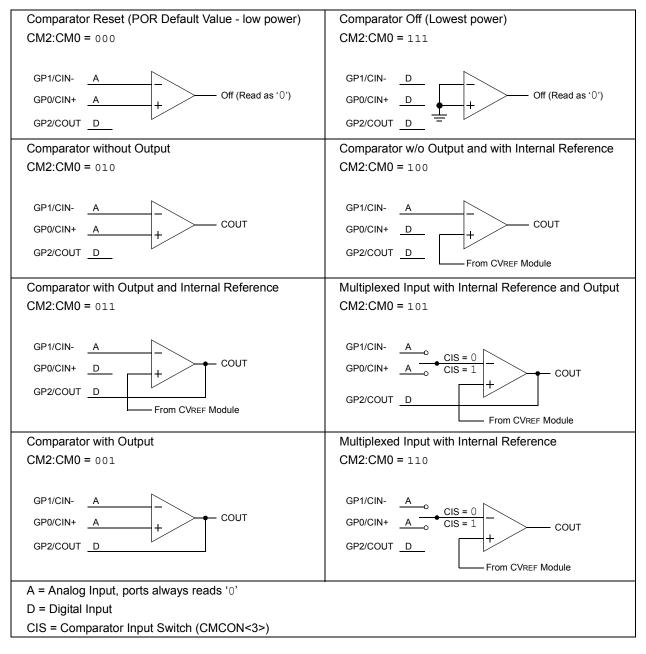

# 6.2 Comparator Configuration

There are eight modes of operation for the comparator. The CMCON register, shown in Register 6-1, is used to select the mode. Figure 6-2 shows the eight possible modes. The TRISIO register controls the data direction of the comparator pins for each mode. If the Comparator mode is changed, the comparator output level may not be valid for a specified period of time. Refer to the specifications in **Section 12.0 "Electrical Specifications"**.

Note: Comparator interrupts should be disabled during a Comparator mode change. Otherwise, a false interrupt may occur.

#### FIGURE 6-2: COMPARATOR I/O OPERATING MODES

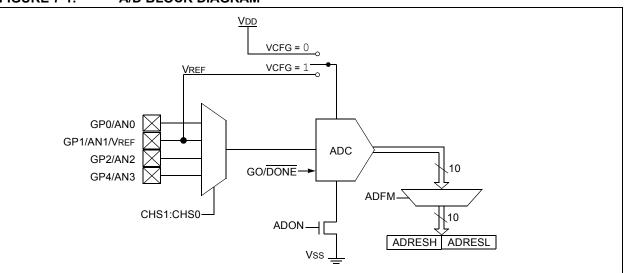

# 7.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE (PIC12F675 ONLY)

The Analog-to-Digital converter (A/D) allows conversion of an analog input signal to a 10-bit binary representation of that signal. The PIC12F675 has four analog inputs, multiplexed into one sample and hold

# FIGURE 7-1: A/D BLOCK DIAGRAM

circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a binary result via successive approximation and stores the result in a 10-bit register. The voltage reference used in the conversion is software selectable to either VDD or a voltage applied by the VREF pin. Figure 7-1 shows the block diagram of the A/D on the PIC12F675.

# 7.1 A/D Configuration and Operation

There are two registers available to control the functionality of the A/D module:

- 1. ADCON0 (Register 7-1)

- 2. ANSEL (Register 7-2)

# 7.1.1 ANALOG PORT PINS

The ANS3:ANS0 bits (ANSEL<3:0>) and the TRISIO bits control the operation of the A/D port pins. Set the corresponding TRISIO bits to set the pin output driver to its high-impedance state. Likewise, set the corresponding ANS bit to disable the digital input buffer.

| Note: | Analog voltages on any pin that is defined |

|-------|--------------------------------------------|

|       | as a digital input may cause the input     |

|       | buffer to conduct excess current.          |

# 7.1.2 CHANNEL SELECTION

There are four analog channels on the PIC12F675, AN0 through AN3. The CHS1:CHS0 bits (ADCON0<3:2>) control which channel is connected to the sample and hold circuit.

# 7.1.3 VOLTAGE REFERENCE

There are two options for the voltage reference to the A/D converter: either VDD is used, or an analog voltage applied to VREF is used. The VCFG bit (ADCON0<6>)

controls the voltage reference selection. If VCFG is set, then the voltage on the VREF pin is the reference; otherwise, VDD is the reference.

# 7.1.4 CONVERSION CLOCK

The A/D conversion cycle requires 11 TAD. The source of the conversion clock is software selectable via the ADCS bits (ANSEL<6:4>). There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal RC oscillator)

For correct conversion, the A/D conversion clock (1/TAD) must be selected to ensure a minimum TAD of 1.6  $\mu$ s. Table 7-1 shows a few TAD calculations for selected frequencies.

# 8.0 DATA EEPROM MEMORY

The EEPROM data memory is readable and writable during normal operation (full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers. There are four SFRs used to read and write this memory:

- EECON1

- EECON2 (not a physically implemented register)

- EEDATA

- EEADR

EEDATA holds the 8-bit data for read/write, and EEADR holds the address of the EEPROM location being accessed. PIC12F629/675 devices have 128 bytes of data EEPROM with an address range from 0h to 7Fh.

The EEPROM data memory allows byte read and write. A byte write automatically erases the location and writes the new data (erase before write). The EEPROM data memory is rated for high erase/write cycles. The write time is controlled by an on-chip timer. The write time will vary with voltage and temperature as well as from chip to chip. Please refer to AC Specifications for exact limits.

When the data memory is code-protected, the CPU may continue to read and write the data EEPROM memory. The device programmer can no longer access this memory.

Additional information on the data EEPROM is available in the  ${\rm PIC}^{\circledast}$  Mid-Range Reference Manual, (DS33023).

|        |        |        |        | •      | ,      |        |        |

|--------|--------|--------|--------|--------|--------|--------|--------|

| R/W-0  |

| EEDAT7 | EEDAT6 | EEDAT5 | EEDAT4 | EEDAT3 | EEDAT2 | EEDAT1 | EEDAT0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0 **EEDATn**: Byte value to write to or read from data EEPROM

#### REGISTER 8-2: EEADR: EEPROM ADDRESS REGISTER (ADDRESS: 9Bh)

| U-0   | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| —     | EADR6 | EADR5 | EADR4 | EADR3 | EADR2 | EADR1 | EADR0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7 Unimplemented: Should be set to '0'

bit 6-0 EEADR: Specifies one of 128 locations for EEPROM Read/Write Operation

# PIC12F629/675

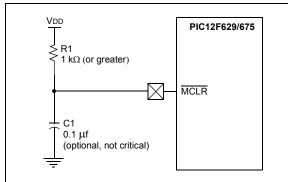

# 9.3.1 MCLR

It should be noted that a WDT Reset does not drive MCLR pin low.

The behavior of the ESD protection on the MCLR pin has been altered from previous devices of this family. Voltages applied to the pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 9-5, is suggested.

An internal MCLR option is enabled by setting the MCLRE bit in the Configuration Word. When enabled, MCLR is internally tied to VDD. No internal pull-up option is available for the MCLR pin.

#### FIGURE 9-5: RECOMMENDED MCLR CIRCUIT

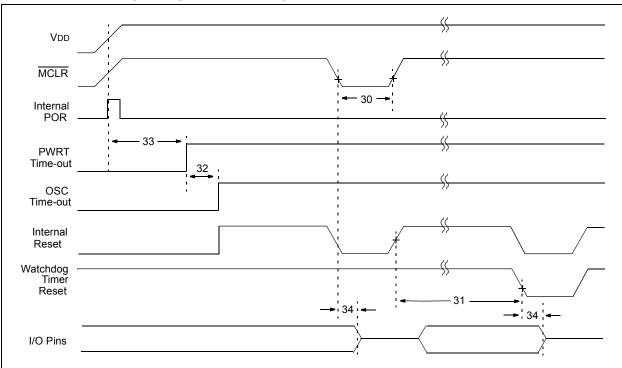

# 9.3.2 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, simply tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See Electrical Specifications for details (see Section 12.0 "Electrical Specifications"). If the BOD is enabled, the maximum rise time specification does not apply. The BOD circuitry will keep the device in Reset until VDD reaches VBOD (see Section 9.3.5 "Brown-Out Detect (BOD)").

| Note: | The POR circuit does not produce a | in |

|-------|------------------------------------|----|

|       | internal Reset when VDD declines.  |    |

When the device starts normal operation (exits the Reset condition), device operating parameters (i.e., voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

## 9.3.3 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from POR or Brown-out Detect. The Power-up Timer operates on an internal RC oscillator. The chip is kept in Reset as long as PWRT is active. The PWRT delay allows the <u>VDD to</u> rise to an acceptable level. A Configuration bit, PWRTE can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should always be enabled when Brown-out Detect is enabled.

The Power-up Time delay will vary from chip to chip and due to:

- VDD variation

- Temperature variation

- · Process variation.

See DC parameters for details (Section 12.0 "Electrical Specifications").

## 9.3.4 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on Power-on Reset or wake-up from Sleep.

| ABLE 9-7: INITIALIZATION CONDITION FOR REGISTERS |         |                   |                                                                                                                                                        |                                                                                                                   |

|--------------------------------------------------|---------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Register                                         | Address | Power-on<br>Reset | <ul> <li>MCLR Reset during<br/>normal operation</li> <li>MCLR Reset during Sleep</li> <li>WDT Reset</li> <li>Brown-out Detect<sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from Sleep<br/>through interrupt</li> <li>Wake-up from Sleep<br/>through WDT Time-out</li> </ul> |

| W                                                |         | XXXX XXXX         | นนนน นนนน                                                                                                                                              | սսսս սսսս                                                                                                         |

| INDF                                             | 00h/80h | —                 | —                                                                                                                                                      | —                                                                                                                 |

| TMR0                                             | 01h     | XXXX XXXX         | นนนน นนนน                                                                                                                                              | นนนน นนนน                                                                                                         |

| PCL                                              | 02h/82h | 0000 0000         | 0000 0000                                                                                                                                              | PC + 1 <sup>(3)</sup>                                                                                             |

| STATUS                                           | 03h/83h | 0001 1xxx         | 000q quuu <sup>(4)</sup>                                                                                                                               | uuuq quuu <sup>(4)</sup>                                                                                          |

| FSR                                              | 04h/84h | XXXX XXXX         | սսսս սսսս                                                                                                                                              | սսսս սսսս                                                                                                         |

| GPIO                                             | 05h     | xx xxxx           | uu uuuu                                                                                                                                                | uu uuuu                                                                                                           |

| PCLATH                                           | 0Ah/8Ah | 0 0000            | 0 0000                                                                                                                                                 | u uuuu                                                                                                            |

| INTCON                                           | 0Bh/8Bh | 0000 0000         | 0000 000u                                                                                                                                              | uuuu uuqq <sup>(2)</sup>                                                                                          |

| PIR1                                             | 0Ch     | 00 00             | 00 00                                                                                                                                                  | qq qq <sup>(2,5)</sup>                                                                                            |

| T1CON                                            | 10h     | -000 0000         | -uuu uuuu                                                                                                                                              | -uuu uuuu                                                                                                         |

| CMCON                                            | 19h     | -0-0 0000         | -0-0 0000                                                                                                                                              | -u-u uuuu                                                                                                         |

| ADRESH                                           | 1Eh     | XXXX XXXX         | นนนน นนนน                                                                                                                                              | นนนน นนนน                                                                                                         |

| ADCON0                                           | 1Fh     | 00 0000           | 00 0000                                                                                                                                                | uu uuuu                                                                                                           |

| OPTION_REG                                       | 81h     | 1111 1111         | 1111 1111                                                                                                                                              | นนนน นนนน                                                                                                         |

| TRISIO                                           | 85h     | 11 1111           | 11 1111                                                                                                                                                | uu uuuu                                                                                                           |

| PIE1                                             | 8Ch     | 00 00             | 00 00                                                                                                                                                  | uu uu                                                                                                             |

| PCON                                             | 8Eh     | 0x                | (1,6)                                                                                                                                                  | uu                                                                                                                |

| OSCCAL                                           | 90h     | 1000 00           | 1000 00                                                                                                                                                | uuuu uu                                                                                                           |

| WPU                                              | 95h     | 11 -111           | 11 -111                                                                                                                                                | นนนน นนนน                                                                                                         |

| IOC                                              | 96h     | 00 0000           | 00 0000                                                                                                                                                | uu uuuu                                                                                                           |

| VRCON                                            | 99h     | 0-0- 0000         | 0-0- 0000                                                                                                                                              | u-u- uuuu                                                                                                         |

| EEDATA                                           | 9Ah     | 0000 0000         | 0000 0000                                                                                                                                              | սսսս սսսս                                                                                                         |

| EEADR                                            | 9Bh     | -000 0000         | -000 0000                                                                                                                                              | -uuu uuuu                                                                                                         |

| EECON1                                           | 9Ch     | x000              | q000                                                                                                                                                   | uuuu                                                                                                              |

| EECON2                                           | 9Dh     |                   |                                                                                                                                                        |                                                                                                                   |

| ADRESL                                           | 9Eh     | XXXX XXXX         | นนนน นนนน                                                                                                                                              | นนนน นนนน                                                                                                         |

| ANSEL                                            | 9Fh     | -000 1111         | -000 1111                                                                                                                                              | -uuu uuuu                                                                                                         |

TABLE 9-7: INITIALIZATION CONDITION FOR REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

**3:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 9-6 for Reset value for specific condition.

5: If wake-up was due to data EEPROM write completing, Bit 7 = 1; A/D conversion completing, Bit 6 = 1; Comparator input changing, bit 3 = 1; or Timer1 rolling over, bit 0 = 1. All other interrupts generating a wake-up will cause these bits to = u.

**6:** If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                           |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                                                                                                  |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.<br>If the result is 1, the next instruction is executed. If the result is 0, then a NOP is executed instead, making it a 2TCY instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                             |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                              |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                    |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'.<br>If the result is 1, the next instruc-<br>tion is executed. If the result is 0,<br>a NOP is executed instead, making<br>it a 2TCY instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                              |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                           |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                              |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                              |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a two-<br>cycle instruction. |

| IORLW            | Inclusive OR Literal with W                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |

| Operands:        | $0 \leq k \leq 255$                                                                                                       |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              |

| Status Affected: | Z                                                                                                                         |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |

| INCF             | Increment f                                                                                                                                                            | IORWF            | Inclusive OR W with f                                                                                                                                       |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                              | Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                      | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                    | Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                    |

| Status Affected: | Z                                                                                                                                                                      | Status Affected: | Z                                                                                                                                                           |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. | Description:     | Inclusive OR the W register with register 'f'. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |

# 11.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

# 11.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

# 11.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

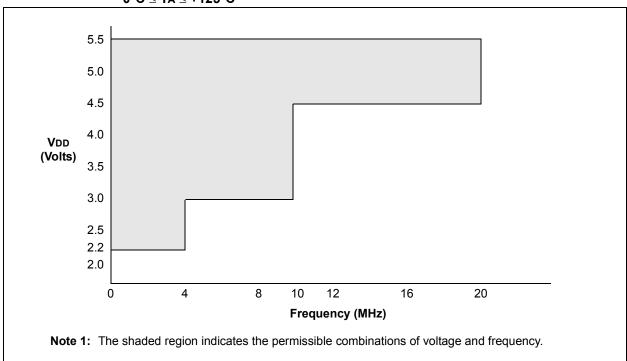

FIGURE 12-3: PIC12F675 WITH A/D ENABLED VOLTAGE-FREQUENCY GRAPH, 0°C  $\leq$  Ta  $\leq$  +125°C

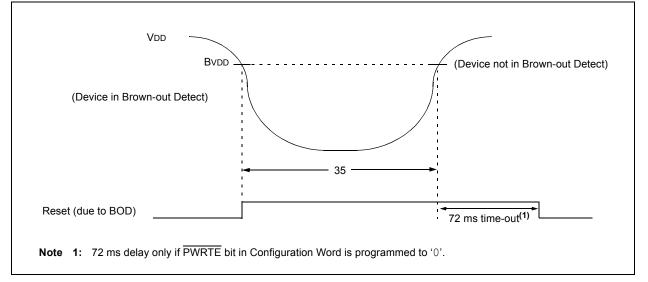

#### FIGURE 12-8: BROWN-OUT DETECT TIMING AND CHARACTERISTICS

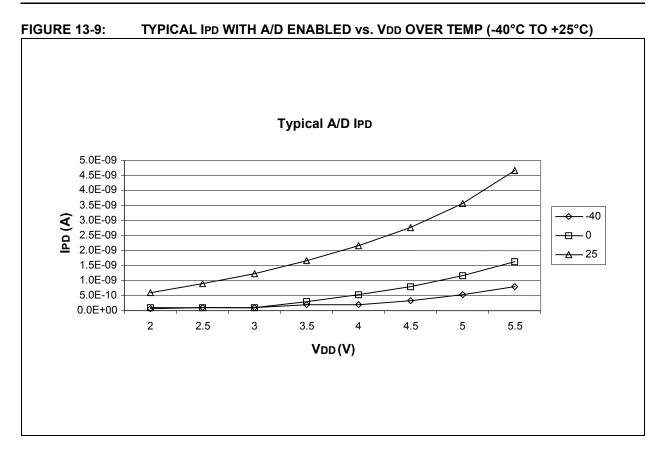

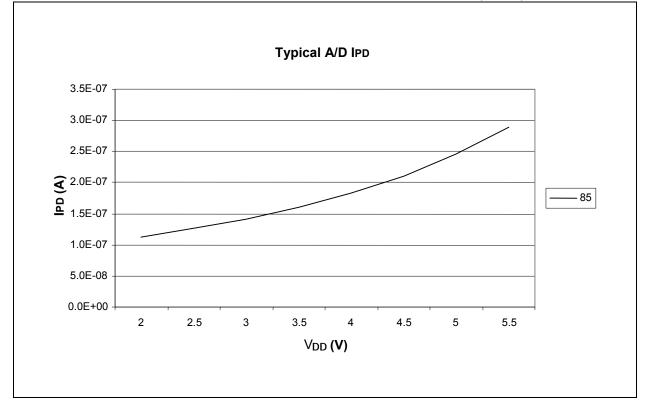

FIGURE 13-10: TYPICAL IPD WITH A/D ENABLED vs. VDD OVER TEMP (+85°C)

# PIC12F629/675

NOTES:

# 14.0 PACKAGING INFORMATION

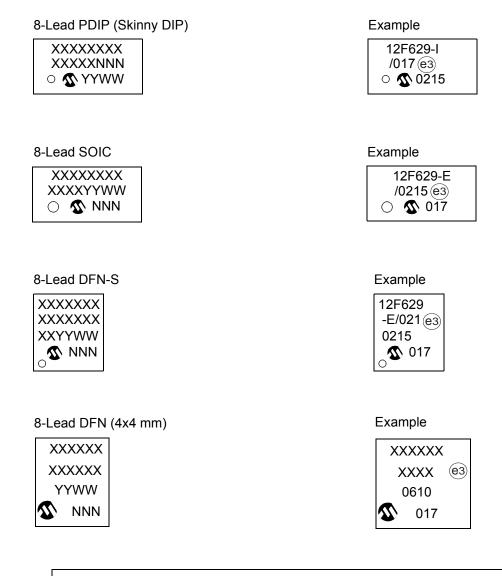

# 14.1 Package Marking Information

| Legend | I: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                     | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                              |

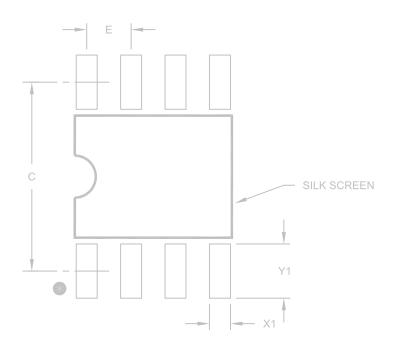

# 8-Lead Plastic Small Outline (SN) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                         | Units |          | MILLIMETERS |      |  |

|-------------------------|-------|----------|-------------|------|--|

| Dimension Limits        |       | MIN      | NOM         | MAX  |  |

| Contact Pitch           | E     | 1.27 BSC |             |      |  |

| Contact Pad Spacing     | С     |          | 5.40        |      |  |

| Contact Pad Width (X8)  | X1    |          |             | 0.60 |  |

| Contact Pad Length (X8) | Y1    |          |             | 1.55 |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A

# WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

# ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-6578-300 Fax: 886-3-6578-370

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-536-4803

Taiwan - Taipei Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

01/05/10