Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                            |

|---------------------------------|------------------------------------------------------------|

| Product Status                  | Active                                                     |

| Core Processor                  | -                                                          |

| Number of Cores/Bus Width       | -                                                          |

| Speed                           | -                                                          |

| Co-Processors/DSP               | -                                                          |

| RAM Controllers                 | -                                                          |

| Graphics Acceleration           | -                                                          |

| Display & Interface Controllers | -                                                          |

| Ethernet                        | -                                                          |

| SATA                            | -                                                          |

| USB                             | -                                                          |

| Voltage - I/O                   | -                                                          |

| Operating Temperature           | -                                                          |

| Security Features               | -                                                          |

| Package / Case                  | -                                                          |

| Supplier Device Package         | -                                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc94mx21dvkn3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- A pin is an external physical connection. The same pin can be used to connect a number of signals.

- Asserted means that a discrete signal is in active logic state.

- Active low signals change from logic level one to logic level zero.

- Active high signals change from logic level zero to logic level one.

- Negated means that an asserted discrete signal changes logic state.

- Active low signals change from logic level zero to logic level one.

- Active high signals change from logic level one to logic level zero.

- LSB means *least significant bit* or *bits*, and MSB means *most significant bit* or *bits*. References to low and high bytes or words are spelled out.

- Numbers preceded by a percent sign (%) are binary. Numbers preceded by a dollar sign (\$) or 0x are hexadecimal.

# 1.2 Target Applications

The i.MX21 is targeted for advanced information appliances, smart phones, Web browsers, digital MP3 audio players, handheld computers based on the popular Palm OS platform, and messaging applications.

### 1.3 Reference Documentation

The following documents are required for a complete description of the i.MX21 and are necessary to design properly with the device. Especially for those not familiar with the ARM926EJ-S processor the following documents are helpful when used in conjunction with this manual.

ARM Architecture Reference Manual (ARM Ltd., order number ARM DDI 0100)

ARM7TDMI Data Sheet (ARM Ltd., order number ARM DDI 0029)

ARM920T Technical Reference Manual (ARM Ltd., order number ARM DDI 0151C)

MC9328MX21 Product Brief (order number MC9328MX21P)

MC9328MX21 Reference Manual (order number MC9328MX21RM)

The Freescale manuals are available on the Freescale Semiconductor Web site at http://www.freescale.com. These documents may be downloaded directly from the Freescale Web site, or printed versions may be ordered. The ARM Ltd. documentation is available from http://www.arm.com.

## 1.4 Ordering Information

Table 1 provides ordering information for the device. See Table 4 on page 14 for core frequency and supply voltage requirements.

**Table 1. Ordering Information**

| Part Order Number | Package Size                           | Package Type | Operating Range |

|-------------------|----------------------------------------|--------------|-----------------|

| MC94MX21DVKN3     | 289-lead MAPBGA<br>0.65mm, 14mm x 14mm | Lead-free    | -30°C–70°C      |

### **Signal Descriptions**

### Table 2. i.MX21 Signal Descriptions (Continued)

| Signal Name               | Function/Notes                                                                                                                                                                                                            |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | CSPI                                                                                                                                                                                                                      |

| CSPI1_MOSI                | Master Out/Slave In signal                                                                                                                                                                                                |

| CSPI1_MISO                | Master In/Slave Out signal                                                                                                                                                                                                |

| CSPI1_SS[2:0]             | Slave Select (Selectable polarity) signal. CSPI1_SS2 is also multiplexed with USBG_RXDAT and CSPI1_SS1 is multiplexed with EXT_DMAGRANT.                                                                                  |

| CSPI1_SCLK                | Serial Clock signal                                                                                                                                                                                                       |

| CSPI1_RDY                 | Serial Data Ready signal. Also multiplexed with EXT_DMAREQ.                                                                                                                                                               |

| CSPI2_MOSI                | Master Out/Slave In signal. This signal is multiplexed with USBH2_TXDP signal of USB OTG.                                                                                                                                 |

| CSPI2_MISO                | Master In/Slave Out signal. This signal is multiplexed with USBH2_TXDM signal of USB OTG.                                                                                                                                 |

| CSPI2_SS[2:0]             | Slave Select (Selectable polarity) signals. These signals are multiplexed with USBH2_FS, USBH2_RXDP and USBH2_RXDM signal of USB OTG                                                                                      |

| CSPI2_SCLK                | Serial Clock signal. This signal is multiplexed with USBH2_OE signal of USB OTG                                                                                                                                           |

| CSPI3_MOSI                | Master Out/Slave In signal. This signal is multiplexed with SD1_CMD.                                                                                                                                                      |

| CSPI3_MISO                | Master In/Slave Out signal. This signal is multiplexed with SD1_D0.                                                                                                                                                       |

| CSPI3_SS                  | Slave Select (Selectable polarity) signal multiplexed with SD1_D3.                                                                                                                                                        |

| CSPI3_SCLK                | Serial Clock signal. This signal is multiplexed with SD1_CLK.                                                                                                                                                             |

|                           | General Purpose Timers                                                                                                                                                                                                    |

| TIN                       | Timer Input Capture or Timer Input Clock—The signal on this input is applied to all 3 timers simultaneously. This signal is muxed with the Walk-up Guard Mode WKGD signal in the PLL, Clock, and Reset Controller module. |

| TOUT1<br>(or simply TOUT) | Timer Output signal from General Purpose Timer1 (GPT1). This signal is multiplexed with SYS_CLK1 and SYS_CLK2 signal of SSI1 and SSI2. The pin name of this signal is simply TOUT.                                        |

| TOUT2                     | Timer Output signal from General Purpose Timer1 (GPT2). This signal is multiplexed with PWMO.                                                                                                                             |

| TOUT3                     | Timer Output signal from General Purpose Timer1 (GPT3). This signal is multiplexed with PWMO.                                                                                                                             |

|                           | USB On-The-Go                                                                                                                                                                                                             |

| USB_BYP                   | USB Bypass input active low signal. This signal can only be used for USB function, not for GPIO.                                                                                                                          |

| USB_PWR                   | USB Power output signal                                                                                                                                                                                                   |

| USB_OC                    | USB Over current input signal. This signal can only be used for USB function, not for GPIO.                                                                                                                               |

| USBG_RXDP                 | USB OTG Receive Data Plus input signal. This signal is muxed with SLCDC1_DAT15.                                                                                                                                           |

| USBG_RXDM                 | USB OTG Receive Data Minus input signal. This signal is muxed with SLCDC1_DAT14.                                                                                                                                          |

| USBG_TXDP                 | USB OTG Transmit Data Plus output signal. This signal is muxed with SLCDC1_DAT13.                                                                                                                                         |

| USBG_TXDM                 | USB OTG Transmit Data Minus output signal. This signal is muxed with SLCDC1_DAT12.                                                                                                                                        |

| USBG_RXDAT                | USB OTG Transceiver differential data receive signal. Multiplexed with CSPI1_SS2.                                                                                                                                         |

| USBG_OE                   | USB OTG Output Enable signal. This signal is muxed with SLCDC1_DAT11.                                                                                                                                                     |

| USBG_ON                   | USB OTG Transceiver ON output signal. This signal is muxed with SLCDC1_DAT9.                                                                                                                                              |

| USBG_FS                   | USB OTG Full Speed output signal. This signal is multiplexed with external transceiver USBG_TXR_INT signal of USB OTG. This signal is muxed with SLCDC1_DAT10.                                                            |

# 3.3 DC Electrical Characteristics

Table 5 contains the DC characteristics of the i.MX21.

**Table 5. DC Characteristics**

| Parameter                                       | Symbol            | Test Conditions                                                                                 | Min                          | Typ <sup>1</sup> | Max     | Units |

|-------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------|------------------------------|------------------|---------|-------|

| High-level input voltage                        | $V_{IH}$          | _                                                                                               | 0.7NVDD                      | _                | NVDD    |       |

| Low-level Input voltage                         | V <sub>IL</sub>   | -                                                                                               | 0                            | _                | 0.3NVDD |       |

| High-level output voltage                       | V <sub>OH</sub>   | I <sub>OH</sub> = spec'ed Drive                                                                 | 0.8NVDD                      | _                | _       | ٧     |

| Low-level output voltage                        | V <sub>OL</sub>   | I <sub>OL</sub> = spec'ed Drive                                                                 | _                            | -                | 0.2NVDD | V     |

| High-level output current, slow I/O             | I <sub>OH_S</sub> | V <sub>out</sub> =0.8NVDD<br>DSCR <sup>2</sup> = 000<br>DSCR = 001<br>DSCR = 011<br>DSCR = 111  | -2<br>-4<br>-8<br>-12        | -                | -       | mA    |

| High-level output current, fast I/O             | I <sub>OH_F</sub> | V <sub>out</sub> =0.8NVDD1<br>DSCR <sup>2</sup> = 000<br>DSCR = 001<br>DSCR = 011<br>DSCR = 111 | -3.5<br>-4.5<br>-5.5<br>-6.5 | -                | -       | mA    |

| Low-level output current, slow I/O              | I <sub>OL_S</sub> | V <sub>out</sub> =0.2NVDD<br>DSCR <sup>2</sup> = 000<br>DSCR = 001<br>DSCR = 011<br>DSCR = 111  | 2<br>4<br>8<br>12            | -                | -       | mA    |

| Low-level output current, fast I/O              | I <sub>OL_F</sub> | V <sub>out</sub> =0.2NVDD1<br>DSCR <sup>2</sup> = 000<br>DSCR = 001<br>DSCR = 011<br>DSCR = 111 | 3.5<br>4.5<br>5.5<br>6.5     | -                | -       | mA    |

| Schmitt trigger Positive-input threshold        | V <sub>T</sub> +  | _                                                                                               | _                            | _                | 2.15    | V     |

| Schmitt trigger Negative-input threshold        | V <sub>T</sub> -  |                                                                                                 | 0.75                         | _                | _       | V     |

| Hysteresis                                      | V <sub>HYS</sub>  | _                                                                                               | _                            | 0.3              | _       | V     |

| Input leakage current (no pull-up or pull-down) | I <sub>in</sub>   | V <sub>in</sub> = 0 or NVDD                                                                     | _                            | -                | ±1      | μА    |

| I/O leakage current                             | I <sub>OZ</sub>   | V <sub>I/O</sub> = NVDD or 0<br>I/O = High impedance<br>state                                   | -                            | -                | ±5      | μА    |

<sup>1.</sup> Data labeled Typical is not guaranteed, but is intended as an indication of the IC's potential performance.

Table 6 shows the input and output capacitance for the device.

**Table 6. Input/Output Capacitance**

| Parameter          | Symbol         | Min | Тур | Max | Units |

|--------------------|----------------|-----|-----|-----|-------|

| Input capacitance  | C <sub>i</sub> | -   | -   | 5   | pF    |

| Output capacitance | C <sub>o</sub> | -   | _   | 5   | pF    |

MC94MX21 Technical Data, Rev. 1.4

<sup>2.</sup> For DSCR definition refer to the System Control chapter in the reference manual.

can write data to BMI RxFIFO anytime as CPU or DMA can move data out from RxFIFO much faster than the BMI interface. Overflow interrupt is generated if RxFIFO overflow is detected. Once this happens, the new coming data is ignored.

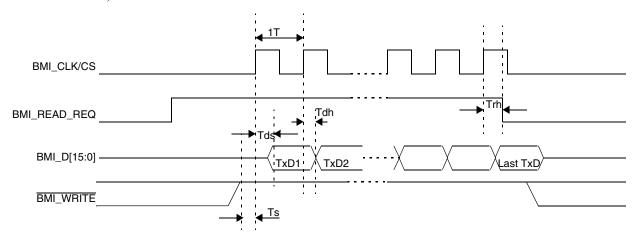

### 3.8.1.1.1 MMD Read BMI Timing

Figure 6 shows the MMD read BMI timing when the MMD drives clock.

On each rising edge of BMI\_CLK/CS BMI checks the BMI\_WRITE logic level to determine if the current cycle is a read cycle. It puts data into the data bus and enables the data out on the rising edge of BMI\_CLK/CS if BMI\_WRITE is logic high. The BMI\_READ\_REQ is negated one hclk cycle after the BMI\_CLK/CS rising edge of last data read. The MMD cannot issues read command when BMI\_READ\_REQ is low (no data in TxFIFO).

Figure 6. MMD (ATI) Drives Clock, MMD Read BMI Timing (MMD\_MODE\_SEL=1, MASTER\_MODE\_SEL=0,MMD\_CLKOUT=0)

Table 13. MMD Read BMI Timing Table when MMD Drives Clock

| Item                     | Symbol | Minimum | Typical | Maximum | Unit |

|--------------------------|--------|---------|---------|---------|------|

| Clock period             | 1T     | 33.3    | _       | _       | ns   |

| write setup time         | Ts     | 11      | -       | _       | ns   |

| read_req hold time       | Trh    | 6       | -       | 24      | ns   |

| transfer data setup time | Tds    | 6       | _       | 14      | ns   |

| transfer data hold time  | Tdh    | 6       | -       | 14      | ns   |

Note: All the timings assume that the hclk is running at 133 MHz.

Note: The MIN period of the 1T is assumed that MMD latch data at falling edge.

**Note:** If the MMD latch data at next rising edge, the ideally max clock can be as much as double, but because the BMI data pads are slow pads and it max frequency can only up to 18MHz, the max clock frequency can only up to 36 MHz.

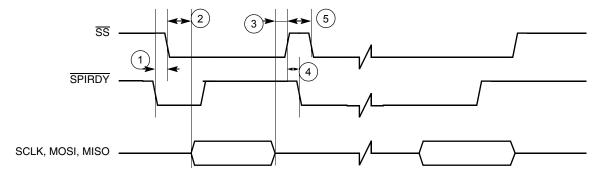

becomes an input signal, and is used to latch data into or load data out to the internal data shift registers, as well as to increment the data FIFO.

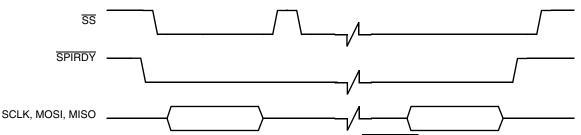

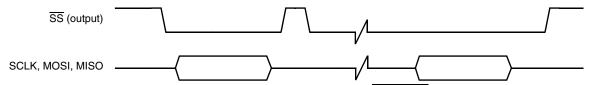

Figure 14. Master CSPI Timing Diagram Using SPI\_RDY Edge Trigger

Figure 15. Master CSPI Timing Diagram Using SPI\_RDY Level Trigger

Figure 16. Master CSPI Timing Diagram Ignore SPI RDY Level Trigger

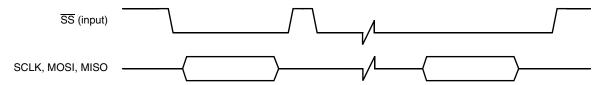

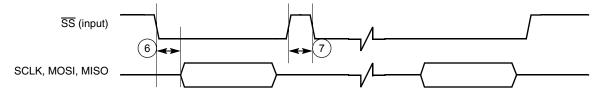

Figure 17. Slave CSPI Timing Diagram FIFO Advanced by BIT COUNT

Figure 18. Slave CSPI Timing Diagram FIFO Advanced by SS Rising Edge

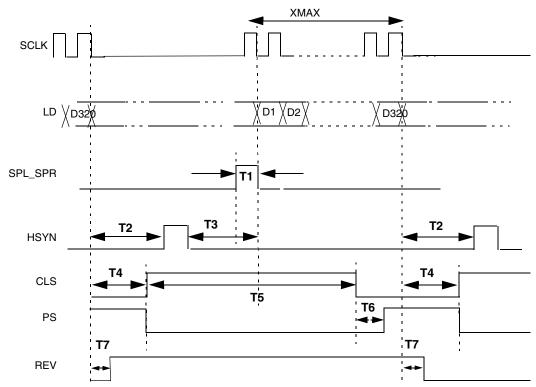

Figure 21. Sharp TFT Panel Timing

**Table 21. Sharp TFT Panel Timing**

| Symbol | Description                            | Minimum | Value              | Unit |

|--------|----------------------------------------|---------|--------------------|------|

| T1     | SPL/SPR pulse width                    | -       | 1                  | Ts   |

| T2     | End of LD of line to beginning of HSYN | 1       | HWAIT1+1           | Ts   |

| Т3     | End of HSYN to beginning of LD of line | 4       | HWAIT2 + 4         | Ts   |

| T4     | CLS rise delay from end of LD of line  | 3       | CLS_RISE_DELAY+1   | Ts   |

| T5     | CLS pulse width                        | 1       | CLS_HI_WIDTH+1     | Ts   |

| Т6     | PS rise delay from CLS negation        | 0       | PS_RISE_DELAY      | Ts   |

| T7     | REV toggle delay from last LD of line  | 1       | REV_TOGGLE_DELAY+1 | Ts   |

### Note:

- Falling of SPL/SPR aligns with first LD of line.

- Falling of PS aligns with rising edge of CLS.

- REV toggles in every HSYN period.

### 3.11 Smart LCD Controller

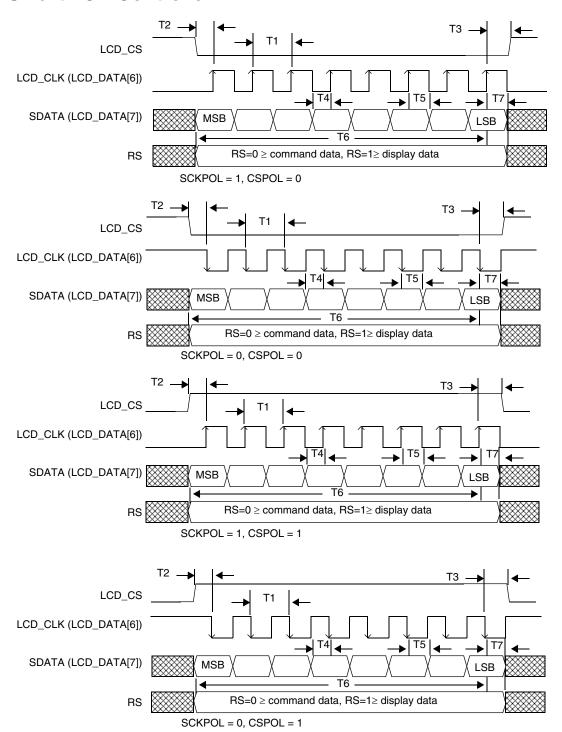

Figure 23. SLCDC Serial Transfer Timing

# 3.15 SDRAM Memory Controller

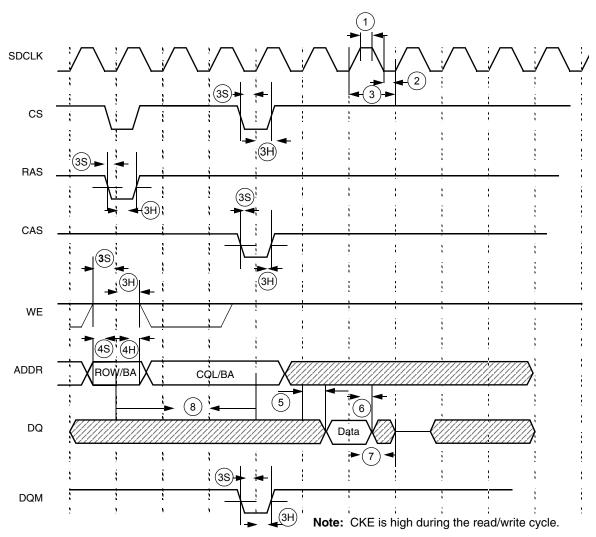

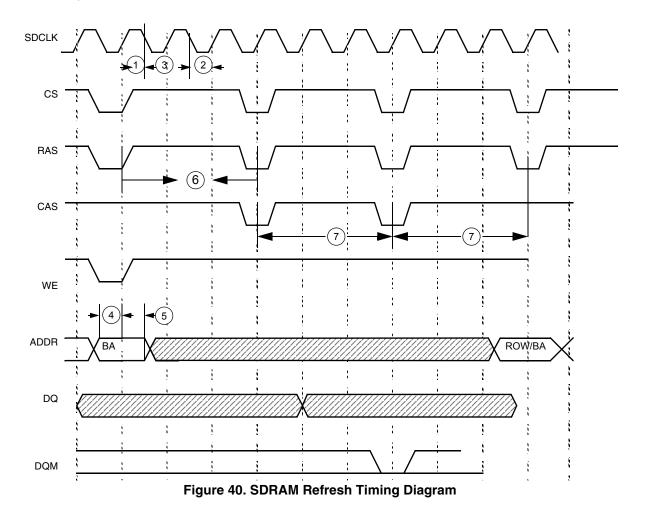

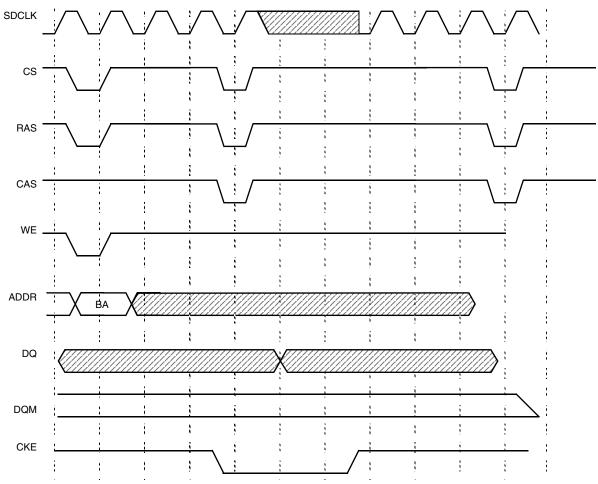

The following figures (Figure 38 through Figure 41) and their associated tables specify the timings related to the SDRAMC module in the i.MX21.

Figure 38. SDRAM Read Cycle Timing Diagram

Table 30. SDRAM Read Cycle Timing Parameter

| Ref | Parameter                        | 1.8 V   | ± 0.1 V | 3.0 V   | Unit    |       |

|-----|----------------------------------|---------|---------|---------|---------|-------|

| No. | raiametei                        | Minimum | Maximum | Minimum | Maximum | Oilit |

| 1   | SDRAM clock high-level width     | 3.00    | _       | 3       | _       | ns    |

| 2   | SDRAM clock low-level width      | 3.00    | _       | 3       | _       | ns    |

| 3   | SDRAM clock cycle time           | 7.5     | _       | 7.5     | _       | ns    |

| 3S  | CS, RAS, CAS, WE, DQM setup time | 4.78    | _       | 3       | _       | ns    |

| ЗН  | CS, RAS, CAS, WE, DQM hold time  | 3.03    | _       | 2       | _       | ns    |

MC94MX21 Technical Data, Rev. 1.4

**Table 31. SDRAM Write Cycle Timing Parameter**

| Ref | Parameter                           | 1.8 V                         | ± 0.1 V | 3.0 V                         | Unit    |       |

|-----|-------------------------------------|-------------------------------|---------|-------------------------------|---------|-------|

| No. | Farameter                           | Minimum                       | Maximum | Minimum                       | Maximum | Oille |

| 1   | SDRAM clock high-level width        | 3.00                          | _       | 3                             | -       | ns    |

| 2   | SDRAM clock low-level width         | 3.00                          | _       | 3                             | _       | ns    |

| 3   | SDRAM clock cycle time              | 7.5                           | _       | 7.5                           | -       | ns    |

| 4   | Address setup time                  | 3.67                          | _       | 2                             | _       | ns    |

| 5   | Address hold time                   | 2.95                          | _       | 2                             | _       | ns    |

| 6   | Precharge cycle period <sup>1</sup> | t <sub>RP</sub> <sup>2</sup>  | _       | t <sub>RP</sub> <sup>2</sup>  | _       | ns    |

| 7   | Active to read/write command delay  | t <sub>RCD</sub> <sup>2</sup> | _       | t <sub>RCD</sub> <sup>2</sup> | _       | ns    |

| 8   | Data setup time                     | 3.41                          | _       | 2                             | -       | ns    |

| 9   | Data hold time                      | 2.45                          | _       | 2                             | -       | ns    |

- 1. Precharge cycle timing is included in the write timing diagram.

- 2.  $t_{RP}$  and  $t_{RCD}$  = SDRAM clock cycle time. These settings can be found in the i.MX21 reference manual.

MC94MX21 Technical Data, Rev. 1.4

**Table 32. SDRAM Refresh Timing Parameters**

| Ref | Parameter                     | 1.8 V             | ± 0.1 V | 3.0 V             | Unit    |       |

|-----|-------------------------------|-------------------|---------|-------------------|---------|-------|

| No. |                               |                   | Maximum | Minimum           | Maximum | Oille |

| 1   | SDRAM clock high-level width  | 3.00              | _       | 3                 | _       | ns    |

| 2   | SDRAM clock low-level width   | 3.00              | _       | 3                 | _       | ns    |

| 3   | SDRAM clock cycle time        | 7.5               | _       | 7.5               | _       | ns    |

| 4   | Address setup time            | 3.67              | _       | 2                 | _       | ns    |

| 5   | Address hold time             | 2.95              | _       | 2                 | _       | ns    |

| 6   | Precharge cycle period        | t <sub>RP</sub> 1 | _       | t <sub>RP</sub> 1 | -       | ns    |

| 7   | Auto precharge command period | t <sub>RC</sub> 1 | _       | t <sub>RC</sub> 1 | -       | ns    |

<sup>1.</sup>  $t_{RP}$  and  $t_{RC}$  = SDRAM clock cycle time. These settings can be found in the i.MX21 reference manual.

Figure 41. SDRAM Self-Refresh Cycle Timing Diagram

### 3.16 Synchronous Serial Interface

The transmit and receive sections of the SSI can be synchronous or asynchronous. In synchronous mode, the transmitter and the receiver use a common clock and frame synchronization signal. In asynchronous mode, the transmitter and receiver each have their own clock and frame synchronization signals. Continuous or gated clock mode can be selected. In continuous mode, the clock runs continuously. In gated clock mode, the clock functions only during transmission. The internal and external clock timing diagrams are shown in Figure 42 through Figure 45.

Normal or network mode can also be selected. In normal mode, the SSI functions with one data word of I/O per frame. In network mode, a frame can contain between 2 and 32 data words. Network mode is typically used in star or ring-time division multiplex networks with other processors or codecs, allowing interface to time division multiplexed networks without additional logic. Use of the gated clock is not allowed in network mode. These distinctions result in the basic operating modes that allow the SSI to communicate with a wide variety of devices.

The SSI can be connected to 4 set of ports, SAP, SSI1, SSI2 and SSI3.

Note: SRXD input in synchronous mode only.

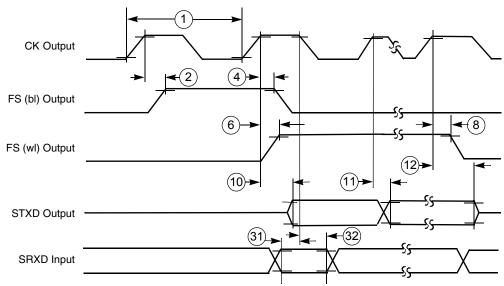

Figure 42. SSI Transmitter Internal Clock Timing Diagram

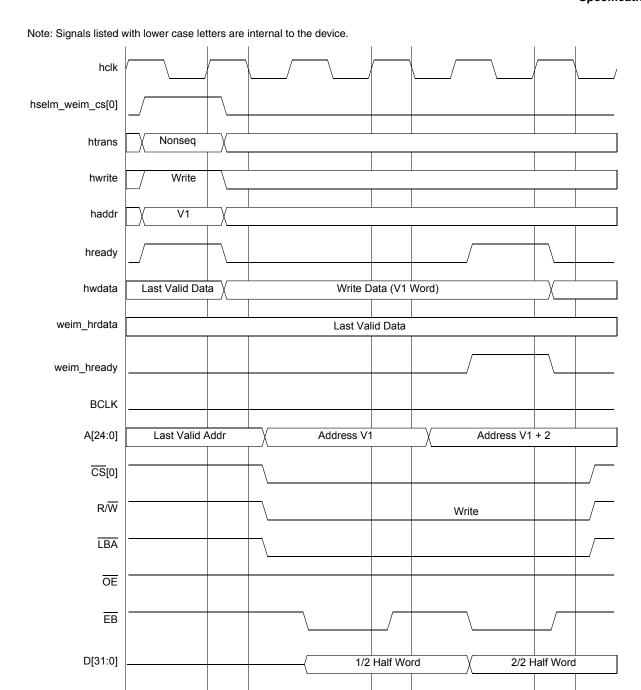

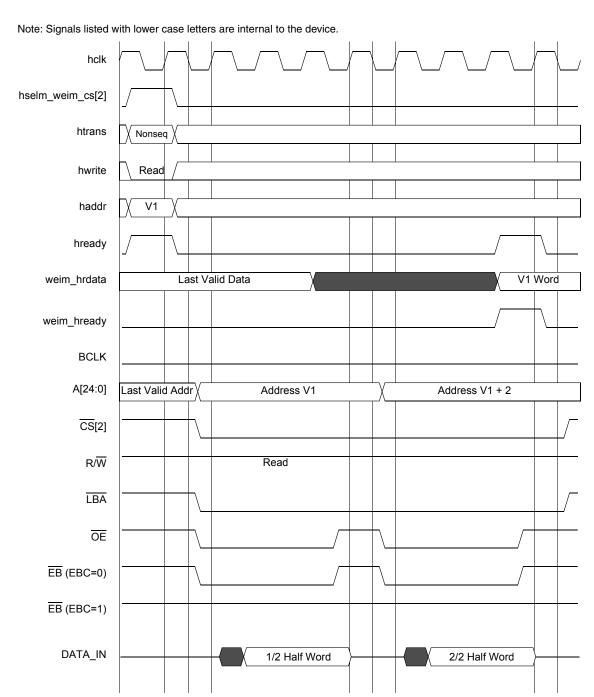

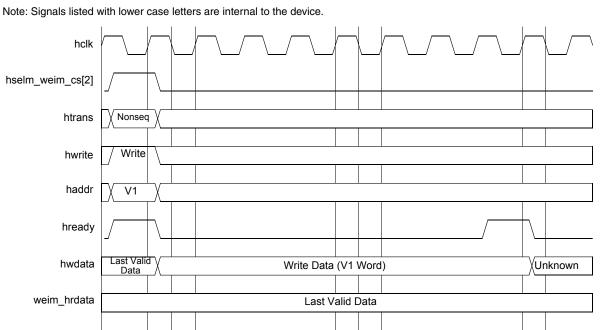

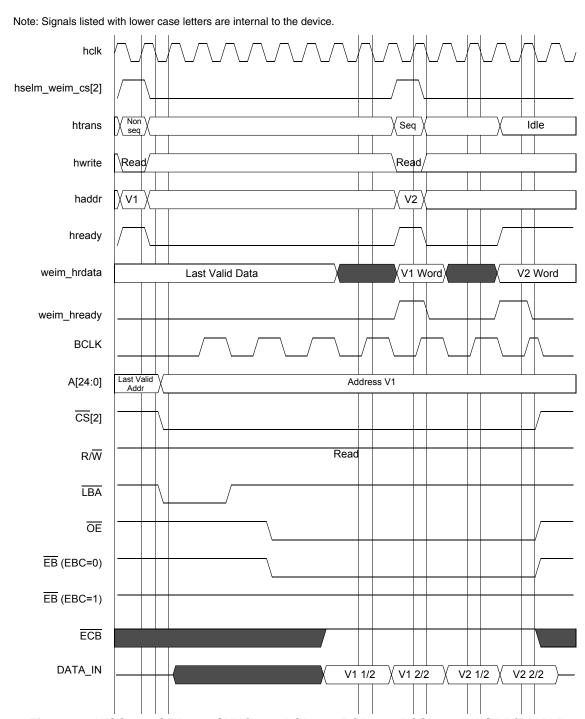

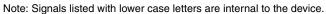

Figure 57. WSC = 1, WEA = 1, WEN = 1, A.WORD/E.HALF

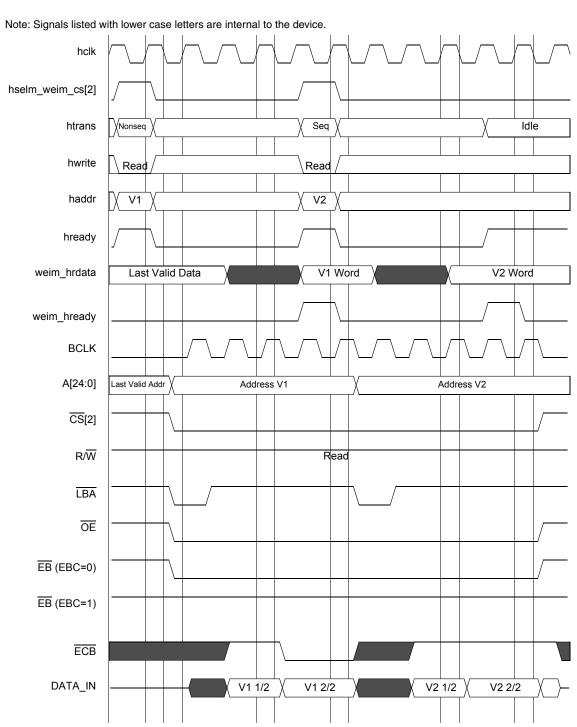

Figure 62. WSC = 3, OEN = 2, A.WORD/E.HALF

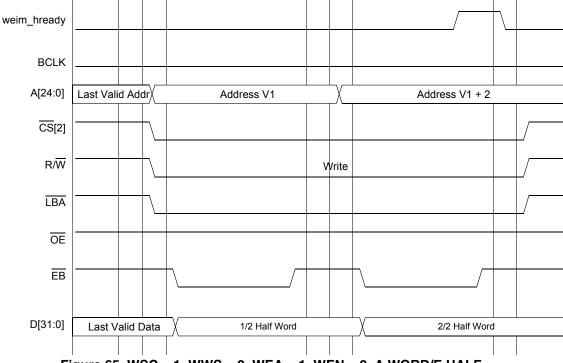

Figure 65. WSC = 1, WWS = 2, WEA = 1, WEN = 2, A.WORD/E.HALF

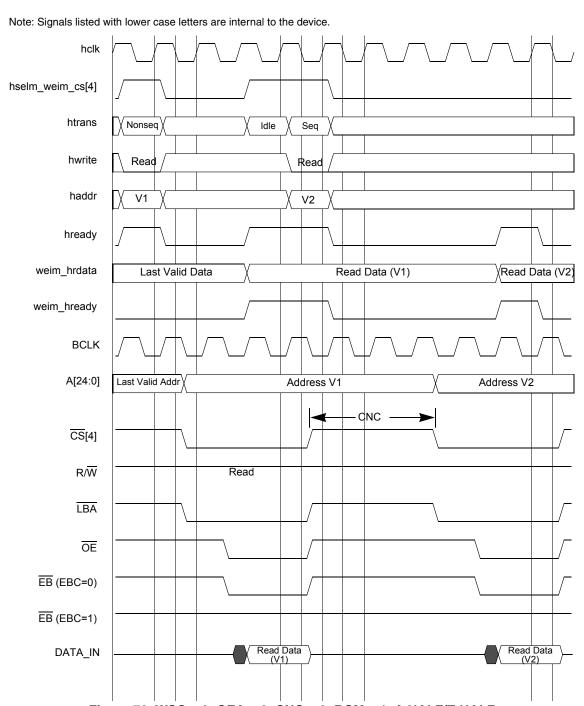

Figure 70. WSC = 2, OEA = 2, CNC = 3, BCM = 1, A.HALF/E.HALF

Figure 74. WSC = 2, SYNC = 1, DOL = [1/0], A.WORD/E.HALF

Figure 75. WSC = 7, OEA = 8, SYNC = 1, DOL = 1, BCD = 1, BCS = 2, A.WORD/E.HALF

Figure 76. WSC = 7, OEA = 8, SYNC = 1, DOL = 1, BCD = 1, BCS = 1, A.WORD/E.HALF

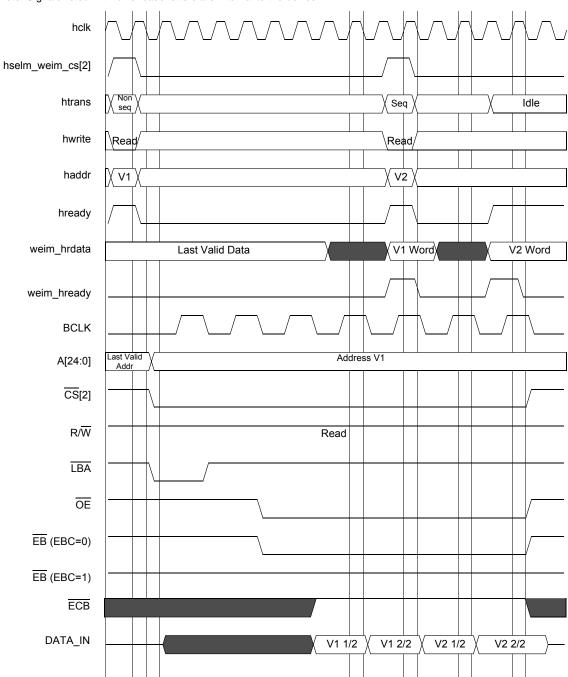

Figure 84. Sensor Output Data on Pixel Clock Rising Edge CSI Latches Data on Pixel Clock Falling Edge

Table 45. Non-Gated Clock Mode Parameters<sup>1</sup>

| Number | Parameter               | Minimum               | Maximum  | Unit |

|--------|-------------------------|-----------------------|----------|------|

| 1      | csi_vsync to csi_pixclk | 9 * T <sub>HCLK</sub> | -        | ns   |

| 2      | csi_d setup time        | 1                     | -        | ns   |

| 3      | csi_d hold time         | 1                     | -        | ns   |

| 4      | csi_pixclk high time    | T <sub>HCLK</sub>     | -        | ns   |

| 5      | csi_pixclk low time     | T <sub>HCLK</sub>     | -        | ns   |

| 6      | csi_pixclk frequency    | 0                     | HCLK / 2 | MHz  |

<sup>1.</sup> HCLK = AHB System Clock, T<sub>HCLK</sub> = Period of HCLK

### 3.22.3 Calculation of Pixel Clock Rise/Fall Time

The limitation on pixel clock rise time/fall time is not specified. It should be calculated from the hold time and setup time based on the following assumptions:

Rising-edge latch data

- max rise time allowed = (positive duty cycle hold time)

- max fall time allowed = (negative duty cycle setup time)

In most of case, duty cycle is 50 / 50, therefore:

- max rise time = (period / 2 hold time)

- max fall time = (period / 2 setup time)

For example: Given pixel clock period = 10 ns, duty cycle = 50 / 50, hold time = 1 ns, setup time = 1 ns.

positive duty cycle = 10 / 2 = 5ns  $\ge$  max rise time allowed = 5 - 1 = 4ns negative duty cycle = 10 / 2 = 5ns  $\ge$  max fall time allowed = 5 - 1 = 4ns

### Falling-edge latch data

- max fall time allowed = (negative duty cycle hold time)

- max rise time allowed = (positive duty cycle setup time)

MC94MX21 Technical Data, Rev. 1.4

MC94MX21 Technical Data, Rev. 1.4

# 4 Pin Assignment and Package Information

Table 46. i.MX21 Pin Assignment

|   | 1              | 2              | 3              | 4           | 5     | 6            | 7      | 8           | 9              | 10             | 11             | 12             | 13            | 14            | 15             | 16             | 17              | 18         | 19             |

|---|----------------|----------------|----------------|-------------|-------|--------------|--------|-------------|----------------|----------------|----------------|----------------|---------------|---------------|----------------|----------------|-----------------|------------|----------------|

| Α | LD9            | LD12           | LD14           | REV         | HSYNC | OE_<br>ACD   | SD2_D2 | CSI_<br>D0  | CSI_<br>PIXCLK | CSI_<br>VSYNC  | USBH1_<br>FS   | USBH1_<br>OE   | USBG_<br>FS   | TOUT          | SAP_<br>TXDAT  | SSI1_<br>CLK   | SSI2_<br>RXDAT  | SSI2_TXDAT | SSI3_<br>FS    |

| В | LD7            | LD5            | LD11           | LD16        | PS    | CON<br>TRAST | SD2_D0 | SD2_<br>CMD | CSI_<br>D4     | CSI_D6         | USB_<br>PWR    | USBG_<br>SCL   | USBG_<br>TXDM | SAP_<br>FS    | SSI1_<br>FS    | SSI2_<br>FS    | SSI3_<br>TXDAT  | I2C_DATA   | CSPI2_<br>SS2  |

| С | LD1            | LD3            | LD6            | LD10        | LD17  | VSYNC        | SD2_D3 | CSI_<br>D1  | CSI_<br>MCLK   | CSI_<br>HSYNC  | USB_<br>OC     | USBH1_<br>RXDM | USBG_<br>RXDM | TIN           | SSI1_<br>TXDAT | SSI3_<br>RXDAT | SSI3_<br>CLK    | I2C_CLK    | CSPI2_<br>SS1  |

| D | LD2            | LD0            | LD13           | CLS         | QVDD  | QVSS         | SD2_D1 | SD2_<br>CLK | CSI_<br>D2     | CSI_D7         | USBH1_<br>TXDM | USBH1_<br>RXDP | USBG_<br>ON   | USBG_<br>RXDP | SAP_<br>RXDAT  | SSI1_<br>RXDAT | SSI2_<br>CLK    | CSPI2_SS0  | CSPI2_<br>SCLK |

| E | LD8            | LD4            | LD15           | SPL_<br>SPR |       |              |        |             |                |                |                |                |               |               |                | SAP_<br>CLK    | CSPI2_<br>MISO  | CSPI1_SS2  | CSPI2_<br>MOSI |

| F | A24_<br>NFIO14 | D31            | A25_<br>NFIO15 | LSCLK       |       |              |        |             |                |                |                |                |               |               |                | CSPI1_<br>SS1  | CSPI1_<br>MISO  | KP_ROW0    | CSPI1_<br>SS0  |

| G | A22_<br>NFIO12 | D29            | A23_<br>NFIO13 | D30         |       |              | NVDD6  | NVSS6       | CSI_D3         | USB_<br>BYP    | USBH_<br>ON    | USBG_<br>SDA   | USBG_<br>TXDP |               |                | KP_<br>ROW1    | KP_<br>ROW3     | UART2_CTS  | KP_<br>ROW4    |

| Н | A20            | D27            | A21_<br>NFIO11 | D28         |       |              | NVDD1  | NVSS5       | CSI_D5         | CSPI1_<br>SCLK | CSPI1_<br>RDY  | USBH1_<br>TXDP | USBG_<br>OE   |               |                | TEST_<br>WB4   | TEST_<br>WB2    | TEST_WB3   | PWMO           |

| J | A19            | A18            | D25            | D26         |       |              | NVDD1  | NVDD5       | NVDD4          | KP_<br>ROW5    | KP_<br>ROW2    | CSPI1_<br>MOSI | TEST_<br>WB0  |               |                | UART2_<br>RTS  | KP_COL1         | KP_COL0    | TEST_<br>WB1   |

| Κ | A16            | A17            | D23            | D24         |       |              | NVSS1  | NVSS4       | QVDDX          | UART1_<br>RXD  | TDO            | QVDD           | QVSS          |               |                | KP_<br>COL3    | KP_COL5         | KP_COL4    | KP_<br>COL2    |

| L | A14_<br>NFIO9  | A15_<br>NFIO10 | D21            | D22         |       |              | NVSS1  | NVDD3       | QVDD           | QVSS           | NFIO2          | NFWP           | UART1_<br>TXD |               |                | UART2_<br>TXD  | UART3_<br>RTS   | UART3_CTS  | UART3_<br>TXD  |

| M | D19            | A13_<br>NFIO8  | D20            | D18         |       |              | NVDD2  | NVDD3       | NVSS3          | QVSS           | NFIO7          | NFRB           | EXT_<br>48M   |               |                | UART2_<br>RXD  | UART3_<br>RXD   | UART1_RTS  | UART1_<br>CTS  |

| N | A11            | A12            | D17            | D16         |       |              | LBA    | NVSS3       | SDCKE0         | NVSS1          | NVSS1          | NVDD1          | NVDD1         |               |                | SD1_<br>D0     | TCK             | SD1_D1     | RTCK           |

| Р | <b>A</b> 9     | A10            | D15            | D14         |       |              |        |             |                |                |                |                |               |               |                | SD1_<br>D2     | SD1_<br>CMD     | TDI        | TMS            |

| R | A7             | A8             | D13            | D12         |       |              |        |             |                |                |                |                |               |               |                | SD1_<br>CLK    | EXT_<br>266M    | NVSS2      | TRST           |

| т | <b>A</b> 5     | A6             | EB3            | D10         | CS3   | CS1          | BCLK   | MA11        | RAS            | CAS            | NFIO5          | NFIO3          | NFWE          | RESET_<br>ĪN  | NFCE           | BOOT1          | SD1_D3          | CLKMODE1   | CLK<br>MODE0   |

| U | D11            | EB1            | EB2            | ŌĒ          | CS4   | D6           | ECB    | D3          | MA10           | PC_<br>PWRON   | PF16           | NFIO4          | NFIO1         | NFALE         | NFCLE          | POR            | BOOT2           | воотз      | XTAL32K        |

| V | A4             | EB0            | D9             | D8          | CS5   | D5           | CS0    | RW          | D1             | JTAG_<br>CTRL  | SDWE           | CLKO           | NFIO6         | QVSS          | RESET_<br>OUT  | воото          | OSC26M_<br>TEST | VDDA       | EXTAL<br>32K   |

| w | A3             | A2             | D7             | A1          | CS2   | A0           | D4     | D2          | D0             | SDCLK          | SDCKE1         | NFIO0          | NFRE          | QVDD          | QVSS           | EXTAL<br>26M   | XTAL26M         | QVDD       | QVSS           |