Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                  |

|----------------------------|------------------------------------------------------------------|

| Product Status             | Active                                                           |

| Core Processor             | e200z4                                                           |

| Core Size                  | 32-Bit Dual-Core                                                 |

| Speed                      | 200MHz                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, LINbus, SCI, SPI, UART/USART |

| Peripherals                | DMA, LVD, POR, Zipwire                                           |

| Number of I/O              | -                                                                |

| Program Memory Size        | 2MB (2M x 8)                                                     |

| Program Memory Type        | FLASH                                                            |

| EEPROM Size                | -                                                                |

| RAM Size                   | 128K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                                      |

| Data Converters            | A/D 12b SAR, 16b Sigma-Delta                                     |

| Oscillator Type            | Internal                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                               |

| Mounting Type              | Surface Mount                                                    |

| Package / Case             | 144-LQFP                                                         |

| Supplier Device Package    | 144-LQFP (20x20)                                                 |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=spc5743rk1mlq5      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

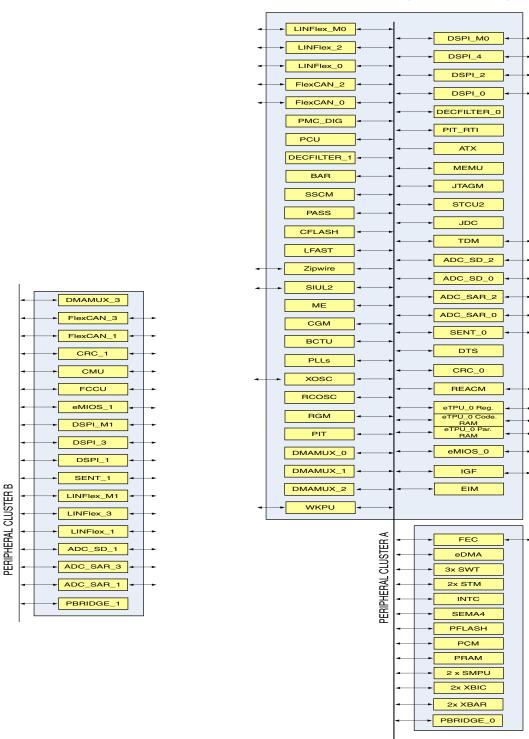

Figure 2. Peripherals allocation

# 2 Package pinouts and signal descriptions

For package pinouts and signal descriptions, refer to the Reference Manual.

| Symbol                                | Parameter                                              | Conditions <sup>1</sup>                                    | V    | alue | Unit |

|---------------------------------------|--------------------------------------------------------|------------------------------------------------------------|------|------|------|

| Symbol                                |                                                        | Conditions                                                 | Min  | Мах  |      |

| I <sub>INJA</sub>                     | Maximum DC injection current for analog pad            | Per pin, applies to all analog pins                        | -5   | 5    | mA   |

| I <sub>MAXSEG</sub> <sup>10, 11</sup> | Maximum current per I/O segment                        | —                                                          | -120 | 120  | mA   |

| T <sub>STG</sub>                      | Storage temperature range and non-<br>operating times  | _                                                          | -55  | 175  | °C   |

| STORAGE                               | Maximum storage time, assembled part programmed in ECU | No supply; storage temperature<br>in range –40 °C to 60 °C |      | 20   | yrs  |

| T <sub>SDR</sub>                      | Maximum solder temperature <sup>12</sup>               |                                                            | —    | 260  | °C   |

|                                       | Pb-free package                                        |                                                            |      |      |      |

| MSL                                   | Moisture sensitivity level <sup>13</sup>               | —                                                          | —    | 3    | —    |

Table 1. Absolute maximum ratings (continued)

- 1. Voltage is referenced to  $V_{\text{SS}}$  unless otherwise noted.

- Allowed 1.45 1.5 V for 60 seconds cumulative time at maximum T<sub>J</sub> = 150 °C, remaining time as defined in note -1 and note -1.

- 3. Allowed 1.375 1.45 V for 10 hours cumulative time at maximum  $T_J = 150$  °C, remaining time as defined in note -1.

- 4. 1.32 1.375 V range allowed periodically for supply with sinusoidal shape and average supply value below 1.275 V at maximum T<sub>J</sub> = 150 °C.

- 5. Allowed 5.5 6.0 V for 10 hours cumulative time at maximum T<sub>J</sub> = 150 °C, remaining time at or below 5.0 V +10%.

- 6. Allowed 3.6 4.5 V for 10 hours cumulative time at maximum  $T_J = 150$  °C, remaining time at or below 3.3 V +10%. This is an internally regulated supply. Values given are for reference only.

- 7. The maximum input voltage on an I/O pin tracks with the associated I/P supply maximum. For the injection current condition on a pin, the voltage will be equal to the supply plus the voltage drop across the internal ESD diode from I/O pin to supply. The diode voltage varies greatly across process and temperature, but a value of 0.3V can be used for nominal calculations.

- Relative value can be exceeded, if design measures are taken to ensure injection current limitation (parameters I<sub>INJD</sub> and I<sub>INJA</sub>).

- 9. V<sub>DD\_HV\_IO</sub>/V<sub>SS\_HV\_IO</sub> refers to supply pins and corresponding grounds: V<sub>DD\_HV\_IO\_MAIN</sub>, V<sub>DD\_HV\_IO\_JTAG</sub>, V<sub>DD\_HV\_IO\_FEC</sub>, V<sub>DD\_HV\_IO\_MSC</sub>.

- 10. Sum of all controller pins (including both digital and analog) must not exceed 200 mA. A V<sub>DD\_HV\_IO</sub> power segment is defined as one or more GPIO pins located between two V<sub>DD\_HV\_IO</sub> supply pins.

- 11. The average current values given in the "I/O pad current specifications" section should be used to calculate total I/O segment current.

- 12. Solder profile per IPC/JEDEC J-STD-020D.

- 13. Moisture sensitivity per JEDEC test method A112.

# 4 Electromagnetic Compatibility (EMC)

EMC measurements to IC-level IEC standards are available from Freescale on request.

# 5 Electrostatic discharge (ESD)

The following table describes the ESD ratings of the device.

#### **Oscillator and FMPLL**

# Table 15. XOSC External Oscillator electrical specifications (continued)

| Symbol             | Symbol Parameter Conditions                                       |                                            | ۱<br>۱                     | Unit |     |    |

|--------------------|-------------------------------------------------------------------|--------------------------------------------|----------------------------|------|-----|----|

| Symbol             | Farameter                                                         |                                            | Julions                    | Min  | Мах |    |

|                    |                                                                   |                                            | f <sub>XTAL</sub> ≤ 40 MHz | 12   | 43  |    |

| V <sub>EXTAL</sub> | Oscillation Amplitude on the EXTAL pin after startup <sup>7</sup> | $T_J = -40 \ ^{\circ}C$ to 150 $^{\circ}C$ |                            | 0.5  | 1.6 | V  |

| I <sub>XTAL</sub>  | XTAL current <sup>7</sup> , <sup>8</sup>                          | $T_J = -40 \ ^{\circ}C$ to 150 $^{\circ}C$ |                            | —    | 14  | mA |

- 1. The range is selectable by UTEST miscellaneous DCF clients XOSC\_LF\_EN and XOSC\_EN\_40MHZ.

- 2. This value is determined by the crystal manufacturer and board design.

- 3. Proper PC board layout procedures must be followed to achieve specifications.

- 4. Crystal recovery time is the time for the oscillator to settle to the correct frequency after adjustment of the integrated load capacitor value.

- 5. This parameter is guaranteed by design rather than 100% tested.

- 6. See crystal manufacturer's specification for recommended load capacitor (C<sub>L</sub>) values. The external oscillator requires external load capacitors when operating from 8 MHz to 16 MHz. Account for on-chip stray capacitance (C<sub>S\_EXTAL</sub>/C<sub>S\_XTAL</sub>) and PCB capacitance when selecting a load capacitor value. When operating at 20 MHz/40 MHz, the integrated load capacitor value is selected via S/W to match the crystal manufacturer's specification, while accounting for on-chip and PCB capacitance. The capacitance on "EXTAL" and "XTAL" by internal capacitance array is controlled by the XOSC LOAD CAP SEL field of the UTEST Miscellaneous DCF client. See the DCF Records chapter of the Reference Manual.

- 7. Amplitude on the EXTAL pin after startup is determined by the ALC block, i.e., the Automatic Level Control Circuit. The function of the ALC is to provide high drive current during oscillator startup, but reduce current after oscillation in order to reduce power, distortion, and RFI, and to avoid overdriving the crystal. The operating point of the ALC is dependent on the crystal value and loading conditions.

- 8. IXTAL is the oscillator bias current out on the XTAL pin with both EXTAL and XTAL pins grounded. This is the maximum current during startup of the oscillator. The current after oscillation is typically in the 2-3 mA range and is dependent on the load and series resistance of the crystal. Test circuit is shown in the figure below.

| load_cap_sel[4:0] from DCF record | Capacitance on EXTAL (C <sub>EXTAL</sub> )/XTAL (C <sub>XTAL</sub> ) <sup>, 1, 2</sup> (pF) |

|-----------------------------------|---------------------------------------------------------------------------------------------|

| 00000                             | 1.0                                                                                         |

| 00001                             | 2.0                                                                                         |

| 00010                             | 2.9                                                                                         |

| 00011                             | 3.8                                                                                         |

| 00100                             | 4.8                                                                                         |

| 00101                             | 5.7                                                                                         |

| 00110                             | 6.6                                                                                         |

| 00111                             | 7.5                                                                                         |

| 01000                             | 8.5                                                                                         |

| 01001                             | 9.4                                                                                         |

| 01010                             | 10.3                                                                                        |

| 01011                             | 11.2                                                                                        |

| 01100                             | 12.2                                                                                        |

| 01101                             | 13.1                                                                                        |

| 01110                             | 14.0                                                                                        |

## Table 16. Selectable load capacitance

Table continues on the next page ...

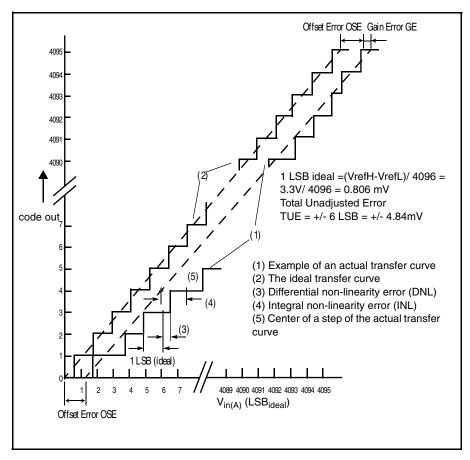

# 11.2 SAR ADC

The device provides a 12-bit Successive Approximation Register (SAR) Analog-to-Digital Converter.

Figure 10. ADC characteristics and error definitions

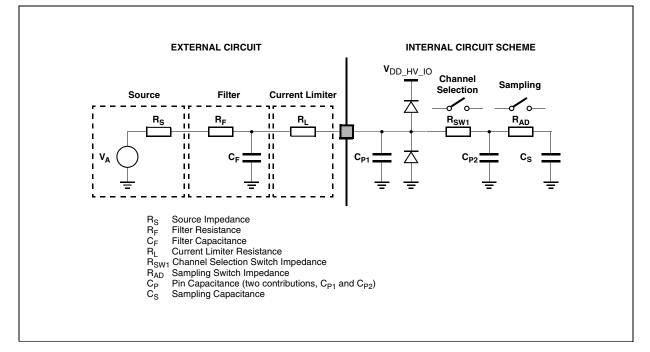

## 11.2.1 Input equivalent circuit and ADC conversion characteristics

## Figure 11. Input equivalent circuit

|                                | Table 19. ADC                                                                                                         | conversion charact                    | Table 19. ADC conversion characteristics |     |      |      |  |  |  |  |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------|-----|------|------|--|--|--|--|--|

| Symbol                         | Parameter                                                                                                             | Conditions <sup>1</sup>               | Min                                      | Тур | Max  | Unit |  |  |  |  |  |

| f <sub>CK</sub> , <sup>2</sup> | ADC Clock frequency (depends<br>on ADC configuration) (The duty<br>cycle depends on AD_CK <sup>3</sup><br>frequency.) |                                       | 20                                       |     | 80   | MHz  |  |  |  |  |  |

| f <sub>s</sub>                 | Sampling frequency                                                                                                    | _                                     | —                                        | —   | 1.00 | MHz  |  |  |  |  |  |

| t <sub>sample</sub>            | Sample time <sup>4</sup>                                                                                              | —                                     | 250                                      | —   | _    | ns   |  |  |  |  |  |

| t <sub>conv</sub>              | Conversion time <sup>5</sup>                                                                                          | 80 MHz                                | 700                                      | _   | _    | ns   |  |  |  |  |  |

| C <sub>S</sub> , <sup>6</sup>  | ADC input sampling capacitance                                                                                        | —                                     | _                                        | 3   | 5    | pF   |  |  |  |  |  |

| C <sub>P1</sub> <sup>6</sup>   | ADC input pin capacitance 1                                                                                           | —                                     | _                                        | _   | 5    | pF   |  |  |  |  |  |

| C <sub>P2</sub> <sup>6</sup>   | ADC input pin capacitance 2                                                                                           | —                                     | _                                        | —   | 0.8  | pF   |  |  |  |  |  |

| R <sub>SW1</sub> <sup>6</sup>  | Internal resistance of analog                                                                                         | V <sub>REF</sub> range = 4.5 to 5.5 V | _                                        | _   | 0.3  | kΩ   |  |  |  |  |  |

|                                | source                                                                                                                | V <sub>REF</sub> range = 3.0 to 3.6 V |                                          | —   | 875  | Ω    |  |  |  |  |  |

| R <sub>AD</sub> <sup>6</sup>   | Internal resistance of analog source                                                                                  | —                                     | —                                        | _   | 825  | Ω    |  |  |  |  |  |

| INL                            | Integral non-linearity                                                                                                | —                                     | -2                                       | —   | 2    | LSB  |  |  |  |  |  |

| DNL                            | Differential non-linearity                                                                                            | —                                     | -1                                       | _   | 1    | LSB  |  |  |  |  |  |

| OFS <sup>7</sup>               | Offset error                                                                                                          | —                                     | -6                                       |     | 6    | LSB  |  |  |  |  |  |

| GNE <sup>7</sup>               | Gain error                                                                                                            | —                                     | -6                                       | —   | 6    | LSB  |  |  |  |  |  |

| Input (double ADC channel)     | Max leakage                                                                                                           | 150 °C                                | —                                        | —   | 300  | nA   |  |  |  |  |  |

## Table 19. ADC conversion characteristics

Table continues on the next page ...

#### NXP Semiconductors

| Symbol                             | Parameter                              | Conditions <sup>1</sup>                                    | Min   | Тур        | Max   | Unit |

|------------------------------------|----------------------------------------|------------------------------------------------------------|-------|------------|-------|------|

| SNR                                | Signal-to-noise ratio                  | $V_{REF} = 3.3 \text{ V}, \text{ Fin} \le 125 \text{ kHz}$ | 66    | _          | _     | dB   |

| SNR                                | Signal-to-noise ratio                  | $V_{REF} = 5.0 \text{ V}, \text{ Fin} \le 125 \text{ kHz}$ | 68    | _          | _     | dB   |

| THD                                | Total harmonic distortion              | @ 125 kHz                                                  | 65    | 70         | —     | dB   |

| ENOB <sup>8</sup>                  | Effective number of bits               | Fin < 125 kHz                                              | 10.5  | —          | —     | bits |

| SINAD                              | Signal-to-noise and distortion         | Fin < 125 kHz                                              | (6.0  | )2*ENOB)+1 | .76   | dB   |

| TUE <sub>IS1WINJ</sub>             | Total unadjusted error for IS1WINJ     | Without current injection                                  | -6    | _          | 6     | LSB  |

| TUE <sub>IS1WWINJ</sub>            | Total unadjusted error for<br>IS1WWINJ | Without current injection                                  | -6    | _          | 6     | LSB  |

| I <sub>DD_VDDA</sub>               | Maximum operating current on VDDA      | Tj = 150C VDD_LV_COR<br>= 1.32 V                           | _     | 3.7        | 5     | mA   |

| I <sub>DD_VDDR</sub>               | Maximum operating current on VREF      | Tj = 150C VDD_LV_COR<br>= 1.32 V                           | —     | 150        | 600   | μA   |

| V <sub>BG_REF</sub> <sup>, 9</sup> | Band gap reference for self test       | Trimmed,<br>INPSAMP=0xFF                                   | 1.164 | 10         | 1.236 | V    |

Table 19. ADC conversion characteristics (continued)

- 1.  $V_{DD_HV_IO} = 3.3 \text{ V} -5\%$ ,+10%,  $T_J = -40$  to +150 °C, unless otherwise specified, and analog input voltage from  $V_{AGND}$  to  $V_{AREF}$

- 2. SAR ADC performance is not guaranteed when IRC is used as clock source for PLL0 to generate SAR ADC clock.

- 3. AD\_CK clock is always half of the ADC module input clock defined via the auxiliary clock divider for the ADC.

- 4. During the sample time the input capacitance C<sub>S</sub> can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>sample</sub>. After the end of the sample time t<sub>sample</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample clock t<sub>sample</sub> depend on programming.

- 5. This parameter does not include the sample time t<sub>sample</sub>, but only the time for determining the digital result and the time to load the result register with the conversion result.

- 6. See the above figure.

- 7. Subject to change with additional -40°C characterization on final silicon version.

- 8. Below 4.5V, ENOB 9.5b, THD- 60dB at Fin= 125KHz

- 9. Band gap reference only applies to Cut 2 silicon.

- 10. Minimum and maximum values are typical +/-3%

## NOTE

- For spec complaint operation, do not expose clock sources, including crystal oscillator, IRC, PLL0, and PLL1 on the CLKOUT pads while the SAR ADC is converting.

- The ADC performance specifications are not guaranteed if two or more ADCs simultaneously sample the same shared channel.

## 11.3 S/D ADC

The SD ADCs are Sigma Delta 16-bit analog-to-digital converters with 333 Ksps maximum output rate.

| Symbol                   | Paramotor                                 | Conditions                                |      | Value<br>Min Typ Max |     | 110:4 |

|--------------------------|-------------------------------------------|-------------------------------------------|------|----------------------|-----|-------|

| Symbol                   | Parameter                                 | Conditions                                | Min  | Тур                  | Max | Unit  |

| SINAD <sub>DIFF150</sub> | Signal to Noise                           | $4.5 < V_{DD_{HV}ADV_{SD}} < 5.5^{7}$     | 72   | _                    | —   | dB    |

|                          | Distortion Ratio in differential mode 150 | $V_{DD_{HV}ADR_{D}} = V_{DD_{HV}ADV_{D}}$ |      |                      |     |       |

|                          | ksps output rate                          | GAIN = 1                                  |      |                      |     |       |

|                          |                                           | T <sub>J</sub> < 150 °C                   |      |                      |     |       |

|                          |                                           | $4.5 < V_{DD_HV_ADV_SD} < 5.5^7$          | 72   | _                    | —   |       |

|                          |                                           | $V_{DD_{HV}ADR_{SD}} =$                   |      |                      |     |       |

|                          |                                           | V <sub>DD_HV_ADV_SD</sub>                 |      |                      |     |       |

|                          |                                           | GAIN = 2                                  |      |                      |     |       |

|                          |                                           | T <sub>J</sub> < 150 °C                   |      |                      |     |       |

|                          |                                           | $4.5 < V_{DD_{HV}ADV_{SD}} < 5.5^{7}$     | 69   | _                    | _   |       |

|                          |                                           | $V_{DD_HV_ADR_SD} =$                      |      |                      |     |       |

|                          |                                           | V <sub>DD_HV_ADV_SD</sub>                 |      |                      |     |       |

|                          |                                           | GAIN = 4                                  |      |                      |     |       |

|                          |                                           | T <sub>J</sub> < 150 °C                   |      |                      |     |       |

|                          |                                           | $4.5 < V_{DD_{HV}ADV_{SD}} < 5.5^{7}$     | 68.8 | _                    | _   |       |

|                          |                                           | $V_{DD_HV_ADR_SD} =$                      |      |                      |     |       |

|                          |                                           | V <sub>DD_HV_ADV_SD</sub>                 |      |                      |     |       |

|                          |                                           | GAIN = 8                                  |      |                      |     |       |

|                          |                                           | T <sub>J</sub> < 150 °C                   |      |                      |     |       |

|                          |                                           | $4.5 < V_{DD_{HV}ADV_{SD}} < 5.5^{7}$     | 64.8 | _                    | _   |       |

|                          |                                           | $V_{DD_HV_ADR_SD} =$                      |      |                      |     |       |

|                          |                                           | V <sub>DD_HV_ADV_SD</sub>                 |      |                      |     |       |

|                          |                                           | GAIN = 16                                 |      |                      |     |       |

|                          |                                           | T <sub>J</sub> < 150 °C                   |      |                      |     |       |

| SINAD <sub>DIFF333</sub> | Signal to Noise                           | $4.5 < V_{DD_{HV}ADV_{SD}} < 5.5^{7}$     | 66   | _                    | _   | dB    |

|                          | Distortion Ratio in differential mode 333 | $V_{DD_HV_ADR_SD} =$                      |      |                      |     |       |

|                          | ksps output rate                          | V <sub>DD_HV_ADV_SD</sub>                 |      |                      |     |       |

|                          |                                           | GAIN = 1                                  |      |                      |     |       |

|                          |                                           | T <sub>J</sub> < 150 °C                   |      |                      |     |       |

|                          |                                           | $4.5 < V_{DD_{HV}ADV_{SD}} < 5.5^{7}$     | 66   | _                    | _   |       |

|                          |                                           | $V_{DD_HV_ADR_SD} =$                      |      |                      |     |       |

|                          |                                           | V <sub>DD_HV_ADV_SD</sub>                 |      |                      |     |       |

|                          |                                           | GAIN = 2                                  |      |                      |     |       |

|                          |                                           | T <sub>J</sub> < 150 °C                   |      |                      |     |       |

|                          |                                           | $4.5 < V_{DD\_HV\_ADV\_SD} < 5.5^7$       | 63   | _                    | _   |       |

|                          |                                           | V <sub>DD_HV_ADR_SD</sub> =               |      |                      |     |       |

|                          | 1                                         |                                           |      |                      |     |       |

## Table 20. SDn ADC electrical specification (continued)

Table continues on the next page ...

#### Aurora LVDS electrical characteristics

# Table 25. LFAST PLL electrical characteristics (continued)

| Symbol Parameter    |                                               | Conditions                   |      | Value   |     |      |  |

|---------------------|-----------------------------------------------|------------------------------|------|---------|-----|------|--|

| Symbol              | Farameter                                     | Conditions                   | Min  | Nominal | Max | Unit |  |

|                     |                                               | Long term,                   | -500 | —       | 500 | ps   |  |

|                     |                                               | f <sub>RF_REF</sub> = 10 MHz |      |         |     |      |  |

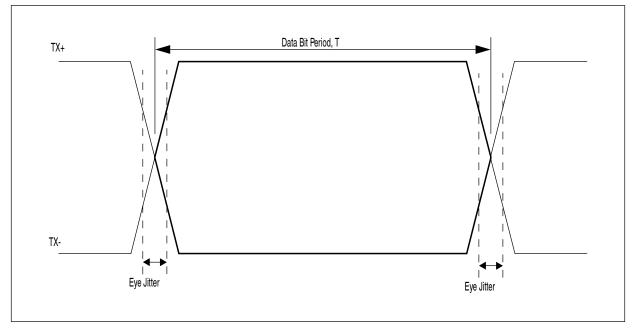

| ΔPER <sub>EYE</sub> | Output Eye Jitter (peak to peak) <sup>3</sup> | —                            | —    | 550     | _   | ps   |  |

- 1. The 640 MHz frequency is achieved with a 10 MHz or 20 MHz reference clock. With a 26 MHz reference, the VCO frequency is 624 MHz.

- 2. The time from the PLL enable bit register write to the start of phase locks is maximum 2 clock cycles of the peripheral bridge clock that is connected to the PLL on the device.

- 3. Measured at the transmitter output across a 100 Ohm termination resistor on a device evaluation board. Refer to the figure below.

Figure 16. LFAST output 'eye' diagram

# **15 Aurora LVDS electrical characteristics**

The following table describes the Aurora LVDS electrical characteristics.

All Aurora electrical characteristics are valid from -40 °C to 150 °C.

All specifications valid for maximum transmit data rate  $F_{TX}$ .

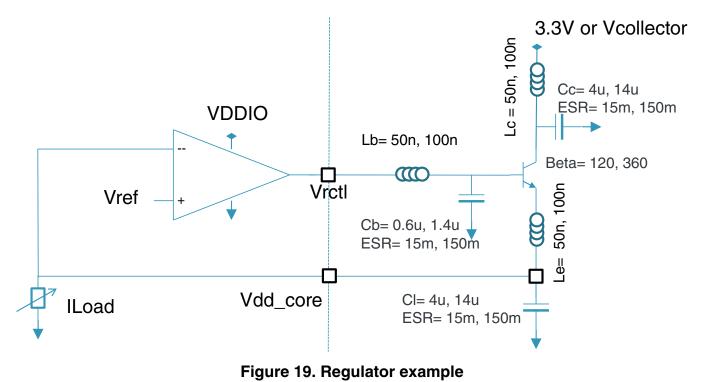

## 16.1.4 Regulator example for the 2SCR574d transistor

## 16.1.5 Device voltage monitoring

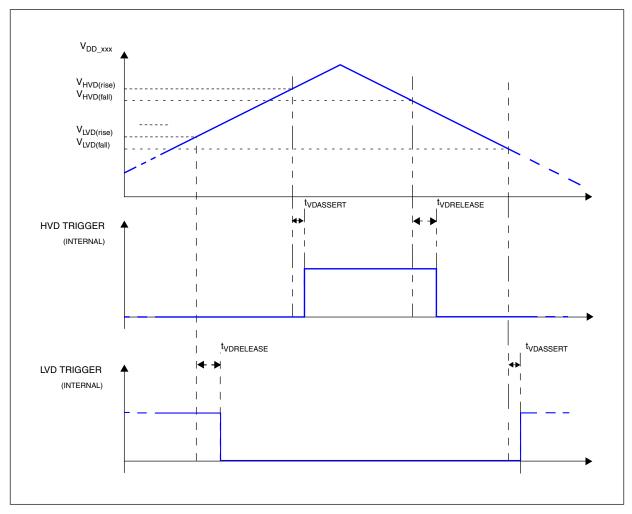

The LVD/HVDs for the device and their levels are given in the following table. Voltage monitoring threshold definition is provided in the following figure.

Figure 20. Voltage monitor threshold definition

For  $V_{DD_LV}$  levels, a maximum of 30 mV IR drop is incurred from the pin to all sinks on the die. For other LVD, the IR drop is estimated by multiplying the supply current by 0.5 ohm.

LVD is released after  $t_{VDRELEASE}$  temporization when upper threshold is crossed, LVD is asserted  $t_{VDASSERT}$  after detection when lower threshold is crossed.

HVD is released after  $t_{VDRELEASE}$  temporization when lower threshold is crossed, HVD is asserted  $t_{VDASSERT}$  after detection when upper threshold is crossed.

|                       |           |                              | Cor | figura           | tion        |     | Value |     |      |

|-----------------------|-----------|------------------------------|-----|------------------|-------------|-----|-------|-----|------|

| Symbol                | Parameter | Conditions                   |     | Mas<br>k<br>Opt. | Pow<br>. Up |     | Тур   | Max | Unit |

| POR085_c <sup>1</sup> |           | Rising voltage (power up)    | N/A | No               | Enab        | 870 | 920   | 970 | mV   |

|                       | reset     | Falling voltage (power down) |     |                  | •           | 850 | 900   | 950 |      |

Table 29.

Voltage monitor electrical characteristics

Table continues on the next page ...

- 1. Maximum usable frequency can be achieved if used with fastest configuration of the highest drive pads.

- 2. Maximum usable frequency does not take into account external device propagation delay.

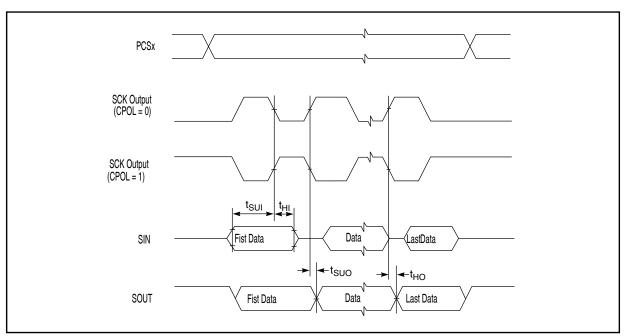

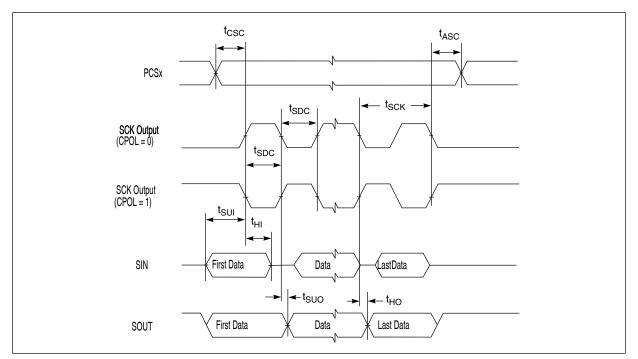

# 18.2.1 DSPI master mode full duplex timing with CMOS and LVDS pads

The values presented in these sections are target values. A complete performance characterization of the pads (in all configuration combinations) is required before the final specifications can be released.

## 18.2.1.1 DSPI CMOS master mode – classic timing

All output timing is worst case and includes the mismatching of rise and fall times of the output pads.

## NOTE

In Table 40, all output timing is worst case and includes the mismatching of rise and fall times of the output pads.

### Table 40. DSPI CMOS master classic timing (full duplex and output only) - MTFE = 0, CPHA = 0 or 1

| # | Symbol           | Characteristic   | Cone                         | dition                 | Val                                                      | ue <sup>1</sup> | Unit |

|---|------------------|------------------|------------------------------|------------------------|----------------------------------------------------------|-----------------|------|

|   |                  |                  | Pad drive <sup>2</sup>       | Load (C <sub>L</sub> ) | Min                                                      | Max             | 1    |

| 1 | t <sub>SCK</sub> | SCK cycle time   | SCK drive strength           | <u>.</u><br>ו          |                                                          |                 |      |

|   |                  |                  | Very strong                  | 25 pF                  | 33.0                                                     | _               | ns   |

|   |                  |                  | Strong                       | 50 pF                  | 80.0                                                     | _               |      |

|   |                  |                  | Medium                       | 50 pF                  | 200.0                                                    | _               |      |

| 2 | t <sub>CSC</sub> | PCS to SCK delay | SCK and PCS driv             | ve strength            |                                                          |                 |      |

|   |                  |                  | Very strong                  | 25 pF                  | (N <sup>3</sup> x t <sub>SYS</sub> <sup>, 4</sup> ) - 16 | _               | ns   |

|   |                  |                  | Strong                       | 50 pF                  | (N <sup>3</sup> x t <sub>SYS</sub> <sup>, 4</sup> ) - 16 | —               |      |

|   |                  |                  | Medium                       | 50 pF                  | (N <sup>3</sup> x t <sub>SYS</sub> <sup>, 4</sup> ) - 16 | _               |      |

|   |                  |                  | PCS medium and               | PCS = 50 pF            | (N <sup>3</sup> x t <sub>SYS</sub> <sup>, 4</sup> ) - 29 | —               |      |

|   |                  |                  | SCK strong                   | SCK = 50 pF            |                                                          |                 |      |

| 3 | t <sub>ASC</sub> | After SCK delay  | SCK and PCS driv             | ve strength            |                                                          |                 |      |

|   |                  |                  | Very strong                  | PCS = 0 pF             | (M <sup>5</sup> x t <sub>SYS</sub> <sup>4</sup> ) - 35   | _               | ns   |

|   |                  |                  |                              | SCK = 50 pF            |                                                          |                 |      |

|   |                  |                  | Strong                       | PCS = 0 pF             | (M <sup>5</sup> x t <sub>SYS</sub> <sup>, 4</sup> ) - 35 | _               |      |

|   |                  |                  |                              | SCK = 50 pF            |                                                          |                 |      |

|   |                  |                  | Medium                       | PCS = 0 pF             | (M <sup>5</sup> x t <sub>SYS</sub> <sup>, 4</sup> ) - 35 |                 |      |

|   |                  |                  |                              | SCK = 50 pF            |                                                          |                 |      |

|   |                  |                  | PCS medium and<br>SCK strong | PCS = 0 pF             | (M <sup>5</sup> x t <sub>SYS</sub> <sup>, 4</sup> ) - 35 | _               |      |

Table continues on the next page...

Figure 31. DSPI CMOS master mode – classic timing, CPHA = 1

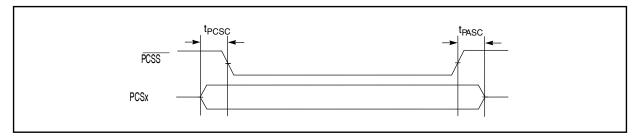

Figure 32. DSPI PCS strobe (PCSS) timing (master mode)

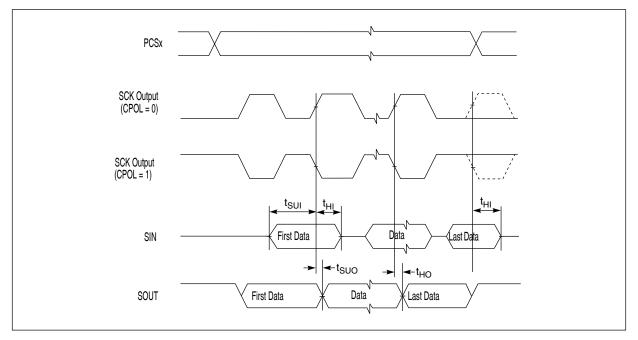

## 18.2.1.2 DSPI CMOS master mode – modified timing

All output timing is worst case and includes the mismatching of rise and fall times of the output pads.

## NOTE

In Table 41, all output timing is worst case and includes the mismatching of rise and fall times of the output pads.

# Table 41. DSPI CMOS master modified timing (full duplex and output only) - MTFE = 1,CPHA = 0 or 1

| # | Symbol           | Characteristic | Con                    | dition                 | Val  | Unit |    |

|---|------------------|----------------|------------------------|------------------------|------|------|----|

|   |                  |                | Pad drive <sup>2</sup> | Load (C <sub>L</sub> ) | Min  | Мах  |    |

| 1 | t <sub>SCK</sub> | SCK cycle time | SCK drive strengt      | า                      |      |      |    |

|   |                  |                | Very strong            | 25 pF                  | 33.0 | —    | ns |

|   |                  |                | Strong                 | 50 pF                  | 80.0 |      |    |

Table continues on the next page ...

#### **AC** specifications

Figure 36. DSPI LVDS master mode – modified timing, CPHA = 0

Figure 37. DSPI LVDS master mode – modified timing, CPHA = 1

## 18.2.1.4 DSPI master mode – output only

For Table 43 :

AC specifications

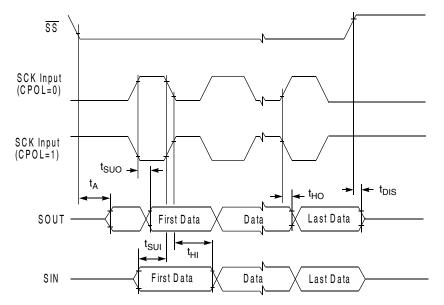

Figure 40. DSPI Slave Mode - Modified transfer format timing (MFTE = 0/1) — CPHA = 1

## 18.3 FEC timing

The FEC supports the 10/100 Mbps MII, 10/100 Mbps MII-lite, and the 10 Mbps-only 7-wire interface.

# 18.3.1 MII-lite receive signal timing (RXD[3:0], RX\_DV, RX\_ER, and RX\_CLK)

The receiver functions correctly up to a RX\_CLK maximum frequency of 25 MHz +1%. There is no minimum frequency requirement. The system clock frequency must be at least equal to or greater than the RX\_CLK frequency.

All timing specifications are referenced from RX\_CLK = 1.4 V to the valid input levels.

| Snoo | Spec Characteristic                    |     | lue | Unit          |

|------|----------------------------------------|-----|-----|---------------|

| Spec | Characteristic                         | Min | Max |               |

| M1   | RXD[3:0], RX_DV, RX_ER to RX_CLK setup | 5   | —   | ns            |

| M2   | RX_CLK to RXD[3:0], RX_DV, RX_ER hold  | 5   | —   | ns            |

| M3   | RX_CLK pulse width high                | 35% | 65% | RX_CLK period |

| M4   | RX_CLK pulse width low                 | 35% | 65% | RX_CLK period |

Table 46. MII-lite receive signal timing

| If you want the drawing for this package | Then use this document number |

|------------------------------------------|-------------------------------|

| LQFP 144 PD                              | 98ASS23177W                   |

| LQFP 176 PD                              | 98ASS23479W                   |

| MAPBGA 252 PD                            | 98ASA00468D                   |

| MAPBGA 292 ED                            | 98ASA00261D                   |

## 20 Thermal characteristics

The following tables describe the thermal characteristics of the device.

Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting side (board) temperature, ambient temperature, air flow, power dissipation or other components on the board, and board thermal resistance.

| Rating                                                    | Conditions              | Symbol            | Value | Unit |

|-----------------------------------------------------------|-------------------------|-------------------|-------|------|

| Junction to Ambient Natural Convection <sup>1, 2</sup>    | Single layer board (1s) | R <sub>θJA</sub>  | 41.3  | °C/W |

| Junction to Ambient Natural Convection <sup>1, 2, 3</sup> | Four layer board (2s2p) | R <sub>0JA</sub>  | 33.0  | °C/W |

| Junction to Ambient (@200 ft/min) <sup>1, 3</sup>         | Single layer board (1s) | R <sub>θJMA</sub> | 32.4  | °C/W |

| Junction to Ambient (@200 ft/min) <sup>1, 3</sup>         | Four layer board (2s2p) | R <sub>θJMA</sub> | 26.7  | °C/W |

| Junction to Board <sup>4</sup>                            | _                       | R <sub>θJB</sub>  | 21.5  | °C/W |

| Junction to Case <sup>5</sup>                             | _                       | R <sub>θJC</sub>  | 7.0   | °C/W |

| Junction to Package Top <sup>6</sup>                      | Natural Convection      | ΨJT               | 0.25  | °C/W |

| Junction to Package Lead <sup>7</sup>                     | Natural Convection      | Ψјв               | 16.5  | °C/W |

Table 56. Thermal characteristics for the 144-pin LQFP package

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 3. Per JEDEC JESD51-6 with the board horizontal.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2.

- 7. Thermal characterization parameter indicating the temperature difference between package bottom center and the junction temperature per JEDEC JESD51-12.

Table 57. Thermal characteristics for the 176-pin LQFP package

| Rating                                                    | Conditions              | Symbol           | Value | Unit |

|-----------------------------------------------------------|-------------------------|------------------|-------|------|

| Junction to Ambient Natural Convection <sup>1, 2</sup>    | Single layer board (1s) | R <sub>θJA</sub> | 49.9  | °C/W |

| Junction to Ambient Natural Convection <sup>1, 2, 3</sup> | Four layer board (2s2p) | R <sub>θJA</sub> | 33.8  | °C/W |

Table continues on the next page ...

7. Thermal characterization parameter indicating the temperature difference between package bottom center and the junction temperature per JEDEC JESD51-12.

# Table 59. Thermal characteristics for the 252-pin MAPBGA package 16 removed balls: 12central, 4 corner peripheral

| Rating                                                    | Conditions              | Symbol           | Value | Unit |

|-----------------------------------------------------------|-------------------------|------------------|-------|------|

| Junction to Ambient Natural Convection <sup>1, 2, 3</sup> | Four layer board (2s2p) | R <sub>θJA</sub> | 23.8  | °C/W |

| Junction to Board <sup>4</sup>                            | Four layer board (2s2p) | R <sub>θJB</sub> | 15.9  | °C/W |

| Junction to Package Lead <sup>5</sup>                     | Natural Convection      | Ψ <sub>JB</sub>  | 4.8   | °C/W |

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.

- 3. Per JEDEC JESD51-6 with the board horizontal.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal characterization parameter indicating the temperature difference between package bottom center and the junction temperature per JEDEC JESD51-12.

# 20.1 General notes for specifications at maximum junction temperature

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from this equation:

$T_J = T_A + (R_{\theta JA} \times P_D)$

where:

- $T_A$  = ambient temperature for the package (°C)

- $R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

- $P_D$  = power dissipation in the package (W)

The junction to ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single layer board and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which value is closer to the application depends on the power dissipated by other components on the board. The value obtained on a single layer board is appropriate for the tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.

When a heat sink is used, the thermal resistance is expressed in the following equation as the sum of a junction-to-case thermal resistance and a case-to-ambient thermal resistance:

$R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$

### Ordering information

where:

- $R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

- $R_{\theta JC}$  = junction to case thermal resistance (°C/W)

- $R_{\theta CA}$  = case to ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user. The user controls the thermal environment to change the case to ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device.

To determine the junction temperature of the device in the application when heat sinks are not used, the Thermal Characterization Parameter ( $\Psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using this equation:

$T_J = T_T + (\Psi_{JT} \times P_D)$

where:

- $T_T$  = thermocouple temperature on top of the package (°C)

- $\Psi_{JT}$  = thermal characterization parameter (°C/W)

- $P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

# 21 Ordering information

| Table 60.         Ordering information |  |

|----------------------------------------|--|

|----------------------------------------|--|

| Part Number      | Device Type            | Flash/SRAM  | Emulation RAM | Package    | Frequency |

|------------------|------------------------|-------------|---------------|------------|-----------|

| SPC5746RK1MMT5   | Sample PD <sup>1</sup> | 4M / 256 KB | -             | 252 MAPBGA | 200 MHz   |

| SPC5745RK1MLU3   | Sample PD              | 3M / 192 KB | -             | 176 LQFP   | 150 MHz   |

| SPC5743RK1MLQ5   | Sample PD              | 2M / 128 KB | -             | 144 LQFP   | 200 MHz   |

| PPC5746R2K1MMZ5A | Sample ED <sup>2</sup> | 4M / 256 KB | 1 MB          | 292 MAPBGA | 200 MHz   |

1. "PD" refers to a production device, orderable in quantity.

2. "ED" refers to an emulation device, orderable in limited quantities. An emulation device (ED) is for use during system development only and is not to be used in production. An ED is a Production PD chip combined with a companion chip to form an Emulation and Debug Device (ED) and includes additional RAM memory and debug features. EDs are provided

"as is" without warranty of any kind. In the event of a suspected ED failure, Freescale agrees to exchange the suspected failing ED from the customer at no additional charge, however Freescale will not analyze ED returns.

# 22 Revision history

Table 61. Revision history

| <ul> <li>to be characterized.</li> <li>In footnotes changed cross references to figures to static text.</li> <li>In section Block diagram : <ul> <li>In Figure 1, changed "AIPS Bridge 0/1" to "AIPS PBridge_0/1".</li> <li>In Figure 2: <ul> <li>Changed figure title (was "Peripherals block diagram").</li> <li>Changed BAF' to "BAR".</li> <li>Added PBRIDGE_1, EIM, XBAR, and PBRIDGE_0.</li> </ul> </li> <li>In section Introduction, removed section "Parameter classification".</li> <li>In section Absolute maximum ratings, Table 1: <ul> <li>VDD_HV_IO_FEC spec: removed row for "Using Ethernet Reference to VSS" condition.</li> <li>Corrected "VIDD_HV_IO_MSC" to "VDD_HV_IO_MSC".</li> <li>Add parameter IIOMAX.</li> <li>Deleted IMAXSEG parameter.</li> </ul> </li> <li>In section Operating conditions : <ul> <li>Deleted sentence "The ranges in this table are design targets",</li> <li>Added a NOTE that all power supplies need to be powered up.</li> <li>In Table 3: <ul> <li>Removed VDD_HV_FLA.</li> <li>Changed minimum voltage of VDD_HV_ADV_SD.</li> <li>Modified footnote for SAR ADC supply voltage.</li> <li>Modified footnote for SAR ADC supply voltage.</li> <li>Modified VRAMP spec to two separate specs for "VRAMP_VDD_LV" and "VRAMP_VDD_HV_IO_MAIN, VRAMP_VDD_HV_PMC".</li> </ul> </li> <li>In section DC electrical specifications : <ul> <li>Removed the statement that the ranges are design targets.</li> <li>In Table 5: <ul> <li>Modified IDD_LV to show specs depending on device model. Modified footnote.</li> <li>Removed the "PMC only" row of the IDD_HV_PMC "internal core reg bypassed" spec.</li> <li>Removed the JDD_LKSTP_AC.</li> <li>Changed IDD_LKSTP_AC.</li> <li>Changed IDD_MSTY_ON value at 40 "C.</li> <li>Changed IDD_MSTY_ON value at 40 "C.</li> <li>Changed IDD_DENTY_N value at 40 "C.</li> <li>Changed IDD_DENTY_N</li></ul></li></ul></li></ul></li></ul></li></ul> | Revision | Date    | Description of changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Editorial changes.</li> <li>Removed the Classification columns in spec tables and removed statements that values neer to be characterized.</li> <li>In footnotes changed cross references to figures to static text.</li> <li>In section Block diagram : <ul> <li>In Figure 1, changed "AIPS Bridge 0/1" to "AIPS PBridge_0/1".</li> <li>In Figure 2: <ul> <li>Changed "BAF"</li> <li>Added PBRIDGE_1, EIM, XBAR, and PBRIDGE_0.</li> </ul> </li> <li>In section Introduction, removed section "Parameter classification".</li> <li>In section Absolute maximum ratings, Table 1: <ul> <li>VDD_HV_IO_FEC spec: removed row for "Using Ethernet Reference to VSS" condition.</li> <li>Corrected 'VIDD HV_IO_MSC' to "VDD_HV_IO_MSC".</li> <li>Add parameter IOMAX.</li> <li>Deleted MAXSEG parameter.</li> </ul> </li> <li>In section Operating conditions : <ul> <li>Beleted Sentence "The ranges in this table are design targets".</li> <li>Added a NOTE that all power supplies need to be powered up.</li> <li>In Table 3: <ul> <li>Removed VDD_HV_FLA.</li> <li>Changed minimum voltage of VDD_HV_ADV_SD.</li> <li>Modified footnote for SDA ADC supply voltage.</li> <li>Modified footnote for SAR ADC supply voltage.</li> <li>Modified footnote for SAR ADC supply voltage.</li> <li>Modified VRAMP spec to two separate specs for "VRAMP_VDD_LV" and "VRAMP_VDD_HV_IO_MIN, VRAMP_VDD_HV_PMC".</li> </ul> </li> <li>In section DC electrical specifications : <ul> <li>Removed the statement that the ranges are design targets.</li> <li>In Table 5: <ul> <li>Modified Iop_LV, to show specs depending on device model. Modified footnote.</li> <li>Removed ID_MAN_CORE_AC.</li> <li>Removed ID_D_MAN_ORE_AC.</li> <li>Changed D_DSTBY_ON VALUE at 40 °C.</li> </ul> </li> </ul></li></ul></li></ul></li></ul>                          | 1        | 05/2013 | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <ul> <li>In Figure 1, changed "AIPS Bridge 0/1" to "AIPS PBridge_0/1".</li> <li>In Figure 2: <ul> <li>Changed figure title (was "Peripherals block diagram").</li> <li>Changed "BAF" to "BAR".</li> <li>Added PBRIDGE_1, EIM, XBAR, and PBRIDGE_0.</li> </ul> </li> <li>In section Introduction, removed section "Parameter classification".</li> <li>In section Absolute maximum ratings, Table 1 : <ul> <li>VDD_HV_IO_FEC spec: removed row for "Using Ethernet Reference to VSS" condition.</li> <li>Corrected "VIDD_HV_IO_MSC" to "VDD_HV_IO_MSC".</li> <li>Added parameter IIOMAX.</li> <li>Deleted IMAXSEG parameter.</li> </ul> </li> <li>In section Operating conditions : <ul> <li>Deleted sentence "The ranges in this table are design targets".</li> <li>Added a NOTE that all power supplies need to be powered up.</li> <li>In Table 3: <ul> <li>Removed VDD_HV_FLA.</li> <li>Changed minimum voltage of VDD_HV_ADV_SD.</li> <li>Modified footnote for S/D ADC supply voltage.</li> <li>Modified IDD_HV_IO_MAIN, VRAMP_VDD_HV_PMC".</li> </ul> </li> <li>In section DC electrical specifications : <ul> <li>Removed the statement that the ranges are design targets.</li> <li>In Table 5: <ul> <li>Modified ID_D_LV' to show specs depending on device model. Modified footnote.</li> <li>Removed IDD_MAIN_CORE_AC.</li> <li>Changed ID_D_LY' to show specs depending on device model. Modified footnote.</li> <li>Removed IDD_MAIN_CORE_AC.</li> <li>Changed ID_D_LY' to show specs depending on device model. Modified footnote.</li> <li>Removed IDD_MAIN_CORE_AC.</li> <li>Changed ID_D_LY''s parameter to "32 KB RAM Standby Regulator Current" (was "Standby Leakage Current"); changed condition to "V<sub>DDSTBY</sub> @1.2 V to 5.9 V, TJ = 150C" (was "V<sub>DDSTBY</sub> @ 1.3 V")</li> </ul> </li> </ul></li></ul></li></ul>                                                                                                                                                  | 2        | 12/2014 | <ul> <li>Editorial changes.</li> <li>Removed the Classification columns in spec tables and removed statements that values need to be characterized.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| In section Absolute maximum ratings, Table 1 :<br>• VDD_HV_IO_FEC spec: removed row for "Using Ethernet Reference to VSS" condition.<br>• Corrected "VIDD_HV_IO_MSC" to "VDD_HV_IO_MSC".<br>• Add parameter IIOMAX.<br>• Deleted IMAXSEG parameter.<br>In section Operating conditions :<br>• Deleted sentence "The ranges in this table are design targets".<br>• Added a NOTE that all power supplies need to be powered up.<br>• In Table 3 :<br>• Removed VDD_HV_FLA.<br>• Changed minimum voltage of VDD_HV_ADV_SD.<br>• Modified footnote for S/D ADC supply voltage.<br>• Modified footnote for S/D ADC supply voltage.<br>• Modified footnote for S/D ADC supply voltage.<br>• Modified VRAMP spec to two separate specs for "VRAMP_VDD_LV" and<br>"VRAMP_VDD_HV_IO_MAIN, VRAMP_VDD_HV_PMC".<br>In section DC electrical specifications :<br>• Removed the statement that the ranges are design targets.<br>• In Table 5 :<br>• Modified I <sub>DD_LV</sub> to show specs depending on device model. Modified footnote.<br>• Removed IDD_MAIN_CORE_AC.<br>• Removed IDD_LKSTP_AC.<br>• Changed I <sub>DD_TW</sub> value at 40 °C.<br>• Changed I <sub>DD_TW</sub> e 1.2 V to 5.9 V, Tj =<br>150C" (was "V <sub>DDSTBY</sub> @ 1.3 V")                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |         | <ul> <li>In Figure 1, changed "AIPS Bridge 0/1" to "AIPS PBridge_0/1".</li> <li>In Figure 2: <ul> <li>Changed figure title (was "Peripherals block diagram").</li> <li>Changed "BAF" to "BAR".</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <ul> <li>VDD_HV_IO_FEC spec: removed row for "Using Ethernet Reference to VSS" condition.</li> <li>Corrected "VIDD_HV_IO_MSC" to "VDD_HV_IO_MSC".</li> <li>Add parameter IIOMAX.</li> <li>Deleted IMAXSEG parameter.</li> <li>In section Operating conditions : <ul> <li>Deleted sentence "The ranges in this table are design targets".</li> <li>Added a NOTE that all power supplies need to be powered up.</li> <li>In Table 3: <ul> <li>Removed VDD_HV_FLA.</li> <li>Changed minimum voltage of VDD_HV_ADV_SD.</li> <li>Modified footnote for S/D ADC supply voltage.</li> <li>Modified footnote for SAR ADC supply voltage.</li> <li>Modified VRAMP spec to two separate specs for "VRAMP_VDD_LV" and "VRAMP_VDD_HV_IO_MAIN, VRAMP_VDD_HV_PMC".</li> </ul> </li> <li>In section DC electrical specifications : <ul> <li>Removed the statement that the ranges are design targets.</li> <li>In Table 5: <ul> <li>Modified IDD_LV to show specs depending on device model. Modified footnote.</li> <li>Removed the "PMC only" row of the IDD_HV_PMC "internal core reg bypassed" spec.</li> <li>Removed IDD_LKSTP_AC.</li> <li>Changed IDD_TMIN_CORE_AC.</li> <li>Changed</li></ul></li></ul></li></ul></li></ul>            |          |         | In section Introduction, removed section "Parameter classification".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <ul> <li>Deleted sentence "The ranges in this table are design targets".</li> <li>Added a NOTE that all power supplies need to be powered up.</li> <li>In Table 3 : <ul> <li>Removed VDD_HV_FLA.</li> <li>Changed minimum voltage of VDD_HV_ADV_SD.</li> <li>Modified footnote for S/D ADC supply voltage.</li> <li>Modified footnote for SAR ADC supply voltage.</li> <li>Modified VRAMP spec to two separate specs for "VRAMP_VDD_LV" and<br/>"VRAMP_VDD_HV_IO_MAIN, VRAMP_VDD_HV_PMC".</li> </ul> </li> <li>In section DC electrical specifications : <ul> <li>Removed the statement that the ranges are design targets.</li> <li>In Table 5 : <ul> <li>Modified I<sub>DD_LV</sub> to show specs depending on device model. Modified footnote.</li> <li>Removed the "PMC only" row of the IDD_HV_PMC "internal core reg bypassed" spec.</li> <li>Removed IDD_MAIN_CORE_AC.</li> <li>Changed I<sub>DD_STBY_ON</sub> value at 40 °C.</li> <li>Changed I<sub>DDSTBY_NEG</sub> parameter to "32 KB RAM Standby Regulator Current" (was<br/>"Standby Leakage Current"); changed condition to "V<sub>DDSTBY</sub> @1.2 V to 5.9 V, Tj =<br/>150C" (was "V<sub>DDSTBY</sub> @1.3 V")</li> </ul> </li> </ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |         | <ul> <li>VDD_HV_IO_FEC spec: removed row for "Using Ethernet Reference to VSS" condition.</li> <li>Corrected "VIDD_HV_IO_MSC" to "VDD_HV_IO_MSC".</li> <li>Add parameter IIOMAX.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <ul> <li>Removed the statement that the ranges are design targets.</li> <li>In Table 5 : <ul> <li>Modified I<sub>DD_LV</sub> to show specs depending on device model. Modified footnote.</li> <li>Removed the "PMC only" row of the IDD_HV_PMC "internal core reg bypassed" spec.</li> <li>Removed IDD_MAIN_CORE_AC.</li> <li>Removed IDD_LKSTP_AC.</li> <li>Changed I<sub>DDSTBY_ON</sub> value at 40 °C.</li> <li>Changed I<sub>DDSTBY_REG</sub> parameter to "32 KB RAM Standby Regulator Current" (was "Standby Leakage Current"); changed condition to "V<sub>DDSTBY</sub> @1.2 V to 5.9 V, Tj = 150C" (was "V<sub>DDSTBY</sub> @ 1.3 V")</li> <li>Removed IDDOFF.</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |         | <ul> <li>Deleted sentence "The ranges in this table are design targets".</li> <li>Added a NOTE that all power supplies need to be powered up.</li> <li>In Table 3 : <ul> <li>Removed VDD_HV_FLA.</li> <li>Changed minimum voltage of VDD_HV_ADV_SD.</li> <li>Modified footnote for S/D ADC supply voltage.</li> <li>Modified footnote for SAR ADC supply voltage.</li> <li>Modified VRAMP spec to two separate specs for "VRAMP_VDD_LV" and</li> </ul> </li> </ul>                                                                                                                                                                                                                                                         |

| Added IDD_BD_STBY.     Added IVDDA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |         | <ul> <li>Removed the statement that the ranges are design targets.</li> <li>In Table 5: <ul> <li>Modified I<sub>DD_LV</sub> to show specs depending on device model. Modified footnote.</li> <li>Removed the "PMC only" row of the IDD_HV_PMC "internal core reg bypassed" spec.</li> <li>Removed IDD_MAIN_CORE_AC.</li> <li>Removed IDD_LKSTP_AC.</li> <li>Changed I<sub>DDSTBY_ON</sub> value at 40 °C.</li> <li>Changed I<sub>DDSTBY_REG</sub> parameter to "32 KB RAM Standby Regulator Current" (was "Standby Leakage Current"); changed condition to "V<sub>DDSTBY</sub> @ 1.2 V to 5.9 V, Tj = 150C" (was "V<sub>DDSTBY</sub> @ 1.3 V")</li> <li>Removed IDD_FF.</li> <li>Added IDD_BD_STBY.</li> </ul> </li> </ul> |

| Table 61. | Revision | history | (continued) |

|-----------|----------|---------|-------------|

|-----------|----------|---------|-------------|

| Revision | Date    | Description of changes                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |         | In section Ordering information table "Ordering Information", changed Part Numbers for the 176 LQFP PD and the ED.                                                                                                                                                                                                                                                                             |

| 5        | 10/2016 | Editorial updates.                                                                                                                                                                                                                                                                                                                                                                             |

|          |         | In section Operating conditions table "Device operating conditions" added foootnote to $V_{\text{DD}_{HV}_{IO}_{JTAG}}.$                                                                                                                                                                                                                                                                       |

|          |         | In section Input pad specifications table "I/O input DC electrical characteristics" for $I_{LKG}$ added condition " $V_{SS} < V_{IN} < V_{DD_HV_IO^*}$ "                                                                                                                                                                                                                                       |

|          |         | In section ADC input description table "Analog Input Leakage and Pull-Up/Down DC electrical characteristics" for ILK_AD added conditions $V_{SS_HV_ADV_SAR} < V_{IN} < V_{DD_HV_ADV_SAR}$ " and $V_{SS_HV_ADV_SD} < V_{IN} < V_{DD_HV_ADV_SD}$ ".                                                                                                                                              |

|          |         | In section Recommended power transistors table "Recommended operating characteristics" for I <sub>CMaxDC</sub> changed the parameter from "Minimum peak collector current" to "Maximum DC collector current".                                                                                                                                                                                  |

|          |         | <ul> <li>In section SAR ADC table "ADC conversion characteristics":</li> <li>Removed the condition for t<sub>sample</sub>.</li> <li>Removed the Min and added the formula (6.02*ENOB) + 1.76 for SINAD.</li> <li>Changed the Min value from 650 to 700 for t<sub>conv</sub>.</li> </ul>                                                                                                        |

|          |         | In section S/D ADC table "SDn ADC electrical specification":<br>• Removed Z <sub>IN</sub> specification<br>• Added Z <sub>DIFF</sub> , Z <sub>CM</sub> , and ΔV <sub>INTCM</sub> specifications<br>• For R <sub>BIAS</sub> :<br>• Changed Parameter description from "Bias resistance" to "Bare bias resistance"<br>• Changed Min from 100 kΩ to 110 kΩ<br>• Changed Typ from 125 kΩ to 144 kΩ |

|          |         | • Changed Max from 160 k $\Omega$ to 180 k $\Omega$                                                                                                                                                                                                                                                                                                                                            |

|          |         | In section Flash memory AC timing specifications table "Flash memory AC timing specifications" for t <sub>psus</sub> :                                                                                                                                                                                                                                                                         |