Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |  |

|----------------------------|------------------------------------------------------------------------|--|

|                            | Active                                                                 |  |

| Product Status             |                                                                        |  |

| Core Processor             | STM8                                                                   |  |

| Core Size                  | 8-Bit                                                                  |  |

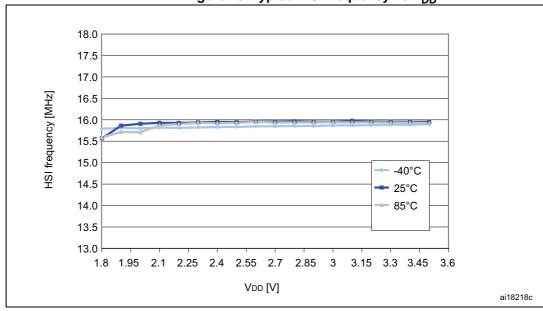

| Speed                      | 16MHz                                                                  |  |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                |  |

| Peripherals                | Brown-out Detect/Reset, DMA, IR, POR, PWM, WDT                         |  |

| Number of I/O              | 18                                                                     |  |

| Program Memory Size        | 8KB (8K x 8)                                                           |  |

| Program Memory Type        | FLASH                                                                  |  |

| EEPROM Size                | 256 x 8                                                                |  |

| RAM Size                   | 1K x 8                                                                 |  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |  |

| Data Converters            | A/D 10x12b                                                             |  |

| Oscillator Type            | Internal                                                               |  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |  |

| Mounting Type              | Surface Mount                                                          |  |

| Package / Case             | 20-UFQFN                                                               |  |

| Supplier Device Package    | 20-UFQFPN (3x3)                                                        |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8l151f3u6tr |  |

| ADC1 characteristics                                                      | 95              |

|---------------------------------------------------------------------------|-----------------|

|                                                                           |                 |

|                                                                           |                 |

|                                                                           |                 |

|                                                                           |                 |

|                                                                           |                 |

|                                                                           |                 |

| ESD absolute maximum ratings                                              | 102             |

|                                                                           |                 |

| LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                   |                 |

| mechanical data                                                           | 104             |

| UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat   |                 |

| package mechanical data                                                   | 107             |

| UFQFPN28 - 28-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |                 |

| package mechanical data                                                   | 109             |

| UFQFPN20 - 20-lead, 3x3 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |                 |

| package mechanical data                                                   | 113             |

| TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, |                 |

| package mechanical data                                                   | 115             |

| Thermal characteristics                                                   | 118             |

| Low-density STM8L151x2/3 ordering information scheme                      | 119             |

| Document revision history                                                 | 120             |

|                                                                           | mechanical data |

### 3.4 Clock management

The clock controller distributes the system clock (SYSCLK) coming from different oscillators to the core and the peripherals. It also manages clock gating for low power modes and ensures clock robustness.

#### **Features**

- Clock prescaler: to get the best compromise between speed and current consumption the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler

- **Safe clock switching:** Clock sources can be changed safely on the fly in run mode through a configuration register.

- **Clock management:** To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- System clock sources: 4 different clock sources can be used to drive the system clock:

- 1-16 MHz High speed external crystal (HSE)

- 16 MHz High speed internal RC oscillator (HSI)

- 32.768 kHz Low speed external crystal (LSE)

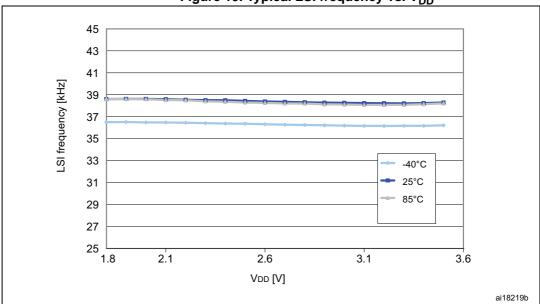

- 38 kHz Low speed internal RC (LSI)

- RTC clock sources: the above four sources can be chosen to clock the RTC whatever the system clock.

- Startup clock: After reset, the microcontroller restarts by default with an internal 2 MHz clock (HSI/8). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): This feature can be enabled by software. If a HSE clock failure occurs, the system clock is automatically switched to HSI.

- Configurable main clock output (CCO): This outputs an external clock for use by the application.

5//

# 4 Pinout and pin description

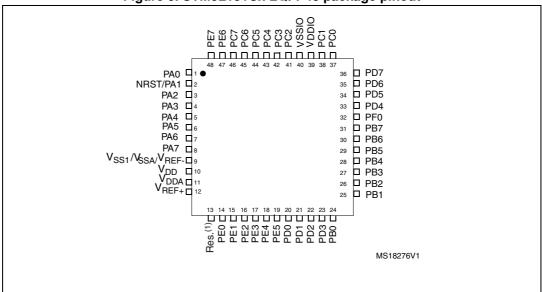

Figure 3. STM8L151Cx LQFP48 package pinout

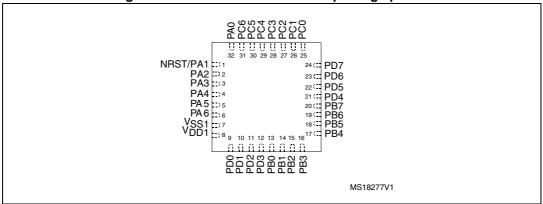

Figure 4. STM8L151Kx UFQFPN32 package pinout

Table 4. Low-density STM8L151x2/3 pin description (continued)

|        | Pin      | num      | ber      |         |                                                                                                        |      |           |          | Inpu | t              | 0                | utpu | ıt |                                |                                                                                                                                   |

|--------|----------|----------|----------|---------|--------------------------------------------------------------------------------------------------------|------|-----------|----------|------|----------------|------------------|------|----|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| LQFP48 | UFQFPN32 | UFQFPN28 | UFQFPN20 | TSSOP20 | Pin name                                                                                               | Туре | I/O level | floating | mbm  | Ext. interrupt | High sink/source | ОО   | PP | Main function<br>(after reset) | Default alternate<br>function                                                                                                     |

| 43     | 29       | 25       | 17       |         | PC4/USART_CK]/<br>I2C_SMB/CCO/<br>ADC1_IN4/<br>COMP1_INP/<br>COMP2_INM                                 | I/O  | •         | х        | Х    | Х              | HS               | Х    | X  | Port C4                        | USART synchronous clock / I2C1_SMB / Configurable clock output / ADC1_IN4/ Comparator1 positive input/Comparator 2 negative input |

| 44     | 30       | 26       | 18       | 1       | PC5/OSC32_IN<br>/[SPI1_NSS] <sup>(2)</sup> /<br>[USART_TX] <sup>(2)</sup> /<br>TIM2_CH1 <sup>(6)</sup> | I/O  | 1         | X        | X    | Х              | HS               | X    | Х  | Port C5                        | LSE oscillator input /<br>[SPI master/slave<br>select] / [USART<br>transmit]/<br>Timer 2 -channel 1 <sup>(6)</sup>                |

| 45     | 31       | 27       | 19       | 2       | PC6/OSC32_OUT/<br>[SPI_SCK] <sup>(2)</sup> /<br>[USART_RX] <sup>(2)</sup> /<br>TIM2_CH2 <sup>(6)</sup> | I/O  | 1         | х        | Х    | Х              | HS               | Х    | Х  | Port C6                        | LSE oscillator output /<br>[SPI clock] / [USART<br>receive]/<br>Timer 2 -channel 2 <sup>(6)</sup>                                 |

| 46     | -        | -        | -        | -       | PC7/ADC1_IN3/<br>COMP1_INP/<br>COMP2_INM                                                               | I/O  | 1         | x        | Х    | Х              | HS               | Х    | Х  | Port C7                        | ADC1_IN3/<br>Comparator1 positive<br>input/Comparator 2<br>negative input                                                         |

| 20     | 9        | 8        | 6        | 9       | PD0/TIM3_CH2/<br>[ADC1_TRIG] <sup>(2)</sup> /<br>ADC1_IN22/<br>COMP1_INP/<br>COMP2_INP                 | I/O  | 1         | X        | X    | Х              | HS               | X    | X  | Port D0                        | Timer 3 - channel 2 / [ADC1_Trigger] / ADC1_IN22/ Comparator1 positive input/Comparator 2 positive input                          |

| 21     | 10       | 9        | -        |         | PD1/TIM3_ETR/<br>ADC1_IN21/<br>COMP1_INP/<br>COMP2_INP                                                 | I/O  | 1         | x        | Х    | Х              | HS               | Х    | X  | Port D1                        | Timer 3 - external<br>trigger / ADC1_IN21/<br>Comparator1 positive<br>input/Comparator 2<br>positive input                        |

| 22     | 11       | 10       | -        | -       | PD2/ADC1_IN20/<br>COMP1_INP                                                                            | I/O  | 1         | х        | х    | Х              | HS               | х    | Х  | Port D2                        | ADC1_IN20/<br>Comparator1 positive<br>input                                                                                       |

| 23     | 12       | 11       | -        | -       | PD3/ADC1_IN19/<br>RTC_CALIB <sup>(7)</sup> /<br>COMP1_INP                                              | I/O  | 1         | X        | Х    | Х              | HS               | Х    | Х  | Port D3                        | ADC1_IN19/<br>RTC calibration <sup>(7)</sup> /<br>Comparator1 positive<br>input                                                   |

| 33     | 21       | 20       | -        | -       | PD4/ADC1_IN10/<br>COMP1_INP                                                                            | I/O  | -         | X        | X    | х              | HS               | X    | Х  | Port D4                        | ADC1_IN10/<br>Comparator1 positive<br>input                                                                                       |

Table 8. General hardware register map (continued)

| Address                      | Block | Register label          | Register name                                        | Reset status |

|------------------------------|-------|-------------------------|------------------------------------------------------|--------------|

| 0x00 5084                    |       |                         | Reserved area (1 byte)                               | ·            |

| 0x00 5085                    |       | DMA1_C1M0ARH            | DMA1 memory 0 address high register (channel 1)      | 0x00         |

| 0x00 5086                    |       | DMA1_C1M0ARL            | DMA1 memory 0 address low register (channel 1)       | 0x00         |

| 0x00 5087<br>0x00 5088       |       |                         | Reserved area (2 byte)                               |              |

| 0x00 5089                    |       | DMA1_C2CR               | DMA1 channel 2 configuration register                | 0x00         |

| 0x00 508A                    | 1     | DMA1_C2SPR              | DMA1 channel 2 status & priority register            | 0x00         |

| 0x00 508B                    |       | DMA1_C2NDTR             | DMA1 number of data to transfer register (channel 2) | 0x00         |

| 0x00 508C                    |       | DMA1_C2PARH             | DMA1 peripheral address high register (channel 2)    | 0x52         |

| 0x00 508D                    |       | DMA1_C2PARL             | DMA1 peripheral address low register (channel 2)     | 0x00         |

| 0x00 508E                    |       |                         | Reserved area (1 byte)                               |              |

| 0x00 508F                    |       | DMA1_C2M0ARH            | DMA1 memory 0 address high register (channel 2)      | 0x00         |

| 0x00 5090                    | DMA1  | DMA1_C2M0ARL            | DMA1 memory 0 address low register (channel 2)       | 0x00         |

| 0x00 5091<br>0x00 5092       |       |                         | Reserved area (2 byte)                               |              |

| 0x00 5093                    |       | DMA1_C3CR               | DMA1 channel 3 configuration register                | 0x00         |

| 0x00 5094                    | 1     | DMA1_C3SPR              | DMA1 channel 3 status & priority register            | 0x00         |

| 0x00 5095                    |       | DMA1_C3NDTR             | DMA1 number of data to transfer register (channel 3) | 0x00         |

| 0x00 5096                    |       | DMA1_C3PARH_<br>C3M1ARH | DMA1 peripheral address high register (channel 3)    | 0x40         |

| 0x00 5097                    |       | DMA1_C3PARL_<br>C3M1ARL | DMA1 peripheral address low register (channel 3)     | 0x00         |

| 0x00 5098                    |       | DMA_C3M0EAR             | DMA channel 3 memory 0 extended address register     | 0x00         |

| 0x00 5099                    |       | DMA1_C3M0ARH            | DMA1 memory 0 address high register (channel 3)      | 0x00         |

| 0x00 509A                    |       | DMA1_C3M0ARL            | DMA1 memory 0 address low register (channel 3)       | 0x00         |

| 0x00 509B<br>to<br>0x00 509C |       |                         | Reserved area (3 byte)                               |              |

Table 9. CPU/SWIM/debug module/interrupt controller registers

| Address                      | Block              | Register Label          | Register Name                          | Reset<br>Status |  |  |  |

|------------------------------|--------------------|-------------------------|----------------------------------------|-----------------|--|--|--|

| 0x00 7F00                    |                    | А                       | Accumulator                            | 0x00            |  |  |  |

| 0x00 7F01                    |                    | PCE                     | Program counter extended               | 0x00            |  |  |  |

| 0x00 7F02                    |                    | PCH                     | Program counter high                   | 0x00            |  |  |  |

| 0x00 7F03                    |                    | PCL                     | Program counter low                    | 0x00            |  |  |  |

| 0x00 7F04                    |                    | XH                      | X index register high                  | 0x00            |  |  |  |

| 0x00 7F05                    | CPU <sup>(1)</sup> | XL                      | X index register low                   | 0x00            |  |  |  |

| 0x00 7F06                    |                    | YH                      | Y index register high                  | 0x00            |  |  |  |

| 0x00 7F07                    |                    | YL                      | Y index register low                   | 0x00            |  |  |  |

| 0x00 7F08                    |                    | SPH                     | Stack pointer high                     | 0x03            |  |  |  |

| 0x00 7F09                    |                    | SPL                     | Stack pointer low                      | 0xFF            |  |  |  |

| 0x00 7F0A                    |                    | CCR                     | Condition code register                | 0x28            |  |  |  |

| 0x00 7F0B to<br>0x00 7F5F    | CPU                |                         | Reserved area (85 byte)                |                 |  |  |  |

| 0x00 7F60                    |                    | CFG_GCR                 | Global configuration register          | 0x00            |  |  |  |

| 0x00 7F70                    |                    | ITC_SPR1                | Interrupt Software priority register 1 | 0xFF            |  |  |  |

| 0x00 7F71                    |                    | ITC_SPR2                | Interrupt Software priority register 2 | 0xFF            |  |  |  |

| 0x00 7F72                    |                    | ITC_SPR3                | Interrupt Software priority register 3 | 0xFF            |  |  |  |

| 0x00 7F73                    | ITC-SPR            | ITC_SPR4                | Interrupt Software priority register 4 | 0xFF            |  |  |  |

| 0x00 7F74                    | 110-5PK            | ITC_SPR5                | Interrupt Software priority register 5 | 0xFF            |  |  |  |

| 0x00 7F75                    |                    | ITC_SPR6                | Interrupt Software priority register 6 | 0xFF            |  |  |  |

| 0x00 7F76                    |                    | ITC_SPR7                | Interrupt Software priority register 7 | 0xFF            |  |  |  |

| 0x00 7F77                    |                    | ITC_SPR8                | Interrupt Software priority register 8 | 0xFF            |  |  |  |

| 0x00 7F78<br>to<br>0x00 7F79 |                    |                         | Reserved area (2 byte)                 |                 |  |  |  |

| 0x00 7F80                    | SWIM               | SWIM_CSR                | SWIM control status register           | 0x00            |  |  |  |

| 0x00 7F81<br>to<br>0x00 7F8F |                    | Reserved area (15 byte) |                                        |                 |  |  |  |

Table 12. Option byte description

|                       | Table 12. Option byte description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Option<br>byte<br>No. | Option description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| OPT0                  | ROP[7:0] Memory readout protection (ROP)  0xAA: Disable readout protection (write access via SWIM protocol)  Refer to Readout protection section in the STM8L15x and STM8L16x reference manual (RM0031).                                                                                                                                                                                                                                                                                                                        |

| OPT1                  | UBC[7:0] Size of the user boot code area  0x00: UBC is not protected.  0x01: Page 0 is write protected.  0x02: Page 0 and 1 reserved for the UBC and write protected. It covers only the interrupt vectors.  0x03: Page 0 to 2 reserved for UBC and write protected.  0x7F to 0xFF - All 128 pages reserved for UBC and write protected.  The protection of the memory area not protected by the UBC is enabled through the MASS keys.  Refer to User boot code section in the STM8L15x and STM8L16x reference manual (RM0031). |

| OPT2                  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                       | IWDG_HW: Independent watchdog  0: Independent watchdog activated by software  1: Independent watchdog activated by hardware  IWDG_HALT: Independent window watchdog off on Halt/Active-halt  0: Independent watchdog continues running in Halt/Active-halt mode                                                                                                                                                                                                                                                                 |

| OPT3                  | 1: Independent watchdog stopped in Halt/Active-halt mode  WWDG_HW: Window watchdog  0: Window watchdog activated by software  1: Window watchdog activated by hardware                                                                                                                                                                                                                                                                                                                                                          |

|                       | WWDG_HALT: Window window watchdog reset on Halt/Active-halt  0: Window watchdog stopped in Halt mode  1: Window watchdog generates a reset when MCU enters Halt mode                                                                                                                                                                                                                                                                                                                                                            |

|                       | HSECNT: Number of HSE oscillator stabilization clock cycles  0x00 - 1 clock cycle  0x01 - 16 clock cycles  0x10 - 512 clock cycles  0x11 - 4096 clock cycles                                                                                                                                                                                                                                                                                                                                                                    |

| OPT4                  | USECNT: Number of LSE oscillator stabilization clock cycles  0x00 - 1 clock cycle  0x01 - 16 clock cycles  0x10 - 512 clock cycles  0x11 - 4096 clock cycles  Refer to Table 31: LSE oscillator characteristics on page 74.                                                                                                                                                                                                                                                                                                     |

Table 12. Option byte description (continued)

| Option<br>byte<br>No. | Option description                                                                                                                |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|                       | BOR_ON: 0: Brownout reset off                                                                                                     |

| OPT5                  | 1: Brownout reset on  BOR_TH[3:1]: Brownout reset thresholds. Refer to <i>Table 22</i> for details on the thresholds according to |

|                       | the value of BOR_TH bits.                                                                                                         |

|                       | OPTBL[15:0]:  This option is checked by the boot ROM code after reset. Depending on                                               |

| OPTBL                 | content of addresses 00 480B, 00 480C and 0x8000 (reset vector) the                                                               |

|                       | CPU jumps to the bootloader or to the reset vector.                                                                               |

|                       | Refer to the UM0560 bootloader user manual for more details.                                                                      |

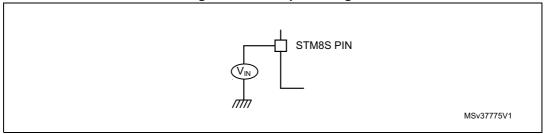

### 9.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 10*.

Figure 10. Pin input voltage

### 9.2 Absolute maximum ratings

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

**Table 14. Voltage characteristics**

| Symbol                            | Ratings                                                                                   | Min                                                                     | Max | Unit |

|-----------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----|------|

| V <sub>DD</sub> - V <sub>SS</sub> | External supply voltage (including $V_{DD}$ , $V_{DDA}$ , and $V_{DDIO}$ ) <sup>(1)</sup> | - 0.3                                                                   | 4.0 | V    |

| V <sub>IN</sub> <sup>(2)</sup>    | Input voltage on true open-drain pins (PC0 and PC1)                                       | V <sub>SS</sub> - 0.3 V <sub>DD</sub> + 4.0                             |     | V    |

|                                   | Input voltage on any other pin                                                            | V <sub>ss</sub> - 0.3                                                   | 4.0 |      |

| V <sub>ESD</sub>                  | Electrostatic discharge voltage                                                           | see Absolute maximum<br>ratings (electrical sensitivity)<br>on page 102 |     |      |

All power (V<sub>DD</sub>, V<sub>DDA</sub>, V<sub>DDIO</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>, V<sub>SSIO</sub>) pins must always be connected to the external power supply.

577

<sup>2.</sup> V<sub>IN</sub> maximum must always be respected. Refer to *Table 15*. for maximum allowed injected current values.

In the following table, data is based on characterization results, unless otherwise specified.

Table 20. Total current consumption in Wait mode

|                       |                             | Conditions <sup>(1)</sup> |                                                              |                                                |                          | Max                      |               |               |              |                          |       |       |       |       |       |  |

|-----------------------|-----------------------------|---------------------------|--------------------------------------------------------------|------------------------------------------------|--------------------------|--------------------------|---------------|---------------|--------------|--------------------------|-------|-------|-------|-------|-------|--|

| Symbol                | Parameter                   |                           |                                                              | Тур                                            | 55°C                     | 85 °C                    | 105 °C<br>(2) | 125 °C<br>(2) | Unit         |                          |       |       |       |       |       |  |

|                       |                             |                           |                                                              | f <sub>CPU</sub> = 125 kHz                     | 0.33                     | 0.39                     | 0.41          | 0.43          | 0.45         |                          |       |       |       |       |       |  |

|                       |                             |                           |                                                              | f <sub>CPU</sub> = 1 MHz                       | 0.35                     | 0.41                     | 0.44          | 0.45          | 0.48         |                          |       |       |       |       |       |  |

|                       |                             |                           | HSI                                                          | f <sub>CPU</sub> = 4 MHz                       | 0.42                     | 0.51                     | 0.52          | 0.54          | 0.58         |                          |       |       |       |       |       |  |

|                       |                             |                           |                                                              | f <sub>CPU</sub> = 8 MHz                       | 0.52                     | 0.57                     | 0.58          | 0.59          | 0.62         |                          |       |       |       |       |       |  |

|                       |                             | 11 0111 1 17 1111         |                                                              | f <sub>CPU</sub> = 16 MHz                      | 0.68                     | 0.76                     | 0.79          | 0.82<br>(5)   | 0.85<br>(5)  |                          |       |       |       |       |       |  |

|                       | Supply current in Wait mode |                           | HSE external clock (f <sub>CPU</sub> =f <sub>HSE</sub> ) (4) | f <sub>CPU</sub> = 125 kHz                     | 0.032                    | 0.056                    | 0.068         | 0.072         | 72 0.093     |                          |       |       |       |       |       |  |

|                       |                             |                           |                                                              | clock<br>(f <sub>CPU</sub> =f <sub>HSE</sub> ) | HSE external             | HSE external             | HSE external  | HSE external  | HSE external | f <sub>CPU</sub> = 1 MHz | 0.078 | 0.121 | 0.144 | 0.163 | 0.197 |  |

| I <sub>DD(Wait)</sub> |                             |                           |                                                              |                                                | f <sub>CPU</sub> = 4 MHz | 0.218                    | 0.26          | 0.30          | 0.36         | 0.40                     | mA    |       |       |       |       |  |

|                       |                             |                           |                                                              |                                                |                          | f <sub>CPU</sub> = 8 MHz | 0.40          | 0.52          | 0.57         | 0.62                     | 0.66  |       |       |       |       |  |

|                       |                             |                           |                                                              | f <sub>CPU</sub> = 16 MHz                      | 0.760                    | 1.01                     | 1.05          | 1.09<br>(5)   | 1.16<br>(5)  |                          |       |       |       |       |       |  |

|                       |                             |                           | LSI                                                          | $f_{CPU} = f_{LSI}$                            | 0.035                    | 0.044                    | 0.046         | 0.049         | 0.054        |                          |       |       |       |       |       |  |

|                       |                             |                           | LSE <sup>(6)</sup> external clock (32.768 kHz)               | f <sub>CPU</sub> = f <sub>LSE</sub>            | 0.032                    | 0.036                    | 0.038         | 0.044         | 0.051        |                          |       |       |       |       |       |  |

Figure 18. Typical HSI frequency vs V<sub>DD</sub>

#### Low speed internal RC oscillator (LSI)

In the following table, data is based on characterization results, not tested in production.

Parameter (1) **Symbol** Conditions<sup>(1)</sup> Min Тур Max Unit Frequency  $f_{LSI}$ 26 38 56 kHz  $200^{(2)}$ LSI oscillator wakeup time μs t<sub>su(LSI)</sub> LSI oscillator frequency  $0 \, ^{\circ}C \leq T_{A} \leq 85 \, ^{\circ}C$  $I_{\text{DD(LSI)}}$ -12 11 % drift<sup>(3)</sup>

Table 33. LSI oscillator characteristics

<sup>1.</sup>  $V_{DD}$  = 1.65 V to 3.6 V,  $T_A$  = -40 to 125 °C unless otherwise specified.

<sup>2.</sup> Guaranteed by design, not tested in production.

<sup>3.</sup> This is a deviation for an individual part, once the initial frequency has been measured.

Figure 19. Typical LSI frequency vs.  $V_{\rm DD}$

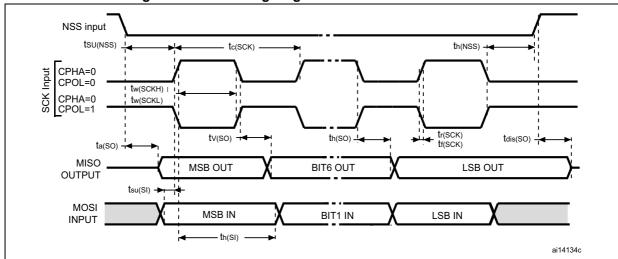

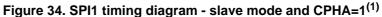

Figure 33. SPI1 timing diagram - slave mode and CPHA=0

1. Measurement points are done at CMOS levels:  $0.3V_{\rm DD}$  and  $0.7V_{\rm DD}$ .

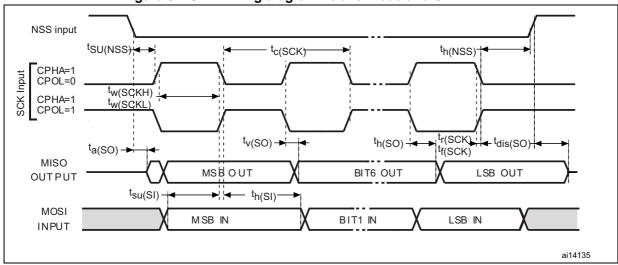

Figure 35. SPI1 timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{\rm DD}$  and  $0.7V_{\rm DD}$ .

### 9.3.10 Temperature sensor

In the following table, data is based on characterization results, not tested in production, unless otherwise specified.

| Symbol                               | Parameter                                              | Min   | Тур   | Max.  | Unit  |

|--------------------------------------|--------------------------------------------------------|-------|-------|-------|-------|

| V <sub>125</sub> <sup>(1)</sup>      | Sensor reference voltage at 90°C ±5 °C,                | 0.640 | 0.660 | 0.680 | V     |

| T <sub>L</sub>                       | V <sub>SENSOR</sub> linearity with temperature         | -     | ±1    | ±2    | °C    |

| Avg_slope (2)                        | Average slope                                          | 1.59  | 1.62  | 1.65  | mV/°C |

| I <sub>DD(TEMP)</sub> <sup>(2)</sup> | Consumption                                            | -     | 3.4   | 6     | μA    |

| T <sub>START</sub> (2)(3)            | Temperature sensor startup time                        | -     | -     | 10    | μs    |

| T <sub>S_TEMP</sub> <sup>(2)</sup>   | ADC1 sampling time when reading the temperature sensor | 10    | -     | -     | μs    |

Table 45. TS characteristics

### 9.3.11 Comparator characteristics

In the following table, data is guaranteed by design, not tested in production, unless otherwise specified.

| Symbol              | Parameter                                 | Min   | Тур   | Max <sup>(1)</sup> | Unit |  |

|---------------------|-------------------------------------------|-------|-------|--------------------|------|--|

| $V_{DDA}$           | Analog supply voltage                     | 1.65  | -     | 3.6                | V    |  |

| T <sub>A</sub>      | Temperature range                         | -40   | -     | 125                | °C   |  |

| R <sub>400K</sub>   | R <sub>400K</sub> value                   | 300   | 400   | 500                | kΩ   |  |

| R <sub>10K</sub>    | R <sub>10K</sub> value                    | 7.5   | 10    | 12.5               | K75  |  |

| V <sub>IN</sub>     | Comparator 1 input voltage range          | 0.6   | -     | $V_{DDA}$          | V    |  |

| V <sub>REFINT</sub> | Internal reference voltage <sup>(2)</sup> | 1.202 | 1.224 | 1.242              | V    |  |

| t <sub>START</sub>  | Comparator startup time                   | -     | 7     | 10                 | 116  |  |

| t <sub>d</sub>      | Propagation delay <sup>(3)</sup>          | -     | 3     | 10                 | μs   |  |

| V <sub>offset</sub> | Comparator offset error                   | -     | ±3    | ±10                | mV   |  |

| I <sub>COMP1</sub>  | Current consumption <sup>(4)</sup>        | -     | 160   | 260                | nA   |  |

Table 46. Comparator 1 characteristics

57

<sup>1.</sup> Tested in production at  $V_{DD}$  = 3 V ±10 mV. The 8 LSB of the  $V_{90}$  ADC1 conversion result are stored in the TS\_Factory\_CONV\_V90 byte.

<sup>2.</sup> Data guaranteed by design, not tested in production.

<sup>3.</sup> Defined for ADC1 output reaching its final value ±1/2LSB.

<sup>1.</sup> Based on characterization, not tested in production.

<sup>2.</sup> Tested in production at  $V_{DD}$  = 3 V ±10 mV.

The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

<sup>4.</sup> Comparator consumption only. Internal reference voltage not included.

## 10 Package information

### 10.1 ECOPACK

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: <a href="www.st.com">www.st.com</a>. ECOPACK® is an ST trademark.

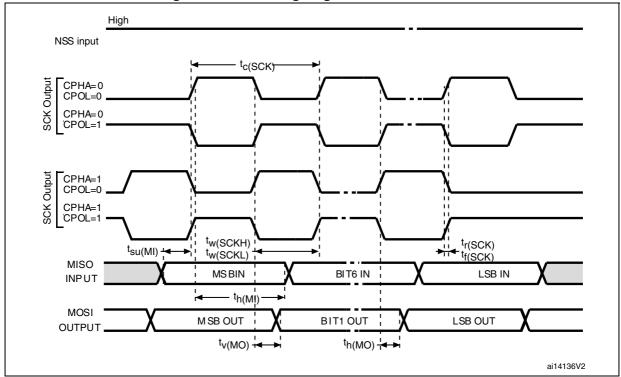

### 10.2 LQFP48 package information

Figure 42. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

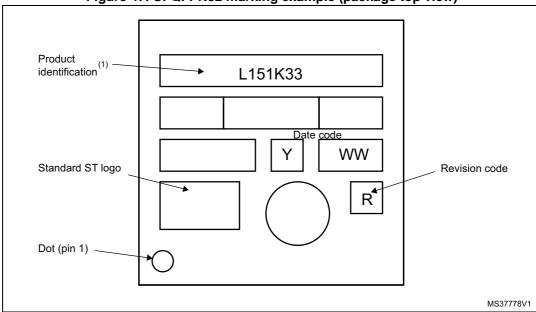

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 47. UFQFPN32 marking example (package top view)

<sup>1.</sup> Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

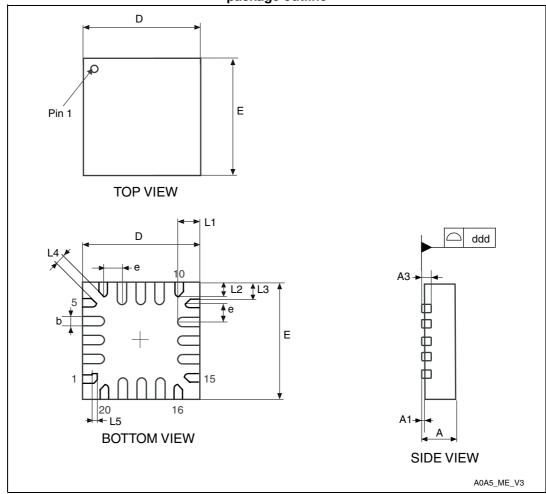

## 10.5 UFQFPN20 package information

Figure 51. UFQFPN20 - 20-lead, 3x3 mm, 0.5 mm pitch, ultra thin fine pitch quad flat package outline

1. Drawing is not to scale.

57

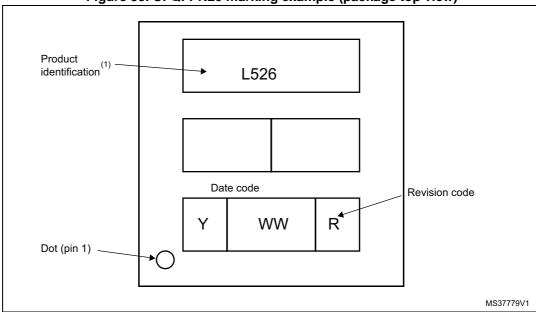

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 53. UFQFPN20 marking example (package top view)

<sup>1.</sup> Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

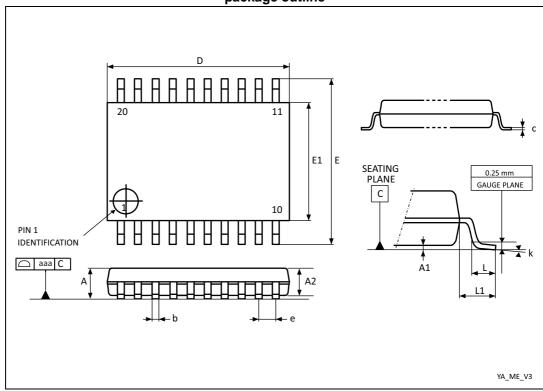

## 10.6 TSSOP20 package information

Figure 54.TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, package outline

1. Drawing is not to scale.

Table 61. TSSOP20 – 20-lead thin shrink small outline, 6.5 x 4.4 mm, 0.65 mm pitch, package mechanical data

| pacitage meananta and |       |             |       |        |                       |        |  |  |  |

|-----------------------|-------|-------------|-------|--------|-----------------------|--------|--|--|--|

| Sumbal                |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |  |  |

| Symbol                | Min.  | Тур.        | Max.  | Min.   | Тур.                  | Max.   |  |  |  |

| А                     | -     | -           | 1.200 | -      | -                     | 0.0472 |  |  |  |

| A1                    | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |  |  |  |

| A2                    | 0.800 | 1.000       | 1.050 | 0.0315 | 0.0394                | 0.0413 |  |  |  |

| b                     | 0.190 | -           | 0.300 | 0.0075 | -                     | 0.0118 |  |  |  |

| С                     | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |  |  |  |

| D                     | 6.400 | 6.500       | 6.600 | 0.2520 | 0.2559                | 0.2598 |  |  |  |

| E                     | 6.200 | 6.400       | 6.600 | 0.2441 | 0.2520                | 0.2598 |  |  |  |

| E1                    | 4.300 | 4.400       | 4.500 | 0.1693 | 0.1732                | 0.1772 |  |  |  |

| е                     | -     | 0.650       | -     | -      | 0.0256                | -      |  |  |  |

| L                     | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |  |  |  |

| L1                    | -     | 1.000       | -     | -      | 0.0394                | -      |  |  |  |