Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | STM8                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 16MHz                                                                |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, IR, POR, PWM, WDT                       |

| Number of I/O              | 26                                                                   |

| Program Memory Size        | 4KB (4K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | 256 x 8                                                              |

| RAM Size                   | 1K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                          |

| Data Converters            | A/D 18x12b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

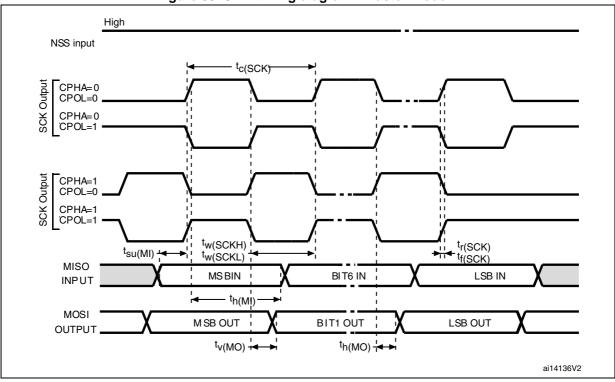

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 28-UFQFN                                                             |

| Supplier Device Package    | 28-UFQFPN (4x4)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8l151g2u6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Contents

| 1 | Intro | duction                                               |

|---|-------|-------------------------------------------------------|

| 2 | Desc  | ription                                               |

|   | 2.1   | Device overview                                       |

|   | 2.2   | Ultra-low-power continuum                             |

| 3 | Func  | tional overview                                       |

|   | 3.1   | Low-power modes                                       |

|   | 3.2   | Central processing unit STM8 15                       |

|   |       | 3.2.1 Advanced STM8 Core                              |

|   |       | 3.2.2 Interrupt controller                            |

|   | 3.3   | Reset and supply management 17                        |

|   |       | 3.3.1 Power supply scheme                             |

|   |       | 3.3.2 Power supply supervisor                         |

|   |       | 3.3.3 Voltage regulator                               |

|   | 3.4   | Clock management                                      |

|   | 3.5   | Low power real-time clock 19                          |

|   | 3.6   | Memories                                              |

|   | 3.7   | DMA 20                                                |

|   | 3.8   | Analog-to-digital converter 20                        |

|   | 3.9   | Ultra-low-power comparators 20                        |

|   | 3.10  | System configuration controller and routing interface |

|   | 3.11  | Touch sensing                                         |

|   | 3.12  | Timers                                                |

|   |       | 3.12.1 16-bit general purpose timers                  |

|   |       | 3.12.2 8-bit basic timer                              |

|   | 3.13  | Watchdog timers                                       |

|   |       | 3.13.1 Window watchdog timer                          |

|   |       | 3.13.2 Independent watchdog timer                     |

|   | 3.14  | Beeper                                                |

|   | 3.15  | Communication interfaces 23                           |

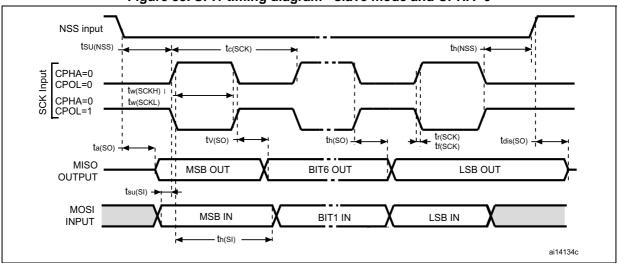

|   |       | 3.15.1 SPI                                            |

## 2.1 Device overview

| Feat                                                | ures               | STM8L151F3          | STM8L151G3        | STM8L151K3/<br>STM8L151C3               | STM8L151F2                     | STM8L151G2        | STM8L151K2/<br>STM8L151C2               |  |  |  |  |  |

|-----------------------------------------------------|--------------------|---------------------|-------------------|-----------------------------------------|--------------------------------|-------------------|-----------------------------------------|--|--|--|--|--|

| Flash (Kby                                          | /te)               |                     | 8                 | <u>.</u>                                |                                | 4                 | <u>.</u>                                |  |  |  |  |  |

| Data EEP<br>(byte)                                  | ROM                |                     |                   | 25                                      | 56                             |                   |                                         |  |  |  |  |  |

| RAM (Kby                                            | te)                |                     |                   |                                         | 1                              |                   |                                         |  |  |  |  |  |

| Timers                                              | Basic              |                     |                   |                                         | 1<br>bit)                      |                   |                                         |  |  |  |  |  |

| Timers                                              | General<br>purpose |                     | 2<br>(16-bit)     |                                         |                                |                   |                                         |  |  |  |  |  |

| Commun                                              | SPI                |                     | 1                 |                                         |                                |                   |                                         |  |  |  |  |  |

| -ication                                            | I2C                |                     |                   |                                         |                                |                   |                                         |  |  |  |  |  |

| interfaces                                          | USART              |                     |                   | ŕ                                       | 1                              |                   |                                         |  |  |  |  |  |

| GPIOs                                               |                    | 18 <sup>(1)</sup>   | 26 <sup>(1)</sup> | 30 <sup>(2)</sup> /41 <sup>(1)(2)</sup> | 18 <sup>(1)</sup>              | 26 <sup>(1)</sup> | 30 <sup>(2)</sup> /41 <sup>(1)(2)</sup> |  |  |  |  |  |

| 12-bit synd<br>ADC (num<br>channels)                |                    | 1<br>(10)           | 1<br>(18)         | 1<br>(23/28) <sup>(3)</sup>             | 1<br>(10)                      | 1<br>(18)         | 1<br>(23/28) <sup>(3)</sup>             |  |  |  |  |  |

| Comparate<br>(COMP1/0                               |                    |                     |                   | 2                                       | 2                              |                   |                                         |  |  |  |  |  |

| Others                                              |                    | 16-MF               |                   | indow watchdog,<br>nternal RC, 1- to    |                                |                   | scillator                               |  |  |  |  |  |

| CPU frequ                                           | iency              |                     |                   | 16 N                                    | MHz                            |                   |                                         |  |  |  |  |  |

| Operating                                           | voltage            |                     | 1.8 to 3.6        | √ (down to 1.65 ∖<br>1.65 to 3.6 V      | ✓ at power-down<br>without BOR | n) with BOR       |                                         |  |  |  |  |  |

| Operating<br>temperature - 40 to +85 °C / - 40 to + |                    |                     |                   |                                         |                                | 2                 |                                         |  |  |  |  |  |

| Packages                                            |                    | TSSOP20<br>UFQFPN20 | UFQFPN28          | UFQFPN32<br>LQFP48                      | TSSOP20<br>UFQFPN20            | UFQFPN28          | UFQFPN32<br>LQFP48                      |  |  |  |  |  |

| Table 1. Low-densit | y STM8L151x2/3 lov | v power device features | and peripheral counts |

|---------------------|--------------------|-------------------------|-----------------------|

|---------------------|--------------------|-------------------------|-----------------------|

The number of GPIOs given in this table includes the NRST/PA1 pin but the application can use the NRST/PA1 pin as general purpose output only (PA1).

2. 26 GPIOs in the STM8L151K3 and 40 GPIOs in the STM8L151C3.

3. 22 channels in the STM8L151K3 and 28 channels in the STM8L151C3.

## 3.1 Low-power modes

The low-density STM8L151x2/3 devices support five low power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

- Wait mode: The CPU clock is stopped, but selected peripherals keep running. An internal or external interrupt or a Reset can be used to exit the microcontroller from Wait mode (WFE or WFI mode). Wait consumption: refer to *Table 20*.

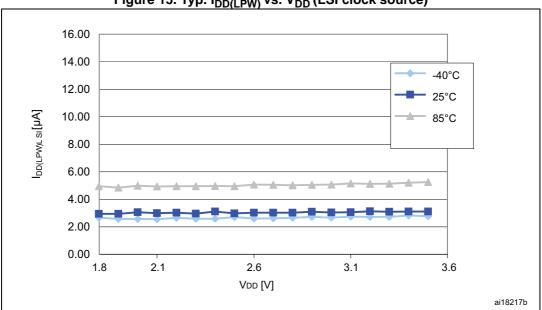

- Low power run mode: The CPU and the selected peripherals are running. Execution is done from RAM with a low speed oscillator (LSI or LSE). Flash and data EEPROM are stopped and the voltage regulator is configured in ultra-low-power mode. The microcontroller enters Low power run mode by software and can exit from this mode by software or by a reset.

All interrupts must be masked. They cannot be used to exit the microcontroller from this mode. Low power run mode consumption: refer to *Table 21*.

- Low power wait mode: This mode is entered when executing a Wait for event in Low power run mode. It is similar to Low power run mode except that the CPU clock is stopped. The wakeup from this mode is triggered by a Reset or by an internal or external event (peripheral event generated by the timers, serial interfaces, DMA controller (DMA1), comparators and I/O ports). When the wakeup is triggered by an event, the system goes back to Low power run mode. All interrupts must be masked. They cannot be used to exit the microcontroller from this mode. Low power wait mode consumption: refer to Table 22.

- Active-halt mode: CPU and peripheral clocks are stopped, except RTC. The wakeup can be triggered by RTC interrupts, external interrupts or reset. Active-halt consumption: refer to *Table 23* and *Table 24*.

- Halt mode: CPU and peripheral clocks are stopped, the device remains powered on. The RAM content is preserved. The wakeup is triggered by an external interrupt or reset. A few peripherals have also a wakeup from Halt capability. Switching off the internal reference voltage reduces power consumption. Through software configuration it is also possible to wake up the device without waiting for the internal reference voltage wakeup time to have a fast wakeup time of 5 µs. Halt consumption: refer to *Table 25*.

## 3.2 Central processing unit STM8

### 3.2.1 Advanced STM8 Core

The 8-bit STM8 core is designed for code efficiency and performance with an Harvard architecture and a 3-stage pipeline.

It contains 6 internal registers which are directly addressable in each execution context, 20 addressing modes including indexed indirect and relative addressing, and 80 instructions.

## 3.6 Memories

The low-density STM8L151x2/3 devices have the following main features:

- Up to 1 Kbyte of RAM

- The non-volatile memory is divided into three arrays:

- Up to 8 Kbyte of low-density embedded Flash program memory

- 256 byte of data EEPROM

- Option bytes.

The EEPROM embeds the error correction code (ECC) feature.

The option byte protects part of the Flash program memory from write and readout piracy.

## 3.7 DMA

A 4-channel direct memory access controller (DMA1) offers a memory-to-memory and peripherals-from/to-memory transfer capability. The 4 channels are shared between the following IPs with DMA capability: ADC1, I2C1, SPI1, USART1, the three Timers.

## 3.8 Analog-to-digital converter

- 12-bit analog-to-digital converter (ADC1) with 25 channels (including 1 fast channel), temperature sensor and internal reference voltage

- Conversion time down to 1  $\mu$ s with f<sub>SYSCLK</sub>= 16 MHz

- Programmable resolution

- Programmable sampling time

- Single and continuous mode of conversion

- Scan capability: automatic conversion performed on a selected group of analog inputs

- Analog watchdog

- Triggered by timer

- Note: ADC1 can be served by DMA1.

## 3.9 Ultra-low-power comparators

The low-density STM8L151x2/3 embed two comparators (COMP1 and COMP2) sharing the same current bias and voltage reference. The voltage reference can be internal or external (coming from an I/O).

- One comparator with fixed threshold (COMP1).

- One comparator rail to rail with fast or slow mode (COMP2). The threshold can be one of the following:

- External I/O

- Internal reference voltage or internal reference voltage sub multiple (1/4, 1/2, 3/4)

The two comparators can be used together to offer a window function. They can wake up from Halt mode.

## 3.17 Development support

#### **Development tools**

Development tools for the STM8 microcontrollers include:

- The STice emulation system offering tracing and code profiling

- The STVD high-level language debugger including C compiler, assembler and integrated development environment

- The STVP Flash programming software

The STM8 also comes with starter kits, evaluation boards and low-cost in-circuit debugging/programming tools.

#### Single wire data interface (SWIM) and debug module

The debug module with its single wire data interface (SWIM) permits non-intrusive real-time in-circuit debugging and fast memory programming.

The single-wire interface is used for direct access to the debugging module and memory programming. The interface can be activated in all device operation modes.

The non-intrusive debugging module features a performance close to a full-featured emulator. Beside memory and peripherals, CPU operation can also be monitored in real-time by means of shadow registers.

#### Bootloader

The low-density STM8L151x2/3 ultra-low-power devices feature a built-in bootloader (see *UM0560: STM8 bootloader user manual*).

The bootloader is used to download application software into the device memories, including RAM, program and data memory, using standard serial interfaces. It is a complementary solution to programming via the SWIM debugging interface.

| Pin number |          |          |          |         | Table 4. Low-density                                                                     | , 51 |           |          |      | •              |                  | -    |    |                                                                                |                                                                                                                     |

|------------|----------|----------|----------|---------|------------------------------------------------------------------------------------------|------|-----------|----------|------|----------------|------------------|------|----|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|            | Pin ı    | num      | nber     |         |                                                                                          |      |           |          | Inpu | t              | 0                | utpu | ıt |                                                                                |                                                                                                                     |

| LQFP48     | UFQFPN32 | UFQFPN28 | UFQFPN20 | TSSOP20 | Pin name                                                                                 | Type | I/O level | floating | ndm  | Ext. interrupt | High sink/source | QO   | ЬР | Main function<br>(after reset)                                                 | Default alternate<br>function                                                                                       |

| 34         | 22       | -        | -        | -       | PD5/ ADC1_IN9/<br>COMP1_INP                                                              | I/O  | -         | x        | х    | х              | HS               | х    | х  | Port D5                                                                        | ADC1_IN9/<br>Comparator1 positive<br>input                                                                          |

| 35         | 23       | -        | -        | -       | PD6/ADC1_IN8/<br>RTC_CALIB/<br>COMP1_INP                                                 | I/O  | -         | x        | х    | х              | HS               | х    | х  | Port D6                                                                        | ADC1_IN8 / RTC<br>calibration/<br>Comparator1 positive<br>input                                                     |

| 36         | 24       | -        | -        | -       | PD7 /ADC1_IN7/<br>RTC_ALARM/<br>COMP1_INP                                                | I/O  | -         | x        | х    | х              | HS               | х    | Х  | Port D7                                                                        | ADC1_IN7/RTC alarm/<br>Comparator1 positive<br>input                                                                |

| 14         | -        | -        | -        | -       | PE0                                                                                      | I/O  | -         | Х        | Х    | Х              | HS               | Х    | Х  | Port E0                                                                        | -                                                                                                                   |

| 15         | -        | -        | -        | -       | PE1                                                                                      | I/O  | -         | Х        | Х    | Х              | HS               | Х    | Х  | Port E1                                                                        | -                                                                                                                   |

| 16         | -        | -        | -        | -       | PE2                                                                                      | I/O  | -         | Х        | Х    | Х              | HS               | Х    | Х  | Port E2 -                                                                      |                                                                                                                     |

| 17         | -        | -        | -        | -       | PE3/ADC1_IN26                                                                            | I/O  | -         | Х        | Х    | Х              | HS               | Х    | Х  | Port E3                                                                        | ADC1_IN26                                                                                                           |

| 18         | -        | -        | -        | -       | PE4/ADC1_IN27                                                                            | I/O  | -         | Х        | Х    | Х              | HS               | Х    | Х  | Port E4                                                                        | ADC1_IN27                                                                                                           |

| 19         | -        | -        | -        | -       | PE5/ADC1_IN23/<br>COMP1_INP/<br>COMP2_INP                                                | I/O  | -         | x        | х    | х              | HS               | х    | х  | Port E5                                                                        | ADC1_IN23/<br>Comparator 1 positive<br>input/Comparator 2<br>positive input                                         |

| 47         | -        | -        | -        | -       | PE6/PVD_IN                                                                               | I/O  | -         | Х        | Х    | Х              | HS               | Х    | Х  | Port E6                                                                        | PVD_IN                                                                                                              |

| 48         | -        | -        | -        | -       | PE7/ADC1_IN25                                                                            | I/O  | -         | Х        | Х    | Х              | HS               | Х    | Х  | Port E7                                                                        | ADC1_IN25                                                                                                           |

| 32         | -        | -        | -        | -       | PF0/ADC1_IN24                                                                            | I/O  | -         | Х        | Х    | Х              | HS               | Х    | Х  | Port F0                                                                        | ADC1_IN24                                                                                                           |

| 10         | -        | -        | -        | -       | V <sub>DD</sub>                                                                          | S    | -         | I        | -    | 1              | -                | -    | 1  | Digital sup                                                                    | oply voltage                                                                                                        |

| -          | 8        | 7        | 5        | 8       | V <sub>DD</sub> /V <sub>DDA</sub> / V <sub>REF+</sub>                                    | S    | -         | -        | -    | -              | -                | -    | 1  |                                                                                | oply voltage /<br>sitive voltage reference                                                                          |

| 9          | 7        | 6        | 4        | 7       | V <sub>SS</sub> / V <sub>REF-</sub> / V <sub>SSA</sub>                                   | S    | -         | -        | -    | -              | -                | -    | -  | Ground voltage / ADC1 negative<br>voltage reference / Analog ground<br>voltage |                                                                                                                     |

| 11         | -        | -        | -        | -       | V <sub>DDA</sub>                                                                         | S    | -         | -        | -    | -              | -                | -    | -  | Analog supply voltage                                                          |                                                                                                                     |

| 12         | -        | -        | -        | -       | V <sub>REF+</sub>                                                                        | S    | -         | -        | -    | -              | -                | -    | -  | ADC1 positive voltage reference                                                |                                                                                                                     |

| 1          | 32       | 28       | 20       | 3       | PA0 <sup>(8)</sup> /[USART_CKJ <sup>(2)</sup><br>/<br>SWIM/BEEP/IR_TIM<br><sup>(9)</sup> | I/O  |           | х        | x    | x              | HS<br>(9)        | х    | x  | Port A0                                                                        | [USART1 synchronous<br>clock] <sup>(2)</sup> / SWIM input<br>and output /<br>Beep output / Infrared<br>Timer output |

| Table 4. Low-density STM8L151x2/3 | pin description | (continued) |

|-----------------------------------|-----------------|-------------|

|-----------------------------------|-----------------|-------------|

| 0x00 5140         RTC_TR1         RTC time register 1         0x00           0x00 5141         RTC_TR2         RTC time register 2         0x00           0x00 5143         RTC_TR3         RTC time register 3         0x00           0x00 5144         RTC_DR1         RTC date register 1         0x01           0x00 5145         RTC_DR2         RTC date register 3         0x00           0x00 5146         RTC_DR3         RTC date register 3         0x00           0x00 5147         RTC_CR1         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5148         RTC_CR2         RTC control register 1         0x01 <sup>(2)</sup> 0x00 5140         RTC_CR3         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5141         RTC_ISR1         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5142         RTC_ISR1         RTC control register 1         0x01 <sup>(2)</sup> 0x00 5141         RTC_ISR1         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5141         RTC_ISR1         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5150         RTC_SPRERL         RTC synchronous prescaler register 1         0x00 <sup>(2)</sup> 0x00 5151         RTC_SPRERL         RTC synchronous prescaler register 1         0x7F <sup>(2)</sup>                                   | Address   | Block | Register label | Register name                            | Reset status        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|----------------|------------------------------------------|---------------------|

| 0x00 5142         RTC_TR3         RTC time register 3         0x00           0x00 5143         RtC_DR1         Reserved area (1 byte)         0x01           0x00 5145         RTC_DR1         RTC date register 1         0x01           0x00 5145         RTC_DR2         RTC date register 3         0x00           0x00 5146         RTC_DR3         RTC date register 1         0x00 <sup>(2)</sup> 0x00 5147         RTC_CR1         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5148         RTC_CR2         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5140         RTC_CR3         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5140         RTC_ISR1         RTC initialization and status register 1         0x01           0x00 5140         RTC_ISR1         RTC initialization and status register 1         0x01           0x00 5141         RTC_ISR2         RTC initialization and status register 1         0x01           0x00 5151         RTC_SPRERH         RTC synchronous prescaler register low         0xF <sup>(2)</sup> 0x00 5152         RTC_WUTRH         RTC subsecond register low         0xF <sup>(2)</sup> 0x00 5153         RTC_SRE         RTC subsecond register low         0xF <sup>(2)</sup> 0x00 5156         RTC_SRL         RTC                                    | 0x00 5140 |       | RTC_TR1        | RTC time register 1                      | 0x00                |

| 0x00 5143         Reserved area (1 byte)           0x00 5144         RTC_DR1         RTC date register 1         0x01           0x00 5145         RTC_DR2         RTC date register 2         0x21           0x00 5146         RTC_DR3         RTC date register 3         0x00           0x00 5147         RTC_CR1         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5148         RTC_CR2         RTC control register 2         0x00 <sup>(2)</sup> 0x00 5140         RTC_CR3         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5141         RTC_ISR1         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5142         RTC_ISR1         RTC initialization and status register 1         0x01           0x00 5145         RTC_SPRERH         RTC synchronous prescaler register 1         0x00           0x00 5151         RTC_SPRERL         RTC synchronous prescaler register 1         0x71 <sup>(2)</sup> 0x00 5153         RTC_WUTRH         RTC subsecond register 1         0x00           0x00 5156         RTC_SRE         RTC subsecond register 1         0x00           0x00 5158         RTC_WUTRH         RTC subsecond register 1         0x00           0x00 5158         RTC_SRE         RTC write protection register         0x00                                                    | 0x00 5141 |       | RTC_TR2        | RTC time register 2                      | 0x00                |

| 0x00 5144         RTC_DR1         RTC date register 1         0x01           0x00 5145         RTC_DR2         RTC date register 2         0x21           0x00 5146         RTC_DR3         RTC date register 3         0x00           0x00 5147         RTC_CR1         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5148         RTC_CR2         RTC control register 2         0x00 <sup>(2)</sup> 0x00 5144         RTC_CR3         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5148         RTC_ISR1         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5140         RTC_ISR1         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5141         RTC_ISR2         RTC initialization and status register 1         0x01           0x00 5140         RTC_SPRERH         RTC synchronous prescaler register 1         0x00           0x00 5151         RTC_SPRERL         RTC synchronous prescaler register 10w         0xF <sup>(2)</sup> 0x00 5153         RTC_WUTRH         RTC wakeup timer register 10w         0xF <sup>(2)</sup> 0x00 5154         RTC_WUTRH         RTC subsecond register low         0xF <sup>(2)</sup> 0x00 5155         RTC_SRH         RTC subsecond register low         0x00           0x00 5155         RTC_SRH         RTC s                                    | 0x00 5142 |       | RTC_TR3        | RTC time register 3                      | 0x00                |

| 0x00 5145         RTC_DR2         RTC date register 2         0x21           0x00 5146         RTC_DR3         RTC date register 3         0x00           0x00 5147         RTC_CR1         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5148         RTC_CR2         RTC control register 2         0x00 <sup>(2)</sup> 0x00 5149         RTC_CR3         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5140         RTC_CR3         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5141         RTC_ISR1         RTC initialization and status register 1         0x01           0x00 5142         RTC_ISR2         RTC initialization and status register 2         0x00           0x00 5141         RTC_ISR2         RTC initialization and status register 1         0x01           0x00 5145         RTC_SPRERH         RTC synchronous prescaler register 1         0x00 <sup>(2)</sup> 0x00 5150         RTC_APRER         RTC asynchronous prescaler register 10w         0xFf <sup>(2)</sup> 0x00 5151         RTC_WUTRH         RTC wakeup timer register 10w         0xFf <sup>(2)</sup> 0x00 5155         RTC_WUTRL         RTC subsecond register high         0x00           0x00 5156         RTC_SRH         RTC subsecond register high         0x00           0x00 5157                           | 0x00 5143 | _     |                | Reserved area (1 byte)                   |                     |

| Ox00 5146         RTC_DR3         RTC date register 3         0x00           0x00 5147         0x00 5147         Reserved area (1 byte)         0x00 5148           0x00 5148         RTC_CR1         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5144         RTC_CR2         RTC control register 2         0x00 <sup>(2)</sup> 0x00 5144         RTC_CR3         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5145         RTC_ISR1         RTC initialization and status register 1         0x01           0x00 5146         RTC_SPRERH         RTC synchronous prescaler register 1         0x00 <sup>(2)</sup> 0x00 5150         RTC_SPRERL         RTC synchronous prescaler register 0x         0xFF <sup>(2)</sup> 0x00 5152         RTC_MUTRH         RTC wakeup timer register low         0xFF <sup>(2)</sup> 0x00 5155         RTC_WUTRL         RTC wakeup timer register low         0xFF <sup>(2)</sup> 0x00 5156         RTC_SSRL         RTC subsecond register low         0x00           0x00 5157         RTC_SSRH         RTC subsecond register low         0x00           0x00 5158         RTC_SSRH         RTC subsecond register low         0x00           0x00 5159         RTC_SSRH         RTC write protection register         0x00           0x00 5156                                    | 0x00 5144 |       | RTC_DR1        | RTC date register 1                      | 0x01                |

| Ox00 5147         Reserved area (1 byte)           0x00 5148         RTC_CR1         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5149         RTC_CR2         RTC control register 2         0x00 <sup>(2)</sup> 0x00 5144         RTC_CR3         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5144         RTC_ISR1         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5144         RTC_ISR1         RTC initialization and status register 1         0x01           0x00 5144         RTC_ISR2         RTC initialization and status register 1         0x01           0x00 5146         RTC_SPRERH         RTC synchronous prescaler register 1         0x00 <sup>(2)</sup> 0x00 5151         RTC_SPRERL         RTC synchronous prescaler register 1         0x01 <sup>(2)</sup> 0x00 5153         RTC_MUTRH         RTC wakeup timer register low         0xFF <sup>(2)</sup> 0x00 5154         RTC_WUTRL         RTC wakeup timer register low         0x0F <sup>(2)</sup> 0x00 5155         RTC_SSRL         RTC subsecond register low         0x00           0x00 5156         RTC_SSRH         RTC subsecond register low         0x00           0x00 5157         RTC_SSRH         RTC subsecond register low         0x00           0x00 5158         RTC_SSRH         RTC write                  | 0x00 5145 |       | RTC_DR2        | RTC date register 2                      | 0x21                |

| 0x00 5148RTC_CR1RTC control register 10x00 <sup>(2)</sup> 0x00 5149RTC_CR2RTC control register 20x00 <sup>(2)</sup> 0x00 5144RTC_CR3RTC control register 30x00 <sup>(2)</sup> 0x00 5146RTC_ISR1RTC initialization and status register 10x010x00 5140RTC_ISR2RTC initialization and Status register 20x000x00 5147RTC_SPRERHRTC synchronous prescaler register high0x00 <sup>(2)</sup> 0x00 5151RTC_SPRERLRTC synchronous prescaler register 10x01 <sup>(2)</sup> 0x00 5153RTC_APRERRTC synchronous prescaler register 10x7F <sup>(2)</sup> 0x00 5154RTC_WUTRHRTC synchronous prescaler register 10x7F <sup>(2)</sup> 0x00 5155RTC_WUTRHRTC wakeup timer register high0xFF <sup>(2)</sup> 0x00 5156RTC_SRLRTC synchronous prescaler register 10x000x00 5157RTC_SRLRTC subsecond register high0x000x00 5158RTC_SRHRTC subsecond register low0x000x00 5159RTC_SRHRTC subsecond register high0x000x00 5159RTC_SRHRTC subsecond register high0x000x00 5158RTC_SHIFTRHRTC shift register low0x000x00 5158RTC_ALRMAR1RTC shift register 10x00 <sup>(2)</sup> 0x00 5150RTC_ALRMAR3RTC alarm A register 30x00 <sup>(2)</sup>                                                                                                                                                                                                                                | 0x00 5146 |       | RTC_DR3        | RTC date register 3                      | 0x00                |

| 0x00 5149RTC_CR2RTC control register 20x00 <sup>(2)</sup> 0x00 514ARTC_CR3RTC control register 30x00 <sup>(2)</sup> 0x00 514BRTC_ISR1RTC initialization and status register 10x010x00 514CRTC_ISR2RTC initialization and status register 10x010x00 514DRTC_ISR2RTC initialization and status register 20x000x00 514ERTC_SPRERHRTC synchronous prescaler register high0x00 <sup>(2)</sup> 0x00 5150RTC_SPRERHRTC synchronous prescaler register low0xFF <sup>(2)</sup> 0x00 5152RTC_APRERRTC asynchronous prescaler register low0xFF <sup>(2)</sup> 0x00 5153RTC_WUTRHRTC wakeup timer register high0xFF <sup>(2)</sup> 0x00 5156RTC_WUTRHRTC subsecond register low0xFF <sup>(2)</sup> 0x00 5157RTC_SSRHRTC subsecond register low0x000x00 5158RTC_WPRRTC write protection register0x000x00 5158RTC_WPRRTC write protection register0x000x00 5158RTC_SHIFTRHRTC subsecond register high0x000x00 5158RTC_SHIFTRHRTC shift register high0x000x00 5156RTC_ALRMAR1RTC shift register 10x00 <sup>(2)</sup> 0x00 5158RTC_ALRMAR3RTC alarm A register 20x00 <sup>(2)</sup> 0x00 5150RTC_ALRMAR3RTC alarm A register 30x00 <sup>(2)</sup>                                                                                                                                                                                                                  | 0x00 5147 |       |                | Reserved area (1 byte)                   | 1                   |

| Ox00 514ARTC_CR3RTC control register 3Ox00 <sup>(2)</sup> 0x00 514BRTC_ISR1RTC initialization and status register 10x010x00 514CRTC_ISR2RTC initialization and status register 10x010x00 514DRTC_ISR2RTC initialization and Status register 20x000x00 514ERTC_SPRERHRTC synchronous prescaler register high0x00 <sup>(2)</sup> 0x00 5150RTC_SPRERLRTC synchronous prescaler register low0xFF <sup>(2)</sup> 0x00 5152RTC_APRERRTC asynchronous prescaler register low0xFF <sup>(2)</sup> 0x00 5153RTC_WUTRHRTC wakeup timer register low0xFF <sup>(2)</sup> 0x00 5156RTC_WUTRHRTC wakeup timer register low0xFF <sup>(2)</sup> 0x00 5156RTC_SRLRTC subsecond register low0xFF <sup>(2)</sup> 0x00 5158RTC_SRHRTC subsecond register low0x000x00 5158RTC_SRHRTC subsecond register low0x000x00 5158RTC_SRHRTC subsecond register high0x000x00 5158RTC_SRHRTC subsecond register high0x000x00 5158RTC_SRHRTC subsecond register high0x000x00 5158RTC_SRHRTC subsecond register high0x000x00 5156RTC_SHIFTRHRTC subsecond register high0x000x00 5158RTC_SHIFTRHRTC subsecond register high0x000x00 5158RTC_SHIFTRHRTC subsecond register high0x00 <sup>(2)</sup> 0x00 515DRTC_ALRMAR1RTC alarm A register 10x00 <sup>(2)</sup> 0x00 515DRTC_ALRMAR3RTC alarm A                                                                                        | 0x00 5148 | _     | RTC_CR1        | RTC control register 1                   | 0x00 <sup>(2)</sup> |

| Ox00 514B         Reserved area (1 byte)           0x00 514C         RTC_ISR1         RTC initialization and status register 1         0x01           0x00 514D         RTC_ISR2         RTC initialization and Status register 2         0x00           0x00 514E         RTC_ISR2         RTC initialization and Status register 2         0x00           0x00 514E         RTC_SPRERH         RTC synchronous prescaler register high         0x00 <sup>(2)</sup> 0x00 5150         RTC_SPRERL         RTC synchronous prescaler register low         0xFF <sup>(2)</sup> 0x00 5152         RTC_APRER         RTC asynchronous prescaler register high         0xFF <sup>(2)</sup> 0x00 5153         RTC_WUTRH         RTC wakeup timer register low         0xFF <sup>(2)</sup> 0x00 5156         RTC_SSRL         RTC subsecond register low         0xFF <sup>(2)</sup> 0x00 5158         RTC_SSRH         RTC subsecond register low         0x00           0x00 5158         RTC_SSRH         RTC subsecond register high         0x00           0x00 5159         RTC_SRH         RTC subsecond register high         0x00           0x00 5158         RTC_SHIFTRH         RTC subsecond register high         0x00           0x00 5158         RTC_SHIFTRH         RTC subsecond register high         0x00           0x00 5155          | 0x00 5149 | _     | RTC_CR2        | RTC control register 2                   | 0x00 <sup>(2)</sup> |

| Ox00 514CRTC_ISR1RTC initialization and status register 1Ox010x00 514DRTC_ISR2RTC initialization and Status register 20x000x00 514ERTC_ISR2RTC initialization and Status register 20x000x00 5150RTC_SPRERHRTC synchronous prescaler register high0x00 <sup>(2)</sup> 0x00 5151RTC_SPRERLRTC synchronous prescaler register low0xFF <sup>(2)</sup> 0x00 5152RTC_APRERRTC asynchronous prescaler register low0xFF <sup>(2)</sup> 0x00 5153RTC_WUTRHRTC wakeup timer register low0xFF <sup>(2)</sup> 0x00 5156RTC_WUTRLRTC wakeup timer register low0xFF <sup>(2)</sup> 0x00 5157RTC_SSRLRTC subsecond register low0x000x00 5158RTC_WPRRTC subsecond register low0x000x00 5158RTC_WPRRTC write protection register0x000x00 5156RTC_SSRHRTC subsecond register high0x000x00 5158RTC_SSRHRTC subsecond register low0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5156RTC_SSRHRTC subsecond register low0x000x00 5156RTC_SSRHRTC subsecond register low0x000x00 5156RTC_SSRHRTC subsecond register low0x000x00 5156RTC_SIFTRHRTC write protection register0x000x00 5156RTC_SIFTRHRTC shift register low0x000x00 5155RTC_ALRMAR1RTC alarm A register 10x00 <sup>(2)</sup> 0x00 5155RTC_ALRMAR3RTC alarm A register 3 </td <td>0x00 514A</td> <td></td> <td>RTC_CR3</td> <td>RTC control register 3</td> <td>0x00<sup>(2)</sup></td>            | 0x00 514A |       | RTC_CR3        | RTC control register 3                   | 0x00 <sup>(2)</sup> |

| Ox00 514D         RTC_ISR2         RTC initialization and Status register 2         Ox00           0x00 514E         RTC_ISR2         RTC initialization and Status register 2         0x00           0x00 514F         RTC_SPRERH         RTC synchronous prescaler register high         0x00 <sup>(2)</sup> 0x00 5150         RTC_SPRERL         RTC synchronous prescaler register low         0xFF <sup>(2)</sup> 0x00 5152         RTC_APRER         RTC asynchronous prescaler register         0x7F <sup>(2)</sup> 0x00 5153         RTC_WUTRH         RTC wakeup timer register high         0xFF <sup>(2)</sup> 0x00 5156         RTC_WUTRL         RTC wakeup timer register low         0xFF <sup>(2)</sup> 0x00 5156         RTC_SSRL         RTC subsecond register low         0x0F <sup>(2)</sup> 0x00 5156         RTC_SSRH         RTC subsecond register low         0x00           0x00 5158         RTC_WPR         RTC write protection register         0x00           0x00 5158         RTC_SHIFTRH         RTC write protection register         0x00           0x00 5156         RTC_SHIFTRH         RTC shift register high         0x00           0x00 5158         RTC_SHIFTRH         RTC write protection register         0x00           0x00 5156         RTC_SHIFTRH         RTC shift register low         0x00 | 0x00 514B | _     |                | Reserved area (1 byte)                   |                     |

| Ox00 514E<br>0x00 514F         Reserved area (2 byte)           0x00 5150         RTC_SPRERH         RTC synchronous prescaler register high         0x00 <sup>(2)</sup> 0x00 5151         RTC_SPRERL         RTC synchronous prescaler register low         0xFF <sup>(2)</sup> 0x00 5152         RTC_APRER         RTC asynchronous prescaler register         0x7F <sup>(2)</sup> 0x00 5153         RTC_WUTRH         RTC wakeup timer register high         0xFF <sup>(2)</sup> 0x00 5155         RTC_WUTRL         RTC wakeup timer register low         0xFF <sup>(2)</sup> 0x00 5156         RTC_WUTRL         RTC subsecond register low         0x00           0x00 5157         RTC_SRH         RTC subsecond register low         0x00           0x00 5158         RTC_SRH         RTC subsecond register high         0x00           0x00 5159         RTC_WURR         RTC subsecond register high         0x00           0x00 5158         RTC_WPR         RTC subsecond register high         0x00           0x00 5159         RTC_SHIFTRH         RTC subsecond register high         0x00           0x00 5150         RTC_SHIFTRH         RTC shift register high         0x00           0x00 5150         RTC_ALRMAR1         RTC alarm A register 1         0x00 <sup>(2)</sup> 0x00 5150         RTC_ALRMAR3                   | 0x00 514C | _     | RTC_ISR1       | RTC initialization and status register 1 | 0x01                |

| Ox00 514F         RTC         RTC_SPRERH         RTC synchronous prescaler register high         0x00 <sup>(2)</sup> 0x00 5150         RTC_SPRERL         RTC synchronous prescaler register low         0xFF <sup>(2)</sup> 0x00 5152         RTC_APRER         RTC asynchronous prescaler register         0x7F <sup>(2)</sup> 0x00 5153         RTC_WUTRH         RTC wakeup timer register high         0xFF <sup>(2)</sup> 0x00 5155         RTC_WUTRL         RTC wakeup timer register low         0xFF <sup>(2)</sup> 0x00 5156         RTC_SSRL         RTC subsecond register low         0xFF <sup>(2)</sup> 0x00 5158         RTC_SSRH         RTC subsecond register low         0x00           0x00 5158         RTC_WPR         RTC write protection register         0x00           0x00 5158         RTC_SSRH         RTC subsecond register high         0x00           0x00 5159         RTC_SSRH         RTC subsecond register high         0x00           0x00 5158         RTC_SSRH         RTC subsecond register high         0x00           0x00 5159         RTC_SSRH         RTC subsecond register high         0x00           0x00 5150         RTC_SHIFTRH         RTC subsecond register high         0x00           0x00 5150         RTC_SHIFTRL         RTC shift register low         0x00                     | 0x00 514D | -     | RTC_ISR2       | RTC initialization and Status register 2 | 0x00                |

| NUMBER<br>OX00 5151RTCRTC_SPRERLRTC synchronous prescaler register low0xFF(2)0x00 5152RTC_APRERRTC asynchronous prescaler register0x7F(2)0x00 5153RTC_WUTRHRTC wakeup timer register high0xFF(2)0x00 5154RTC_WUTRHRTC wakeup timer register high0xFF(2)0x00 5155RTC_WUTRLRTC wakeup timer register low0xFF(2)0x00 5156RTC_WUTRLRTC wakeup timer register low0x000x00 5157RTC_SSRLRTC subsecond register low0x000x00 5158RTC_WPRRTC subsecond register high0x000x00 5159RTC_SSRHRTC subsecond register high0x000x00 5159RTC_SSRHRTC subsecond register high0x000x00 5158RTC_SIFTRHRTC subsecond register high0x000x00 5158RTC_SIFTRHRTC subsecond register high0x000x00 5155RTC_SIFTRHRTC subsecond register high0x000x00 5156RTC_SIFTRHRTC subsecond register high0x000x00 5150RTC_ALRMAR1RTC shift register high0x000x00 515DRTC_ALRMAR2RTC alarm A register 10x00(2)0x00 515ERTC_ALRMAR3RTC alarm A register 30x00(2)                                                                                                                                                                                                                                                                                                                                                                                                                            |           |       |                | Reserved area (2 byte)                   | L                   |

| DX00 5151RTC_SPRERLRTC synchronous prescaler register 10wDXFF(2)0x00 5152RTC_APRERRTC asynchronous prescaler register0x7F(2)0x00 5153RTC_WUTRHRTC wakeup timer register high0xFF(2)0x00 5155RTC_WUTRLRTC wakeup timer register low0xFF(2)0x00 5156RTC_SSRLRTC subsecond register low0x000x00 5157RTC_SSRHRTC subsecond register low0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_SSRHRTC subsecond register high0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5158RTC_SHIFTRHRTC subsecond register high0x000x00 515ARTC_SHIFTRHRTC shift register high0x000x00 515BRTC_ALRMAR1RTC alarm A register 10x00(2)0x00 515DRTC_ALRMAR3RTC alarm A register 30x00(2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x00 5150 |       | RTC_SPRERH     | RTC synchronous prescaler register high  | 0x00 <sup>(2)</sup> |

| Ox00 5153Ox00 5153RtC_WUTRHRtC wakeup timer register highOxFF <sup>(2)</sup> Ox00 5155RtC_WUTRLRtC wakeup timer register lowOxFF <sup>(2)</sup> Ox00 5156RtC_SSRLRtC subsecond register lowOx00Ox00 5157RtC_SSRLRtC subsecond register highOx00Ox00 5158RtC_SSRHRtC subsecond register highOx00Ox00 5159RtC_SSRHRtC subsecond register highOx00Ox00 5158RtC_SSRHRtC subsecond register highOx00Ox00 5158RtC_SSRHRtC subsecond register highOx00Ox00 5158RtC_SRHRtC subsecond register highOx00Ox00 5158RtC_SHIFTRHRtC subsecond register highOx00Ox00 5150RtC_SHIFTRHRtC shift register highOx00Ox00 515DRtC_ALRMAR1RtC alarm A register 1Ox00 <sup>(2)</sup> Ox00 515DRtC_ALRMAR3RtC alarm A register 3Ox00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x00 5151 | RTC   | RTC_SPRERL     | RTC synchronous prescaler register low   | 0xFF <sup>(2)</sup> |

| 0x00 5154RTC_WUTRHRTC wakeup timer register high0xFF^{(2)}0x00 5155RTC_WUTRLRTC wakeup timer register low0xFF^{(2)}0x00 5156RTC_SSRLRTC wakeup timer register low0x000x00 5157RTC_SSRLRTC subsecond register low0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_WPRRTC write protection register0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5158RTC_SIFHRTC subsecond register high0x000x00 5158RTC_SHIFTRHRTC subsecond register high0x000x00 515ARTC_SHIFTRHRTC shift register high0x000x00 515BRTC_ALRMAR1RTC alarm A register 10x00^{(2)}0x00 515DRTC_ALRMAR3RTC alarm A register 30x00^{(2)}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x00 5152 |       | RTC_APRER      | RTC asynchronous prescaler register      | 0x7F <sup>(2)</sup> |

| 0x00 5155RTC_WUTRLRTC wakeup timer register low0xFF <sup>(2)</sup> 0x00 5156RTC_SSRLRTC subsecond register low0x000x00 5157RTC_SSRLRTC subsecond register low0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_WPRRTC write protection register0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_SRHRTC subsecond register high0x000x00 5159RTC_SHIFTRHRTC write protection register0x000x00 515ARTC_SHIFTRHRTC shift register high0x000x00 515BRTC_ALRMAR1RTC alarm A register 10x00 <sup>(2)</sup> 0x00 515DRTC_ALRMAR2RTC alarm A register 30x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x00 5153 |       |                | Reserved area (1 byte)                   | 1                   |

| 0x00 5156Reserved area (1 byte)0x00 5157RTC_SSRLRTC subsecond register low0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_WPRRTC write protection register0x000x00 5159RTC_WPRRTC subsecond register high0x000x00 5159RTC_WPRRTC subsecond register high0x000x00 5159RTC_SSRHRTC subsecond register high0x000x00 515ARTC_SHIFTRHRTC write protection register0x000x00 515BRTC_SHIFTRLRTC shift register high0x000x00 515CRTC_ALRMAR1RTC alarm A register 10x00 <sup>(2)</sup> 0x00 515DRTC_ALRMAR2RTC alarm A register 30x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0x00 5154 |       | RTC_WUTRH      | RTC wakeup timer register high           | 0xFF <sup>(2)</sup> |

| 0x00 5157RTC_SSRLRTC subsecond register low0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_WPRRTC write protection register0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_WPRRTC write protection register0x000x00 5159RTC_SHIFTRHRTC write protection register0x000x00 515ARTC_SHIFTRHRTC shift register high0x000x00 515BRTC_ALRMAR1RTC alarm A register 10x00 <sup>(2)</sup> 0x00 515DRTC_ALRMAR3RTC alarm A register 30x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x00 5155 |       | RTC_WUTRL      | RTC wakeup timer register low            | 0xFF <sup>(2)</sup> |

| 0x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_WPRRTC write protection register0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_WPRRTC write protection register0x000x00 515ARTC_SHIFTRHRTC shift register high0x000x00 515BRTC_SHIFTRLRTC shift register low0x000x00 515CRTC_ALRMAR1RTC alarm A register 10x00 <sup>(2)</sup> 0x00 515ERTC_ALRMAR3RTC alarm A register 30x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x00 5156 |       |                | Reserved area (1 byte)                   | 1                   |

| 0x00 5159RTC_WPRRTC write protection register0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_WPRRTC write protection register0x000x00 515ARTC_SHIFTRHRTC shift register high0x000x00 515BRTC_SHIFTRLRTC shift register low0x000x00 515CRTC_ALRMAR1RTC alarm A register 10x00 <sup>(2)</sup> 0x00 515ERTC_ALRMAR3RTC alarm A register 30x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x00 5157 |       | RTC_SSRL       | RTC subsecond register low               | 0x00                |

| 0x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_WPRRTC write protection register0x000x00 515ARTC_SHIFTRHRTC shift register high0x000x00 515BRTC_ALRMAR1RTC shift register low0x000x00 515CRTC_ALRMAR2RTC alarm A register 10x00 <sup>(2)</sup> 0x00 515ERTC_ALRMAR3RTC alarm A register 30x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x00 5158 |       | RTC_SSRH       | RTC subsecond register high              | 0x00                |

| 0x00 5159RTC_WPRRTC write protection register0x000x00 515ARTC_SHIFTRHRTC shift register high0x000x00 515BRTC_SHIFTRLRTC shift register low0x000x00 515CRTC_ALRMAR1RTC alarm A register 10x00 <sup>(2)</sup> 0x00 515DRTC_ALRMAR2RTC alarm A register 20x00 <sup>(2)</sup> 0x00 515ERTC_ALRMAR3RTC alarm A register 30x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0x00 5159 |       | RTC_WPR        | RTC write protection register            | 0x00                |

| 0x00 515A       RTC_SHIFTRH       RTC shift register high       0x00         0x00 515B       RTC_SHIFTRL       RTC shift register low       0x00         0x00 515C       RTC_ALRMAR1       RTC alarm A register 1       0x00 <sup>(2)</sup> 0x00 515D       RTC_ALRMAR2       RTC alarm A register 2       0x00 <sup>(2)</sup> 0x00 515E       RTC_ALRMAR3       RTC alarm A register 3       0x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0x00 5158 |       | RTC_SSRH       | RTC subsecond register high              | 0x00                |

| 0x00 515B       RTC_SHIFTRL       RTC shift register low       0x00         0x00 515C       RTC_ALRMAR1       RTC alarm A register 1       0x00 <sup>(2)</sup> 0x00 515D       RTC_ALRMAR2       RTC alarm A register 2       0x00 <sup>(2)</sup> 0x00 515E       RTC_ALRMAR3       RTC alarm A register 3       0x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0x00 5159 |       | RTC_WPR        | RTC write protection register            | 0x00                |

| 0x00 515C     RTC_ALRMAR1     RTC alarm A register 1     0x00 <sup>(2)</sup> 0x00 515D     RTC_ALRMAR2     RTC alarm A register 2     0x00 <sup>(2)</sup> 0x00 515E     RTC_ALRMAR3     RTC alarm A register 3     0x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0x00 515A |       | RTC_SHIFTRH    | RTC shift register high                  | 0x00                |

| 0x00 515D     RTC_ALRMAR2     RTC alarm A register 2     0x00 <sup>(2)</sup> 0x00 515E     RTC_ALRMAR3     RTC alarm A register 3     0x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x00 515B |       | RTC_SHIFTRL    | RTC shift register low                   | 0x00                |

| 0x00 515E RTC_ALRMAR3 RTC alarm A register 3 0x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x00 515C |       | RTC_ALRMAR1    | RTC alarm A register 1                   | 0x00 <sup>(2)</sup> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x00 515D |       | RTC_ALRMAR2    | RTC alarm A register 2                   | 0x00 <sup>(2)</sup> |

| 0x00 515F RTC_ALRMAR4 RTC alarm A register 4 0x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x00 515E |       | RTC_ALRMAR3    | RTC alarm A register 3                   | 0x00 <sup>(2)</sup> |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x00 515F |       | RTC_ALRMAR4    | RTC alarm A register 4                   | 0x00 <sup>(2)</sup> |

Table 8. General hardware register map (continued)

## 7 Option bytes

Option bytes contain configurations for device hardware features as well as the memory protection of the device. They are stored in a dedicated memory block.

All option bytes can be modified in ICP mode (with SWIM) by accessing the EEPROM address. See *Table 11* for details on option byte addresses.

The option bytes can also be modified 'on the fly' by the application in IAP mode, except for the ROP and UBC values which can only be taken into account when they are modified in ICP mode (with the SWIM).

Refer to the STM8L15x Flash programming manual (PM0054) and STM8 SWIM and Debug Manual (UM0470) for information on SWIM programming procedures.

| Addr.     | Ontion nome                                                                  | Option        | n Option bits          |                                  |   |    |               |             |               |             | Factory default |

|-----------|------------------------------------------------------------------------------|---------------|------------------------|----------------------------------|---|----|---------------|-------------|---------------|-------------|-----------------|

| Addr.     | Option name                                                                  | byte<br>No.   | 7                      | 6                                | 5 | 4  | 3             | 2           | 1             | 0           | setting         |

| 0x00 4800 | Read-out<br>protection<br>(ROP)                                              | OPT0          |                        | ROP[7:0]                         |   |    |               |             |               |             | 0xAA            |

| 0x00 4802 | UBC (User<br>Boot code size)                                                 | OPT1          |                        | UBC[7:0]                         |   |    |               |             |               |             | 0x00            |

| 0x00 4807 |                                                                              |               |                        | Reserved                         |   |    |               |             |               |             |                 |

| 0x00 4808 | Independent<br>watchdog<br>option                                            | OPT3<br>[3:0] |                        | Reserved                         |   |    | WWDG<br>_HALT | WWDG<br>_HW | IWDG<br>_HALT | IWDG<br>_HW | 0x00            |

| 0x00 4809 | Number of<br>stabilization<br>clock cycles for<br>HSE and LSE<br>oscillators | OPT4          |                        | Reserved LSECNT[1:0] HSECNT[1:0] |   |    |               | 0x00        |               |             |                 |

| 0x00 480A | Brownout reset<br>(BOR)                                                      | OPT5<br>[3:0] | Reserved BOR_TH BOR_ON |                                  |   |    |               | 0x01        |               |             |                 |

| 0x00 480B | Bootloader                                                                   | OPTBL         |                        |                                  |   |    |               |             |               | 0x00        |                 |