Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | STM8                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 16MHz                                                                |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, IR, POR, PWM, WDT                       |

| Number of I/O              | 26                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | 256 x 8                                                              |

| RAM Size                   | 1K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                          |

| Data Converters            | A/D 18x12b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 28-UFQFN                                                             |

| Supplier Device Package    | 28-UFQFPN (4x4)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8l151g3u6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.3 Reset and supply management

## 3.3.1 Power supply scheme

The device requires a 1.65 V to 3.6 V operating supply voltage ( $V_{DD}$ ). The external power supply pins must be connected as follows:

- V<sub>SS1</sub>; V<sub>DD1</sub> = 1.8 to 3.6 V, down to 1.65 V at power down: external power supply for I/Os and for the internal regulator. Provided externally through V<sub>DD1</sub> pins, the corresponding ground pin is V<sub>SS1</sub>.

- $V_{SSA;} V_{DDA} = 1.8$  to 3.6 V, down to 1.65 V at power down: external power supplies for analog peripherals (minimum voltage to be applied to  $V_{DDA}$  is 1.8 V when the ADC1 is used).  $V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD1}$  and  $V_{SS1}$ , respectively.

- $V_{SS2}$ ;  $V_{DD2} = 1.8$  to 3.6 V, down to 1.65 V at power down: external power supplies for I/Os.  $V_{DD2}$  and  $V_{SS2}$  must be connected to  $V_{DD1}$  and  $V_{SS1}$ , respectively.

- V<sub>REF+</sub>; V<sub>REF-</sub> (for ADC1): external reference voltage for ADC1. Must be provided externally through V<sub>REF+</sub> and V<sub>REF-</sub> pin.

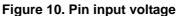

## 3.3.2 Power supply supervisor

The device has an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR), coupled with a brownout reset (BOR) circuitry. At power-on, BOR is always active, and ensures proper operation starting from 1.8 V. After the 1.8 V BOR threshold is reached, the option byte loading process starts, either to confirm or modify default thresholds, or to disable BOR permanently (in which case, the V<sub>DD</sub> min value at power down is 1.65 V).

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Halt mode, it is possible to automatically switch off the internal reference voltage (and consequently the BOR) in Halt mode. The device remains under reset when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

### 3.3.3 Voltage regulator

The low-density STM8L151x2/3 embeds an internal voltage regulator for generating the 1.8 V power supply for the core and peripherals.

This regulator has two different modes:

- Main voltage regulator mode (MVR) for Run, Wait for interrupt (WFI) and Wait for event (WFE) modes.

- Low power voltage regulator mode (LPVR) for Halt, Active-halt, Low power run and Low power wait modes.

When entering Halt or Active-halt modes, the system automatically switches from the MVR to the LPVR in order to reduce current consumption.

MSB have a fixed value: 0x6.

- 3. The TS\_Factory\_CONV\_V90 byte represents the LSB of the V<sub>90</sub> 12-bit ADC1 conversion result. The MSB have a fixed value: 0x3.

- 4. Refer to *Table 8* for an overview of hardware register mapping, to *Table 7* for details on I/O port hardware registers, and to *Table 9* for information on CPU/SWIM/debug module controller registers.

| Memory area          | Size    | Start address | End address |  |  |  |  |  |

|----------------------|---------|---------------|-------------|--|--|--|--|--|

| RAM                  | 1 Kbyte | 0x00 0000     | 0x00 03FF   |  |  |  |  |  |

|                      | 8 Kbyte | 0x00 8000     | 0x00 9FFF   |  |  |  |  |  |

| Flash program memory | 4 Kbyte | 0x00 8000     | 0x00 8FFF   |  |  |  |  |  |

#### Table 5. Flash and RAM boundary addresses

## 5.2 Register map

| ······································ |                           |                          |                                                                                  |                 |  |  |  |  |

|----------------------------------------|---------------------------|--------------------------|----------------------------------------------------------------------------------|-----------------|--|--|--|--|

| Address                                | dress Block Register labe |                          | Register name                                                                    | Reset<br>status |  |  |  |  |

| 0x00 4910                              | -                         | VREFINT_Factory_<br>CONV | Value of the internal reference voltage<br>measured during the factory phase     | 0xXX            |  |  |  |  |

| 0x00 4911                              | -                         | TS_Factory_CONV_<br>V90  | Value of the temperature sensor output voltage measured during the factory phase | 0xXX            |  |  |  |  |

### Table 6. Factory conversion registers

| Table 7. I/O port hardware register ma | ap |

|----------------------------------------|----|

|----------------------------------------|----|

| Address   | Block  | Register label                           | Register name                     | Reset<br>status |

|-----------|--------|------------------------------------------|-----------------------------------|-----------------|

| 0x00 5000 |        | PA_ODR Port A data output latch register |                                   | 0x00            |

| 0x00 5001 |        | PA_IDR                                   | Port A input pin value register   | 0xXX            |

| 0x00 5002 | Port A | PA_DDR                                   | Port A data direction register    | 0x00            |

| 0x00 5003 |        | PA_CR1                                   | Port A control register 1         | 0x01            |

| 0x00 5004 |        | PA_CR2                                   | Port A control register 2         | 0x00            |

| 0x00 5005 |        | PB_ODR                                   | Port B data output latch register | 0x00            |

| 0x00 5006 |        | PB_IDR                                   | Port B input pin value register   | 0xXX            |

| 0x00 5007 | Port B | PB_DDR                                   | Port B data direction register    | 0x00            |

| 0x00 5008 | ]      | PB_CR1                                   | Port B control register 1         | 0x00            |

| 0x00 5009 |        | PB_CR2                                   | Port B control register 2         | 0x00            |

| Address                      | Block | lock Register label Register name |                                                         | Reset status |

|------------------------------|-------|-----------------------------------|---------------------------------------------------------|--------------|

| 0x00 5084                    |       |                                   | Reserved area (1 byte)                                  |              |

| 0x00 5085                    |       | DMA1_C1M0ARH                      | DMA1 memory 0 address high register<br>(channel 1)      | 0x00         |

| 0x00 5086                    |       | DMA1_C1M0ARL                      | DMA1 memory 0 address low register<br>(channel 1)       | 0x00         |

| 0x00 5087<br>0x00 5088       |       |                                   | Reserved area (2 byte)                                  |              |

| 0x00 5089                    |       | DMA1_C2CR                         | DMA1 channel 2 configuration register                   | 0x00         |

| 0x00 508A                    |       | DMA1_C2SPR                        | DMA1 channel 2 status & priority register               | 0x00         |

| 0x00 508B                    |       | DMA1_C2NDTR                       | DMA1 number of data to transfer register<br>(channel 2) | 0x00         |

| 0x00 508C                    |       | DMA1_C2PARH                       | DMA1 peripheral address high register<br>(channel 2)    | 0x52         |

| 0x00 508D                    |       | DMA1_C2PARL                       | DMA1 peripheral address low register<br>(channel 2)     | 0x00         |

| 0x00 508E                    |       |                                   | Reserved area (1 byte)                                  |              |

| 0x00 508F                    |       | DMA1_C2M0ARH                      | DMA1 memory 0 address high register<br>(channel 2)      | 0x00         |

| 0x00 5090                    | DMA1  | DMA1_C2M0ARL                      | DMA1 memory 0 address low register<br>(channel 2)       | 0x00         |

| 0x00 5091<br>0x00 5092       |       |                                   | Reserved area (2 byte)                                  |              |

| 0x00 5093                    |       | DMA1_C3CR                         | DMA1 channel 3 configuration register                   | 0x00         |

| 0x00 5094                    |       | DMA1_C3SPR                        | DMA1 channel 3 status & priority register               | 0x00         |

| 0x00 5095                    |       | DMA1_C3NDTR                       | DMA1 number of data to transfer register<br>(channel 3) | 0x00         |

| 0x00 5096                    |       | DMA1_C3PARH_<br>C3M1ARH           | DMA1 peripheral address high register<br>(channel 3)    | 0x40         |

| 0x00 5097                    |       | DMA1_C3PARL_<br>C3M1ARL           | DMA1 peripheral address low register<br>(channel 3)     | 0x00         |

| 0x00 5098                    |       | DMA_C3M0EAR                       | DMA channel 3 memory 0 extended<br>address register     | 0x00         |

| 0x00 5099                    |       | DMA1_C3M0ARH                      | DMA1 memory 0 address high register<br>(channel 3)      | 0x00         |

| 0x00 509A                    |       | DMA1_C3M0ARL                      | DMA1 memory 0 address low register<br>(channel 3)       | 0x00         |

| 0x00 509B<br>to<br>0x00 509C |       |                                   | Reserved area (3 byte)                                  |              |

Table 8. General hardware register map (continued)

| Address                      | Block | Register label | Register name                          | Reset status |

|------------------------------|-------|----------------|----------------------------------------|--------------|

| 0x00 5250                    |       | TIM2_CR1       | TIM2 control register 1                | 0x00         |

| 0x00 5251                    |       | TIM2_CR2       | TIM2 control register 2                | 0x00         |

| 0x00 5252                    |       | TIM2_SMCR      | TIM2 Slave mode control register       | 0x00         |

| 0x00 5253                    |       | TIM2_ETR       | TIM2 external trigger register         | 0x00         |

| 0x00 5254                    |       | TIM2_DER       | TIM2 DMA1 request enable register      | 0x00         |

| 0x00 5255                    |       | TIM2_IER       | TIM2 interrupt enable register         | 0x00         |

| 0x00 5256                    |       | TIM2_SR1       | TIM2 status register 1                 | 0x00         |

| 0x00 5257                    |       | TIM2_SR2       | TIM2 status register 2                 | 0x00         |

| 0x00 5258                    |       | TIM2_EGR       | TIM2 event generation register         | 0x00         |

| 0x00 5259                    |       | TIM2_CCMR1     | TIM2 capture/compare mode register 1   | 0x00         |

| 0x00 525A                    |       | TIM2_CCMR2     | TIM2 capture/compare mode register 2   | 0x00         |

| 0x00 525B                    | TIM2  | TIM2_CCER1     | TIM2 capture/compare enable register 1 | 0x00         |

| 0x00 525C                    |       | TIM2_CNTRH     | TIM2 counter high                      | 0x00         |

| 0x00 525D                    |       | TIM2_CNTRL     | TIM2 counter low                       | 0x00         |

| 0x00 525E                    |       | TIM2_PSCR      | TIM2 prescaler register                | 0x00         |

| 0x00 525F                    | ]     | TIM2_ARRH      | TIM2 auto-reload register high         | 0xFF         |

| 0x00 5260                    | ]     | TIM2_ARRL      | TIM2 auto-reload register low          | 0xFF         |

| 0x00 5261                    | ]     | TIM2_CCR1H     | TIM2 capture/compare register 1 high   | 0x00         |

| 0x00 5262                    |       | TIM2_CCR1L     | TIM2 capture/compare register 1 low    | 0x00         |

| 0x00 5263                    | ]     | TIM2_CCR2H     | TIM2 capture/compare register 2 high   | 0x00         |

| 0x00 5264                    | ]     | TIM2_CCR2L     | TIM2 capture/compare register 2 low    | 0x00         |

| 0x00 5265                    | ]     | TIM2_BKR       | TIM2 break register                    | 0x00         |

| 0x00 5266                    | ]     | TIM2_OISR      | TIM2 output idle state register        | 0x00         |

| 0x00 5267<br>to<br>0x00 527F |       |                | Reserved area (25 byte)                |              |

Table 8. General hardware register map (continued)

# 6 Interrupt vector mapping

|            | Table 10. Interrupt mapping |                                                                                                        |                             |                                       |                                      |                                                     |                   |  |  |

|------------|-----------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------|--------------------------------------|-----------------------------------------------------|-------------------|--|--|

| IRQ<br>No. | Source<br>block             | Description                                                                                            | Wakeup<br>from Halt<br>mode | Wakeup<br>from<br>Active-halt<br>mode | Wakeup<br>from Wait<br>(WFI<br>mode) | Wakeup<br>from Wait<br>(WFE<br>mode) <sup>(1)</sup> | Vector<br>address |  |  |

| -          | RESET                       | Reset                                                                                                  | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8000         |  |  |

| -          | TRAP                        | Software interrupt                                                                                     | -                           | -                                     | -                                    | -                                                   | 0x00 8004         |  |  |

| 0          | TLI <sup>(2)</sup>          | External top level interrupt                                                                           | -                           | -                                     | -                                    | -                                                   | 0x00 8008         |  |  |

| 1          | FLASH                       | FLASH end of programing/<br>write attempted to<br>protected page interrupt                             | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 800C         |  |  |

| 2          | DMA1 0/1                    | DMA1 channels 0/1 half<br>transaction/transaction<br>complete interrupt                                | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8010         |  |  |

| 3          | DMA1 2/3                    | DMA1 channels 2/3 half<br>transaction/transaction<br>complete interrupt                                | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8014         |  |  |

| 4          | RTC                         | RTC alarm A/<br>wakeup/tamper 1/<br>tamper 2/tamper 3                                                  | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8018         |  |  |

| 5          | EXTIE/<br>PVD               | External interrupt port E<br>PVD interrupt                                                             | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 801C         |  |  |

| 6          | EXTIB                       | External interrupt port B                                                                              | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8020         |  |  |

| 7          | EXTID                       | External interrupt port D                                                                              | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8024         |  |  |

| 8          | EXTI0                       | External interrupt 0                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8028         |  |  |

| 9          | EXTI1                       | External interrupt 1                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 802C         |  |  |

| 10         | EXTI2                       | External interrupt 2                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8030         |  |  |

| 11         | EXTI3                       | External interrupt 3                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8034         |  |  |

| 12         | EXTI4                       | External interrupt 4                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8038         |  |  |

| 13         | EXTI5                       | External interrupt 5                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 803C         |  |  |

| 14         | EXTI6                       | External interrupt 6                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8040         |  |  |

| 15         | EXTI7                       | External interrupt 7                                                                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8044         |  |  |

| 16         |                             |                                                                                                        | Reserved                    |                                       |                                      |                                                     | 0x00 8048         |  |  |

| 17         | CLK                         | CLK system clock switch/<br>CSS interrupt                                                              | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 804C         |  |  |

| 18         | COMP1/<br>COMP2/<br>ADC1    | COMP1 interrupt<br>COMP2 interrupt<br>ACD1 end of conversion/<br>analog watchdog/<br>overrun interrupt | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8050         |  |  |

### Table 10. Interrupt mapping

| IRQ<br>No. | Source<br>block   | Description                                                                                               | Wakeup<br>from Halt<br>mode | Wakeup<br>from<br>Active-halt<br>mode | Wakeup<br>from Wait<br>(WFI<br>mode) | Wakeup<br>from Wait<br>(WFE<br>mode) <sup>(1)</sup> | Vector<br>address |  |  |

|------------|-------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------|--------------------------------------|-----------------------------------------------------|-------------------|--|--|

| 19         | TIM2              | TIM2 update/overflow/<br>trigger/break interrupt                                                          | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8054         |  |  |

| 20         | TIM2              | TIM2 capture/<br>compare interrupt                                                                        | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8058         |  |  |

| 21         | TIM3              | TIM3 update/overflow/<br>trigger/break interrupt                                                          | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 805C         |  |  |

| 22         | ТІМЗ              | TIM3 capture/<br>compare interrupt                                                                        | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8060         |  |  |

| 23         | RI                | RI trigger interrupt                                                                                      | -                           | -                                     | Yes                                  | -                                                   | 0x00 8064         |  |  |

| 24         |                   |                                                                                                           | Reserved                    |                                       | 0x00 8068                            |                                                     |                   |  |  |

| 25         | TIM4              | TIM4 update/overflow/<br>trigger interrupt                                                                | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 806C         |  |  |

| 26         | SPI1              | SPI1 TX buffer empty/<br>RX buffer not empty/<br>error/wakeup interrupt                                   | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 8070         |  |  |

| 27         | USART1            | USART1 transmit data<br>register empty/<br>transmission complete<br>interrupt                             | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8074         |  |  |

| 28         | USART1            | USART1 received data<br>ready/overrun error/<br>idle line detected/parity<br>error/global error interrupt | -                           | -                                     | Yes                                  | Yes                                                 | 0x00 8078         |  |  |

| 29         | I <sup>2</sup> C1 | I <sup>2</sup> C1 interrupt <sup>(3)</sup>                                                                | Yes                         | Yes                                   | Yes                                  | Yes                                                 | 0x00 807C         |  |  |

Table 10. Interrupt mapping (continued)

The Low power wait mode is entered when executing a WFE instruction in Low power run mode. In WFE mode, the

interrupt is served if it has been previously enabled. After processing the interrupt, the processor goes back to WFE mode.

When the interrupt is configured as a wakeup event, the CPU wakes up and resumes processing.

2. The TLI interrupt is the logic OR between TIM2 overflow interrupt, and TIM4 overflow interrupts.

3. The device is woken up from Halt or Active-halt mode only when the address received matches the interface address.

# 8 Unique ID

STM8 devices feature a 96-bit unique device identifier which provides a reference number that is unique for any device and in any context. The 96 bits of the identifier can never be altered by the user.

The unique device identifier can be read in single bytes and may then be concatenated using a custom algorithm.

The unique device identifier is ideally suited:

- For use as serial numbers

- For use as security keys to increase the code security in the program memory while using and combining this unique ID with software cryptographic primitives and protocols before programming the internal memory.

- To activate secure boot processes

| Address | Content          |                            | Unique ID bits |   |      |          |   |   |   |  |

|---------|------------------|----------------------------|----------------|---|------|----------|---|---|---|--|

| Address | description      | 7                          | 6              | 5 | 4    | 3        | 2 | 1 | 0 |  |

| 0x4926  | X co-ordinate on | U_ID[7:0]                  |                |   |      |          |   |   |   |  |

| 0x4927  | the wafer        | U_ID[15:8]                 |                |   |      |          |   |   |   |  |

| 0x4928  | Y co-ordinate on |                            | U_ID[23:16]    |   |      |          |   |   |   |  |

| 0x4929  | the wafer        | U_ID[31:24]                |                |   |      |          |   |   |   |  |

| 0x492A  | Wafer number     | U_ID[39:32]                |                |   |      |          |   |   |   |  |

| 0x492B  |                  | U_ID[47:40]<br>U_ID[55:48] |                |   |      |          |   |   |   |  |

| 0x492C  |                  |                            |                |   |      |          |   |   |   |  |

| 0x492D  | -                | U_ID[63:56]<br>U_ID[71:64] |                |   |      |          |   |   |   |  |

| 0x492E  | Lot number       |                            |                |   |      |          |   |   |   |  |

| 0x492F  |                  | U_ID[79:72]<br>U_ID[87:80] |                |   |      |          |   |   |   |  |

| 0x4930  |                  |                            |                |   |      |          |   |   |   |  |

| 0x4931  |                  |                            |                |   | U_II | D[95:88] |   |   |   |  |

### Table 13. Unique ID registers (96 bits)

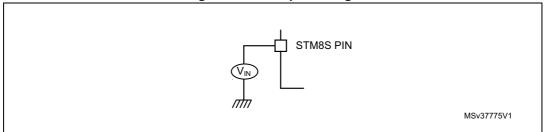

## 9.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 10.

## 9.2 Absolute maximum ratings

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                                                     | Min                                                                     | Max                   | Unit |  |  |

|-----------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------|------|--|--|

| V <sub>DD</sub> - V <sub>SS</sub> | External supply voltage (including $V_{DD}, V_{DDA},$ and $V_{DDIO})^{(1)}$ | - 0.3                                                                   | 4.0                   | V    |  |  |

| V <sub>IN</sub> <sup>(2)</sup>    | Input voltage on true open-drain pins (PC0 and PC1)                         | V <sub>ss</sub> - 0.3                                                   | V <sub>DD</sub> + 4.0 | V    |  |  |

|                                   | Input voltage on any other pin                                              | V <sub>ss</sub> - 0.3                                                   | 4.0                   |      |  |  |

| V <sub>ESD</sub>                  | Electrostatic discharge voltage                                             | see Absolute maximum<br>ratings (electrical sensitivity)<br>on page 102 |                       |      |  |  |

1. All power (V<sub>DD</sub>, V<sub>DDA</sub>, V<sub>DDIO</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>, V<sub>SSIO</sub>) pins must always be connected to the external power supply.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 15.* for maximum allowed injected current values.

Figure 11. POR/BOR thresholds

## 9.3.3 Supply current characteristics

## **Total current consumption**

The MCU is placed under the following conditions:

- I All I/O pins in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- All peripherals are disabled except if explicitly mentioned.

In the following table, data is based on characterization results, unless otherwise specified. Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$ .

In the following table, data is based on characterization results, unless otherwise specified.

|                       |                                   | Conditions <sup>(1)</sup>                                                                                                              |                                                            |                                     | Мах   |              |               |               |             |    |

|-----------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------|-------|--------------|---------------|---------------|-------------|----|

| Symbol                | Parameter                         |                                                                                                                                        |                                                            | Тур                                 | 55°C  | 85 °C        | 105 °C<br>(2) | 125 °C<br>(2) | Unit        |    |

|                       |                                   |                                                                                                                                        |                                                            | f <sub>CPU</sub> = 125 kHz          | 0.33  | 0.39         | 0.41          | 0.43          | 0.45        |    |

|                       |                                   |                                                                                                                                        |                                                            | f <sub>CPU</sub> = 1 MHz            | 0.35  | 0.41         | 0.44          | 0.45          | 0.48        | mA |

|                       |                                   |                                                                                                                                        | HSI                                                        | f <sub>CPU</sub> = 4 MHz            |       | 0.51         | 0.52          | 0.54          | 0.58        |    |

|                       |                                   |                                                                                                                                        |                                                            | f <sub>CPU</sub> = 8 MHz            |       | 0.57         | 0.58          | 0.59          | 0.62        |    |

|                       |                                   | CPU not<br>clocked,<br>all peripherals<br>OFF,<br>code executed<br>from RAM<br>with Flash in<br>I <sub>DDQ</sub> mode <sup>(3)</sup> , |                                                            | f <sub>CPU</sub> = 16 MHz           | 0.68  | 0.76         | 0.76 0.79     | 0.82<br>(5)   | 0.85<br>(5) |    |

|                       | Supply<br>current in<br>Wait mode |                                                                                                                                        | f <sub>CPU</sub> = 128                                     | f <sub>CPU</sub> = 125 kHz          | 0.032 | 0.056        | 0.068         | 0.072         | 0.093       |    |

|                       |                                   |                                                                                                                                        | HSE external                                               | f <sub>CPU</sub> = 1 MHz            | 0.078 | 0.121        | 0.144         | 0.163         | 0.197       |    |

| I <sub>DD(Wait)</sub> |                                   |                                                                                                                                        | clock                                                      | f <sub>CPU</sub> = 4 MHz            | 0.218 | 0.26         | 0.30          | 0.36          | 0.40        |    |

|                       |                                   |                                                                                                                                        | (f <sub>CPU</sub> =f <sub>HSE</sub> )<br>(4)               | f <sub>CPU</sub> = 8 MHz C          | 0.40  | 0.52         | 0.57          | 0.62          | 0.66        |    |

|                       |                                   | V <sub>DD</sub> from<br>1.65 V to 3.6 V                                                                                                |                                                            | f <sub>CPU</sub> = 16 MHz           | 0.760 | 60 1.01 1.05 | 1.05          | 1.09<br>(5)   | 1.16<br>(5) |    |

|                       |                                   |                                                                                                                                        | LSI $f_{CPU} = f_{LSI}$ 0.035 0.                           | 0.044                               | 0.046 | 0.049        | 0.054         |               |             |    |

|                       |                                   |                                                                                                                                        | LSE <sup>(6)</sup><br>external<br>clock<br>(32.768<br>kHz) | f <sub>CPU</sub> = f <sub>LSE</sub> | 0.032 | 0.036        | 0.038         | 0.044         | 0.051       |    |

Table 20. Total current consumption in Wait mode

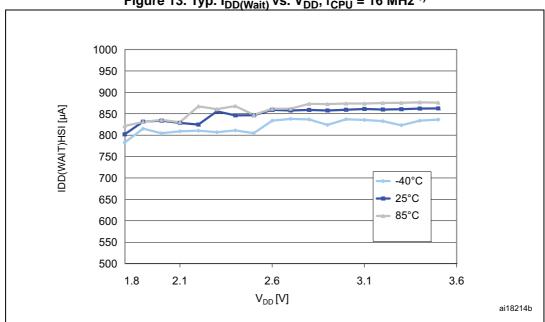

Figure 13. Typ.  $I_{DD(Wait)}$  vs.  $V_{DD}$ ,  $f_{CPU}$  = 16 MHz <sup>1)</sup>

1. Typical current consumption measured with code executed from Flash memory.

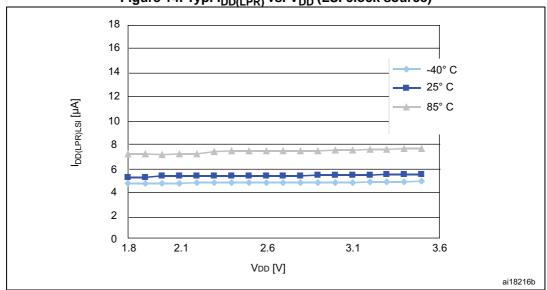

Figure 14. Typ. I<sub>DD(LPR)</sub> vs. V<sub>DD</sub> (LSI clock source)

## NRST pin

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                | Parameter                                    | Conditions                                                  | Min                       | Тур | Max             | Unit |

|-----------------------|----------------------------------------------|-------------------------------------------------------------|---------------------------|-----|-----------------|------|

| V <sub>IL(NRST)</sub> | NRST input low level voltage <sup>(1)</sup>  | -                                                           | V <sub>SS</sub>           | -   | 0.8             |      |

| V <sub>IH(NRST)</sub> | NRST input high level voltage (1)            | -                                                           | 1.4                       | -   | V <sub>DD</sub> |      |

| V <sub>OL(NRST)</sub> | NRST output low level voltage <sup>(1)</sup> | $I_{OL} = 2 \text{ mA}$<br>for 2.7 V $\leq V_{DD} \leq 3.6$ |                           | 0.4 | V               |      |

|                       | ·····e································       | $I_{OL}$ = 1.5 mA<br>for V <sub>DD</sub> < 2.7 V            | -                         | -   |                 |      |

| V <sub>HYST</sub>     | NRST input hysteresis <sup>(3)</sup>         | -                                                           | 10%V <sub>DD</sub><br>(2) | -   | -               | mV   |

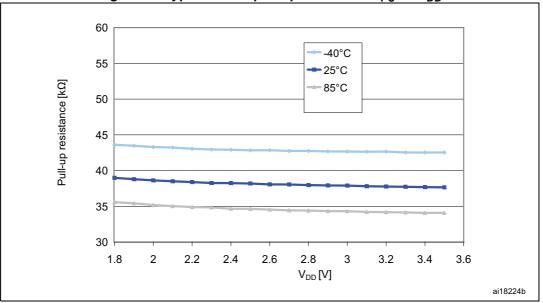

| R <sub>PU(NRST)</sub> | NRST pull-up equivalent resistor             | -                                                           | 30                        | 45  | 60              | kΩ   |

| V <sub>F(NRST)</sub>  | NRST input filtered pulse (3)                | -                                                           | -                         | -   | 50              | ns   |

| V <sub>NF(NRST)</sub> | NRST input not filtered pulse <sup>(3)</sup> | -                                                           | 300                       | -   | -               | 115  |

| Table 41 | NRST | nin | characteristics |

|----------|------|-----|-----------------|

|          |      | P   |                 |

1. Data based on characterization results, not tested in production.

2. 200 mV min.

3. Data guaranteed by design, not tested in production.

## Figure 30. Typical NRST pull-up resistance R<sub>PU</sub> vs V<sub>DD</sub>

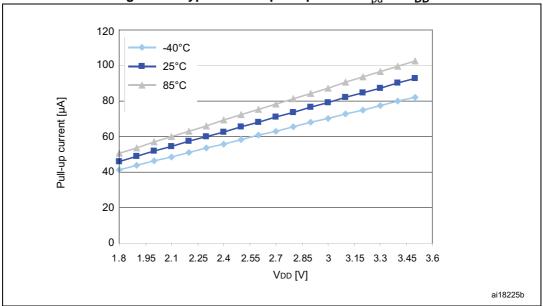

Figure 31. Typical NRST pull-up current I<sub>pu</sub> vs V<sub>DD</sub>

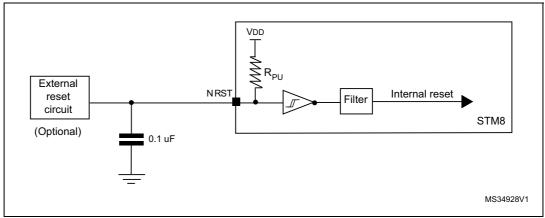

The reset network shown in *Figure 32* protects the device against parasitic resets. The user must ensure that the level on the NRST pin can go below the  $V_{IL(NRST)}$  max. level specified in *Table 41*. Otherwise the reset is not taken into account internally.

For power consumption sensitive applications, the external reset capacitor value can be reduced to limit the charge/discharge current. If the NRST signal is used to reset the external circuitry, attention must be paid to the charge/discharge time of the external capacitor to fulfill the external devices reset timing conditions. The minimum recommended capacity is 10 nF.

Figure 32. Recommended NRST pin configuration

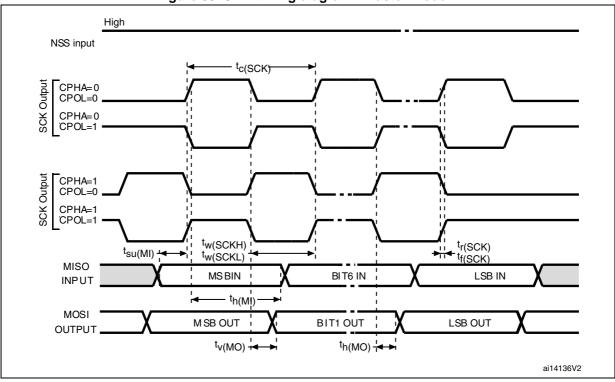

Figure 35. SPI1 timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}.$

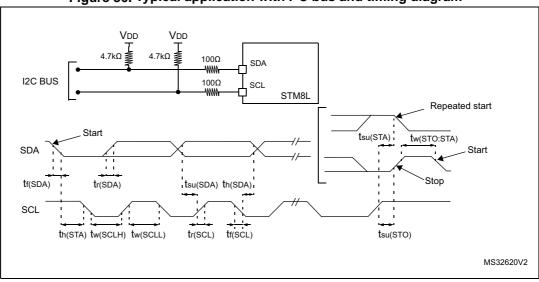

Figure 36. Typical application with I<sup>2</sup>C bus and timing diagram<sup>1)</sup>

1. Measurement points are done at CMOS levels: 0.3 x  $\rm V_{DD}$  and 0.7 x  $\rm V_{DD}$

In the following three tables, data is guaranteed by characterization result, not tested in production.

| Symbol | Parameter                  | Conditions                 | Тур | Max | Unit  |

|--------|----------------------------|----------------------------|-----|-----|-------|

|        |                            | f <sub>ADC1</sub> = 16 MHz | 1   | 1.6 |       |

| DNL    | Differential non linearity | f <sub>ADC1</sub> = 8 MHz  | 1   | 1.6 | 1     |

|        |                            | f <sub>ADC1</sub> = 4 MHz  | 1   | 1.5 | 1     |

|        |                            | f <sub>ADC1</sub> = 16 MHz | 1.2 | 2   | ]     |

| INL    | Integral non linearity     | f <sub>ADC1</sub> = 8 MHz  | 1.2 | 1.8 | LSB   |

|        |                            | f <sub>ADC1</sub> = 4 MHz  | 1.2 | 1.7 | ]     |

|        | Total unadjusted error     | f <sub>ADC1</sub> = 16 MHz | 2.2 | 3.0 | ]     |

| TUE    |                            | f <sub>ADC1</sub> = 8 MHz  | 1.8 | 2.5 |       |

|        |                            | f <sub>ADC1</sub> = 4 MHz  | 1.8 | 2.3 | ]     |

|        |                            | f <sub>ADC1</sub> = 16 MHz | 1.5 | 2   |       |

| Offset | Offset error               | f <sub>ADC1</sub> = 8 MHz  | 1   | 1.5 | ]     |

|        |                            | f <sub>ADC1</sub> = 4 MHz  | 0.7 | 1.2 | - LSB |

|        |                            | f <sub>ADC1</sub> = 16 MHz |     |     |       |

| Gain   | Gain error                 | f <sub>ADC1</sub> = 8 MHz  | 1   | 1.5 |       |

|        |                            | f <sub>ADC1</sub> = 4 MHz  |     |     |       |

Table 49. ADC1 accuracy with  $V_{DDA} = 3.3$  V to 2.5 V

| Symbol | Parameter                  | Тур | Max | Unit |

|--------|----------------------------|-----|-----|------|

| DNL    | Differential non linearity | 1   | 2   | LSB  |

| INL    | Integral non linearity     | 1.7 | 3   | LSB  |

| TUE    | TUE Total unadjusted error |     | 4   | LSB  |

| Offset | Offset error               | 1   | 2   | LSB  |

| Gain   | Gain error                 | 1.5 | 3   | LSB  |

| Table 51. ADC1 accuracy with V <sub>DDA</sub> = V <sub>REF</sub> <sup>+</sup> = 1.8 V to 2.4 | V |

|----------------------------------------------------------------------------------------------|---|

|----------------------------------------------------------------------------------------------|---|

| Symbol                     | Parameter                  |   | Max | Unit |

|----------------------------|----------------------------|---|-----|------|

| DNL                        | Differential non linearity | 1 | 2   | LSB  |

| INL Integral non linearity |                            | 2 | 3   | LSB  |

| TUE                        | Total unadjusted error     | 3 | 5   | LSB  |

| Offset                     | Offset error               | 2 | 3   | LSB  |

| Gain Gain error            |                            | 2 | 3   | LSB  |

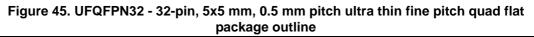

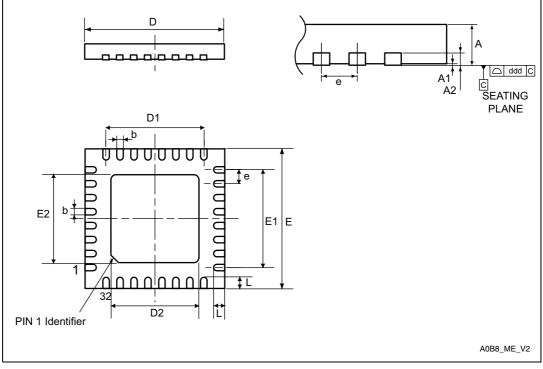

# 10.3 UFQFPN32 package information

<sup>1.</sup> Drawing is not to scale.

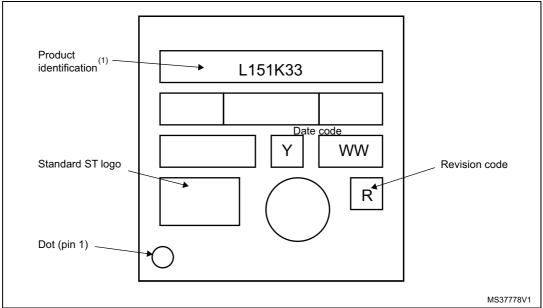

## **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

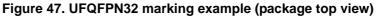

# 10.4 UFQFPN28 package information

Figure 48. UFQFPN28 - 28-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat package outline

1. Drawing is not to scale.

| Table 59. UFQFPN28 - 28-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |

|-------------------------------------------------------------------------------------|

| package mechanical data <sup>(1)</sup>                                              |

| Cumhal |       | millimeters |       |        | inches |        |

|--------|-------|-------------|-------|--------|--------|--------|

| Symbol | Min   | Тур         | Max   | Min    | Тур    | Мах    |

| А      | 0.500 | 0.550       | 0.600 | 0.0197 | 0.0217 | 0.0236 |

| A1     | -     | 0.000       | 0.050 | -      | 0.0000 | 0.0020 |

| D      | 3.900 | 4.000       | 4.100 | 0.1535 | 0.1575 | 0.1614 |

| D1     | 2.900 | 3.000       | 3.100 | 0.1142 | 0.1181 | 0.1220 |

| Е      | 3.900 | 4.000       | 4.100 | 0.1535 | 0.1575 | 0.1614 |

| E1     | 2.900 | 3.000       | 3.100 | 0.1142 | 0.1181 | 0.1220 |

| L      | 0.300 | 0.400       | 0.500 | 0.0118 | 0.0157 | 0.0197 |

| L1     | 0.250 | 0.350       | 0.450 | 0.0098 | 0.0138 | 0.0177 |

| Т      | -     | 0.152       | -     | -      | 0.0060 | -      |

| b      | 0.200 | 0.250       | 0.300 | 0.0079 | 0.0098 | 0.0118 |

| е      | -     | 0.500       | -     | -      | 0.0197 | -      |

DocID018780 Rev 8