Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | STM8                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, IR, POR, PWM, WDT                         |

| Number of I/O              | 26                                                                     |

| Program Memory Size        | 8KB (8K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 256 x 8                                                                |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

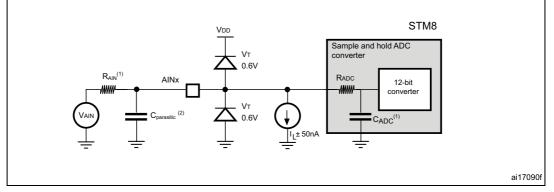

| Data Converters            | A/D 18x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 28-UFQFN                                                               |

| Supplier Device Package    | 28-UFQFPN (4x4)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8l151g3u6tr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    |        | 9.3.11   | Comparator characteristics93  |

|----|--------|----------|-------------------------------|

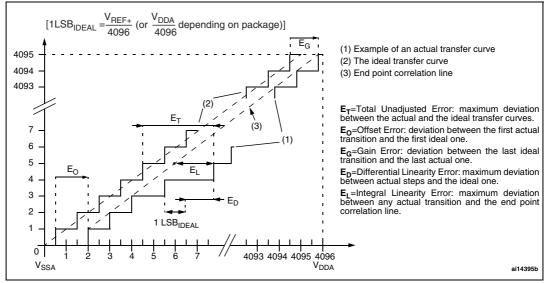

|    |        | 9.3.12   | 12-bit ADC1 characteristics95 |

|    |        | 9.3.13   | EMC characteristics           |

| 10 | Packa  | age info | rmation                       |

|    | 10.1   | ECOPA    | СК 103                        |

|    | 10.2   | LQFP48   | 3 package information         |

|    | 10.3   | UFQFP    | N32 package information 106   |

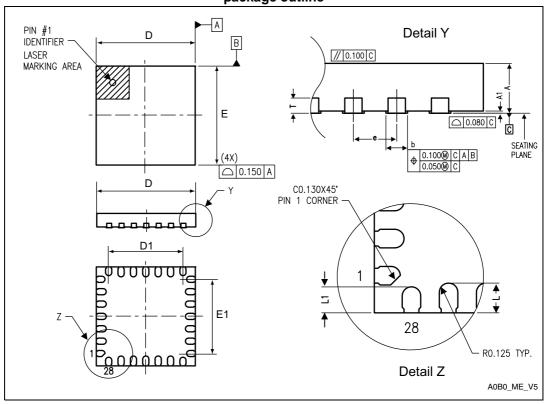

|    | 10.4   | UFQFP    | N28 package information 109   |

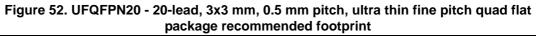

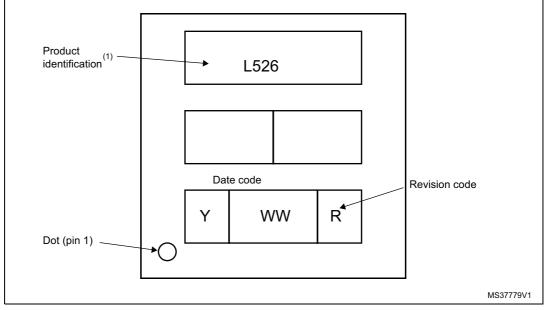

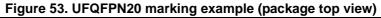

|    | 10.5   | UFQFP    | N20 package information112    |

|    | 10.6   | TSSOP    | 20 package information115     |

|    | 10.7   | Therma   | I characteristics             |

| 11 | Part r | numberi  | ng 119                        |

| 12 | Revis  | ion hist | ory                           |

## 3.1 Low-power modes

The low-density STM8L151x2/3 devices support five low power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

- Wait mode: The CPU clock is stopped, but selected peripherals keep running. An internal or external interrupt or a Reset can be used to exit the microcontroller from Wait mode (WFE or WFI mode). Wait consumption: refer to *Table 20*.

- Low power run mode: The CPU and the selected peripherals are running. Execution is done from RAM with a low speed oscillator (LSI or LSE). Flash and data EEPROM are stopped and the voltage regulator is configured in ultra-low-power mode. The microcontroller enters Low power run mode by software and can exit from this mode by software or by a reset.

All interrupts must be masked. They cannot be used to exit the microcontroller from this mode. Low power run mode consumption: refer to *Table 21*.

- Low power wait mode: This mode is entered when executing a Wait for event in Low power run mode. It is similar to Low power run mode except that the CPU clock is stopped. The wakeup from this mode is triggered by a Reset or by an internal or external event (peripheral event generated by the timers, serial interfaces, DMA controller (DMA1), comparators and I/O ports). When the wakeup is triggered by an event, the system goes back to Low power run mode. All interrupts must be masked. They cannot be used to exit the microcontroller from this mode. Low power wait mode consumption: refer to Table 22.

- Active-halt mode: CPU and peripheral clocks are stopped, except RTC. The wakeup can be triggered by RTC interrupts, external interrupts or reset. Active-halt consumption: refer to *Table 23* and *Table 24*.

- Halt mode: CPU and peripheral clocks are stopped, the device remains powered on. The RAM content is preserved. The wakeup is triggered by an external interrupt or reset. A few peripherals have also a wakeup from Halt capability. Switching off the internal reference voltage reduces power consumption. Through software configuration it is also possible to wake up the device without waiting for the internal reference voltage wakeup time to have a fast wakeup time of 5 µs. Halt consumption: refer to *Table 25*.

## 3.2 Central processing unit STM8

## 3.2.1 Advanced STM8 Core

The 8-bit STM8 core is designed for code efficiency and performance with an Harvard architecture and a 3-stage pipeline.

It contains 6 internal registers which are directly addressable in each execution context, 20 addressing modes including indexed indirect and relative addressing, and 80 instructions.

### Architecture and registers

- Harvard architecture

- 3-stage pipeline

- 32-bit wide program memory bus single cycle fetching most instructions

- X and Y 16-bit index registers enabling indexed addressing modes with or without offset and read-modify-write type data manipulations

- 8-bit accumulator

- 24-bit program counter 16 Mbyte linear memory space

- 16-bit stack pointer access to a 64 Kbyte level stack

- 8-bit condition code register 7 condition flags for the result of the last instruction

### Addressing

- 20 addressing modes

- Indexed indirect addressing mode for lookup tables located anywhere in the address space

- Stack pointer relative addressing mode for local variables and parameter passing

### Instruction set

- 80 instructions with 2-byte average instruction size

- Standard data movement and logic/arithmetic functions

- 8-bit by 8-bit multiplication

- 16-bit by 8-bit and 16-bit by 16-bit division

- Bit manipulation

- Data transfer between stack and accumulator (push/pop) with direct stack access

- Data transfer using the X and Y registers or direct memory-to-memory transfers

### 3.2.2 Interrupt controller

The low-density STM8L151x2/3 feature a nested vectored interrupt controller:

- Nested interrupts with 3 software priority levels

- 32 interrupt vectors with hardware priority

- Up to 40 external interrupt sources on 11 vectors

- Trap and reset interrupts

## 3.15 Communication interfaces

### 3.15.1 SPI

The serial peripheral interface (SPI1) provides half/ full duplex synchronous serial communication with external devices.

- Maximum speed: 8 Mbit/s (f<sub>SYSCLK</sub>/2) both for master and slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on 2 lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- Hardware CRC calculation

- Slave/master selection input pin

Note: SPI1 can be served by the DMA1 Controller.

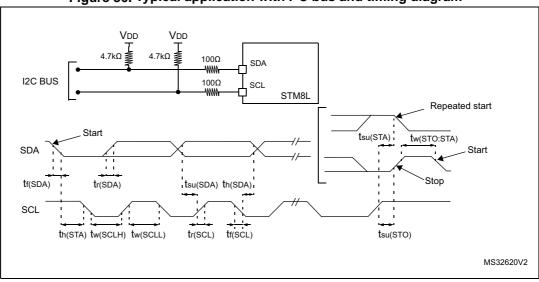

## 3.15.2 I<sup>2</sup>C

The I<sup>2</sup>C bus interface (I<sup>2</sup>C1) provides multi-master capability, and controls all I<sup>2</sup>C busspecific sequencing, protocol, arbitration and timing.

- Master, slave and multi-master capability

- Standard mode up to 100 kHz and fast speed modes up to 400 kHz.

- 7-bit and 10-bit addressing modes.

- SMBus 2.0 and PMBus support

- Hardware CRC calculation

Note:  $l^2C1$  can be served by the DMA1 Controller.

## 3.15.3 USART

The USART interface (USART1) allows full duplex, asynchronous communications with external devices requiring an industry standard NRZ asynchronous serial data format. It offers a very wide range of baud rates.

- 1 Mbit/s full duplex SCI

- SPI1 emulation

- High precision baud rate generator

- SmartCard emulation

- IrDA SIR encoder decoder

- Single wire half duplex mode

Note: USART1 can be served by the DMA1 Controller.

## 3.16 Infrared (IR) interface

The low-density STM8L151x2/3 devices contain an infrared interface which can be used with an IR LED for remote control functions. Two timer output compare channels are used to generate the infrared remote control signals.

| 0x00 5140         RTC_TR1         RTC time register 1         0x00           0x00 5141         RTC_TR2         RTC time register 2         0x00           0x00 5143         RTC_TR3         RTC time register 3         0x00           0x00 5144         RTC_DR1         RTC date register 1         0x01           0x00 5145         RTC_DR2         RTC date register 3         0x00           0x00 5146         RTC_DR3         RTC date register 3         0x00           0x00 5147         RTC_CR1         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5148         RTC_CR2         RTC control register 1         0x01 <sup>(2)</sup> 0x00 5140         RTC_CR3         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5141         RTC_ISR1         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5142         RTC_ISR1         RTC control register 1         0x01 <sup>(2)</sup> 0x00 5141         RTC_ISR1         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5141         RTC_ISR1         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5150         RTC_SPRERL         RTC synchronous prescaler register 1         0x00 <sup>(2)</sup> 0x00 5151         RTC_SPRERL         RTC synchronous prescaler register 1         0x7F <sup>(2)</sup>                                   | Address   | Block | Register label              | Register name                              | Reset status        |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|-----------------------------|--------------------------------------------|---------------------|--|--|

| 0x00 5142         RTC_TR3         RTC time register 3         0x00           0x00 5143         RtC_DR1         Reserved area (1 byte)         0x01           0x00 5145         RTC_DR1         RTC date register 1         0x01           0x00 5145         RTC_DR2         RTC date register 3         0x00           0x00 5146         RTC_DR3         RTC date register 1         0x00 <sup>(2)</sup> 0x00 5147         RTC_CR1         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5148         RTC_CR2         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5140         RTC_CR3         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5140         RTC_ISR1         RTC initialization and status register 1         0x01           0x00 5140         RTC_ISR1         RTC initialization and status register 1         0x01           0x00 5141         RTC_ISR2         RTC initialization and status register 1         0x01           0x00 5151         RTC_SPRERH         RTC synchronous prescaler register low         0xF <sup>(2)</sup> 0x00 5152         RTC_WUTRH         RTC subsecond register low         0xF <sup>(2)</sup> 0x00 5153         RTC_SRE         RTC subsecond register low         0xF <sup>(2)</sup> 0x00 5156         RTC_SRL         RTC                                    | 0x00 5140 |       | RTC_TR1                     | RTC time register 1                        | 0x00                |  |  |

| 0x00 5143         Reserved area (1 byte)           0x00 5144         RTC_DR1         RTC date register 1         0x01           0x00 5145         RTC_DR2         RTC date register 2         0x21           0x00 5146         RTC_DR3         RTC date register 3         0x00           0x00 5147         RTC_CR1         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5148         RTC_CR2         RTC control register 2         0x00 <sup>(2)</sup> 0x00 5140         RTC_CR3         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5141         RTC_ISR1         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5142         RTC_ISR1         RTC initialization and status register 1         0x01           0x00 5145         RTC_SPRERH         RTC synchronous prescaler register 1         0x00           0x00 5151         RTC_SPRERL         RTC synchronous prescaler register 1         0x71 <sup>(2)</sup> 0x00 5153         RTC_WUTRH         RTC subsecond register 1         0x00           0x00 5156         RTC_SRE         RTC subsecond register 1         0x00           0x00 5158         RTC_WUTRH         RTC subsecond register 1         0x00           0x00 5158         RTC_SRE         RTC write protection register         0x00                                                    | 0x00 5141 |       | RTC_TR2                     | RTC time register 2                        | 0x00                |  |  |

| 0x00 5144         RTC_DR1         RTC date register 1         0x01           0x00 5145         RTC_DR2         RTC date register 2         0x21           0x00 5146         RTC_DR3         RTC date register 3         0x00           0x00 5147         RTC_CR1         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5148         RTC_CR2         RTC control register 2         0x00 <sup>(2)</sup> 0x00 5144         RTC_CR3         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5148         RTC_ISR1         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5140         RTC_ISR1         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5141         RTC_ISR2         RTC initialization and status register 1         0x01           0x00 5140         RTC_SPRERH         RTC synchronous prescaler register 1         0x00           0x00 5151         RTC_SPRERL         RTC synchronous prescaler register 10w         0xF <sup>(2)</sup> 0x00 5153         RTC_WUTRH         RTC wakeup timer register 10w         0xF <sup>(2)</sup> 0x00 5154         RTC_WUTRH         RTC subsecond register low         0xF <sup>(2)</sup> 0x00 5155         RTC_SRH         RTC subsecond register low         0x00           0x00 5155         RTC_SRH         RTC s                                    | 0x00 5142 |       | RTC_TR3                     | RTC time register 3                        | 0x00                |  |  |

| 0x00 5145         RTC_DR2         RTC date register 2         0x21           0x00 5146         RTC_DR3         RTC date register 3         0x00           0x00 5147         RTC_CR1         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5148         RTC_CR2         RTC control register 2         0x00 <sup>(2)</sup> 0x00 5149         RTC_CR3         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5140         RTC_CR3         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5141         RTC_ISR1         RTC initialization and status register 1         0x01           0x00 5142         RTC_ISR2         RTC initialization and status register 2         0x00           0x00 5141         RTC_ISR2         RTC initialization and status register 1         0x01           0x00 5145         RTC_SPRERH         RTC synchronous prescaler register 1         0x00 <sup>(2)</sup> 0x00 5150         RTC_APRER         RTC asynchronous prescaler register 10w         0xFf <sup>(2)</sup> 0x00 5151         RTC_WUTRH         RTC wakeup timer register 10w         0xFf <sup>(2)</sup> 0x00 5155         RTC_WUTRL         RTC subsecond register high         0x00           0x00 5156         RTC_SRH         RTC subsecond register high         0x00           0x00 5157                           | 0x00 5143 | _     |                             | Reserved area (1 byte)                     |                     |  |  |

| Ox00 5146         RTC_DR3         RTC date register 3         0x00           0x00 5147         0x00 5147         Reserved area (1 byte)         0x00 5148           0x00 5148         RTC_CR1         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5144         RTC_CR2         RTC control register 2         0x00 <sup>(2)</sup> 0x00 5144         RTC_CR3         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5145         RTC_ISR1         RTC initialization and status register 1         0x01           0x00 5146         RTC_SPRERH         RTC synchronous prescaler register 1         0x00 <sup>(2)</sup> 0x00 5150         RTC_SPRERL         RTC synchronous prescaler register 0x         0xFF <sup>(2)</sup> 0x00 5152         RTC_MUTRH         RTC wakeup timer register low         0xFF <sup>(2)</sup> 0x00 5155         RTC_WUTRL         RTC wakeup timer register low         0xFF <sup>(2)</sup> 0x00 5156         RTC_SSRL         RTC subsecond register low         0x00           0x00 5157         RTC_SSRH         RTC subsecond register low         0x00           0x00 5158         RTC_SSRH         RTC subsecond register low         0x00           0x00 5159         RTC_SSRH         RTC write protection register         0x00           0x00 5156                                    | 0x00 5144 |       | RTC_DR1 RTC date register 1 |                                            | 0x01                |  |  |

| Ox00 5147         Reserved area (1 byte)           0x00 5148         RTC_CR1         RTC control register 1         0x00 <sup>(2)</sup> 0x00 5149         RTC_CR2         RTC control register 2         0x00 <sup>(2)</sup> 0x00 5144         RTC_CR3         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5144         RTC_ISR1         RTC control register 3         0x00 <sup>(2)</sup> 0x00 5144         RTC_ISR1         RTC initialization and status register 1         0x01           0x00 5144         RTC_ISR2         RTC initialization and status register 1         0x01           0x00 5146         RTC_SPRERH         RTC synchronous prescaler register 1         0x00 <sup>(2)</sup> 0x00 5151         RTC_SPRERL         RTC synchronous prescaler register 1         0x01 <sup>(2)</sup> 0x00 5153         RTC_MUTRH         RTC wakeup timer register low         0xFF <sup>(2)</sup> 0x00 5154         RTC_WUTRL         RTC wakeup timer register low         0x0F <sup>(2)</sup> 0x00 5155         RTC_SSRL         RTC subsecond register low         0x00           0x00 5156         RTC_SSRH         RTC subsecond register low         0x00           0x00 5157         RTC_SSRH         RTC subsecond register low         0x00           0x00 5158         RTC_SSRH         RTC write                  | 0x00 5145 |       | RTC_DR2                     | 0x21                                       |                     |  |  |

| 0x00 5148RTC_CR1RTC control register 10x00 <sup>(2)</sup> 0x00 5149RTC_CR2RTC control register 20x00 <sup>(2)</sup> 0x00 5144RTC_CR3RTC control register 30x00 <sup>(2)</sup> 0x00 5146RTC_ISR1RTC initialization and status register 10x010x00 5140RTC_ISR2RTC initialization and Status register 20x000x00 5147RTC_SPRERHRTC synchronous prescaler register high0x00 <sup>(2)</sup> 0x00 5151RTC_SPRERLRTC synchronous prescaler register 10x01 <sup>(2)</sup> 0x00 5153RTC_APRERRTC synchronous prescaler register 10x7F <sup>(2)</sup> 0x00 5154RTC_WUTRHRTC synchronous prescaler register 10x7F <sup>(2)</sup> 0x00 5155RTC_WUTRHRTC wakeup timer register high0xFF <sup>(2)</sup> 0x00 5156RTC_SRLRTC synchronous prescaler register 10x000x00 5157RTC_SRLRTC subsecond register high0x000x00 5158RTC_SRHRTC subsecond register low0x000x00 5159RTC_SRHRTC subsecond register high0x000x00 5159RTC_SRHRTC subsecond register high0x000x00 5158RTC_SHIFTRHRTC shift register low0x000x00 5158RTC_ALRMAR1RTC shift register 10x00 <sup>(2)</sup> 0x00 5150RTC_ALRMAR3RTC alarm A register 30x00 <sup>(2)</sup>                                                                                                                                                                                                                                | 0x00 5146 |       | RTC_DR3                     | RTC date register 3                        | 0x00                |  |  |

| 0x00 5149RTC_CR2RTC control register 20x00 <sup>(2)</sup> 0x00 514ARTC_CR3RTC control register 30x00 <sup>(2)</sup> 0x00 514BRTC_ISR1RTC initialization and status register 10x010x00 514CRTC_ISR2RTC initialization and status register 10x010x00 514DRTC_ISR2RTC initialization and status register 20x000x00 514ERTC_SPRERHRTC synchronous prescaler register high0x00 <sup>(2)</sup> 0x00 5150RTC_SPRERHRTC synchronous prescaler register low0xFF <sup>(2)</sup> 0x00 5152RTC_APRERRTC asynchronous prescaler register low0xFF <sup>(2)</sup> 0x00 5153RTC_WUTRHRTC wakeup timer register high0xFF <sup>(2)</sup> 0x00 5156RTC_WUTRHRTC subsecond register low0xFF <sup>(2)</sup> 0x00 5157RTC_SSRHRTC subsecond register low0x000x00 5158RTC_WPRRTC write protection register0x000x00 5158RTC_WPRRTC write protection register0x000x00 5158RTC_SHIFTRHRTC subsecond register high0x000x00 5158RTC_SHIFTRHRTC shift register high0x000x00 5155RTC_ALRMAR1RTC shift register 10x00 <sup>(2)</sup> 0x00 5150RTC_ALRMAR3RTC alarm A register 20x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                | 0x00 5147 |       |                             | Reserved area (1 byte)                     | 1                   |  |  |

| Ox00 514ARTC_CR3RTC control register 3Ox00 <sup>(2)</sup> 0x00 514BRTC_ISR1RTC initialization and status register 10x010x00 514CRTC_ISR2RTC initialization and status register 10x010x00 514DRTC_ISR2RTC initialization and Status register 20x000x00 514ERTC_SPRERHRTC synchronous prescaler register high0x00 <sup>(2)</sup> 0x00 5150RTC_SPRERLRTC synchronous prescaler register low0xFF <sup>(2)</sup> 0x00 5152RTC_APRERRTC asynchronous prescaler register low0xFF <sup>(2)</sup> 0x00 5153RTC_WUTRHRTC wakeup timer register low0xFF <sup>(2)</sup> 0x00 5156RTC_WUTRHRTC wakeup timer register low0xFF <sup>(2)</sup> 0x00 5156RTC_SRLRTC subsecond register low0xFF <sup>(2)</sup> 0x00 5158RTC_SRHRTC subsecond register low0x000x00 5158RTC_SRHRTC subsecond register low0x000x00 5158RTC_SRHRTC subsecond register high0x000x00 5158RTC_SRHRTC subsecond register high0x000x00 5158RTC_SRHRTC subsecond register high0x000x00 5158RTC_SRHRTC subsecond register high0x000x00 5156RTC_SHIFTRHRTC subsecond register high0x000x00 5158RTC_SHIFTRHRTC subsecond register high0x000x00 5156RTC_SHIFTRHRTC subsecond register high0x000x00 5156RTC_SHIFTRHRTC subsecond register high0x000x00 5156RTC_ALRMAR1RTC alarm A regi                                                                                                              | 0x00 5148 | _     | RTC_CR1                     | RTC control register 1                     | 0x00 <sup>(2)</sup> |  |  |

| Ox00 514B         Reserved area (1 byte)           0x00 514C         RTC_ISR1         RTC initialization and status register 1         0x01           0x00 514D         RTC_ISR2         RTC initialization and Status register 2         0x00           0x00 514E         RTC_ISR2         RTC initialization and Status register 2         0x00           0x00 514E         RTC_SPRERH         RTC synchronous prescaler register high         0x00 <sup>(2)</sup> 0x00 5150         RTC_SPRERL         RTC synchronous prescaler register low         0xFF <sup>(2)</sup> 0x00 5152         RTC_APRER         RTC asynchronous prescaler register high         0xFF <sup>(2)</sup> 0x00 5153         RTC_WUTRH         RTC wakeup timer register low         0xFF <sup>(2)</sup> 0x00 5156         RTC_SSRL         RTC subsecond register low         0xFF <sup>(2)</sup> 0x00 5158         RTC_SSRH         RTC subsecond register low         0x00           0x00 5158         RTC_SSRH         RTC subsecond register high         0x00           0x00 5159         RTC_SRH         RTC subsecond register high         0x00           0x00 5158         RTC_SHIFTRH         RTC subsecond register high         0x00           0x00 5158         RTC_SHIFTRH         RTC subsecond register high         0x00           0x00 5155          | 0x00 5149 | _     | RTC_CR2                     | RTC control register 2                     | 0x00 <sup>(2)</sup> |  |  |

| Ox00 514CRTC_ISR1RTC initialization and status register 1Ox010x00 514DRTC_ISR2RTC initialization and Status register 20x000x00 514ERTC_ISR2RTC initialization and Status register 20x000x00 5150RTC_SPRERHRTC synchronous prescaler register high0x00 <sup>(2)</sup> 0x00 5151RTC_SPRERLRTC synchronous prescaler register low0xFF <sup>(2)</sup> 0x00 5152RTC_APRERRTC asynchronous prescaler register low0xFF <sup>(2)</sup> 0x00 5153RTC_WUTRHRTC wakeup timer register low0xFF <sup>(2)</sup> 0x00 5156RTC_WUTRLRTC wakeup timer register low0xFF <sup>(2)</sup> 0x00 5157RTC_SSRLRTC subsecond register low0x000x00 5158RTC_WPRRTC subsecond register low0x000x00 5158RTC_WPRRTC write protection register0x000x00 5156RTC_SSRHRTC subsecond register high0x000x00 5158RTC_SSRHRTC subsecond register low0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5156RTC_SSRHRTC subsecond register low0x000x00 5156RTC_SSRHRTC subsecond register low0x000x00 5156RTC_SSRHRTC subsecond register low0x000x00 5156RTC_SIFTRHRTC write protection register0x000x00 5156RTC_SIFTRHRTC shift register low0x000x00 5155RTC_ALRMAR1RTC alarm A register 10x00 <sup>(2)</sup> 0x00 5155RTC_ALRMAR3RTC alarm A register 3 </td <td>0x00 514A</td> <td></td> <td>RTC_CR3</td> <td>RTC control register 3</td> <td>0x00<sup>(2)</sup></td>            | 0x00 514A |       | RTC_CR3                     | RTC control register 3                     | 0x00 <sup>(2)</sup> |  |  |

| Ox00 514D         RTC_ISR2         RTC initialization and Status register 2         Ox00           0x00 514E         RTC_ISR2         RTC initialization and Status register 2         0x00           0x00 514F         RTC_SPRERH         RTC synchronous prescaler register high         0x00 <sup>(2)</sup> 0x00 5150         RTC_SPRERL         RTC synchronous prescaler register low         0xFF <sup>(2)</sup> 0x00 5152         RTC_APRER         RTC asynchronous prescaler register         0x7F <sup>(2)</sup> 0x00 5153         RTC_WUTRH         RTC wakeup timer register high         0xFF <sup>(2)</sup> 0x00 5156         RTC_WUTRL         RTC wakeup timer register low         0xFF <sup>(2)</sup> 0x00 5156         RTC_SSRL         RTC subsecond register low         0x0F <sup>(2)</sup> 0x00 5156         RTC_SSRH         RTC subsecond register low         0x00           0x00 5158         RTC_WPR         RTC write protection register         0x00           0x00 5158         RTC_SHIFTRH         RTC write protection register         0x00           0x00 5156         RTC_SHIFTRH         RTC shift register high         0x00           0x00 5158         RTC_SHIFTRH         RTC write protection register         0x00           0x00 5156         RTC_SHIFTRH         RTC shift register low         0x00 | 0x00 514B | _     |                             | Reserved area (1 byte)                     |                     |  |  |

| Ox00 514E<br>0x00 514F         Reserved area (2 byte)           0x00 5150         RTC_SPRERH         RTC synchronous prescaler register high         0x00 <sup>(2)</sup> 0x00 5151         RTC_SPRERL         RTC synchronous prescaler register low         0xFF <sup>(2)</sup> 0x00 5152         RTC_APRER         RTC asynchronous prescaler register         0x7F <sup>(2)</sup> 0x00 5153         RTC_WUTRH         RTC wakeup timer register high         0xFF <sup>(2)</sup> 0x00 5155         RTC_WUTRL         RTC wakeup timer register low         0xFF <sup>(2)</sup> 0x00 5156         RTC_WUTRL         RTC subsecond register low         0x00           0x00 5157         RTC_SRH         RTC subsecond register low         0x00           0x00 5158         RTC_SRH         RTC subsecond register high         0x00           0x00 5159         RTC_WURR         RTC subsecond register high         0x00           0x00 5159         RTC_WPR         RTC subsecond register high         0x00           0x00 5156         RTC_WPR         RTC subsecond register high         0x00           0x00 5157         RTC_SHIFTRH         RTC subsecond register high         0x00           0x00 5156         RTC_SHIFTRH         RTC shift register low         0x00           0x00 5155         RTC_ALRMAR1                        | 0x00 514C | _     | RTC_ISR1                    | RTC initialization and status register 1   | 0x01                |  |  |

| Ox00 514F         RTC         RTC_SPRERH         RTC synchronous prescaler register high         0x00 <sup>(2)</sup> 0x00 5150         RTC_SPRERL         RTC synchronous prescaler register low         0xFF <sup>(2)</sup> 0x00 5152         RTC_APRER         RTC asynchronous prescaler register         0x7F <sup>(2)</sup> 0x00 5153         RTC_WUTRH         RTC wakeup timer register high         0xFF <sup>(2)</sup> 0x00 5155         RTC_WUTRL         RTC wakeup timer register low         0xFF <sup>(2)</sup> 0x00 5156         RTC_SSRL         RTC subsecond register low         0xFF <sup>(2)</sup> 0x00 5158         RTC_SSRH         RTC subsecond register low         0x00           0x00 5158         RTC_WPR         RTC write protection register         0x00           0x00 5158         RTC_SSRH         RTC subsecond register high         0x00           0x00 5159         RTC_SSRH         RTC subsecond register high         0x00           0x00 5158         RTC_SSRH         RTC subsecond register high         0x00           0x00 5159         RTC_SSRH         RTC subsecond register high         0x00           0x00 5150         RTC_SHIFTRH         RTC subsecond register high         0x00           0x00 5150         RTC_SHIFTRL         RTC shift register low         0x00                     | 0x00 514D | -     | RTC_ISR2                    | 2 RTC initialization and Status register 2 |                     |  |  |

| NUMBER<br>OX00 5151RTCRTC_SPRERLRTC synchronous prescaler register low0xFF(2)0x00 5152RTC_APRERRTC asynchronous prescaler register0x7F(2)0x00 5153RTC_WUTRHRTC wakeup timer register high0xFF(2)0x00 5154RTC_WUTRHRTC wakeup timer register high0xFF(2)0x00 5155RTC_WUTRLRTC wakeup timer register low0xFF(2)0x00 5156RTC_WUTRLRTC wakeup timer register low0x000x00 5157RTC_SSRLRTC subsecond register low0x000x00 5158RTC_WPRRTC subsecond register high0x000x00 5159RTC_SSRHRTC subsecond register high0x000x00 5159RTC_SSRHRTC subsecond register high0x000x00 5158RTC_SIFTRHRTC subsecond register high0x000x00 5158RTC_SIFTRHRTC subsecond register high0x000x00 5155RTC_SIFTRHRTC subsecond register high0x000x00 5156RTC_SIFTRHRTC subsecond register high0x000x00 5150RTC_ALRMAR1RTC shift register high0x000x00 515DRTC_ALRMAR2RTC alarm A register 10x00(2)0x00 515ERTC_ALRMAR3RTC alarm A register 30x00(2)                                                                                                                                                                                                                                                                                                                                                                                                                            |           |       |                             | Reserved area (2 byte)                     | L                   |  |  |

| DX00 5151RTC_SPRERLRTC synchronous prescaler register 10wDXFF(2)0x00 5152RTC_APRERRTC asynchronous prescaler register0x7F(2)0x00 5153RTC_WUTRHRTC wakeup timer register high0xFF(2)0x00 5155RTC_WUTRLRTC wakeup timer register low0xFF(2)0x00 5156RTC_SSRLRTC subsecond register low0x000x00 5157RTC_SSRHRTC subsecond register low0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_SSRHRTC subsecond register high0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5158RTC_SHIFTRHRTC subsecond register high0x000x00 515ARTC_SHIFTRHRTC shift register high0x000x00 515BRTC_ALRMAR1RTC alarm A register 10x00(2)0x00 515DRTC_ALRMAR3RTC alarm A register 30x00(2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x00 5150 |       | RTC_SPRERH                  | RTC synchronous prescaler register high    | 0x00 <sup>(2)</sup> |  |  |

| Ox00 51530x00 5153RTC_WUTRHRTC wakeup timer register high0xFF <sup>(2)</sup> 0x00 5155RTC_WUTRLRTC wakeup timer register low0xFF <sup>(2)</sup> 0x00 5156RTC_SSRLRTC subsecond register low0x000x00 5157RTC_SSRLRTC subsecond register low0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_SSRHRTC subsecond register high0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5158RTC_SHIFTRHRTC subsecond register high0x000x00 5158RTC_SHIFTRHRTC shift register high0x000x00 5150RTC_ALRMAR1RTC alarm A register 10x00 <sup>(2)</sup> 0x00 515DRTC_ALRMAR3RTC alarm A register 30x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x00 5151 | RTC   | RTC_SPRERL                  | 0xFF <sup>(2)</sup>                        |                     |  |  |

| 0x00 5154RTC_WUTRHRTC wakeup timer register high0xFF^{(2)}0x00 5155RTC_WUTRLRTC wakeup timer register low0xFF^{(2)}0x00 5156RTC_SSRLRTC wakeup timer register low0x000x00 5157RTC_SSRLRTC subsecond register low0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_WPRRTC write protection register0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5158RTC_SIFHRTC subsecond register high0x000x00 5158RTC_SHIFTRHRTC subsecond register high0x000x00 515ARTC_SHIFTRHRTC shift register high0x000x00 515BRTC_ALRMAR1RTC alarm A register 10x00^{(2)}0x00 515DRTC_ALRMAR3RTC alarm A register 30x00^{(2)}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x00 5152 |       | RTC_APRER                   | RTC asynchronous prescaler register        | 0x7F <sup>(2)</sup> |  |  |

| 0x00 5155RTC_WUTRLRTC wakeup timer register low0xFF <sup>(2)</sup> 0x00 5156RTC_SSRLRTC subsecond register low0x000x00 5157RTC_SSRLRTC subsecond register low0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_WPRRTC write protection register0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_SRHRTC subsecond register high0x000x00 5159RTC_SHIFTRHRTC write protection register0x000x00 515ARTC_SHIFTRHRTC shift register high0x000x00 515BRTC_ALRMAR1RTC alarm A register 10x00 <sup>(2)</sup> 0x00 515DRTC_ALRMAR2RTC alarm A register 30x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x00 5153 |       |                             | Reserved area (1 byte)                     | 1                   |  |  |

| 0x00 5156Reserved area (1 byte)0x00 5157RTC_SSRLRTC subsecond register low0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_WPRRTC write protection register0x000x00 5159RTC_WPRRTC subsecond register high0x000x00 5159RTC_WPRRTC subsecond register high0x000x00 5159RTC_SSRHRTC subsecond register high0x000x00 515ARTC_SHIFTRHRTC write protection register0x000x00 515BRTC_SHIFTRLRTC shift register high0x000x00 515CRTC_ALRMAR1RTC alarm A register 10x00 <sup>(2)</sup> 0x00 515DRTC_ALRMAR2RTC alarm A register 30x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0x00 5154 |       | RTC_WUTRH                   | RTC wakeup timer register high             | 0xFF <sup>(2)</sup> |  |  |

| 0x00 5157RTC_SSRLRTC subsecond register low0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_WPRRTC write protection register0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_WPRRTC write protection register0x000x00 5159RTC_SHIFTRHRTC write protection register0x000x00 515ARTC_SHIFTRHRTC shift register high0x000x00 515BRTC_ALRMAR1RTC alarm A register 10x00 <sup>(2)</sup> 0x00 515DRTC_ALRMAR3RTC alarm A register 30x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x00 5155 |       | RTC_WUTRL                   | RTC_WUTRL RTC wakeup timer register low    |                     |  |  |

| 0x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_WPRRTC write protection register0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_WPRRTC write protection register0x000x00 515ARTC_SHIFTRHRTC shift register high0x000x00 515BRTC_SHIFTRLRTC shift register low0x000x00 515CRTC_ALRMAR1RTC alarm A register 10x00 <sup>(2)</sup> 0x00 515ERTC_ALRMAR3RTC alarm A register 30x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x00 5156 |       |                             | Reserved area (1 byte)                     | 1                   |  |  |

| 0x00 5159RTC_WPRRTC write protection register0x000x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_WPRRTC write protection register0x000x00 515ARTC_SHIFTRHRTC shift register high0x000x00 515BRTC_SHIFTRLRTC shift register low0x000x00 515CRTC_ALRMAR1RTC alarm A register 10x00 <sup>(2)</sup> 0x00 515ERTC_ALRMAR3RTC alarm A register 30x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x00 5157 |       | RTC_SSRL                    | RTC subsecond register low                 | 0x00                |  |  |

| 0x00 5158RTC_SSRHRTC subsecond register high0x000x00 5159RTC_WPRRTC write protection register0x000x00 515ARTC_SHIFTRHRTC shift register high0x000x00 515BRTC_ALRMAR1RTC shift register low0x000x00 515CRTC_ALRMAR2RTC alarm A register 10x00 <sup>(2)</sup> 0x00 515ERTC_ALRMAR3RTC alarm A register 30x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x00 5158 |       | RTC_SSRH                    | RTC subsecond register high                | 0x00                |  |  |

| 0x00 5159RTC_WPRRTC write protection register0x000x00 515ARTC_SHIFTRHRTC shift register high0x000x00 515BRTC_SHIFTRLRTC shift register low0x000x00 515CRTC_ALRMAR1RTC alarm A register 10x00 <sup>(2)</sup> 0x00 515DRTC_ALRMAR2RTC alarm A register 20x00 <sup>(2)</sup> 0x00 515ERTC_ALRMAR3RTC alarm A register 30x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0x00 5159 |       | RTC_WPR                     | RTC write protection register              | 0x00                |  |  |

| 0x00 515A       RTC_SHIFTRH       RTC shift register high       0x00         0x00 515B       RTC_SHIFTRL       RTC shift register low       0x00         0x00 515C       RTC_ALRMAR1       RTC alarm A register 1       0x00 <sup>(2)</sup> 0x00 515D       RTC_ALRMAR2       RTC alarm A register 2       0x00 <sup>(2)</sup> 0x00 515E       RTC_ALRMAR3       RTC alarm A register 3       0x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0x00 5158 |       | RTC_SSRH                    | RTC subsecond register high                | 0x00                |  |  |

| 0x00 515B       RTC_SHIFTRL       RTC shift register low       0x00         0x00 515C       RTC_ALRMAR1       RTC alarm A register 1       0x00 <sup>(2)</sup> 0x00 515D       RTC_ALRMAR2       RTC alarm A register 2       0x00 <sup>(2)</sup> 0x00 515E       RTC_ALRMAR3       RTC alarm A register 3       0x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0x00 5159 |       | RTC_WPR                     | RTC write protection register              | 0x00                |  |  |

| 0x00 515C     RTC_ALRMAR1     RTC alarm A register 1     0x00 <sup>(2)</sup> 0x00 515D     RTC_ALRMAR2     RTC alarm A register 2     0x00 <sup>(2)</sup> 0x00 515E     RTC_ALRMAR3     RTC alarm A register 3     0x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0x00 515A |       | RTC_SHIFTRH                 | RTC shift register high                    | 0x00                |  |  |

| 0x00 515D     RTC_ALRMAR2     RTC alarm A register 2     0x00 <sup>(2)</sup> 0x00 515E     RTC_ALRMAR3     RTC alarm A register 3     0x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x00 515B |       | RTC_SHIFTRL                 | RTC shift register low                     | 0x00                |  |  |

| 0x00 515E RTC_ALRMAR3 RTC alarm A register 3 0x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x00 515C |       | RTC_ALRMAR1                 | RTC alarm A register 1                     | 0x00 <sup>(2)</sup> |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x00 515D |       | RTC_ALRMAR2                 | RTC alarm A register 2                     | 0x00 <sup>(2)</sup> |  |  |

| 0x00 515F RTC_ALRMAR4 RTC alarm A register 4 0x00 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x00 515E |       | RTC_ALRMAR3                 | RTC alarm A register 3                     | 0x00 <sup>(2)</sup> |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x00 515F |       | RTC_ALRMAR4                 | RTC alarm A register 4                     | 0x00 <sup>(2)</sup> |  |  |

Table 8. General hardware register map (continued)

|                              |       |                | aalo/intoirapt controllor registere (continuea/ |                 |  |  |

|------------------------------|-------|----------------|-------------------------------------------------|-----------------|--|--|

| Address                      | Block | Register Label | Register Name                                   | Reset<br>Status |  |  |

| 0x00 7F90                    |       | DM_BK1RE       | DM breakpoint 1 register extended byte          | 0xFF            |  |  |

| 0x00 7F91                    |       | DM_BK1RH       | DM breakpoint 1 register high byte              | 0xFF            |  |  |

| 0x00 7F92                    |       | DM_BK1RL       | DM breakpoint 1 register low byte               | 0xFF            |  |  |

| 0x00 7F93                    |       | DM_BK2RE       | DM breakpoint 2 register extended byte          | 0xFF            |  |  |

| 0x00 7F94                    |       | DM_BK2RH       | DM breakpoint 2 register high byte              | 0xFF            |  |  |

| 0x00 7F95                    | DM    | DM_BK2RL       | DM_BK2RL DM breakpoint 2 register low byte      |                 |  |  |

| 0x00 7F96                    |       | DM_CR1         | DM Debug module control register 1              | 0x00            |  |  |

| 0x00 7F97                    |       | DM_CR2         | DM_CR2 DM Debug module control register 2       |                 |  |  |

| 0x00 7F98                    |       | DM_CSR1        | DM Debug module control/status register 1       | 0x10            |  |  |

| 0x00 7F99                    |       | DM_CSR2        | DM Debug module control/status register 2       | 0x00            |  |  |

| 0x00 7F9A                    |       | DM_ENFCTR      | DM enable function register                     | 0xFF            |  |  |

| 0x00 7F9B<br>to<br>0x00 7F9F |       |                | Reserved area (5 byte)                          |                 |  |  |

Table 9. CPU/SWIM/debug module/interrupt controller registers (continued)

1. Accessible by debug module only

## 7 Option bytes

Option bytes contain configurations for device hardware features as well as the memory protection of the device. They are stored in a dedicated memory block.

All option bytes can be modified in ICP mode (with SWIM) by accessing the EEPROM address. See *Table 11* for details on option byte addresses.

The option bytes can also be modified 'on the fly' by the application in IAP mode, except for the ROP and UBC values which can only be taken into account when they are modified in ICP mode (with the SWIM).

Refer to the STM8L15x Flash programming manual (PM0054) and STM8 SWIM and Debug Manual (UM0470) for information on SWIM programming procedures.

| Addr.     | Ontion nome                                                                  | Option        |                            | Option bits |                         |    |               |             |               |             | Factory default |

|-----------|------------------------------------------------------------------------------|---------------|----------------------------|-------------|-------------------------|----|---------------|-------------|---------------|-------------|-----------------|

| Addr.     | Option name                                                                  | byte<br>No.   | 7                          | 6           | 5                       | 4  | 3             | 2           | 1             | 0           | setting         |

| 0x00 4800 | Read-out<br>protection<br>(ROP)                                              | OPT0          |                            | ROP[7:0]    |                         |    |               |             |               | 0xAA        |                 |

| 0x00 4802 | UBC (User<br>Boot code size)                                                 | OPT1          |                            | UBC[7:0]    |                         |    |               |             |               | 0x00        |                 |

| 0x00 4807 |                                                                              |               |                            |             | Reserv                  | ed |               |             |               |             | 0x00            |

| 0x00 4808 | Independent<br>watchdog<br>option                                            | OPT3<br>[3:0] |                            | Rese        | erved                   |    | WWDG<br>_HALT | WWDG<br>_HW | IWDG<br>_HALT | IWDG<br>_HW | 0x00            |

| 0x00 4809 | Number of<br>stabilization<br>clock cycles for<br>HSE and LSE<br>oscillators | OPT4          | Reserved                   |             | LSECNT[1:0] HSECNT[1:0] |    |               |             | 0x00          |             |                 |

| 0x00 480A | Brownout reset<br>(BOR)                                                      | OPT5<br>[3:0] | Reserved BOR_TH BOR_<br>ON |             |                         |    |               | 0x01        |               |             |                 |

| 0x00 480B | Bootloader                                                                   | OPTBL         |                            |             |                         |    |               |             |               |             | 0x00            |

| 0x00 480C | option bytes<br>(OPTBL)                                                      | [15:0]        |                            |             |                         | OF | PTBL[15:0     | ני          |               |             | 0x00            |

Table 11. Option byte addresses

## 8 Unique ID

STM8 devices feature a 96-bit unique device identifier which provides a reference number that is unique for any device and in any context. The 96 bits of the identifier can never be altered by the user.

The unique device identifier can be read in single bytes and may then be concatenated using a custom algorithm.

The unique device identifier is ideally suited:

- For use as serial numbers

- For use as security keys to increase the code security in the program memory while using and combining this unique ID with software cryptographic primitives and protocols before programming the internal memory.

- To activate secure boot processes

| Address | Content          |   |             |   | ue ID bits | S        |   |   |   |  |

|---------|------------------|---|-------------|---|------------|----------|---|---|---|--|

| Address | description      | 7 | 6           | 5 | 4          | 3        | 2 | 1 | 0 |  |

| 0x4926  | X co-ordinate on |   |             |   | U_         | ID[7:0]  |   |   |   |  |

| 0x4927  | the wafer        |   |             |   | U_I        | D[15:8]  |   |   |   |  |

| 0x4928  | Y co-ordinate on |   |             |   | U_II       | D[23:16] |   |   |   |  |

| 0x4929  | the wafer        |   |             |   | U_II       | D[31:24] |   |   |   |  |

| 0x492A  | Wafer number     |   | U_ID[39:32] |   |            |          |   |   |   |  |

| 0x492B  |                  |   | U_ID[47:40] |   |            |          |   |   |   |  |

| 0x492C  |                  |   |             |   | U_II       | D[55:48] |   |   |   |  |

| 0x492D  | -                |   |             |   | U_II       | D[63:56] |   |   |   |  |

| 0x492E  | Lot number       |   | U_ID[71:64] |   |            |          |   |   |   |  |

| 0x492F  |                  |   | U_ID[79:72] |   |            |          |   |   |   |  |

| 0x4930  |                  |   |             |   | U_II       | D[87:80] |   |   |   |  |

| 0x4931  |                  |   |             |   | U_II       | D[95:88] |   |   |   |  |

### Table 13. Unique ID registers (96 bits)

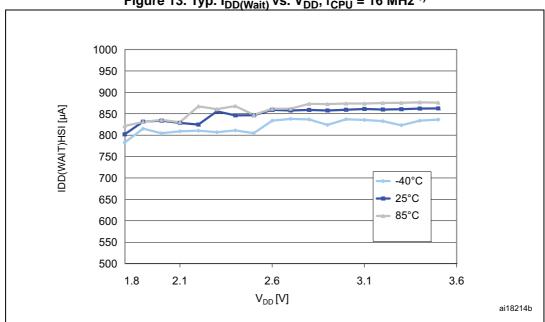

Figure 13. Typ.  $I_{DD(Wait)}$  vs.  $V_{DD}$ ,  $f_{CPU}$  = 16 MHz <sup>1)</sup>

1. Typical current consumption measured with code executed from Flash memory.

In the following table, data is based on characterization results, unless otherwise specified.

| Symbol               | Parameter                           |                                       | Conditions <sup>(1)(2</sup>     | )                                        | Тур  | Max  | Unit |

|----------------------|-------------------------------------|---------------------------------------|---------------------------------|------------------------------------------|------|------|------|

|                      |                                     |                                       |                                 | $T_A = -40 \text{ °C to } 25 \text{ °C}$ | 3    | 3.3  |      |

|                      |                                     |                                       |                                 | T <sub>A</sub> = 55 °C                   | 3.3  | 3.6  |      |

|                      |                                     |                                       | all peripherals OFF             | T <sub>A</sub> = 85 °C                   | 4.4  | 5    |      |

|                      |                                     |                                       |                                 | T <sub>A</sub> = 105 °C                  | 6.7  | 8    |      |

|                      |                                     | LSI RC osc.                           |                                 | T <sub>A</sub> = 125 °C                  | 11   | 14   |      |

|                      |                                     | (at 38 kHz)                           |                                 | $T_A = -40 \text{ °C to } 25 \text{ °C}$ | 3.4  | 3.7  |      |

|                      |                                     |                                       |                                 | T <sub>A</sub> = 55 °C                   | 3.7  | 4    |      |

|                      |                                     | with TIM2 active <sup>(3)</sup>       | T <sub>A</sub> = 85 °C          | 4.8                                      | 5.4  | -    |      |

|                      |                                     |                                       | T <sub>A</sub> = 105 °C         | 7                                        | 8.3  |      |      |

| I <sub>DD(LPW)</sub> | Supply current in<br>Low power wait |                                       |                                 | T <sub>A</sub> = 125 °C                  | 11.3 | 14.5 | μA   |

| 'DD(LPVV)            | mode                                |                                       |                                 | $T_A = -40 \text{ °C to } 25 \text{ °C}$ | 2.35 | 2.7  | μΛ   |

|                      |                                     |                                       | all peripherals OFF             | T <sub>A</sub> = 55 °C                   | 2.42 | 2.82 | -    |

|                      |                                     |                                       |                                 | T <sub>A</sub> = 85 °C                   | 3.10 | 3.71 |      |

|                      |                                     |                                       |                                 | T <sub>A</sub> = 105 °C                  | 4.36 | 5.7  |      |

|                      |                                     | LSE external<br>clock <sup>(4)</sup>  |                                 | T <sub>A</sub> = 125 °C                  | 7.20 | 11   |      |

|                      |                                     | (32.768 kHz)                          |                                 | $T_A = -40 \text{ °C to } 25 \text{ °C}$ | 2.46 | 2.75 |      |

|                      |                                     | · · · · · · · · · · · · · · · · · · · |                                 | T <sub>A</sub> = 55 °C                   | 2.50 | 2.81 |      |

|                      |                                     |                                       | with TIM2 active <sup>(3)</sup> | T <sub>A</sub> = 85 °C                   | 3.16 | 3.82 |      |

|                      |                                     |                                       |                                 | T <sub>A</sub> = 105 °C                  | 4.51 | 5.9  |      |

|                      |                                     |                                       |                                 | T <sub>A</sub> = 125 °C                  | 7.28 | 11   |      |

| Table 22. Total current consumption in Low | nower wait mode at $V_{-}$ = -1.65 V to 3.6 V |

|--------------------------------------------|-----------------------------------------------|

| Table 22. Total current consumption in Low | power wait mode at $v_{DD} = 1.05 v$ to 5.0 v |

1. No floating I/Os.

2.  $T_A > 85$  °C is valid only for devices with suffix 3 temperature range.

3. Timer 2 clock enabled and counter is running.

Oscillator bypassed (LSEBYP = 1 in CLK\_ECKCR). When configured for external crystal, the LSE consumption (I<sub>DD LSE</sub>) must be added. Refer to Table 31.

In the following table, data is based on characterization results, unless otherwise specified.

| Symbol                                      | Parameter                                                          | Condition <sup>(1)(2)</sup>              | Тур  | Мах                 | Unit |

|---------------------------------------------|--------------------------------------------------------------------|------------------------------------------|------|---------------------|------|

|                                             |                                                                    | $T_A = -40 \text{ °C to } 25 \text{ °C}$ | 350  | 1400 <sup>(3)</sup> |      |

|                                             | Supply current in Halt mode                                        | T <sub>A</sub> = 55 °C                   | 580  | 2000                |      |

| I <sub>DD(Halt)</sub>                       | (Ultra-low-power ULP bit =1 in                                     | T <sub>A</sub> = 85 °C                   | 1160 | 2800 <sup>(3)</sup> | nA   |

|                                             | the PWR_CSR2 register)                                             | T <sub>A</sub> = 105 °C                  | 2560 | 6700 <sup>(3)</sup> |      |

|                                             |                                                                    | T <sub>A</sub> = 125 °C                  | 4.4  | 13 <sup>(3)</sup>   | μA   |

| IDD(WUHait)                                 | Supply current during wakeup<br>time from Halt mode (using<br>HSI) | -                                        | 2.4  | -                   | mA   |

| t <sub>WU_HSI(Halt)</sub> <sup>(4)(5)</sup> | Wakeup time from Halt to Run mode (using HSI)                      | -                                        | 4.7  | 7                   | μs   |

| t <sub>WU_LSI(Halt)</sub> <sup>(4)(5)</sup> | Wakeup time from Halt mode to Run mode (using LSI)                 | -                                        | 150  | -                   | μs   |

Table 25. Total current consumption and timing in Halt mode at  $V_{DD}$  = 1.65 to 3.6 V

1.  $T_A = -40$  to 125 °C, no floating I/O, unless otherwise specified.

2.  $T_A$  > 85 °C is valid only for devices with suffix 3 temperature range.

3. Tested in production.

4. ULP=0 or ULP=1 and FWU=1 in the PWR\_CSR2 register.

5. Wakeup time until start of interrupt vector fetch. The first word of interrupt routine is fetched 4 CPU cycles after  $t_{WU}$ .

## 9.3.8 Communication interfaces

### SPI1 - Serial peripheral interface

Unless otherwise specified, the parameters given in *Table 42* are derived from tests performed under ambient temperature, f<sub>SYSCLK</sub> frequency and V<sub>DD</sub> supply voltage conditions summarized in *Section 9.3.1*. Refer to I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                                 | Parameter                     | Conditions <sup>(1)</sup>                                             | Min                       | Max                      | Unit |  |

|------------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------|---------------------------|--------------------------|------|--|

| f <sub>SCK</sub>                                                       | SDI1 alook fraguanay          | Master mode                                                           | 0                         | 8                        |      |  |

| 1/t <sub>c(SCK)</sub>                                                  | SPI1 clock frequency          | Slave mode                                                            | 0                         | 8                        | MHz  |  |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>                             | SPI1 clock rise and fall time | Capacitive load: C = 30 pF                                            | -                         | 30                       |      |  |

| t <sub>su(NSS)</sub> <sup>(2)</sup>                                    | NSS setup time                | Slave mode                                                            | 4 x 1/f <sub>SYSCLK</sub> | -                        |      |  |

| t <sub>h(NSS)</sub> <sup>(2)</sup>                                     | NSS hold time                 | Slave mode                                                            | 80                        | -                        |      |  |

| t <sub>w(SCKH)</sub> (2)<br>t <sub>w(SCKL)</sub> (2)                   | SCK high and low time         | Master mode,<br>f <sub>MASTER</sub> = 8 MHz, f <sub>SCK</sub> = 4 MHz | 105                       | 145                      | -    |  |

| t <sub>su(MI)</sub> (2)                                                | Data input setup time         | Master mode                                                           | 30                        | -                        |      |  |

| t <sub>su(MI)</sub> (2)<br>t <sub>su(SI)</sub> (2)                     |                               | Slave mode                                                            | 3                         | -                        |      |  |

| t <sub>h(MI)</sub> <sup>(2)</sup>                                      | Data input hold time          | Master mode                                                           | 15                        | -                        |      |  |

| t <sub>h(MI)</sub> <sup>(2)</sup><br>t <sub>h(SI)</sub> <sup>(2)</sup> | Data input hold time          | Slave mode                                                            | 0                         | -                        | ns   |  |