Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| 2014                       |                                                                                         |

|----------------------------|-----------------------------------------------------------------------------------------|

| Product Status             | Last Time Buy                                                                           |

| Core Processor             | ARM® Cortex®-M0                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                      |

| Speed                      | 50MHz                                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 35                                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                                          |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | -                                                                                       |

| RAM Size                   | 4K x 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                             |

| Data Converters            | A/D 8x12b                                                                               |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 48-LQFP                                                                                 |

| Supplier Device Package    | -                                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/nuc130lc1cn |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **1 GENERAL DESCRIPTION**

The NuMicro<sup>™</sup> NUC100 Series is 32-bit microcontrollers with embedded ARM<sup>®</sup> Cortex<sup>™</sup>-M0 core for industrial control and applications which need rich communication interfaces. The Cortex<sup>™</sup>-M0 is the newest ARM<sup>®</sup> embedded processor with 32-bit performance and at a cost equivalent to traditional 8-bit microcontroller. NuMicro<sup>™</sup> NUC100 Series includes NUC100, NUC120, NUC130 and NUC140 product line.

The NuMicro<sup>™</sup> NUC130 Automotive Line with CAN function embeds Cortex<sup>™</sup>-M0 core running up to 50 MHz with 32K/64K/128K-byte embedded flash, 4K/8K/16K-byte embedded SRAM, and 4K-byte loader ROM for the ISP. It also equips with plenty of peripheral devices, such as Timers, Watchdog Timer, RTC, PDMA, UART, SPI, I<sup>2</sup>C, I<sup>2</sup>S, PWM Timer, GPIO, LIN, CAN, PS/2, 12-bit ADC, Analog Comparator, Low Voltage Reset Controller and Brown-out Detector.

| Product Line | UART | SPI | I <sup>2</sup> C | USB | LIN | CAN | PS/2 | l <sup>2</sup> S |    |

|--------------|------|-----|------------------|-----|-----|-----|------|------------------|----|

| NUC100       | •    | •   | •                |     |     |     | 0    | 100              |    |

| NUC120       | •    | •   | •                | •   |     |     | •    | •                | D. |

| NUC130       | •    | •   | •                |     | •   | •   | •    | N.               | 1  |

| NUC140       | •    | •   | •                | •   | •   | •   | •    | •                | 2  |

Table 1-1 Connectivity Supported Table

## 2 FEATURES

The equipped features are dependent on the product line and their sub products.

## 2.1 NuMicro™ NUC130 Features – Automotive Line

- Core

- ARM<sup>®</sup> Cortex<sup>™</sup>-M0 core runs up to 50 MHz

- One 24-bit system timer

- Supports low power sleep mode

- Single-cycle 32-bit hardware multiplier

- NVIC for the 32 interrupt inputs, each with 4-levels of priority

- Serial Wire Debug supports with 2 watchpoints/4 breakpoints

- Build-in LDO for wide operating voltage ranges from 2.5 V to 5.5 V

- Flash Memory

- 32K/64K/128K bytes Flash for program code

- 4KB flash for ISP loader

- Support In-system program (ISP) application code update

- 512 byte page erase for flash

- Configurable data flash address and size for 128KB system, fixed 4KB data flash for the 32KB and 64KB system

- Support 2 wire ICP update through SWD/ICE interface

- Support fast parallel programming mode by external programmer

- SRAM Memory

- 4K/8K/16K bytes embedded SRAM

- Support PDMA mode

- PDMA (Peripheral DMA)

- Support 9 channels PDMA for automatic data transfer between SRAM and peripherals

- Clock Control

- Flexible selection for different applications

- Built-in 22.1184 MHz high speed OSC for system operation

- Trimmed to  $\pm$  1 % at +25 °C and V<sub>DD</sub> = 5 V

- Trimmed to  $\pm$  3 % at -40 °C ~ +85 °C and V<sub>DD</sub> = 2.5 V ~ 5.5 V

- Built-in 10 kHz low speed OSC for Watchdog Timer and Wake-up operation

- Support one PLL, up to 50 MHz, for high performance system operation

- External 4~24 MHz high speed crystal input for precise timing operation External 32.768 kHz low speed crystal input for RTC function and low power system operation

- GPIO

- Four I/O modes:

- Quasi bi-direction

- Push-Pull output

- Open-Drain output

- Input only with high impendence

- TTL/Schmitt trigger input selectable

- I/O pin can be configured as interrupt source with edge/level setting

- High driver and high sink IO mode support

- Support PDMA mode

- Analog Comparator

- Up to two analog comparator

- External input or internal bandgap voltage selectable at negative node

- Interrupt when compare result change

- Power down wake-up

- One built-in temperature sensor with  $1\,{}^\circ\!\mathrm{C}$  resolution

- Brown-Out detector

- With 4 levels: 4.5 V/3.8 V/2.7 V/2.2 V

- Support Brown-Out Interrupt and Reset option

- Low Voltage Reset

- Threshold voltage levels: 2.0 V

- Operating Temperature: -40°C~85°C

- Packages:

- All Green package (RoHS)

- LQFP 100-pin / 64-pin / 48-pin

## ηυνοτοη

### 5.2.6 Nested Vectored Interrupt Controller (NVIC)

Cortex-M0 provides an interrupt controller as an integral part of the exception mode, named as "Nested Vectored Interrupt Controller (NVIC)". It is closely coupled to the processor kernel and provides following features:

- Nested and Vectored interrupt support

- Automatic processor state saving and restoration

- Reduced and deterministic interrupt latency

The NVIC prioritizes and handles all supported exceptions. All exceptions are handled in "Handler Mode". This NVIC architecture supports 32 (IRQ[31:0]) discrete interrupts with 4 levels of priority. All of the interrupts and most of the system exceptions can be configured to different priority levels. When an interrupt occurs, the NVIC will compare the priority of the new interrupt to the current running one's priority. If the priority of the new interrupt is higher than the current one, the new interrupt handler will override the current handler.

When any interrupts is accepted, the starting address of the interrupt service routine (ISR) is fetched from a vector table in memory. There is no need to determine which interrupt is accepted and branch to the starting address of the correlated ISR by software. While the starting address is fetched, NVIC will also automatically save processor state including the registers "PC, PSR, LR, R0~R3, R12" to the stack. At the end of the ISR, the NVIC will restore the mentioned registers from stack and resume the normal execution. Thus it will take less and deterministic time to process the interrupt request.

The NVIC supports "Tail Chaining" which handles back-to-back interrupts efficiently without the overhead of states saving and restoration and therefore reduces delay time in switching to pending ISR at the end of current ISR. The NVIC also supports "Late Arrival" which improves the efficiency of concurrent ISRs. When a higher priority interrupt request occurs before the current ISR starts to execute (at the stage of state saving and starting address fetching), the NVIC will give priority to the higher one without delay penalty. Thus it advances the real-time capability.

For more detailed information, please refer to the documents "ARM<sup>®</sup> Cortex™-M0 Technical Reference Manual" and "ARM<sup>®</sup> v6-M Architecture Reference Manual".

Publication Release Date: Jan. 2, 2012 Revision V3.02

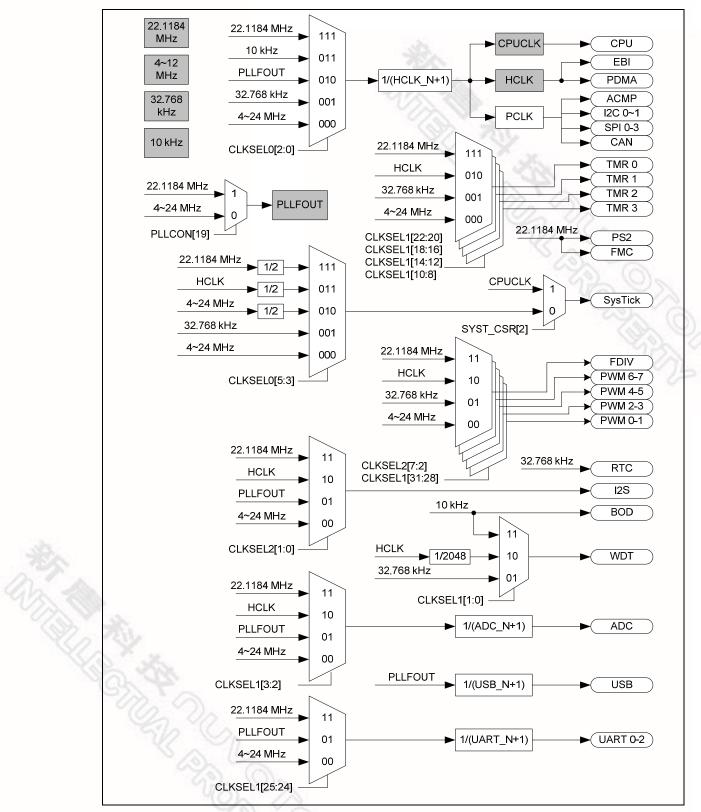

### 5.3 Clock Controller

### 5.3.1 Overview

The clock controller generates the clocks for the whole chip, including system clocks and all peripheral clocks. The clock controller also implements the power control function with the individually clock ON/OFF control, clock source selection and a clock divider. The chip will not enter power down mode until CPU sets the power down enable bit (PWR\_DOWN\_EN) and Cortex-M0 core executes the WFI instruction. After that, chip enter power down mode and wait for wake-up interrupt source triggered to leave power down mode. In the power down mode, the clock controller turns off the external 4~24 MHz high speed crystal and internal 22.1184 MHz high speed oscillator to reduce the overall system power consumption.

Figure 5-3 Clock generator global view diagram

### 5.3.4 Peripherals Clock

The peripherals clock had different clock source switch setting which depends on the different peripheral. Please refer the CLKSEL1 and CLKSEL2 register description in 5.3.7.

### 5.3.5 Power Down Mode Clock

When chip enters into power down mode, system clocks, some clock sources, and some peripheral clocks will be disabled. Some clock sources and peripherals clock are still active in power down mode.

For theses clocks which still keep active list below:

- Clock Generator

- Internal 10 kHz low speed oscillator clock

- External 32.768 kHz low speed crystal clock

- Peripherals Clock (When these IP adopt external 32.768 kHz low speed crystal or 10 kHz low speed oscillator as clock source)

## 5.5 I<sup>2</sup>C Serial Interface Controller (Master/Slave) (I<sup>2</sup>C)

### 5.5.1 Overview

$I^2C$  is a two-wire, bi-directional serial bus that provides a simple and efficient method of data exchange between devices. The  $I^2C$  standard is a true multi-master bus including collision detection and arbitration that prevents data corruption if two or more masters attempt to control the bus simultaneously.

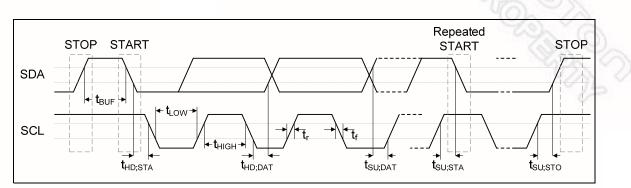

Data is transferred between a Master and a Slave synchronously to SCL on the SDA line on a byte-by-byte basis. Each data byte is 8-bit long. There is one SCL clock pulse for each data bit with the MSB being transmitted first. An acknowledge bit follows each transferred byte. Each bit is sampled during the high period of SCL; therefore, the SDA line may be changed only during the low period of SCL and must be held stable during the high period of SCL. A transition on the SDA line while SCL is high is interpreted as a command (START or STOP). Please refer to the Figure 5-9 for more detail I<sup>2</sup>C BUS Timing.

Figure 5-9 I<sup>2</sup>C Bus Timing

The device's on-chip  $I^2C$  logic provides the serial interface that meets the  $I^2C$  bus standard mode specification. The  $I^2C$  port handles byte transfers autonomously. To enable this port, the bit ENS1 in I2CON should be set to '1'. The  $I^2C$  H/W interfaces to the  $I^2C$  bus via two pins: SDA and SCL. Pull up resistor is needed for  $I^2C$  operation as these are open drain pins. When the I/O pins are used as  $I^2C$  port, user must set the pins function to  $I^2C$  in advance.

# nuvoton

PIIR to get interrupt source and Read CRLRx/CFLRx(x=0~3) to get capture value and finally write 1 to clear PIIR to zero. If interrupt latency will take time T0 to finish, the capture signal mustn't transition during this interval (T0). In this case, the maximum capture frequency will be 1/T0. For example:

HCLK = 50 MHz, PWM\_CLK = 25 MHz, Interrupt latency is 900 ns

So the maximum capture frequency will is 1/900ns ≈ 1000 kHz

#### 5.6.2 Features

5.6.2.1 PWM function features:

- PWM group has two PWM generators. Each PWM generator supports one 8-bit prescaler, one clock divider, two PWM-timers (down counter), one dead-zone generator and two PWM outputs.

- Up to 16-bit resolution

- PWM Interrupt request synchronized with PWM period

- One-shot or Auto-reload mode PWM

- Up to 2 PWM group (PWMA/PWMB) to support 8 PWM channels or 4 PWM paired channels

#### 5.6.2.2 Capture Function Features:

- Timing control logic shared with PWM Generators

- Support 8 Capture input channels shared with 8 PWM output channels

- Each channel supports one rising latch register (CRLR), one falling latch register (CFLR) and Capture interrupt flag (CAPIFx)

## 5.7 Real Time Clock (RTC)

### 5.7.1 Overview

Real Time Clock (RTC) controller provides user the real time and calendar message. The clock source of RTC is from an external 32.768 kHz low speed crystal connected at pins X321 and X32O (reference to pin descriptions) or from an external 32.768 kHz low speed oscillator output fed at pin X321. The RTC controller provides the time message (second, minute, hour) in Time Loading Register (TLR) as well as calendar message (day, month, year) in Calendar Loading Register (CLR). The data message is expressed in BCD format. It also offers alarm function that user can preset the alarm time in Time Alarm Register (TAR) and alarm calendar in Calendar Alarm Register (CAR).

The RTC controller supports periodic Time Tick and Alarm Match interrupts. The periodic interrupt has 8 period options 1/128, 1/64, 1/32, 1/16, 1/8, 1/4, 1/2 and 1 second which are selected by TTR (TTR[2:0]). When RTC counter in TLR and CLR is equal to alarm setting time registers TAR and CAR, the alarm interrupt flag (RIIR.AIF) is set and the alarm interrupt is requested if the alarm interrupt is enabled (RIER.AIER=1). Both RTC Time Tick and Alarm Match can cause chip wake-up from power down mode if wake-up function is enabled (TWKE (TTR[3])=1).

### 5.7.2 Features

- There is a time counter (second, minute, hour) and calendar counter (day, month, year) for user to check the time

- Alarm register (second, minute, hour, day, month, year)

- 12-hour or 24-hour mode is selectable

- Leap year compensation automatically

- Day of week counter

- Frequency compensate register (FCR)

- All time and calendar message is expressed in BCD code

- Support periodic time tick interrupt with 8 period options 1/128, 1/64, 1/32, 1/16, 1/8, 1/4, 1/2 and 1 second

- Support RTC Time Tick and Alarm Match interrupt

- Support wake-up chip from power down mode

#### **Timer Controller (TMR)** 5.9

#### 5.9.1 **Overview**

The timer controller includes four 32-bit timers, TIMER0~TIMER3, which allows user to easily implement a timer control for applications. The timer can perform functions like frequency measurement, event counting, interval measurement, clock generation, delay timing, and so on. The timer can generate an interrupt signal upon timeout, or provide the current value during operation.

#### 5.9.2 Features

- 4 sets of 32-bit timers with 24-bit up-timer and one 8-bit pre-scale counter

- Independent clock source for each timer

- Provides one-shot, periodic, toggle and continuous counting operation modes

- Time out period = (Period of timer clock input) \* (8-bit pre-scale counter + 1) \* (24-bit TCMP)

- Maximum counting cycle time =  $(1 / T MHz) * (2^8) * (2^{24})$ , T is the period of timer clock

- 24-bit timer value is readable through TDR (Timer Data Register)

- Support event counting function to count the event from external pin

- Support input capture function to capture or reset counter value

| System clock = internal 22.1184 MHz high speed oscillator |                    |             |                                       |                                           |           |             |  |  |  |

|-----------------------------------------------------------|--------------------|-------------|---------------------------------------|-------------------------------------------|-----------|-------------|--|--|--|

| Baud rate                                                 | Mode0              |             | М                                     | ode1                                      | Mode2     |             |  |  |  |

| Budd fullo                                                | Parameter Register |             | Parameter Register                    |                                           | Parameter | Register    |  |  |  |

| 230400                                                    | A=4                | 0x0000_0004 | A=4,B=15<br>A=6,B=11                  | 0x2F00_0004<br>0x2B00_0006                | A=94      | 0x3000_005E |  |  |  |

| 115200                                                    | A=10               | 0x0000_000A | A=10,B=15<br>A=14,B=11                | 0x2F00_000A<br>0x2B00_000E                | A=190     | 0x3000_00BE |  |  |  |

| 57600                                                     | A=22               | 0x0000_0016 | A=22,B=15<br>A=30,B=11                | 0x2F00_0016<br>0x2B00_001E                | A=382     | 0x3000_017E |  |  |  |

| 38400                                                     | A=34               | 0x0000_0022 | A=62,B=8<br>A=46,B=11<br>A=34,B=15    | 0x2800_003E<br>0x2B00_002E<br>0x2F00_0022 | A=574     | 0x3000_023E |  |  |  |

| 19200                                                     | A=70               | 0x0000_0046 | A=126,B=8<br>A=94,B=11<br>A=70,B=15   | 0x2800_007E<br>0x2B00_005E<br>0x2F00_0046 | A=1150    | 0x3000_047E |  |  |  |

| 9600                                                      | A=142              | 0x0000_008E | A=254,B=8<br>A=190,B=11<br>A=142,B=15 | 0x2800_00FE<br>0x2B00_00BE<br>0x2F00_008E | A=2302    | 0x3000_08FE |  |  |  |

| 4800                                                      | A=286              | 0x0000_011E | A=510,B=8<br>A=382,B=11<br>A=286,B=15 | 0x2800_01FE<br>0x2B00_017E<br>0x2F00_011E | A=4606    | 0x3000_11FE |  |  |  |

Table 5-7 UART Baud Rate Setting Table

The UART0 and UART1 controllers support auto-flow control function that uses two low-level signals, /CTS (clear-to-send) and /RTS (request-to-send), to control the flow of data transfer between the UART and external devices (ex: Modem). When auto-flow is enabled, the UART is not allowed to receive data until the UART asserts /RTS to external device. When the number of bytes in the RX FIFO equals the value of RTS\_TRI\_LEV (UA\_FCR [19:16]), the /RTS is deasserted. The UART sends data out when UART controller detects /CTS is asserted from external device. If a valid asserted /CTS is not detected the UART controller will not send data out.

The UART controllers also provides Serial IrDA (SIR, Serial Infrared) function (User must set IrDA\_EN (UA\_FUN\_SEL [1]) to enable IrDA function). The SIR specification defines a short-range infrared asynchronous serial transmission mode with one start bit, 8 data bits, and 1 stop bit. The maximum data rate is 115.2 Kbps (half duplex). The IrDA SIR block contains an IrDA SIR Protocol encoder/decoder. The IrDA SIR protocol is half-duplex only. So it cannot transmit and receive data at the same time. The IrDA SIR physical layer specifies a minimum 10ms transfer delay between transmission and reception. This delay feature must be implemented by software.

The alternate function of UART controllers is LIN (Local Interconnect Network) function. The LIN mode is selected by setting the UA\_FUN\_SEL[1:0] to '01'. In LIN mode, one start bit and 8-bit data format with 1-bit stop bit are required in accordance with the LIN standard.

For NuMicro<sup>™</sup> NUC100 Series, another alternate function of UART controllers is RS-485 9-bit mode function, and direction control provided by RTS pin or can program GPIO (PB.2 for RTS0 and PB.6 for RTS1) to implement the function by software. The RS-485 mode is selected by setting the UA\_FUN\_SEL register to select RS-485 function. The RS-485 driver control is implemented using the RTS control signal from an asynchronous serial port to enable the RS-485 driver. In RS-485 mode, many characteristics of the RX and TX are same as UART.

## 5.12 Controller Area Network (CAN)

### 5.12.1 Overview

The C\_CAN consists of the CAN Core, Message RAM, Message Handler, Control Registers and Module Interface (Refer **Error! Reference source not found.**). The CAN Core performs communication according to the CAN protocol version 2.0 part A and B. The bit rate can be programmed to values up to 1MBit/s. For the connection to the physical layer, additional transceiver hardware is required.

For communication on a CAN network, individual Message Objects are configured. The Message Objects and Identifier Masks for acceptance filtering of received messages are stored in the Message RAM. All functions concerning the handling of messages are implemented in the Message Handler. These functions include acceptance filtering, the transfer of messages between the CAN Core and the Message RAM, and the handling of transmission requests as well as the generation of the module interrupt.

The register set of the C\_CAN can be accessed directly by the software through the module interface. These registers are used to control/configure the CAN Core and the Message Handler and to access the Message RAM.

### 5.12.2 Features

- Supports CAN protocol version 2.0 part A and B.

- Bit rates up to 1 MBit/s.

- 32 Message Objects.

- Each Message Object has its own identifier mask.

- Programmable FIFO mode (concatenation of Message Objects).

- Maskable interrupt.

- Disabled Automatic Re-transmission mode for Time Triggered CAN applications.

- Programmable loop-back mode for self-test operation.

- 16-bit module interfaces to the AMBA APB bus.

- Support wake-up function

## 5.15 Analog-to-Digital Converter (ADC)

### 5.15.1 Overview

NuMicro<sup>™</sup> NUC100 Series contains one 12-bit successive approximation analog-to-digital converters (SAR A/D converter) with 8 input channels. The A/D converter supports three operation modes: single, single-cycle scan and continuous scan mode. The A/D converters can be started by software and external STADC pin.

### 5.15.2 Features

- Analog input voltage range: 0~V<sub>REF</sub>

- 12-bit resolution and 10-bit accuracy is guaranteed

- Up to 8 single-end analog input channels or 4 differential analog input channels

- Maximum ADC clock frequency is 16 MHz

- Up to 700K SPS conversion rate

- Three operating modes

- Single mode: A/D conversion is performed one time on a specified channel

- Single-cycle scan mode: A/D conversion is performed one cycle on all specified channels with the sequence from the lowest numbered channel to the highest numbered channel

- Continuous scan mode: A/D converter continuously performs Single-cycle scan mode until software stops A/D conversion

- An A/D conversion can be started by

- Software write 1 to ADST bit

- External pin STADC

- Conversion results are held in data registers for each channel with valid and overrun indicators

- Conversion result can be compared with specify value and user can select whether to generate an interrupt when conversion result is equal to the compare register setting

- Channel 7 supports 3 input sources: external analog voltage, internal bandgap voltage, and internal temperature sensor output

- Support Self-calibration to minimize conversion error

## 5.16 Analog Comparator (CMP)

### 5.16.1 Overview

NuMicro<sup>™</sup> NUC100 Series contains two comparators. The comparators can be used in a number of different configurations. The comparator output is a logical one when positive input greater than negative input, otherwise the output is a zero. Each comparator can be configured to cause an interrupt when the comparator output value changes. The block diagram is shown in **Error! Reference source not found.**

### 5.16.2 Features

- Analog input voltage range: 0~5.0 V

- Hysteresis function supported

- Two analog comparators with optional internal reference voltage input at negative end

- One interrupt vector for both comparators

## 5.18 External Bus Interface (EBI)

### 5.18.1 Overview

The NuMicro<sup>™</sup> NUC130/NUC140 LQFP-64 and LQFP-100 package equips an external bus interface (EBI) for external device used.

To save the connections between external device and this chip, EBI support address bus and data bus multiplex mode. And, address latch enable (ALE) signal supported differentiate the address and data cycle.

### 5.18.2 Features

External Bus Interface has the following functions:

- External devices with max. 64K-byte size (8-bit data width)/128K-byte (16-bit data width) supported

- Variable external bus base clock (MCLK) supported

- 8-bit or 16-bit data width supported

- Variable data access time (tACC), address latch enable time (tALE) and address hold time (tAHD) supported

- Address bus and data bus multiplex mode supported to save the address pins

- Configurable idle cycle supported for different access condition: Write command finish (W2X), Read-to-Read (R2R)

## 7 ELECTRICAL CHARACTERISTICS

## 7.1 Absolute Maximum Ratings

| PARAMETER                                 | SYMBOL                           | MIN.                 | MAX                  | UNIT |

|-------------------------------------------|----------------------------------|----------------------|----------------------|------|

| DC Power Supply                           | V <sub>DD</sub> -V <sub>SS</sub> | -0.3                 | +7.0                 | V    |

| Input Voltage                             | V <sub>IN</sub>                  | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +0.3 | V    |

| Oscillator Frequency                      | 1/t <sub>CLCL</sub>              | 4 3                  | 24                   | MHz  |

| Operating Temperature                     | TA                               | -40                  | +85                  | °C   |

| Storage Temperature                       | TST                              | -55                  | +150                 | °C   |

| Maximum Current into V <sub>DD</sub>      |                                  | -                    | 120                  | mA   |

| Maximum Current out of V <sub>SS</sub>    |                                  |                      | 120                  | mA   |

| Maximum Current sunk by a I/O pin         |                                  |                      | 35                   | mA   |

| Maximum Current sourced by a I/O pin      |                                  |                      | 35                   | mA   |

| Maximum Current sunk by total I/O pins    |                                  |                      | 100                  | mA   |

| Maximum Current sourced by total I/O pins |                                  |                      | 100                  | mA   |

Note: Exposure to conditions beyond those listed under absolute maximum ratings may adversely affects the lift and reliability of the device.

| DADAMETER                                  | 0)/14              | SPECIFICATION    |     |      | TEST CONDITIONS |                                                                                 |

|--------------------------------------------|--------------------|------------------|-----|------|-----------------|---------------------------------------------------------------------------------|

| PARAMETER                                  | SYM.               | MIN. TYP. MAX. U |     | UNIT | TEST CONDITIONS |                                                                                 |

|                                            | I <sub>DD8</sub>   |                  | 6   |      | mA              | $V_{DD}$ = 3 V@12 MHz,<br>disable all IP and disable PLL,<br>XTAL=12 MHz        |

|                                            | I <sub>DD9</sub>   |                  | 11  | Ŷ    | mA              | V <sub>DD</sub> = 5 V@4 MHz,<br>enable all IP and disable PLL,<br>XTAL=4 MHz    |

| Operating Current                          | I <sub>DD10</sub>  |                  | 3   |      | mA              | V <sub>DD</sub> = 5 V@4 MHz,<br>disable all IP and disable PLL,<br>XTAL=4 MHz   |

| Normal Run Mode<br>@ 4 MHz                 | I <sub>DD11</sub>  |                  | 10  |      | mA              | V <sub>DD</sub> = 3 V@4 MHz,<br>enable all IP and disable PLL,<br>XTAL=4 MHz    |

|                                            | I <sub>DD12</sub>  |                  | 2.5 |      | mA              | V <sub>DD</sub> = 3 V@4 MHz,<br>disable all IP and disable PLL,<br>XTAL=4 MHz   |

|                                            | I <sub>IDLE1</sub> |                  | 35  |      | mA              | V <sub>DD</sub> = 5.5 V@50 MHz,<br>enable all IP and PLL, XTAL=12<br>MHz        |

| Operating Current                          | I <sub>IDLE2</sub> |                  | 15  |      | mA              | V <sub>DD</sub> =5.5 V@50 MHz,<br>disable all IP and enable PLL,<br>XTAL=12 MHz |

| Idle Mode<br>@ 50 MHz                      | I <sub>IDLE3</sub> |                  | 33  |      | mA              | V <sub>DD</sub> = 3 V@50 MHz,<br>enable all IP and PLL, XTAL=12<br>MHz          |

|                                            | I <sub>IDLE4</sub> |                  | 13  |      | mA              | V <sub>DD</sub> = 3 V@50 MHz,<br>disable all IP and enable PLL,<br>XTAL=12 MHz  |

| Operating Current<br>Idle Mode<br>@ 12 MHz | I <sub>IDLE5</sub> |                  | 10  |      | mA              | $V_{DD} = 5.5 V@12 MHz,$<br>enable all IP and disable PLL,<br>XTAL=12 MHz       |

|                                            | I <sub>IDLE6</sub> |                  | 4.5 |      | mA              | $V_{DD} = 5.5 V@12 MHz,$<br>disable all IP and disable PLL,<br>XTAL=12 MHz      |

|                                            | I <sub>IDLE7</sub> |                  | 9   |      | mA              | V <sub>DD</sub> = 3 V@12 MHz,<br>enable all IP and disable PLL,<br>XTAL=12 MHz  |

| 7.4.2 | Specification of LDO and Power management |

|-------|-------------------------------------------|

|-------|-------------------------------------------|

| PARAMETER      | MIN. | TYP. | MAX. | UNIT | NOTE                          |

|----------------|------|------|------|------|-------------------------------|

| Input Voltage  | 2.7  | 5    | 5.5  | V    | $V_{\text{DD}}$ input voltage |

| Output Voltage | -10% | 2.5  | +10% | V    | V <sub>DD</sub> > 2.7 V       |

| Temperature    | -40  | 25   | 85   | °C   | 24                            |

| Сbр            | -    | 1    | 19   | uF   | Resr=10hm                     |

Note:

1. It is recommended that a 10uF or higher capacitor and a 100nF bypass capacitor are connected between  $V_{DD}$  and the closest  $V_{SS}$  pin of the device.

2. For ensuring power stability, a 1uF or higher capacitor must be connected between LDO pin and the closest  $V_{SS}$  pin of the device.

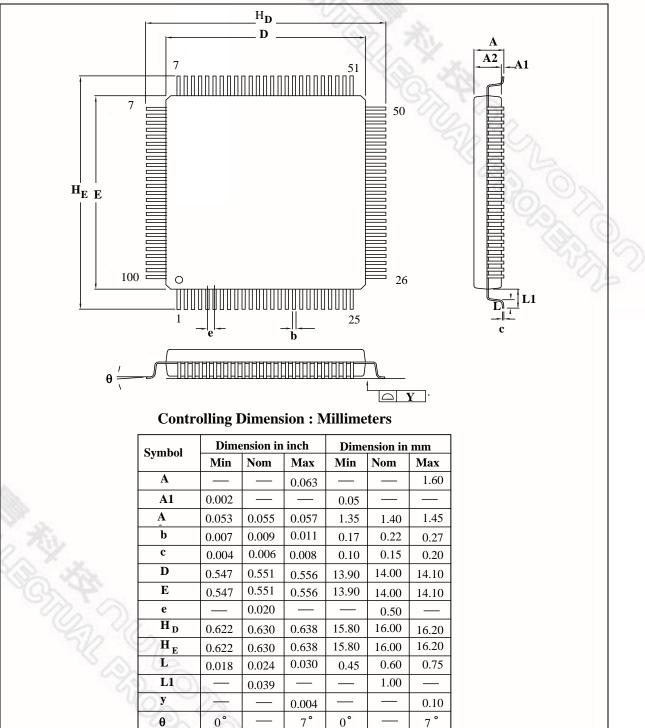

## 8 PACKAGE DIMENSIONS

## 8.1 100L LQFP (14x14x1.4 mm footprint 2.0mm)