Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Last Time Buy                                                                           |

|----------------------------|-----------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                      |

| Speed                      | 50MHz                                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 35                                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | -                                                                                       |

| RAM Size                   | 16K x 8                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                             |

| Data Converters            | A/D 8x12b                                                                               |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 48-LQFP                                                                                 |

| Supplier Device Package    | -                                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/nuc130le3cn |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

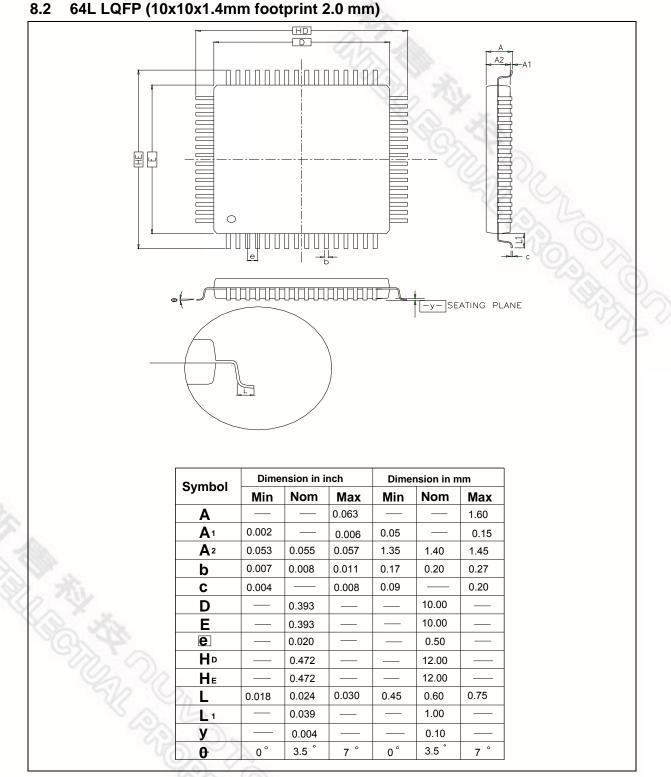

### Figures

| Figure 3-1 NuMicro™ NUC100 Series selection code      | 12 |

|-------------------------------------------------------|----|

| Figure 3-2 NuMicro™ NUC130 LQFP 100-pin Pin Diagram   | 13 |

| Figure 3-3 NuMicro™ NUC130 LQFP 64-pin Pin Diagram    | 14 |

| Figure 3-4 NuMicro™ NUC130 LQFP 48-pin Pin Diagram    | 15 |

| Figure 4-1 NuMicro™ NUC130 Block Diagram              |    |

| Figure 5-1 Functional Controller Diagram              | 17 |

| Figure 5-3 NuMicro™ NUC130 Power Distribution Diagram | 20 |

| Figure 5-4 Clock generator global view diagram        | 29 |

| Figure 5-5 Clock generator block diagram              |    |

| Figure 5-6 System Clock Block Diagram                 | 31 |

| Figure 5-7 SysTick Clock Control Block Diagram        |    |

| Figure 5-8 Clock Source of Frequency Divider          | 33 |

| Figure 5-9 Block Diagram of Frequency Divider         | 33 |

| Figure 5-10 I <sup>2</sup> C Bus Timing               | 35 |

| Figure 5-11 Timing of Interrupt and Reset Signal      | 43 |

| Figure 7-1 Typical Crystal Application Circuit        | 63 |

| Figure 7-2 SPI Master dynamic characteristics tiMINg  | 70 |

| Figure 7-3 SPI Slave dynamic characteristics timing   | 70 |

### **1 GENERAL DESCRIPTION**

The NuMicro<sup>™</sup> NUC100 Series is 32-bit microcontrollers with embedded ARM<sup>®</sup> Cortex<sup>™</sup>-M0 core for industrial control and applications which need rich communication interfaces. The Cortex<sup>™</sup>-M0 is the newest ARM<sup>®</sup> embedded processor with 32-bit performance and at a cost equivalent to traditional 8-bit microcontroller. NuMicro<sup>™</sup> NUC100 Series includes NUC100, NUC120, NUC130 and NUC140 product line.

The NuMicro<sup>™</sup> NUC130 Automotive Line with CAN function embeds Cortex<sup>™</sup>-M0 core running up to 50 MHz with 32K/64K/128K-byte embedded flash, 4K/8K/16K-byte embedded SRAM, and 4K-byte loader ROM for the ISP. It also equips with plenty of peripheral devices, such as Timers, Watchdog Timer, RTC, PDMA, UART, SPI, I<sup>2</sup>C, I<sup>2</sup>S, PWM Timer, GPIO, LIN, CAN, PS/2, 12-bit ADC, Analog Comparator, Low Voltage Reset Controller and Brown-out Detector.

| Product Line | UART | SPI | I <sup>2</sup> C | USB | LIN | CAN | PS/2 | l <sup>2</sup> S |    |

|--------------|------|-----|------------------|-----|-----|-----|------|------------------|----|

| NUC100       | •    | •   | •                |     |     |     | 0    | 100              |    |

| NUC120       | •    | •   | •                | •   |     |     | •    | •                | D. |

| NUC130       | •    | •   | •                |     | •   | •   | •    | N.               | 1  |

| NUC140       | •    | •   | •                | •   | •   | •   | •    | •                | 2  |

Table 1-1 Connectivity Supported Table

### 2 FEATURES

The equipped features are dependent on the product line and their sub products.

### 2.1 NuMicro<sup>™</sup> NUC130 Features – Automotive Line

- Core

- ARM<sup>®</sup> Cortex<sup>™</sup>-M0 core runs up to 50 MHz

- One 24-bit system timer

- Supports low power sleep mode

- Single-cycle 32-bit hardware multiplier

- NVIC for the 32 interrupt inputs, each with 4-levels of priority

- Serial Wire Debug supports with 2 watchpoints/4 breakpoints

- Build-in LDO for wide operating voltage ranges from 2.5 V to 5.5 V

- Flash Memory

- 32K/64K/128K bytes Flash for program code

- 4KB flash for ISP loader

- Support In-system program (ISP) application code update

- 512 byte page erase for flash

- Configurable data flash address and size for 128KB system, fixed 4KB data flash for the 32KB and 64KB system

- Support 2 wire ICP update through SWD/ICE interface

- Support fast parallel programming mode by external programmer

- SRAM Memory

- 4K/8K/16K bytes embedded SRAM

- Support PDMA mode

- PDMA (Peripheral DMA)

- Support 9 channels PDMA for automatic data transfer between SRAM and peripherals

- Clock Control

- Flexible selection for different applications

- Built-in 22.1184 MHz high speed OSC for system operation

- Trimmed to  $\pm$  1 % at +25 °C and V<sub>DD</sub> = 5 V

- Trimmed to  $\pm$  3 % at -40 °C ~ +85 °C and V<sub>DD</sub> = 2.5 V ~ 5.5 V

- Built-in 10 kHz low speed OSC for Watchdog Timer and Wake-up operation

- Support one PLL, up to 50 MHz, for high performance system operation

- External 4~24 MHz high speed crystal input for precise timing operation External 32.768 kHz low speed crystal input for RTC function and low power system operation

- GPIO

- Four I/O modes:

- Quasi bi-direction

- Push-Pull output

- Open-Drain output

- Input only with high impendence

- TTL/Schmitt trigger input selectable

- I/O pin can be configured as interrupt source with edge/level setting

- High driver and high sink IO mode support

### **5 FUNCTIONAL DESCRIPTION**

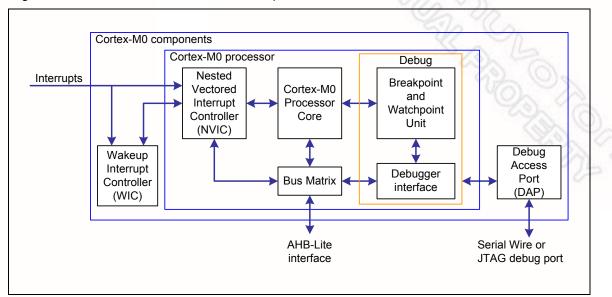

### 5.1 ARM<sup>®</sup> Cortex<sup>™</sup>-M0 Core

The Cortex<sup>™</sup>-M0 processor is a configurable, multistage, 32-bit RISC processor. It has an AMBA AHB-Lite interface and includes an NVIC component. It also has optional hardware debug functionality. The processor can execute Thumb code and is compatible with other Cortex-M profile processor. The profile supports two modes -Thread mode and Handler mode. Handler mode is entered as a result of an exception. An exception return can only be issued in Handler mode. Thread mode is entered on Reset, and can be entered as a result of an exception return. Figure 5-1 shows the functional controller of processor.

Figure 5-1 Functional Controller Diagram

The implemented device provides:

- A low gate count processor that features:

- The ARMv6-M Thumb® instruction set

- Thumb-2 technology

- ARMv6-M compliant 24-bit SysTick timer

- A 32-bit hardware multiplier

- The system interface supports little-endian data accesses

- The ability to have deterministic, fixed-latency, interrupt handling

- Load/store-multiples and multicycle-multiplies that can be abandoned and restarted to facilitate rapid interrupt handling

- C Application Binary Interface compliant exception model. This is the ARMv6-M, C Application Binary Interface (C-ABI) compliant exception model that enables the use of pure C functions as interrupt handlers

- Low power sleep mode entry using Wait For Interrupt (WFI), Wait For Event (WFE) instructions, or the return from interrupt sleep-on-exit feature

- NVIC that features:

- ♦ 32 external interrupt inputs, each with four levels of priority

- Dedicated Non-Maskable Interrupt (NMI) input.

- Support for both level-sensitive and pulse-sensitive interrupt lines

- Wake-up Interrupt Controller (WIC), providing ultra-low power sleep mode support.

- Debug support

- Four hardware breakpoints.

- Two watchpoints.

- Program Counter Sampling Register (PCSR) for non-intrusive code profiling.

- Single step and vector catch capabilities.

- Bus interfaces:

- Single 32-bit AMBA-3 AHB-Lite system interface that provides simple integration to all system peripherals and memory.

- Single 32-bit slave port that supports the DAP (Debug Access Port).

### 5.2 System Manager

#### 5.2.1 Overview

System management includes these following sections:

- System Resets

- System Memory Map

- System management registers for Part Number ID, chip reset and on-chip controllers reset, multi-functional pin control

- System Timer (SysTick)

- Nested Vectored Interrupt Controller (NVIC)

- System Control registers

### 5.2.2 System Reset

The system reset can be issued by one of the below listed events. For these reset event flags can be read by RSTSRC register.

- The Power-On Reset

- The low level on the /RESET pin

- Watchdog Time Out Reset

- Low Voltage Reset

- Brown-Out Detector Reset

- CPU Reset

- System Reset

System Reset and Power-On Reset all reset the whole chip including all peripherals. The difference between System Reset and Power-On Reset is external crystal circuit and ISPCON.BS bit. System Reset doesn't reset external crystal circuit and ISPCON.BS bit, but Power-On Reset does.

#### 5.2.5 System Timer (SysTick)

The Cortex-M0 includes an integrated system timer, SysTick. SysTick provides a simple, 24-bit clear-on-write, decrementing, wrap-on-zero counter with a flexible control mechanism. The counter can be used as a Real Time Operating System (RTOS) tick timer or as a simple counter.

When system timer is enabled, it will count down from the value in the SysTick Current Value Register (SYST\_CVR) to zero, and reload (wrap) to the value in the SysTick Reload Value Register (SYST\_RVR) on the next clock cycle, then decrement on subsequent clocks. When the counter transitions to zero, the COUNTFLAG status bit is set. The COUNTFLAG bit clears on reads.

The SYST\_CVR value is UNKNOWN on reset. Software should write to the register to clear it to zero before enabling the feature. This ensures the timer will count from the SYST\_RVR value rather than an arbitrary value when it is enabled.

If the SYST\_RVR is zero, the timer will be maintained with a current value of zero after it is reloaded with this value. This mechanism can be used to disable the feature independently from the timer enable bit.

For more detailed information, please refer to the documents "ARM<sup>®</sup> Cortex<sup>™</sup>-M0 Technical Reference Manual" and "ARM<sup>®</sup> v6-M Architecture Reference Manual".

|            | Syster    | m clock = intern | al 22.1184 M                          | Hz high speed o                           | scillator |             |  |

|------------|-----------|------------------|---------------------------------------|-------------------------------------------|-----------|-------------|--|

| Baud rate  | М         | ode0             | М                                     | ode1                                      | Mode2     |             |  |

| Budd fullo | Parameter | Register         | Parameter                             | Register                                  | Parameter | Register    |  |

| 230400     | A=4       | 0x0000_0004      | A=4,B=15<br>A=6,B=11                  | 0x2F00_0004<br>0x2B00_0006                | A=94      | 0x3000_005E |  |

| 115200     | A=10      | 0x0000_000A      | A=10,B=15<br>A=14,B=11                | 0x2F00_000A<br>0x2B00_000E                | A=190     | 0x3000_00BE |  |

| 57600      | A=22      | 0x0000_0016      | A=22,B=15<br>A=30,B=11                | 0x2F00_0016<br>0x2B00_001E                | A=382     | 0x3000_017E |  |

| 38400      | A=34      | 0x0000_0022      | A=62,B=8<br>A=46,B=11<br>A=34,B=15    | 0x2800_003E<br>0x2B00_002E<br>0x2F00_0022 | A=574     | 0x3000_023E |  |

| 19200      | A=70      | 0x0000_0046      | A=126,B=8<br>A=94,B=11<br>A=70,B=15   | 0x2800_007E<br>0x2B00_005E<br>0x2F00_0046 | A=1150    | 0x3000_047E |  |

| 9600       | A=142     | 0x0000_008E      | A=254,B=8<br>A=190,B=11<br>A=142,B=15 | 0x2800_00FE<br>0x2B00_00BE<br>0x2F00_008E | A=2302    | 0x3000_08FE |  |

| 4800       | A=286     | 0x0000_011E      | A=510,B=8<br>A=382,B=11<br>A=286,B=15 | 0x2800_01FE<br>0x2B00_017E<br>0x2F00_011E | A=4606    | 0x3000_11FE |  |

Table 5-7 UART Baud Rate Setting Table

The UART0 and UART1 controllers support auto-flow control function that uses two low-level signals, /CTS (clear-to-send) and /RTS (request-to-send), to control the flow of data transfer between the UART and external devices (ex: Modem). When auto-flow is enabled, the UART is not allowed to receive data until the UART asserts /RTS to external device. When the number of bytes in the RX FIFO equals the value of RTS\_TRI\_LEV (UA\_FCR [19:16]), the /RTS is deasserted. The UART sends data out when UART controller detects /CTS is asserted from external device. If a valid asserted /CTS is not detected the UART controller will not send data out.

The UART controllers also provides Serial IrDA (SIR, Serial Infrared) function (User must set IrDA\_EN (UA\_FUN\_SEL [1]) to enable IrDA function). The SIR specification defines a short-range infrared asynchronous serial transmission mode with one start bit, 8 data bits, and 1 stop bit. The maximum data rate is 115.2 Kbps (half duplex). The IrDA SIR block contains an IrDA SIR Protocol encoder/decoder. The IrDA SIR protocol is half-duplex only. So it cannot transmit and receive data at the same time. The IrDA SIR physical layer specifies a minimum 10ms transfer delay between transmission and reception. This delay feature must be implemented by software.

The alternate function of UART controllers is LIN (Local Interconnect Network) function. The LIN mode is selected by setting the UA\_FUN\_SEL[1:0] to '01'. In LIN mode, one start bit and 8-bit data format with 1-bit stop bit are required in accordance with the LIN standard.

For NuMicro<sup>™</sup> NUC100 Series, another alternate function of UART controllers is RS-485 9-bit mode function, and direction control provided by RTS pin or can program GPIO (PB.2 for RTS0 and PB.6 for RTS1) to implement the function by software. The RS-485 mode is selected by setting the UA\_FUN\_SEL register to select RS-485 function. The RS-485 driver control is implemented using the RTS control signal from an asynchronous serial port to enable the RS-485 driver. In RS-485 mode, many characteristics of the RX and TX are same as UART.

### 5.15 Analog-to-Digital Converter (ADC)

#### 5.15.1 Overview

NuMicro<sup>™</sup> NUC100 Series contains one 12-bit successive approximation analog-to-digital converters (SAR A/D converter) with 8 input channels. The A/D converter supports three operation modes: single, single-cycle scan and continuous scan mode. The A/D converters can be started by software and external STADC pin.

#### 5.15.2 Features

- Analog input voltage range: 0~V<sub>REF</sub>

- 12-bit resolution and 10-bit accuracy is guaranteed

- Up to 8 single-end analog input channels or 4 differential analog input channels

- Maximum ADC clock frequency is 16 MHz

- Up to 700K SPS conversion rate

- Three operating modes

- Single mode: A/D conversion is performed one time on a specified channel

- Single-cycle scan mode: A/D conversion is performed one cycle on all specified channels with the sequence from the lowest numbered channel to the highest numbered channel

- Continuous scan mode: A/D converter continuously performs Single-cycle scan mode until software stops A/D conversion

- An A/D conversion can be started by

- Software write 1 to ADST bit

- External pin STADC

- Conversion results are held in data registers for each channel with valid and overrun indicators

- Conversion result can be compared with specify value and user can select whether to generate an interrupt when conversion result is equal to the compare register setting

- Channel 7 supports 3 input sources: external analog voltage, internal bandgap voltage, and internal temperature sensor output

- Support Self-calibration to minimize conversion error

### 5.16 Analog Comparator (CMP)

#### 5.16.1 Overview

NuMicro<sup>™</sup> NUC100 Series contains two comparators. The comparators can be used in a number of different configurations. The comparator output is a logical one when positive input greater than negative input, otherwise the output is a zero. Each comparator can be configured to cause an interrupt when the comparator output value changes. The block diagram is shown in **Error! Reference source not found.**

#### 5.16.2 Features

- Analog input voltage range: 0~5.0 V

- Hysteresis function supported

- Two analog comparators with optional internal reference voltage input at negative end

- One interrupt vector for both comparators

### 5.17 PDMA Controller (PDMA)

#### 5.17.1 Overview

NuMicro<sup>™</sup> NUC130/NUC140 contains a peripheral direct memory access (PDMA) controller that transfers data to and from memory or transfer data to and from APB devices. The PDMA has nine channels of DMA (Peripheral-to-Memory or Memory-to-Peripheral or Memory-to-Memory). For each PDMA channel (PDMA CH0~CH8), there is one word buffer as transfer buffer between the Peripherals APB devices and Memory.

Software can stop the PDMA operation by disable PDMA [PDMACEN]. The CPU can recognize the completion of a PDMA operation by software polling or when it receives an internal PDMA interrupt. The PDMA controller can increase source or destination address or fixed them as well.

Notice: The partial of NuMicro<sup>™</sup> NUC130/NUC140 only has 1 PDMA channel (channel 0).

#### 5.17.2 Features

- Support nine DMA channels. Each channel can support a unidirectional transfer

- AMBA AHB master/slave interface compatible, for data transfer and register read/write

- Support source and destination address increased mode or fixed mode

- Hardware channel priority. DMA channel 0 has the highest priority and channel 8 has the lowest priority

### 7.2 DC Electrical Characteristics

### 7.2.1 NuMicro™ NUC130/NUC140 DC Electrical Characteristics

(V<sub>DD</sub>-V<sub>SS</sub>=3.3 V, TA = 25°C, FOSC = 50 MHz unless otherwise specified.)

| PARAMETER                                        | SYM                                 | SYM. |      | CATION           |      | TEST CONDITIONS                                                                   |

|--------------------------------------------------|-------------------------------------|------|------|------------------|------|-----------------------------------------------------------------------------------|

| FARAMETER                                        | STW.                                | MIN. | TYP. | MAX.             | UNIT |                                                                                   |

| Operation voltage                                | V <sub>DD</sub>                     | 2.5  |      | 5.5              | v    | V <sub>DD</sub> =2.5 V ~ 5.5 V up to 50 MHz                                       |

| Power Ground                                     | V <sub>SS</sub><br>AV <sub>SS</sub> | -0.3 |      |                  | V    | R CL                                                                              |

| LDO Output Voltage                               | $V_{LDO}$                           | -10% | 2.5  | +10%             | V    | V <sub>DD</sub> > 2.7 V                                                           |

| Analog Operating Voltage                         | AV <sub>DD</sub>                    | 0    |      | V <sub>DD</sub>  | V    |                                                                                   |

| Analog Reference Voltage                         | Vref                                | 0    |      | AV <sub>DD</sub> | V    | 0                                                                                 |

|                                                  |                                     |      |      |                  |      | V <sub>DD</sub> = 5.5 V@50 MHz,                                                   |

|                                                  | I <sub>DD1</sub>                    |      | 51   |                  |      | enable all IP and PLL, XTAL=12<br>MHz                                             |

| Operating Current                                | I <sub>DD2</sub>                    |      | 25   |                  | mA   | $V_{DD}$ = 5.5 V@50 MHz,<br>disable all IP and enable PLL,<br>XTAL=12 MHz         |

| Normal Run Mode<br>@ 50 MHz                      | I <sub>DD3</sub>                    |      | 48   |                  |      | V <sub>DD</sub> = 3 V@50 MHz,<br>enable all IP and PLL, XTAL=12<br>MHz            |

| 流                                                | I <sub>DD4</sub>                    |      | 23   |                  | mA   | $V_{DD}$ = 3 V@50 MHz,<br>disable all IP and enable PLL,<br>XTAL=12 MHz           |

| Operating Current<br>Normal Run Mode<br>@ 12 MHz | I <sub>DD5</sub>                    |      | 19   |                  | mA   | V <sub>DD</sub> = 5.5 V@12 MHz,<br>enable all IP and disable PLL,<br>XTAL=12 MHz  |

|                                                  | I <sub>DD6</sub>                    |      | 7    |                  |      | V <sub>DD</sub> = 5.5 V@12 MHz,<br>disable all IP and disable PLL,<br>XTAL=12 MHz |

| No.                                              | I <sub>DD7</sub>                    |      | 17   |                  | mA   | $V_{DD}$ = 3 V@12 MHz,<br>enable all IP and disable PLL,<br>XTAL=12 MHz           |

| DADAMETED                                                              | SPECIFICATION                  |      | TEST CONDITIONS |                         |      |                                                                                 |  |

|------------------------------------------------------------------------|--------------------------------|------|-----------------|-------------------------|------|---------------------------------------------------------------------------------|--|

| PARAMETER                                                              | 5111.                          | MIN. | TYP.            | MAX.                    | UNIT |                                                                                 |  |

|                                                                        | I <sub>IDLE8</sub>             |      | 3.5             |                         | mA   | V <sub>DD</sub> = 3 V@12 MHz,<br>disable all IP and disable PLL,<br>XTAL=12 MHz |  |

|                                                                        | I <sub>IDLE9</sub>             |      | 4               | Q                       | 2.   | V <sub>DD</sub> = 5 V@4 MHz,<br>enable all IP and disable PLL,<br>XTAL=4 MHz    |  |

| Operating Current                                                      | I <sub>IDLE10</sub>            |      | 2.5             |                         | mA   | V <sub>DD</sub> = 5 V@4 MHz,<br>disable all IP and disable PLL,<br>XTAL=4 MHz   |  |

| Idle Mode<br>@ 4 MHz                                                   | I <sub>IDLE11</sub>            |      | 3.5             |                         | mA   | V <sub>DD</sub> = 3 V@4 MHz,<br>enable all IP and disable PLL,<br>XTAL=4 MHz    |  |

|                                                                        | I <sub>IDLE12</sub>            |      | 1.5             |                         | mA   | V <sub>DD</sub> = 3 V@4 MHz,<br>disable all IP and disable PLL,<br>XTAL=4 MHz   |  |

|                                                                        | I <sub>PWD1</sub>              |      | 12              |                         | μA   | V <sub>DD</sub> = 5.5 V, RTC OFF, No load<br>@ Disable BOV function             |  |

| Standby Current                                                        | I <sub>PWD2</sub>              |      | 9               |                         | μΑ   | V <sub>DD</sub> = 3.3 V, RTC OFF, No load<br>@ Disable BOV function             |  |

| Power down Mode                                                        | I <sub>PWD3</sub>              |      |                 |                         | μΑ   | V <sub>DD</sub> = 5.5 V, RTC run , No load<br>@ Disable BOV function            |  |

|                                                                        | I <sub>PWD4</sub>              |      |                 |                         | μA   | V <sub>DD</sub> = 3.3 V, RTC run , No load<br>@ Disable BOV function            |  |

| Input Current PA, PB, PC,<br>PD, PE (Quasi-bidirectional<br>mode)      | I <sub>IN1</sub>               |      | -50             | -60                     | μΑ   | $V_{DD}$ = 5.5 V, $V_{IN}$ = 0 V or $V_{IN}$ = $V_{DI}$                         |  |

| Input Current at /RESET <sup>[1]</sup>                                 | I <sub>IN2</sub>               | -55  | -45             | -30                     | μA   | V <sub>DD</sub> = 3.3 V, V <sub>IN</sub> = 0.45 V                               |  |

| Input Leakage Current PA,<br>PB, PC, PD, PE                            | I <sub>LK</sub>                | -2   | -               | +2                      | μA   | V <sub>DD</sub> = 5.5 V, 0 <v<sub>IN<v<sub>DD</v<sub></v<sub>                   |  |

| Logic 1 to 0 Transition Current<br>PA~PE (Quasi-bidirectional<br>mode) | I <sub>TL</sub> <sup>[3]</sup> | -650 | -               | -200                    | μΑ   | V <sub>DD</sub> = 5.5 V, V <sub>IN</sub> <2.0 V                                 |  |

| Input Low Voltage PA, PB,                                              | V <sub>IL1</sub>               | -0.3 | -               | 0.8                     | v    | V <sub>DD</sub> = 4.5 V                                                         |  |

| PC, PD, PE (TTL input)                                                 | v IL1                          | -0.3 | -               | 0.6                     | v    | V <sub>DD</sub> = 2.5 V                                                         |  |

| Input High Voltage PA, PB,                                             | V <sub>IH1</sub>               | 2.0  | -               | V <sub>DD</sub><br>+0.2 | V    | V <sub>DD</sub> = 5.5 V                                                         |  |

| PC, PD, PE (TTL input)                                                 | v IH1                          | 1.5  | -               | V <sub>DD</sub><br>+0.2 | v    | V <sub>DD</sub> =3.0 V                                                          |  |

| Input Low Voltage PA, PB,<br>PC, PD, PE (Schmitt input)                | V <sub>IL2</sub>               | -0.5 | -               | 0.3 V <sub>DD</sub>     | v    |                                                                                 |  |

| PARAMETER       | SYM.     | w    | SPECIFIC | CATION |      | TEST CONDITIONS               |

|-----------------|----------|------|----------|--------|------|-------------------------------|

|                 | ••••     | MIN. | TYP.     | MAX.   | UNIT |                               |

| Bandgap voltage | $V_{BG}$ | 1.20 | 1.26     | 1.32   | V    | V <sub>DD</sub> = 2.5 V~5.5 V |

Note:

1. /RESET pin is a Schmitt trigger input.

2. Crystal Input is a CMOS input.

3. Pins of PA, PB, PC, PD and PE can source a transition current when they are being externally driven from 1 to 0. In the condition of  $V_{DD}$ =5.5 V, 5he transition current reaches its maximum value when  $V_{IN}$  approximates to 2 V.

Figure 7-1 Typical Crystal Application Circuit

### 7.3.3 External 32.768 kHz Low Speed Crystal

| PARAMETER             | CONDITION        | MIN. | TYP.   | MAX. | UNIT |

|-----------------------|------------------|------|--------|------|------|

| Input clock frequency | External crystal | -    | 32.768 | -    | kHz  |

| Temperature           | - X2             | -40  | -      | 85   | °C   |

| V <sub>DD</sub>       |                  | 2.5  | - Z    | 5.5  | V    |

### 7.3.4 Internal 22.1184 MHz High Speed Oscillator

| PARAMETER                                | CONDITION                                    | MIN. | TYP.    | MAX. | UNIT |  |  |  |

|------------------------------------------|----------------------------------------------|------|---------|------|------|--|--|--|

| Supply voltage <sup>[1]</sup>            | -                                            | 2.5  | -93     | 5.5  | V    |  |  |  |

| Center Frequency                         | -                                            | -    | 22.1184 | Ya.  | MHz  |  |  |  |

|                                          | +25℃; V <sub>DD</sub> =5 V                   | -1   | -       | +1   | %    |  |  |  |

| Calibrated Internal Oscillator Frequency | -40°C~+85°C;<br>V <sub>DD</sub> =2.5 V~5.5 V | -3   | -       | +3   | %    |  |  |  |

| Operation Current                        | V <sub>DD</sub> =5 V                         | -    | 500     | -    | uA   |  |  |  |

### 7.3.5 Internal 10 kHz Low Speed Oscillator

| PARAMETER                                | CONDITION                                    | MIN. | TYP. | MAX. | UNIT |

|------------------------------------------|----------------------------------------------|------|------|------|------|

| Supply voltage <sup>[1]</sup>            | -                                            | 2.5  | -    | 5.5  | V    |

| Center Frequency                         | -                                            | -    | 10   | -    | kHz  |

|                                          | +25℃; V <sub>DD</sub> =5 V                   | -30  | -    | +30  | %    |

| Calibrated Internal Oscillator Frequency | -40°C~+85°C;<br>V <sub>DD</sub> =2.5 V~5.5 V | -50  | -    | +50  | %    |

Note: Internal operation voltage comes from LDO.

### 7.4 Analog Characteristics

### 7.4.1 Specification of 12-bit SARADC

| SYMBOL           | PARAMETER                                     | MIN. | TYP.             | MAX.             | UNIT  |

|------------------|-----------------------------------------------|------|------------------|------------------|-------|

| -                | Resolution                                    | S-   | -                | 12               | Bit   |

| DNL              | Differential nonlinearity error               | 1-36 | ±3               | -                | LSB   |

| INL              | Integral nonlinearity error                   | 1.18 | ±4               | -                | LSB   |

| EO               | Offset error                                  | C)   | ±1               | 10               | LSB   |

| EG               | Gain error (Transfer gain)                    | -21  | 21               | 1.005            | -     |

| -                | Monotonic                                     | (    | Guarantee        | d                |       |

| FADC             | ADC clock frequency (AV <sub>DD</sub> =5V/3V) | -    | -21              | 16/8             | MHz   |

| FS               | Sample rate                                   | -    | - 1              | 700              | K SPS |

| V <sub>DDA</sub> | Supply voltage                                | 3    | -                | 5.5              | V     |

| I <sub>DD</sub>  | Supply current (Avg.)                         | -    | 0.5              | -                | mA    |

| I <sub>DDA</sub> | Supply current (Avg.)                         | -    | 1.5              | -                | mA    |

| $V_{REF}$        | Reference voltage                             | -    | V <sub>DDA</sub> | -                | V     |

| I <sub>REF</sub> | Reference current (Avg.)                      | -    | 1                | -                | mA    |

| V <sub>IN</sub>  | Input voltage                                 | 0    | -                | V <sub>REF</sub> | V     |

| SYMBOL          | PARAMETER                                        | MIN.       | TYP.      | MAX.      | UNIT |

|-----------------|--------------------------------------------------|------------|-----------|-----------|------|

| SPI master mod  | e (V <sub>DD</sub> = 4.5V ~ 5.5V, 30pF loading ( | Capacitor) | 9 .       |           |      |

| t <sub>DS</sub> | Data setup time                                  | 4          | 2         | -         | ns   |

| t <sub>DH</sub> | Data hold time                                   | 0          | a so      | -         | ns   |

| t <sub>v</sub>  | Data output valid time                           | -          | C7        | 11        | ns   |

| SPI master mod  | e (V <sub>DD</sub> = 3.0V ~ 3.6V, 30pF loading ( | Capacitor) | ° OL      | Dr.       |      |

| t <sub>DS</sub> | Data setup time                                  | 5          | 3         | 2 Sh      | ns   |

| t <sub>DH</sub> | Data hold time                                   | 0          | -         | 2. 6      | ns   |

| t <sub>v</sub>  | Data output valid time                           | -          | 13        | 18        | ns   |

| SPI slave mode  | (V <sub>DD</sub> = 4.5V ~ 5.5V, 30pF loading Ca  | apacitor)  |           | 20        | 20   |

| t <sub>DS</sub> | Data setup time                                  | 0          | -         | - 53      | ns   |

| t <sub>DH</sub> | Data hold time                                   | 2*PCLK+4   | -         | -         | ns   |

| t <sub>v</sub>  | Data output valid time                           | -          | 2*PCLK+11 | 2*PCLK+19 | ns   |

| SPI slave mode  | (V <sub>DD</sub> = 3.0V ~ 3.6V, 30pF loading Ca  | apacitor)  |           |           |      |

| t <sub>DS</sub> | Data setup time                                  | 0          | -         | -         | ns   |

| t <sub>DH</sub> | Data hold time                                   | 2*PCLK+6   | -         | -         | ns   |

| t <sub>v</sub>  | Data output valid time                           | _          | 2*PCLK+19 | 2*PCLK+25 | ns   |

|                 |                                                  | 2*PCLK+6   |           |           | n    |

#### SPI Dynamic Characteristics 7.6

### 9 REVISION HISTORY

| VERSION | DATE          | PAGE/<br>CHAP. | DESCRIPTION                                                                                                                                                                 |

|---------|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V1.00   | March 1, 2010 | -              | Preliminary version initial issued                                                                                                                                          |

| V1.01   | April 9, 2010 | Ch4            | Modify the block diagram                                                                                                                                                    |

| V1.02   | May 31, 2010  | 7.2            | Add operation current of DC characteristics                                                                                                                                 |

| V1.03   | Aug. 23, 2010 | 7.2            | Modify operation current of DC characteristics                                                                                                                              |

| V2.00   | Nov. 11, 2010 | -              | Update low density and selection table                                                                                                                                      |

| V3.00   | May 6, 2011   | All            | Revise from NUC130XXXAN or NUC130XXXBN to NUC130XXXCN<br>Revise NUC130 selection guide<br>Revise Functional Description<br>Revise DC Electrical Characteristics             |

| V3.01   | June 22, 2011 | -              | modify temperature sensor spec<br>Revise Pin description position for multi-function T2EX, T3EX, nRD, nWR<br>update title of SPI Dynamic Characteristics<br>update BOD spec |

| V3.02   | Jan. 2, 2012  | -              | <ol> <li>Remove feature "Dynamic priority changing" for NVIC</li> <li>Modify ADC analog characteristic spec</li> <li>Remove SPI FIFO mode</li> </ol>                        |

#### **Important Notice**

Nuvoton Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, "Insecure Usage".

Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, the control or operation of dynamic, brake or safety systems designed for vehicular use, traffic signal instruments, all types of safety devices, and other applications intended to support or sustain life.

All Insecure Usage shall be made at customer's risk, and in the event that third parties lay claims to Nuvoton as a result of customer's Insecure Usage, customer shall indemnify the damages and liabilities thus incurred by Nuvoton.

Please note that all data and specifications are subject to change without notice. All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.

> Publication Release Date: Jan. 2, 2012 Revision V3.02