Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Last Time Buy                                                                           |

|----------------------------|-----------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                      |

| Speed                      | 50MHz                                                                                   |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                            |

| Number of I/O              | 49                                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | -                                                                                       |

| RAM Size                   | 16K x 8                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                             |

| Data Converters            | A/D 8x12b                                                                               |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 64-LQFP                                                                                 |

| Supplier Device Package    | -                                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/nuc130re3cn |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2 FEATURES

The equipped features are dependent on the product line and their sub products.

### 2.1 NuMicro™ NUC130 Features – Automotive Line

- Core

- ARM<sup>®</sup> Cortex<sup>™</sup>-M0 core runs up to 50 MHz

- One 24-bit system timer

- Supports low power sleep mode

- Single-cycle 32-bit hardware multiplier

- NVIC for the 32 interrupt inputs, each with 4-levels of priority

- Serial Wire Debug supports with 2 watchpoints/4 breakpoints

- Build-in LDO for wide operating voltage ranges from 2.5 V to 5.5 V

- Flash Memory

- 32K/64K/128K bytes Flash for program code

- 4KB flash for ISP loader

- Support In-system program (ISP) application code update

- 512 byte page erase for flash

- Configurable data flash address and size for 128KB system, fixed 4KB data flash for the 32KB and 64KB system

- Support 2 wire ICP update through SWD/ICE interface

- Support fast parallel programming mode by external programmer

- SRAM Memory

- 4K/8K/16K bytes embedded SRAM

- Support PDMA mode

- PDMA (Peripheral DMA)

- Support 9 channels PDMA for automatic data transfer between SRAM and peripherals

- Clock Control

- Flexible selection for different applications

- Built-in 22.1184 MHz high speed OSC for system operation

- Trimmed to  $\pm$  1 % at +25 °C and V<sub>DD</sub> = 5 V

- Trimmed to  $\pm$  3 % at -40 °C ~ +85 °C and V<sub>DD</sub> = 2.5 V ~ 5.5 V

- Built-in 10 kHz low speed OSC for Watchdog Timer and Wake-up operation

- Support one PLL, up to 50 MHz, for high performance system operation

- External 4~24 MHz high speed crystal input for precise timing operation External 32.768 kHz low speed crystal input for RTC function and low power system operation

- GPIO

- Four I/O modes:

- Quasi bi-direction

- Push-Pull output

- Open-Drain output

- Input only with high impendence

- TTL/Schmitt trigger input selectable

- I/O pin can be configured as interrupt source with edge/level setting

- High driver and high sink IO mode support

- Timer

- Support 4 sets of 32-bit timers with 24-bit up-timer and one 8-bit pre-scale counter

- Independent clock source for each timer

- Provides one-shot, periodic, toggle and continuous counting operation modes

- Support event counting function

- Support input capture function

- Watchdog Timer

- Multiple clock sources

- 8 selectable time out period from 1.6ms ~ 26.0sec (depends on clock source)

- WDT can wake-up from power down or idle mode

- Interrupt or reset selectable on watchdog time-out

- RTC

- Support software compensation by setting frequency compensate register (FCR)

- Support RTC counter (second, minute, hour) and calendar counter (day, month, year)

- Support Alarm registers (second, minute, hour, day, month, year)

- Selectable 12-hour or 24-hour mode

- Automatic leap year recognition

- Support periodic time tick interrupt with 8 period options 1/128, 1/64, 1/32, 1/16, 1/8, 1/4, 1/2 and 1 second

- Support wake-up function

- PWM/Capture

- Built-in up to four 16-bit PWM generators provide eight PWM outputs or four complementary paired PWM outputs

- Each PWM generator equipped with one clock source selector, one clock divider, one 8-bit prescaler and one Dead-Zone generator for complementary paired PWM

- Up to eight 16-bit digital Capture timers (shared with PWM timers) provide eight rising/falling capture inputs

- Support Capture interrupt

- UART

- Up to three UART controllers

- UART ports with flow control (TXD, RXD, CTS and RTS)

- UART0 with 64-byte FIFO is for high speed

- UART1/2(optional) with 16-byte FIFO for standard device

- Support IrDA (SIR) and LIN function

- Support RS-485 9-bit mode and direction control.

- Programmable baud-rate generator up to 1/16 system clock

- Support PDMA mode

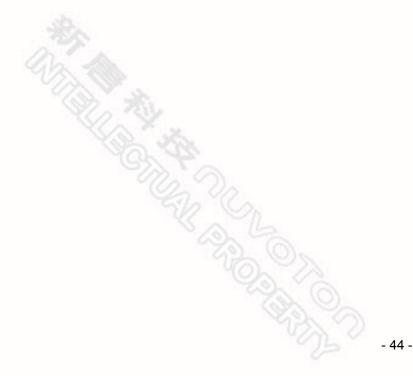

- SPI

- Up to four sets of SPI controller

- Master up to 32 MHz, and Slave up to 10 MHz (chip working @ 5V)

- Support SPI master/slave mode

- Full duplex synchronous serial data transfer

- Variable length of transfer data from 1 to 32 bits

- MSB or LSB first data transfer

- Rx and Tx on both rising or falling edge of serial clock independently

- 2 slave/device select lines when it is as the master, and 1 slave/device select line when it is as the slave

- Support byte suspend mode in 32-bit transmission

- Support PDMA mode

- Support three wire, no slave select signal, bi-direction interface

- I<sup>2</sup>C

- Up to two sets of I<sup>2</sup>C device

- Master/Slave mode

- Bidirectional data transfer between masters and slaves

- Multi-master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer

- Programmable clocks allow versatile rate control

- Support multiple address recognition (four slave address with mask option)

- I<sup>2</sup>S

- Interface with external audio CODEC

- Operate as either master or slave mode

- Capable of handling 8-, 16-, 24- and 32-bit word sizes

- Mono and stereo audio data supported

- I<sup>2</sup>S and MSB justified data format supported

- Two 8 word FIFO data buffers are provided, one for transmit and one for receive

- Generates interrupt requests when buffer levels cross a programmable boundary

- Support two DMA requests, one for transmit and one for receive

- PS/2 Device Controller

- Host communication inhibit and request to send detection

- Reception frame error detection

- Programmable 1 to 16 bytes transmit buffer to reduce CPU intervention

- Double buffer for data reception

- S/W override bus

- CAN 2.0

- Supports CAN protocol version 2.0 part A and B

- Bit rates up to 1M bit/s

- 32 Message Objects

- Each Message Object has its won identifier mask

- Programmable FIFO mode (concatenation of Message Object)

- Maskable interrupt

- Disabled Automatic Re-transmission mode for Time Triggered CAN applications

- Support power down wake-up function

- EBI (External bus interface) support (100-pin and 64-pin Package Only)

- Accessible space: 64KB in 8-bit mode or 128KB in 16-bit mode

- Support 8-/16-bit data width

- Support byte write in 16-bit data width mode

- ADC

- 12-bit SAR ADC with 700K SPS

- Up to 8-ch single-end input or 4-ch differential input

- Single scan/single cycle scan/continuous scan

- Each channel with individual result register

- Scan on enabled channels

- Threshold voltage detection

- Conversion start by software programming or external input

- Support PDMA mode

- Analog Comparator

- Up to two analog comparator

- External input or internal bandgap voltage selectable at negative node

- Interrupt when compare result change

- Power down wake-up

- One built-in temperature sensor with  $1\,{}^\circ\!\mathrm{C}$  resolution

- Brown-Out detector

- With 4 levels: 4.5 V/3.8 V/2.7 V/2.2 V

- Support Brown-Out Interrupt and Reset option

- Low Voltage Reset

- Threshold voltage levels: 2.0 V

- Operating Temperature: -40°C ~85°C

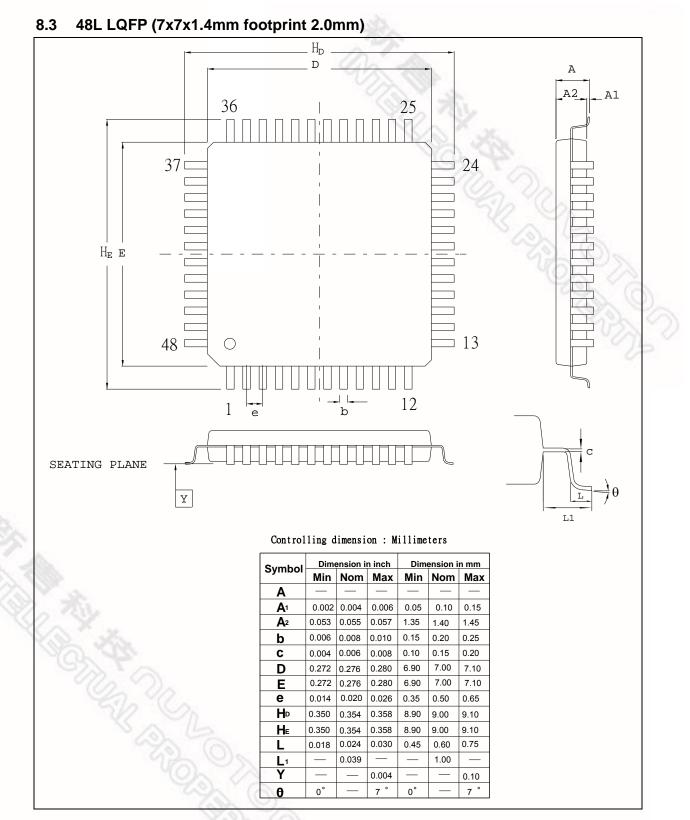

- Packages:

- All Green package (RoHS)

- LQFP 100-pin / 64-pin / 48-pin

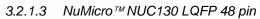

3.2.1.2 NuMicro™NUC130 LQFP 64 pin

Figure 3-3 NuMicro™ NUC130 LQFP 64-pin Pin Diagram

Publication Release Date: Jan. 2, 2012 Revision V3.02

### 5.2 System Manager

#### 5.2.1 Overview

System management includes these following sections:

- System Resets

- System Memory Map

- System management registers for Part Number ID, chip reset and on-chip controllers reset, multi-functional pin control

- System Timer (SysTick)

- Nested Vectored Interrupt Controller (NVIC)

- System Control registers

#### 5.2.2 System Reset

The system reset can be issued by one of the below listed events. For these reset event flags can be read by RSTSRC register.

- The Power-On Reset

- The low level on the /RESET pin

- Watchdog Time Out Reset

- Low Voltage Reset

- Brown-Out Detector Reset

- CPU Reset

- System Reset

System Reset and Power-On Reset all reset the whole chip including all peripherals. The difference between System Reset and Power-On Reset is external crystal circuit and ISPCON.BS bit. System Reset doesn't reset external crystal circuit and ISPCON.BS bit, but Power-On Reset does.

#### 5.3 Clock Controller

#### 5.3.1 Overview

The clock controller generates the clocks for the whole chip, including system clocks and all peripheral clocks. The clock controller also implements the power control function with the individually clock ON/OFF control, clock source selection and a clock divider. The chip will not enter power down mode until CPU sets the power down enable bit (PWR\_DOWN\_EN) and Cortex-M0 core executes the WFI instruction. After that, chip enter power down mode and wait for wake-up interrupt source triggered to leave power down mode. In the power down mode, the clock controller turns off the external 4~24 MHz high speed crystal and internal 22.1184 MHz high speed oscillator to reduce the overall system power consumption.

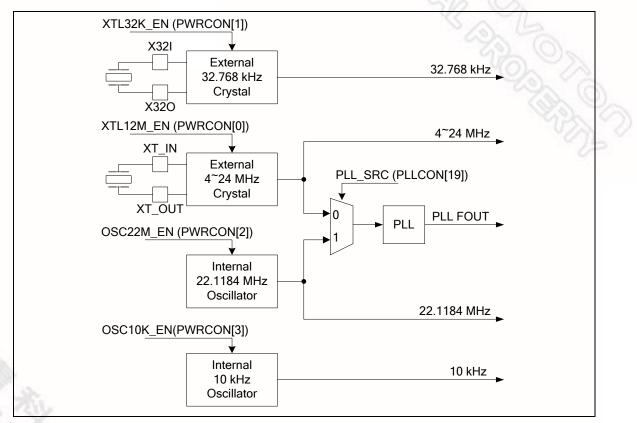

#### 5.3.2 Clock Generator

The clock generator consists of 5 clock sources which are listed below:

- One external 32.768 kHz low speed crystal

- One external 4~24 MHz high speed crystal

- One programmable PLL FOUT(PLL source consists of external 4~24 MHz high speed crystal and internal 22.1184 MHz high speed oscillator)

- One internal 22.1184 MHz high speed oscillator

- One internal 10 kHz low speed oscillator

#### 5.5.2 Features

The I<sup>2</sup>C bus uses two wires (SDA and SCL) to transfer information between devices connected to the bus. The main features of the bus are:

- Master/Slave mode

- Bidirectional data transfer between masters and slaves

- Multi-master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer

- Built-in a 14-bit time-out counter will request the I<sup>2</sup>C interrupt if the I<sup>2</sup>C bus hangs up and timer-out counter overflows.

- External pull-up are needed for high output

- Programmable clocks allow versatile rate control

- Supports 7-bit addressing mode

- I<sup>2</sup>C-bus controllers support multiple address recognition (Four slave address with mask option)

#### 5.10.2 Features

- 18-bit free running counter to avoid chip from Watchdog timer reset before the delay time expires.

- Selectable time-out interval (2<sup>4</sup> ~ 2<sup>18</sup>) and the time out interval is 104 ms ~ 26.3168 s (if WDT\_CLK = 10 kHz).

- Reset period = (1 / 10 kHz) \* 63, if WDT\_CLK = 10 kHz.

## nuvoton

### 5.11 UART Interface Controller (UART)

NuMicro™ NUC130/NUC140 provides up to three channels of Universal Asynchronous Receiver/Transmitters (UART). UART0 supports High Speed UART and UART1~2 perform Normal Speed UART, besides, only UART0 and UART1 support flow control function.

#### 5.11.1 Overview

The Universal Asynchronous Receiver/Transmitter (UART) performs a serial-to-parallel conversion on data received from the peripheral, and a parallel-to-serial conversion on data transmitted from the CPU. The UART controller also supports IrDA SIR Function, LIN master/slave mode function and RS-485 mode functions. Each UART channel supports seven types of interrupts including transmitter FIFO empty interrupt (INT THRE), receiver threshold level reaching interrupt (INT RDA), line status interrupt (parity error or framing error or break interrupt) (INT RLS), receiver buffer time out interrupt (INT TOUT), MODEM/Wake-up status interrupt (INT MODEM), Buffer error interrupt (INT BUF ERR) and LIN receiver break field detected interrupt (INT LIN RX BREAK). Interrupts of UART0 and UART2 share the interrupt number 12 (vector number is 28); Interrupt number 13 (vector number is 29) only supports UART1 interrupt. Refer to Nested Vectored Interrupt Controller chapter for System Interrupt Map.

The UART0 is built-in with a 64-byte transmitter FIFO (TX FIFO) and a 64-byte receiver FIFO (RX FIFO) that reduces the number of interrupts presented to the CPU and the UART1~2 are equipped 16-byte transmitter FIFO (TX FIFO) and 16-byte receiver FIFO (RX FIFO). The CPU can read the status of the UART at any time during the operation. The reported status information includes the type and condition of the transfer operations being performed by the UART, as well as 4 error conditions (parity error, framing error, break interrupt and buffer error) probably occur while receiving data. The UART includes a programmable baud rate generator that is capable of dividing clock input by divisors to produce the serial clock that transmitter and receiver need. The baud rate equation is Baud Rate = UART\_CLK / M \* [BRD + 2], where M and BRD are defined in Baud Rate Divider Register (UA BAUD). Table 5-6 lists the equations in the various conditions and Table 5-7 list the UART baud rate setting table.

|        | Mode                                                                                          | DIV_X_EN | DIV_X_ONE | Divider X  | BRD | Baud rate equation                       |  |  |  |  |

|--------|-----------------------------------------------------------------------------------------------|----------|-----------|------------|-----|------------------------------------------|--|--|--|--|

| 100    | 0                                                                                             | 0        | 0         | В          | А   | UART_CLK / [16 * (A+2)]                  |  |  |  |  |

| 15     | 1                                                                                             | 1        | 0         | В          | А   | UART_CLK / [(B+1) * (A+2)] , B must >= 8 |  |  |  |  |

| gra to | 2                                                                                             | 1        | 1         | Don't care | А   | UART_CLK / (A+2), A must >=3             |  |  |  |  |

|        | Table 5-6 UART Baud Rate Equation   System clock = internal 22.1184 MHz high speed oscillator |          |           |            |     |                                          |  |  |  |  |

|        |                                                                                               |          |           |            |     |                                          |  |  |  |  |

#### Table 5-6 UART Baud Rate Equation

| System clock = internal 22.1184 MHz high speed oscillator |           |             |                      |                            |           |             |  |  |  |  |

|-----------------------------------------------------------|-----------|-------------|----------------------|----------------------------|-----------|-------------|--|--|--|--|

| Baud rate Mode0 Mode1 Mode2                               |           |             |                      |                            |           |             |  |  |  |  |

| Badd fallo                                                | Parameter | Register    | Parameter            | Register                   | Parameter | Register    |  |  |  |  |

| 921600                                                    | x         | х           | A=0,B=11             | 0x2B00_0000                | A=22      | 0x3000_0016 |  |  |  |  |

| 460800                                                    | A=1       | 0x0000_0001 | A=1,B=15<br>A=2,B=11 | 0x2F00_0001<br>0x2B00_0002 | A=46      | 0x3000_002E |  |  |  |  |

### 5.13 PS/2 Device Controller (PS2D)

#### 5.13.1 Overview

PS/2 device controller provides basic timing control for PS/2 communication. All communication between the device and the host is managed through the CLK and DATA pins. Unlike PS/2 keyboard or mouse device controller, the received/transmit code needs to be translated as meaningful code by firmware. The device controller generates the CLK signal after receiving a request to send, but host has ultimate control over communication. DATA sent from the host to the device is read on the rising edge and DATA sent from device to the host is change after rising edge. A 16 bytes FIFO is used to reduce CPU intervention. S/W can select 1 to 16 bytes for a continuous transmission.

#### 5.13.2 Features

- Host communication inhibit and request to send detection

- Reception frame error detection

- Programmable 1 to 16 bytes transmit buffer to reduce CPU intervention

- Double buffer for data reception

- S/W override bus

### 5.16 Analog Comparator (CMP)

#### 5.16.1 Overview

NuMicro<sup>™</sup> NUC100 Series contains two comparators. The comparators can be used in a number of different configurations. The comparator output is a logical one when positive input greater than negative input, otherwise the output is a zero. Each comparator can be configured to cause an interrupt when the comparator output value changes. The block diagram is shown in **Error! Reference source not found.**

#### 5.16.2 Features

- Analog input voltage range: 0~5.0 V

- Hysteresis function supported

- Two analog comparators with optional internal reference voltage input at negative end

- One interrupt vector for both comparators

### 5.17 PDMA Controller (PDMA)

#### 5.17.1 Overview

NuMicro<sup>™</sup> NUC130/NUC140 contains a peripheral direct memory access (PDMA) controller that transfers data to and from memory or transfer data to and from APB devices. The PDMA has nine channels of DMA (Peripheral-to-Memory or Memory-to-Peripheral or Memory-to-Memory). For each PDMA channel (PDMA CH0~CH8), there is one word buffer as transfer buffer between the Peripherals APB devices and Memory.

Software can stop the PDMA operation by disable PDMA [PDMACEN]. The CPU can recognize the completion of a PDMA operation by software polling or when it receives an internal PDMA interrupt. The PDMA controller can increase source or destination address or fixed them as well.

Notice: The partial of NuMicro<sup>™</sup> NUC130/NUC140 only has 1 PDMA channel (channel 0).

#### 5.17.2 Features

- Support nine DMA channels. Each channel can support a unidirectional transfer

- AMBA AHB master/slave interface compatible, for data transfer and register read/write

- Support source and destination address increased mode or fixed mode

- Hardware channel priority. DMA channel 0 has the highest priority and channel 8 has the lowest priority

| 7.4.2 | Specification of LDO and Power management |

|-------|-------------------------------------------|

|-------|-------------------------------------------|

| PARAMETER      |      | TYP. | MAX. | UNIT | NOTE                          |

|----------------|------|------|------|------|-------------------------------|

| Input Voltage  | 2.7  | 5    | 5.5  | V    | $V_{\text{DD}}$ input voltage |

| Output Voltage | -10% | 2.5  | +10% | V    | V <sub>DD</sub> > 2.7 V       |

| Temperature    | -40  | 25   | 85   | °C   | 24                            |

| Сbр            | -    | 1    | 19   | uF   | Resr=10hm                     |

Note:

1. It is recommended that a 10uF or higher capacitor and a 100nF bypass capacitor are connected between  $V_{DD}$  and the closest  $V_{SS}$  pin of the device.

2. For ensuring power stability, a 1uF or higher capacitor must be connected between LDO pin and the closest  $V_{SS}$  pin of the device.

### 7.4.3 Specification of Low Voltage Reset

| PARAMETER         | CONDITION              | MIN. | TYP. | MAX. | UNIT |

|-------------------|------------------------|------|------|------|------|

| Operation voltage | Mr. Cor                | 1.7  | -    | 5.5  | V    |

| Quiescent current | V <sub>DD</sub> =5.5 V | -    | -    | 5    | uA   |

| Temperature       |                        | -40  | 25   | 85   | °C   |

|                   | Temperature=25℃        | 1.7  | 2.0  | 2.3  | V    |

| Threshold voltage | Temperature=-40°C      | Sil  | 2.4  | -    | V    |

|                   | Temperature=85℃        | 15   | 1.6  | 10   | V    |

| Hysteresis        | -                      | 0    | 0    | 0    | V    |

### 7.4.4 Specification of Brown-Out Detector

| PARAMETER         | CONDITION               | MIN. | TYP. | MAX. | UNIT |

|-------------------|-------------------------|------|------|------|------|

| Operation voltage | -                       | 2.5  | -    | 5.5  | V    |

| Quiescent current | AV <sub>DD</sub> =5.5 V | -    | -    | 125  | μA   |

| Temperature       | -                       | -40  | 25   | 85   | °C   |

|                   | BOV_VL[1:0]=11          | 4.3  | 4.5  | 4.7  | V    |

| Brown-out voltage | BOV_VL [1:0]=10         | 3.6  | 3.8  | 4.0  | V    |

| Brown-out voltage | BOV_VL [1:0]=01         | 2.6  | 2.7  | 2.8  | V    |

|                   | BOV_VL [1:0]=00         | 2.1  | 2.2  | 2.3  | V    |

| Hysteresis        | -                       | 30   | -    | 150  | mV   |

### 7.4.5 Specification of Power-On Reset (5 V)

| PARAMETER         | CONDITION                                                       | MIN. | TYP.      | MAX.    | UNIT |  |

|-------------------|-----------------------------------------------------------------|------|-----------|---------|------|--|

| Temperature       | -                                                               | -40  | 25        | 85      | °C   |  |

| Reset voltage     | V+                                                              | -    | 2         | -       | V    |  |

| Quiescent current | Vin>reset voltage                                               | -    | 1         | -       | nA   |  |

|                   | Publicatio                                                      |      | o Data: I | an 2 20 | 12   |  |

|                   | Publication Release Date: Jan. 2, 2012<br>- 66 - Revision V3.02 |      |           |         |      |  |

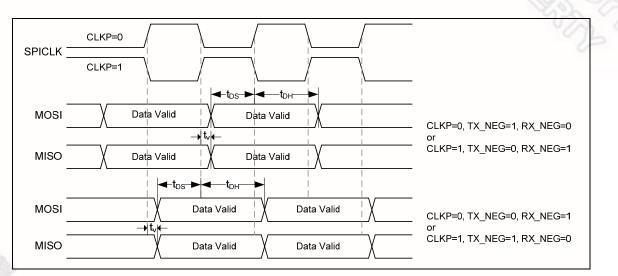

Figure 7-2 SPI Master dynamic characteristics tiMINg

Figure 7-3 SPI Slave dynamic characteristics timing

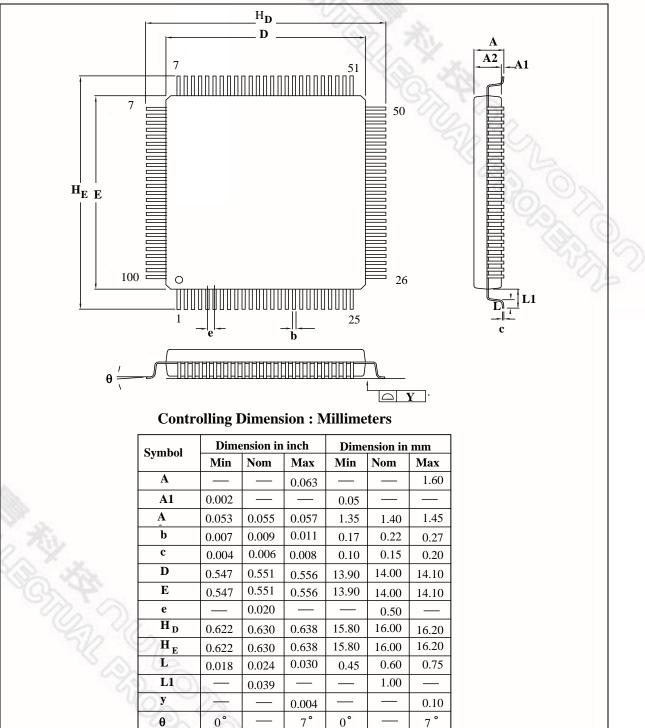

### 8 PACKAGE DIMENSIONS

### 8.1 100L LQFP (14x14x1.4 mm footprint 2.0mm)

Publication Release Date: Jan. 2, 2012 Revision V3.02