## E·XFL

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                          |

|--------------------------------|--------------------------------------------------------------------------|

| Product Status                 | Active                                                                   |

| Number of LABs/CLBs            |                                                                          |

| Number of Logic Elements/Cells |                                                                          |

| Total RAM Bits                 | 202752                                                                   |

| Number of I/O                  | 158                                                                      |

| Number of Gates                | 1000000                                                                  |

| Voltage - Supply               | 2.3V ~ 2.7V                                                              |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | -55°C ~ 125°C (TC)                                                       |

| Package / Case                 | 208-BFCQFP with Tie Bar                                                  |

| Supplier Device Package        | 208-CQFP (75x75)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/apa1000-cq208m |

|                                |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Temperature Grade Offerings**

| Package | APA075 | APA150 | APA300  | APA450 | APA600  | APA750 | APA1000 |

|---------|--------|--------|---------|--------|---------|--------|---------|

| TQ100   | C, I   | C, I   |         |        |         |        |         |

| TQ144   | C, I   |        |         |        |         |        |         |

| PQ208   | C, I   | C, I   | C, I, M | C, I   | C, I, M | C, I   | C, I, M |

| BG456   |        | C, I   | C, I, M | C, I   | C, I, M | C, I   | C, I, M |

| FG144   | C, I   | C, I   | C, I, M | C, I   |         |        |         |

| FG256   |        | C, I   | C, I, M | C, I   | C, I, M |        |         |

| FG484   |        |        |         | C, I   | C, I, M |        |         |

| FG676   |        |        |         |        | C, I, M | C, I   |         |

| FG896   |        |        |         |        |         | C, I   | C, I, M |

| FG1152  |        |        |         |        |         |        | C, I    |

| CQ208   |        |        | M, B    |        | M, B    |        | M, B    |

| CQ352   |        |        | M, B    |        | M, B    |        | M, B    |

| CG624   |        |        |         |        | M, B    |        | M, B    |

*Note:* C = Commercial

I = Industrial

M = Military

B = MIL-STD-883

## Speed Grade and Temperature Matrix

|      | -F           | Std.         |

|------|--------------|--------------|

| С    | $\checkmark$ | $\checkmark$ |

| 1    |              | $\checkmark$ |

| М, В |              | $\checkmark$ |

*Note:* C = Commercial

l = Industrial

M = Military

B = MIL-STD-883

## ProASIC<sup>PLUS</sup> Architecture

The proprietary ProASIC<sup>PLUS</sup> architecture provides granularity comparable to gate arrays.

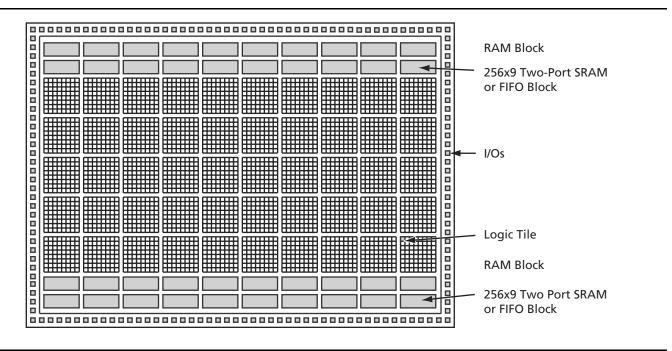

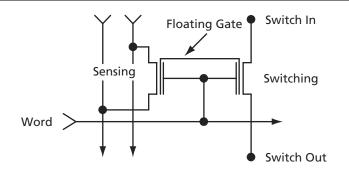

The ProASIC<sup>PLUS</sup> device core consists of a Sea-of-Tiles (Figure 1-1). Each tile can be configured as a three-input logic function (e.g., NAND gate, D-Flip-Flop, etc.) by programming the appropriate Flash switch interconnections (Figure 1-2 and Figure 1-3 on page 1-3). Tiles and larger functions are connected with any of the four levels of routing hierarchy. Flash switches are distributed throughout the device to provide nonvolatile, reconfigurable interconnect programming. Flash switches are programmed to connect signal lines to

the appropriate logic cell inputs and outputs. Dedicated high-performance lines are connected as needed for fast, low-skew global signal distribution throughout the core. Maximum core utilization is possible for virtually any design.

ProASIC<sup>PLUS</sup> devices also contain embedded, two-port SRAM blocks with built-in FIFO/RAM control logic. Programming options include synchronous or asynchronous operation, two-port RAM configurations, user defined depth and width, and parity generation or checking. Please see the "Embedded Memory Configurations" section on page 1-23 for more information.

Figure 1-1 • The ProASIC<sup>PLUS</sup> Device Architecture

Figure 1-2 • Flash Switch

#### ProASIC<sup>PLUS</sup> Flash Family FPGAs

Table 1-8

Clock-Conditioning Circuitry Delay-Line

Settings

| Delay Line | Delay Value (ns) |

|------------|------------------|

| DLYB       | ·                |

| 0          | 0                |

| 1          | +0.25            |

| 2          | +0.50            |

| 3          | +4.0             |

| DLYA       |                  |

| 0          | 0                |

| 1          | +0.25            |

| 2          | +0.50            |

| 3          | +4.0             |

#### Lock Signal

An active-high Lock signal (added via the SmartGen PLL development tool) indicates that the PLL has locked to the incoming clock signal. The PLL will acquire and maintain lock even when there is jitter on the incoming clock signal. The PLL will maintain lock with an input jitter up to 5% of the input period, with a maximum of 5 ns. Users can employ the Lock signal as a soft reset of the logic driven by GLB and/or GLA. Note if  $F_{IN}$  is not within specified frequencies, then both the  $F_{OUT}$  and lock signal are indeterminate.

## **PLL Configuration Options**

The PLL can be configured during design (via Flashconfiguration bits set in the programming bitstream) or dynamically during device operation, thus eliminating the need to reprogram the device. The dynamic configuration bits are loaded into a serial-in/parallel-out shift register provided in the clock conditioning circuit. The shift register can be accessed either from user logic within the device or via the JTAG port. Another option is internal dynamic configuration via user-designed hardware. Refer to Actel's *ProASIC*<sup>PLUS</sup> *PLL Dynamic Reconfiguration Using JTAG* application note for more information.

For information on the clock conditioning circuit, refer to Actel's Using ProASIC<sup>PLUS</sup> Clock Conditioning Circuits application note.

## **Sample Implementations**

#### **Frequency Synthesis**

Figure 1-16 on page 1-17 illustrates an example where the PLL is used to multiply a 33 MHz external clock up to 133 MHz. Figure 1-17 on page 1-17 uses two dividers to synthesize a 50 MHz output clock from a 40 MHz input reference clock. The input frequency of 40 MHz is multiplied by five and divided by four, giving an output clock (GLB) frequency of 50 MHz. When dividers are used, a given ratio can be generated in multiple ways, allowing the user to stay within the operating frequency ranges of the PLL. For example, in this case the input divider could have been two and the output divider also two, giving us a division of the input frequency by four to go with the feedback loop division (effective multiplication) by five.

## Adjustable Clock Delay

Figure 1-18 on page 1-18 illustrates the delay of the input clock by employing one of the adjustable delay lines. This is easily done in ProASIC<sup>PLUS</sup> by bypassing the PLL core entirely and using the output delay line. Notice also that the output clock can be effectively advanced relative to the input clock by using the delay line in the feedback path. This is shown in Figure 1-19 on page 1-18.

## **Clock Skew Minimization**

Figure 1-20 on page 1-19 indicates how feedback from the clock network can be used to create minimal skew between the distributed clock network and the input clock. The input clock is fed to the reference clock input of the PLL. The output clock (GLA) feeds a clock network. The feedback input to the PLL uses a clock input delayed by a routing network. The PLL then adjusts the phase of the input clock to match the delayed clock, thus providing nearly zero effective skew between the two clocks. Refer to Actel's Using ProASIC<sup>PLUS</sup> Clock Conditioning Circuits application note for more information.

## **PLL Electrical Specifications**

| Parameter                                            | Value $T_J \leq -40^{\circ}C$                                                                                | Value                    | Value T <sub>J</sub> > –40°C     |       | Notes                                                                    |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------|-------|--------------------------------------------------------------------------|

| Frequency Ranges                                     |                                                                                                              | 1                        |                                  |       |                                                                          |

| Reference Frequency f <sub>IN</sub> (min.)           | 2.0 MHz                                                                                                      |                          | 1.5 MHz                          |       | Clock conditioning circuitry (min.) lowest input frequency               |

| Reference Frequency f <sub>IN</sub> (max.)           | 180 MHz                                                                                                      |                          | 180 MHz                          |       | Clock conditioning circuitry (max.) highest input frequency              |

| OSC Frequency f <sub>VCO</sub> (min.)                | 60                                                                                                           |                          | 24 MHz                           |       | Lowest output frequency voltage controlled oscillator                    |

| OSC Frequency f <sub>VCO</sub> (max.)                | 180                                                                                                          |                          | 180 MHz                          |       | Highest output frequency voltage controlled oscillator                   |

| Clock Conditioning Circuitry f <sub>OUT</sub> (min.) | $\begin{array}{l} f_{\text{IN}} \leq 40 = 18 \text{ MHz} \\ f_{\text{IN}} > 40 = 16 \text{ MHz} \end{array}$ |                          | 6 MHz                            |       | Lowest output frequency clock conditioning circuitry                     |

| Clock Conditioning Circuitry f <sub>OUT</sub> (max.) | 180                                                                                                          |                          | 180 MHz                          |       | Highest output frequency clock conditioning circuitry                    |

| Acquisition Time from Cold Start                     |                                                                                                              |                          |                                  |       | •                                                                        |

| Acquisition Time (max.)                              | 80 µs                                                                                                        |                          | 30 µs                            |       | $f_{VCO} \le 40 \text{ MHz}$                                             |

| Acquisition Time (max.)                              | 80 µs                                                                                                        |                          | 80 µs                            |       | $f_{VCO} > 40 \text{ MHz}$                                               |

| Long Term Jitter Peak-to-Peak Ma                     | x.*                                                                                                          |                          |                                  |       | •                                                                        |

| Temperature                                          |                                                                                                              | Freq                     | uency I                          | ИНz   |                                                                          |

|                                                      |                                                                                                              | f <sub>VCO</sub> <<br>10 | 10 <f<sub>V<br/>co&lt;60</f<sub> |       |                                                                          |

| 25°C (or higher)                                     |                                                                                                              | ±1%                      | ±2%                              | ±1%   | Jitter(ps) = Jitter(%)*period                                            |

|                                                      |                                                                                                              |                          |                                  |       | For example:                                                             |

|                                                      |                                                                                                              |                          |                                  |       | Jitter in picoseconds at 100 MHz                                         |

|                                                      |                                                                                                              |                          |                                  |       | = 0.01 * (1/100E6) = 100 ps                                              |

| 0°C                                                  |                                                                                                              | ±1.5%                    | ±2.5%                            | ±1%   |                                                                          |

| –40°C                                                |                                                                                                              | ±2.5%                    | ±3.5%                            | ±1%   |                                                                          |

| –55°C                                                |                                                                                                              | ±2.5%                    | ±3.5%                            | ±1%   |                                                                          |

| Power Consumption                                    | •                                                                                                            |                          |                                  |       | •                                                                        |

| Analog Supply Power (max.*)                          |                                                                                                              | 6.9                      | mW per                           | PLL   |                                                                          |

| Digital Supply Current (max.)                        |                                                                                                              | 7 μW/MHz                 |                                  | Z     |                                                                          |

| Duty Cycle                                           |                                                                                                              | 50                       | % ±0.5%                          | 6     |                                                                          |

| Input Jitter Tolerance                               |                                                                                                              | 5% inp                   | ut period<br>5 ns)               | (max. | Maximum jitter allowable on an input clock to acquire and maintain lock. |

Note: \*High clock frequencies (>60 MHz) under typical setup conditions

#### ProASIC<sup>PLUS</sup> Flash Family FPGAs

#### **PLL I/O Constraints**

PLL locking is guaranteed only when the following constraints are followed:

| Table 1-10 • 1 | PLL I/O | Constraints |

|----------------|---------|-------------|

|----------------|---------|-------------|

|          |                        | T <sub>J</sub> ≤ −40°C                                                                                                                                                          | Value T <sub>J</sub> > –40°C                                   |  |

|----------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|

| І/О Туре | low slew rate I/O. PLL | PLL locking is guaranteed only when using low drive strength and<br>low slew rate I/O. PLL locking may be inconsistent when using high<br>drive strength or high slew rate I/Os |                                                                |  |

| SSO      | APA300                 | Hermetic packages $\leq$ 8 SSO                                                                                                                                                  | With FIN $\leq$ 180 MHz and                                    |  |

|          |                        | Plastic packages $\leq$ 16 SSO                                                                                                                                                  | outputs switching simultaneously                               |  |

|          | APA600                 | Hermetic packages ≤ 16 SSO                                                                                                                                                      | ,<br>,                                                         |  |

|          |                        | Plastic packages $\leq$ 32 SSO                                                                                                                                                  |                                                                |  |

|          | APA1000                | Hermetic packages ≤ 16 SSO                                                                                                                                                      |                                                                |  |

|          |                        | Plastic packages $\leq$ 32 SSO                                                                                                                                                  |                                                                |  |

|          | APA300                 | Hermetic packages ≤ 12 SSO                                                                                                                                                      | With FIN $\leq$ 50 MHz and half                                |  |

|          |                        | Plastic packages $\leq$ 20 SSO                                                                                                                                                  | outputs switching on positive<br>clock edge, half switching on |  |

|          | APA600                 | Hermetic packages ≤ 32 SSO                                                                                                                                                      | the negative clock edge no less                                |  |

|          |                        | Plastic packages $\leq$ 64 SSO                                                                                                                                                  | than 10nsec later                                              |  |

|          | APA1000                | Hermetic packages ≤ 32 SSO                                                                                                                                                      |                                                                |  |

|          |                        | Plastic packages $\leq$ 64 SSO                                                                                                                                                  |                                                                |  |

## **B** <sup>®</sup>User Security

ProASICPLUS devices have FlashLock protection bits that, FlashLockonce programmed, block the entire programmed contents from being read externally. Please refer to Table 1-11 for details on the number of bits in the key for each device. If locked, the user can only reprogram the device employing the user-defined security key. This protects the device from being read back and duplicated. Since programmed data is stored in nonvolatile memory cells (actually very small capacitors) rather than in the wiring, physical deconstruction cannot be used to compromise data. This type of security breach is further discouraged by the placement of the memory cells beneath the four metal layers (whose removal cannot be accomplished without disturbing the charge in the capacitor). This is the highest security provided in the industry. For more information, refer to Actel's Design Security in Nonvolatile Flash and Antifuse FPGAs white paper.

| Device  | Key Size |

|---------|----------|

| APA075  | 79 bits  |

| APA150  | 79 bits  |

| APA300  | 79 bits  |

| APA450  | 119 bits |

| APA600  | 167 bits |

| APA750  | 191 bits |

| APA1000 | 263 bits |

Table 1-11 • Flashlock Key Size by Device

## **Embedded Memory Floorplan**

The embedded memory is located across the top and bottom of the device in 256x9 blocks (Figure 1-1 on page 1-2). Depending on the device, up to 88 blocks are available to support a variety of memory configurations. Each block can be programmed as an independent memory array or combined (using dedicated memory routing resources) to form larger, more complex memory configurations. A single memory configuration could include blocks from both the top and bottom memory locations.

Table 1-12 • ProASIC<sup>PLUS</sup> Memory Configurations by Device

## **Embedded Memory Configurations**

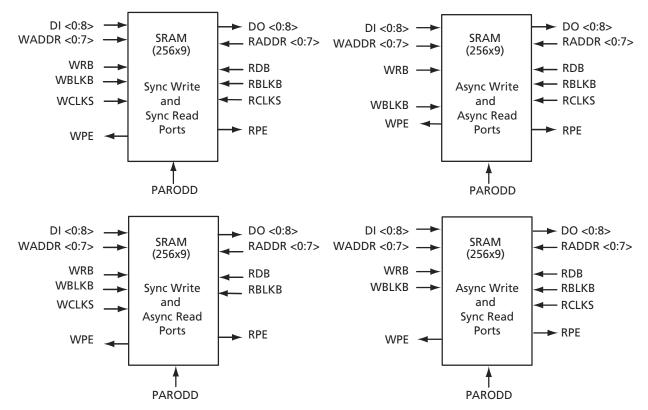

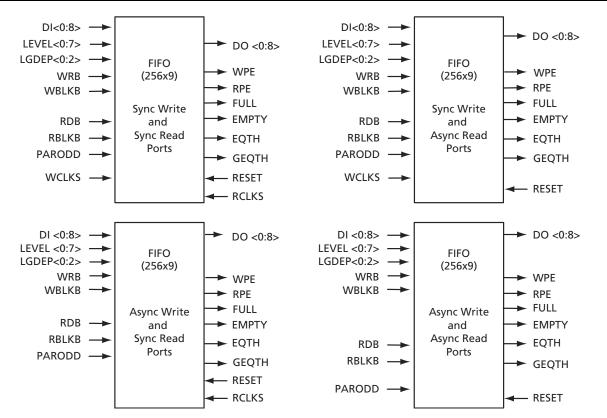

The embedded memory in the ProASIC<sup>PLUS</sup> family provides great configuration flexibility (Table 1-12). Each ProASIC<sup>PLUS</sup> block is designed and optimized as a two-port memory (one read, one write). This provides 198 kbits of two-port and/or single port memory in the APA1000 device.

Each memory block can be configured as FIFO or SRAM, with independent selection of synchronous or asynchronous read and write ports (Table 1-13). Additional characteristics include programmable flags as well as parity checking and generation. Figure 1-21 on page 1-25 and Figure 1-22 on page 1-26 show the block diagrams of the basic SRAM and FIFO blocks. Table 1-14 on page 1-25 and Table 1-15 on page 1-26 describe memory block SRAM and FIFO interface signals, respectively. A single memory block is designed to operate at up to 150 MHz (standard speed grade typical conditions). Each block is comprised of 256 9-bit words (one read port, one write port). The memory blocks may be cascaded in width and/or depth to create the desired memory organization. (Figure 1-23 on page 1-27). This provides optimal bit widths of 9 (one block), 18, 36, and 72, and optimal depths of 256, 512, 768, and 1,024. Refer to Actel's SmartGen User's Guide for more information.

Figure 1-24 on page 1-27 gives an example of optimal memory usage. Ten blocks with 23,040 bits have been used to generate three arrays of various widths and depths. Figure 1-25 on page 1-27 shows how RAM blocks can be used in parallel to create extra read ports. In this example, using only 10 of the 88 available blocks of the APA1000 yields an effective 6,912 bits of multiple port RAM. The Actel SmartGen software facilitates building wider and deeper memory configurations for optimal memory usage.

|        |        |     | Maximu | m Width | Maximum Depth |   |

|--------|--------|-----|--------|---------|---------------|---|

| Device | Bottom | Тор | D      | w       | D             | w |

| APA075 | 0      | 12  | 256    | 108     | 1,536         | 9 |

| APA150 | 0      | 16  | 256    | 144     | 2,048         | 9 |

| APA300 | 16     | 16  | 256    | 144     | 2,048         | 9 |

| APA450 | 24     | 24  | 256    | 216     | 3,072         | 9 |

| APA600 | 28     | 28  | 256    | 252     | 3,584         | 9 |

#### ProASIC<sup>PLUS</sup> Flash Family FPGAs

|         |        | Maximum Wid |     | Maximum Width |       | m Depth |

|---------|--------|-------------|-----|---------------|-------|---------|

| Device  | Bottom | Тор         | D   | W             | D     | W       |

| APA750  | 32     | 32          | 256 | 288           | 4,096 | 9       |

| APA1000 | 44     | 44          | 256 | 396           | 5,632 | 9       |

#### Table 1-13 • Basic Memory Configurations

| Туре | Write Access | Read Access             | Parity    | Library Cell Name |

|------|--------------|-------------------------|-----------|-------------------|

| RAM  | Asynchronous | Asynchronous            | Checked   | RAM256x9AA        |

| RAM  | Asynchronous | Asynchronous            | Generated | RAM256x9AAP       |

| RAM  | Asynchronous | Synchronous Transparent | Checked   | RAM256x9AST       |

| RAM  | Asynchronous | Synchronous Transparent | Generated | RAM256x9ASTP      |

| RAM  | Asynchronous | Synchronous Pipelined   | Checked   | RAM256x9ASR       |

| RAM  | Asynchronous | Synchronous Pipelined   | Generated | RAM256x9ASRP      |

| RAM  | Synchronous  | Asynchronous            | Checked   | RAM256x9SA        |

| RAM  | Synchronous  | Asynchronous            | Generated | RAM256xSAP        |

| RAM  | Synchronous  | Synchronous Transparent | Checked   | RAM256x9SST       |

| RAM  | Synchronous  | Synchronous Transparent | Generated | RAM256x9SSTP      |

| RAM  | Synchronous  | Synchronous Pipelined   | Checked   | RAM256x9SSR       |

| RAM  | Synchronous  | Synchronous Pipelined   | Generated | RAM256x9SSRP      |

| FIFO | Asynchronous | Asynchronous            | Checked   | FIFO256x9AA       |

| FIFO | Asynchronous | Asynchronous            | Generated | FIFO256x9AAP      |

| FIFO | Asynchronous | Synchronous Transparent | Checked   | FIFO256x9AST      |

| FIFO | Asynchronous | Synchronous Transparent | Generated | FIFO256x9ASTP     |

| FIFO | Asynchronous | Synchronous Pipelined   | Checked   | FIFO256x9ASR      |

| FIFO | Asynchronous | Synchronous Pipelined   | Generated | FIFO256x9ASRP     |

| FIFO | Synchronous  | Asynchronous            | Checked   | FIFO256x9SA       |

| FIFO | Synchronous  | Asynchronous            | Generated | FIFO256x9SAP      |

| FIFO | Synchronous  | Synchronous Transparent | Checked   | FIFO256x9SST      |

| FIFO | Synchronous  | Synchronous Transparent | Generated | FIFO256x9SSTP     |

| FIFO | Synchronous  | Synchronous Pipelined   | Checked   | FIFO256x9SSR      |

| FIFO | Synchronous  | Synchronous Pipelined   | Generated | FIFO256x9SSRP     |

**Note:** Each RAM block contains a multiplexer (called DMUX) for each output signal, increasing design efficiency. These DMUX cells do not consume any core logic tiles and connect directly to high-speed routing resources between the RAM blocks. They are used when RAM blocks are cascaded and are automatically inserted by the software tools.

Figure 1-21 • Example SRAM Block Diagrams

| Table 1-14 • | Memory | Block SRAM | Interface | Signals |

|--------------|--------|------------|-----------|---------|

|--------------|--------|------------|-----------|---------|

| SRAM Signal | Bits | In/Out | Description                                                          |

|-------------|------|--------|----------------------------------------------------------------------|

| WCLKS       | 1    | In     | Write clock used on synchronization on write side                    |

| RCLKS       | 1    | In     | Read clock used on synchronization on read side                      |

| RADDR<0:7>  | 8    | In     | Read address                                                         |

| RBLKB       | 1    | In     | Read block select (active Low)                                       |

| RDB         | 1    | In     | Read pulse (active Low)                                              |

| WADDR<0:7>  | 8    | In     | Write address                                                        |

| WBLKB       | 1    | In     | Write block select (active Low)                                      |

| DI<0:8>     | 9    | In     | Input data bits <0:8>, <8> can be used for parity In                 |

| WRB         | 1    | In     | Write pulse (active Low)                                             |

| DO<0:8>     | 9    | Out    | Output data bits <0:8>, <8> can be used for parity Out               |

| RPE         | 1    | Out    | Read parity error (active High)                                      |

| WPE         | 1    | Out    | Write parity error (active High)                                     |

| PARODD      | 1    | In     | Selects Odd parity generation/detect when High, Even parity when Low |

Note: Not all signals shown are used in all modes.

#### ProASIC<sup>PLUS</sup> Flash Family FPGAs

**Note:** Each RAM block contains a multiplexer (called DMUX) for each output signal, increasing design efficiency. These DMUX cells do not consume any core logic tiles and connect directly to high-speed routing resources between the RAM blocks. They are used when RAM blocks are cascaded and are automatically inserted by the software tools.

Figure 1-22 • Basic FIFO Block Diagrams

| FIFO Signal                                                               | Bits | In/Out | Description                                                                                                                                 |

|---------------------------------------------------------------------------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|

| WCLKS                                                                     | 1    | In     | Write clock used for synchronization on write side                                                                                          |

| WCLKS         1           RCLKS         1           LEVEL <0:7>         8 |      | In     | Read clock used for synchronization on read side                                                                                            |

| LEVEL <0:7>                                                               | 8    | In     | Direct configuration implements static flag logic                                                                                           |

| RBLKB                                                                     | 1    | In     | Read block select (active Low)                                                                                                              |

| RDB                                                                       | 1    | In     | Read pulse (active Low)                                                                                                                     |

| RESET                                                                     | 1    | In     | Reset for FIFO pointers (active Low)                                                                                                        |

| WBLKB                                                                     | 1    | In     | Write block select (active Low)                                                                                                             |

| DI<0:8>                                                                   | 9    | In     | Input data bits <0:8>, <8> will be generated parity if PARGEN is true                                                                       |

| WRB                                                                       | 1    | In     | Write pulse (active Low)                                                                                                                    |

| FULL, EMPTY                                                               | 2    | Out    | FIFO flags. FULL prevents write and EMPTY prevents read                                                                                     |

| EQTH, GEQTH                                                               | 2    | Out    | EQTH is true when the FIFO holds the number of words specified by the LEVEL signal. GEQTH is true when the FIFO holds (LEVEL) words or more |

| DO<0:8>                                                                   | 9    | Out    | Output data bits <0:8>. <8> will be parity output if PARGEN is true.                                                                        |

| RPE                                                                       | 1    | Out    | Read parity error (active High)                                                                                                             |

| WPE                                                                       | 1    | Out    | Write parity error (active High)                                                                                                            |

| LGDEP <0:2>                                                               | 3    | In     | Configures DEPTH of the FIFO to 2 (LGDEP+1)                                                                                                 |

| PARODD                                                                    | 1    | In     | Parity generation/detect – Even when Low, Odd when High                                                                                     |

| Table 1-15 • | Memory | <b>Block FIFO</b> | Interface | Signals |

|--------------|--------|-------------------|-----------|---------|

|--------------|--------|-------------------|-----------|---------|

## **Package Thermal Characteristics**

The ProASIC<sup>PLUS</sup> family is available in several package types with a range of pin counts. Actel has selected packages based on high pin count, reliability factors, and superior thermal characteristics.

Thermal resistance defines the ability of a package to conduct heat away from the silicon, through the package to the surrounding air. Junction-to-ambient thermal resistance is measured in degrees Celsius/Watt and is represented as Theta ja  $(\Theta_{ja})$ . The lower the thermal resistance, the more efficiently a package will dissipate heat.

A package's maximum allowed power (P) is a function of maximum junction temperature  $(T_J)$ , maximum ambient operating temperature  $(T_A)$ , and junction-to-ambient thermal resistance  $\Theta_{ia}$ . Maximum junction temperature is

the maximum allowable temperature on the active surface of the IC and is 110° C. P is defined as:

$$P = \frac{T_J - T_A}{\Theta_{ja}}$$

EQ 1-4

$\Theta_{ja}$  is a function of the rate (in linear feet per minute (lfpm)) of airflow in contact with the package. When the estimated power consumption exceeds the maximum allowed power, other means of cooling, such as increasing the airflow rate, must be used. The maximum power dissipation allowed for a Military temperature device is specified as a function of  $\Theta_{jc}$ . The absolute maximum junction temperature is 150°C.

The calculation of the absolute maximum power dissipation allowed for a Military temperature application is illustrated in the following example for a 456-pin PBGA package:

Maximum Power Allowed =

$$\frac{\text{Max. junction temp. (°C)} - \text{Max. case temp. (°C)}}{\theta_{ic}(°C/W)} = \frac{150°C - 125°C}{3.0°C/W} = 8.333W$$

EQ 1-5

Table 1-16

Package Thermal Characteristics

|                                                |           |               |           | $\theta_{ja}$           |                         |       |  |

|------------------------------------------------|-----------|---------------|-----------|-------------------------|-------------------------|-------|--|

| Plastic Packages                               | Pin Count | $\theta_{jc}$ | Still Air | 1.0 m/s<br>200 ft./min. | 2.5 m/s<br>500 ft./min. | Units |  |

| Thin Quad Flat Pack (TQFP)                     | 100       | 14.0          | 33.5      | 27.4                    | 25.0                    | °C/W  |  |

| Thin Quad Flat Pack (TQFP)                     | 144       | 11.0          | 33.5      | 28.0                    | 25.7                    | °C/W  |  |

| Plastic Quad Flat Pack (PQFP) <sup>1</sup>     | 208       | 8.0           | 26.1      | 22.5                    | 20.8                    | °C/W  |  |

| PQFP with Heat spreader <sup>2</sup>           | 208       | 3.8           | 16.2      | 13.3                    | 11.9                    | °C/W  |  |

| Plastic Ball Grid Array (PBGA)                 | 456       | 3.0           | 15.6      | 12.5                    | 11.6                    | °C/W  |  |

| Fine Pitch Ball Grid Array (FBGA)              | 144       | 3.8           | 26.9      | 22.9                    | 21.5                    | °C/W  |  |

| Fine Pitch Ball Grid Array (FBGA)              | 256       | 3.8           | 26.6      | 22.8                    | 21.5                    | °C/W  |  |

| Fine Pitch Ball Grid Array (FBGA) <sup>3</sup> | 484       | 3.2           | 18.0      | 14.7                    | 13.6                    | °C/W  |  |

| Fine Pitch Ball Grid Array (FBGA) <sup>4</sup> | 484       | 3.2           | 20.5      | 17.0                    | 15.9                    | °C/W  |  |

| Fine Pitch Ball Grid Array (FBGA)              | 676       | 3.2           | 16.4      | 13.0                    | 12.0                    | °C/W  |  |

| Fine Pitch Ball Grid Array (FBGA)              | 896       | 2.4           | 13.6      | 10.4                    | 9.4                     | °C/W  |  |

| Fine Pitch Ball Grid Array (FBGA)              | 1152      | 1.8           | 12.0      | 8.9                     | 7.9                     | °C/W  |  |

| Ceramic Quad Flat Pack (CQFP)                  | 208       | 2.0           | 22.0      | 19.8                    | 18.0                    | °C/W  |  |

| Ceramic Quad Flat Pack (CQFP)                  | 352       | 2.0           | 17.9      | 16.1                    | 14.7                    | °C/W  |  |

| Ceramic Column Grid Array (CCGA/LGA)           | 624       | 6.5           | 8.9       | 8.5                     | 8.0                     | °C/W  |  |

#### Notes:

1. Valid for the following devices irrespective of temperature grade: APA075, APA150, and APA300

2. Valid for the following devices irrespective of temperature grade: APA450, APA600, APA750, and APA1000

3. Depopulated Array

4. Full array

## **Operating Conditions**

Standard and -F parts are the same unless otherwise noted. All -F parts are only available as commercial.

#### Table 1-17 • Absolute Maximum Ratings\*

| Parameter                                   | Condition                                 | Minimum | Maximum                | Units |

|---------------------------------------------|-------------------------------------------|---------|------------------------|-------|

| Supply Voltage Core (V <sub>DD</sub> )      |                                           | -0.3    | 3.0                    | V     |

| Supply Voltage I/O Ring (V <sub>DDP</sub> ) |                                           | -0.3    | 4.0                    | V     |

| DC Input Voltage                            |                                           | -0.3    | V <sub>DDP</sub> + 0.3 | V     |

| PCI DC Input Voltage                        |                                           | -1.0    | V <sub>DDP</sub> + 1.0 | V     |

| PCI DC Input Clamp Current (absolute)       | $V_{IN} < -1$ or $V_{IN} = V_{DDP} + 1$ V | 10      |                        | mA    |

| LVPECL Input Voltage                        |                                           | -0.3    | V <sub>DDP</sub> + 0.5 | V     |

| GND                                         |                                           | 0       | 0                      | V     |

**Note:** \*Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Devices should not be operated outside the Recommended Operating Conditions.

| Table 1-18 • | Programming, Storage, and Operating Limits |

|--------------|--------------------------------------------|

|--------------|--------------------------------------------|

|               |                           |                                  | Storage Te | mperature | Operating                                      |

|---------------|---------------------------|----------------------------------|------------|-----------|------------------------------------------------|

| Product Grade | Programming Cycles (min.) | Program Retention (min.)         | Min.       | Max.      | T <sub>J</sub> Max.<br>Junction<br>Temperature |

| Commercial    | 500                       | 20 years                         | –55°C      | 110°C     | 110°C                                          |

| Industrial    | 500                       | 20 years                         | –55°C      | 110°C     | 110°C                                          |

| Military      | 100                       | Refer to Table 1-19 on page 1-35 | –65°C      | 150°C     | 150°C                                          |

| MIL-STD-883   | 100                       | Refer to Table 1-19 on page 1-35 | –65°C      | 150°C     | 150°C                                          |

#### Performance Retention

For devices operated and stored at 110°C or less, the performance retention period is 20 years after programming. For devices operated and stored at temperatures greater than 110°C, refer to Table 1-19 on page 1-35 to determine the performance retention period. Actel does not guarantee performance if the performance retention period is exceeded. Designers can determine the performance retention period from the following table.

Evaluate the percentage of time spent at the highest temperature, then determine the next highest temperature to which the device will be exposed. In Table 1-19 on page 1-35, find the temperature profile that most closely matches the application. Example – the ambient temperature of a system cycles between 100°C (25% of the time) and 50°C (75% of the time). No forced ventilation cooling system is in use. An APA600-PQ208M FPGA operates in the system, dissipating 1 W. The package thermal resistance (junction-to-ambient) in still air  $\Theta_{ja}$  is 20°C/W, indicating that the junction temperature of the FPGA will be 120°C (25% of the time) and 70°C (75% of the time). The entry in Table 1-19 on page 1-35, which most closely matches the application, is 25% at 125°C with 75% at 110°C. Performance retention in this example is at least 16.0 years.

Note that exceeding the stated retention period may result in a performance degradation in the FPGA below the worst-case performance indicated in the Actel Timer. To ensure that performance does not degrade below the worst-case values in the Actel Timer, the FPGA must be reprogrammed within the performance retention period. In addition, note that performance retention is independent of whether or not the FPGA is operating. The retention period of a device in storage at a given temperature will be the same as the retention period of a device operating at that junction temperature.

|                  |                                    |                            |                    |                     | nercial/<br>strial <sup>2,3</sup> | Military/MI         | L-STD- 883 <sup>2,3</sup> |       |

|------------------|------------------------------------|----------------------------|--------------------|---------------------|-----------------------------------|---------------------|---------------------------|-------|

| Symbol           | Parameter                          | Condition                  |                    | Min.                | Max.                              | Min.                | Max.                      | Units |

| V <sub>DD</sub>  | Supply Voltage for Core            |                            |                    | 2.3                 | 2.7                               | 2.3                 | 2.7                       | V     |

| V <sub>DDP</sub> | Supply Voltage for I/O Ring        |                            |                    | 3.0                 | 3.6                               | 3.0                 | 3.6                       | V     |

| V <sub>IH</sub>  | Input High Voltage                 |                            |                    | $0.5V_{DDP}$        | V <sub>DDP</sub> + 0.5            | 0.5V <sub>DDP</sub> | V <sub>DDP</sub> + 0.5    | V     |

| V <sub>IL</sub>  | Input Low Voltage                  |                            |                    | -0.5                | 0.3V <sub>DDP</sub>               | -0.5                | 0.3V <sub>DDP</sub>       | V     |

| I <sub>IPU</sub> | Input Pull-up Voltage <sup>4</sup> |                            |                    | $0.7V_{\text{DDP}}$ |                                   | 0.7V <sub>DDP</sub> |                           | V     |

| I <sub>IL</sub>  | Input Leakage Current <sup>5</sup> | $0 < V_{IN} < V_{DDP}$     | Std.               | -10                 | 10                                | -50                 | 50                        | μΑ    |

|                  |                                    |                            | -F <sup>3, 6</sup> | -10                 | 100                               |                     |                           | μΑ    |

| V <sub>OH</sub>  | Output High Voltage                | I <sub>OUT</sub> = -500 μA |                    | $0.9V_{\text{DDP}}$ |                                   | 0.9V <sub>DDP</sub> |                           | V     |

| V <sub>OL</sub>  | Output Low Voltage                 | I <sub>OUT</sub> = 1500 μA |                    |                     | 0.1V <sub>DDP</sub>               |                     | 0.1V <sub>DDP</sub>       | V     |

| C <sub>IN</sub>  | Input Pin Capacitance (except CLK) |                            |                    |                     | 10                                |                     | 10                        | pF    |

| C <sub>CLK</sub> | CLK Pin Capacitance                |                            |                    | 5                   | 12                                | 5                   | 12                        | рF    |

#### Notes:

1. For PCI operation, use GL33, OTB33PH, OB33PH, IOB33PH, IB33, or IB33S macro library cell only.

2. All process conditions. Junction Temperature: -40 to +110°C for Commercial and Industrial devices and -55 to +125°C for Military.

3. All –F parts are available as commercial only.

4. This specification is guaranteed by design. It is the minimum voltage to which pull-up resistors are calculated to pull a floated network. Designers with applications sensitive to static power utilization should ensure that the input buffer is conducting minimum current at this input voltage.

5. Input leakage currents include hi-Z output leakage for all bidirectional buffers with tristate outputs.

6. The sum of the leakage currents for all inputs shall not exceed 2mA per device.

#### Table 1-48 Recommended Operating Conditions

|                                         |                                | Limits                |                      |  |  |

|-----------------------------------------|--------------------------------|-----------------------|----------------------|--|--|

| Parameter                               | Symbol                         | Commercial/Industrial | Military/MIL-STD-883 |  |  |

| Maximum Clock Frequency*                | f <sub>CLOCK</sub>             | 180 MHz               | 180 MHz              |  |  |

| Maximum RAM Frequency*                  | f <sub>RAM</sub>               | 150 MHz               | 150 MHz              |  |  |

| Maximum Rise/Fall Time on Inputs*       |                                |                       |                      |  |  |

| • Schmitt Trigger Mode (10% to 90%)     | t <sub>R</sub> /t <sub>F</sub> | N/A                   | 100 ns               |  |  |

| • Non-Schmitt Trigger Mode (10% to 90%) | t <sub>R</sub> /t <sub>F</sub> | 100 ns                | 10 ns                |  |  |

| Maximum LVPECL Frequency*               |                                | 180 MHz               | 180 MHz              |  |  |

| Maximum TCK Frequency (JTAG)            | f <sub>TCK</sub>               | 10 MHz                | 10 MHz               |  |  |

Note: \*All –F parts will be 20% slower than standard commercial devices.

#### Table 1-49 • Slew Rates Measured at C = 30pF, Nominal Power Supplies and 25°C

| Туре     | Trig. Level | Rising Edge (ns) | Slew Rate (V/ns) | Falling Edge (ns) | Slew Rate (V/ns) | PCI Mode |

|----------|-------------|------------------|------------------|-------------------|------------------|----------|

| OB33PH   | 10%-90%     | 1.60             | 1.65             | 1.65              | 1.60             | Yes      |

| OB33PN   | 10%-90%     | 1.57             | 1.68             | 3.32              | 0.80             | No       |

| OB33PL   | 10%-90%     | 1.57             | 1.68             | 1.99              | 1.32             | No       |

| OB33LH   | 10%-90%     | 3.80             | 0.70             | 4.84              | 0.55             | No       |

| OB33LN   | 10%-90%     | 4.19             | 0.63             | 3.37              | 0.78             | No       |

| OB33LL   | 10%-90%     | 5.49             | 0.48             | 2.98              | 0.89             | No       |

| OB25LPHH | 10%-90%     | 1.55             | 1.29             | 1.56              | 1.28             | No       |

| OB25LPHN | 10%-90%     | 1.70             | 1.18             | 2.08              | 0.96             | No       |

| OB25LPHL | 10%-90%     | 1.97             | 1.02             | 2.09              | 0.96             | No       |

| OB25LPLH | 10%-90%     | 3.57             | 0.56             | 3.93              | 0.51             | No       |

| OB25LPLN | 10%-90%     | 4.65             | 0.43             | 3.28              | 0.61             | No       |

| OB25LPLL | 10%-90%     | 5.52             | 0.36             | 3.44              | 0.58             | No       |

Notes:

1. Standard and –F parts.

2. All –F only available as commercial.

## **Embedded Memory Specifications**

This section discusses ProASIC<sup>PLUS</sup> SRAM/FIFO embedded memory and its interface signals, including timing diagrams that show the relationships of signals as they pertain to single embedded memory blocks (Table 1-51). Table 1-13 on page 1-24 shows basic SRAM and FIFO configurations. Simultaneous read and write to the same location must be done with care. On such accesses the DI bus is output to the DO bus. Refer to the *ProASIC*<sup>PLUS</sup> *RAM and FIFO Blocks* application note for more information.

#### Enclosed Timing Diagrams—SRAM Mode:

- "Synchronous SRAM Read, Access Timed Output Strobe (Synchronous Transparent)" section on page 1-58

- "Synchronous SRAM Read, Pipeline Mode Outputs (Synchronous Pipelined)" section on page 1-59

- "Asynchronous SRAM Write" section on page 1-60

- "Asynchronous SRAM Read, Address Controlled, RDB=0" section on page 1-61

- "Asynchronous SRAM Read, RDB Controlled" section on page 1-62

- "Synchronous SRAM Write"

- Embedded Memory Specifications

The difference between synchronous transparent and pipeline modes is the timing of all the output signals from the memory. In transparent mode, the outputs will change within the same clock cycle to reflect the data requested by the currently valid access to the memory. If clock cycles are short (high clock speed), the data requires most of the clock cycle to change to valid values (stable signals). Processing of this data in the same clock cycle is nearly impossible. Most designers add registers at all outputs of the memory to push the data processing into the next clock cycle. An entire clock cycle can then be used to process the data. To simplify use of this memorv setup, suitable registers have been implemented as part of the memory primitive and are available to the user in the synchronous pipeline mode. In this mode, the output signals will change shortly after the second rising edge, following the initiation of the read access.

| SRAM Signal Bits In/Out Descript |   | Description |                                                               |  |  |  |

|----------------------------------|---|-------------|---------------------------------------------------------------|--|--|--|

| WCLKS                            | 1 | In          | Write clock used on synchronization on write side             |  |  |  |

| RCLKS                            | 1 | In          | Read clock used on synchronization on read side               |  |  |  |

| RADDR<0:7>                       | 8 | In          | Read address                                                  |  |  |  |

| RBLKB                            | 1 | In          | True read block select (active Low)                           |  |  |  |

| RDB                              | 1 | In          | True read pulse (active Low)                                  |  |  |  |

| WADDR<0:7>                       | 8 | In          | Write address                                                 |  |  |  |

| WBLKB                            | 1 | In          | Write block select (active Low)                               |  |  |  |

| DI<0:8>                          | 9 | In          | Input data bits <0:8>, <8> can be used for parity In          |  |  |  |

| WRB                              | 1 | In          | Negative true write pulse                                     |  |  |  |

| DO<0:8>                          | 9 | Out         | Output data bits <0:8>, <8> can be used for parity Out        |  |  |  |

| RPE                              | 1 | Out         | Read parity error (active High)                               |  |  |  |

| WPE                              | 1 | Out         | Write parity error (active High)                              |  |  |  |

| PARODD                           | 1 | In          | Selects Odd parity generation/detect when high, Even when low |  |  |  |

Table 1-51 • Memory Block SRAM Interface Signals

**Note:** Not all signals shown are used in all modes.

#### Asynchronous SRAM Read, RDB Controlled

#### **Note:** The plot shows the normal operation status.

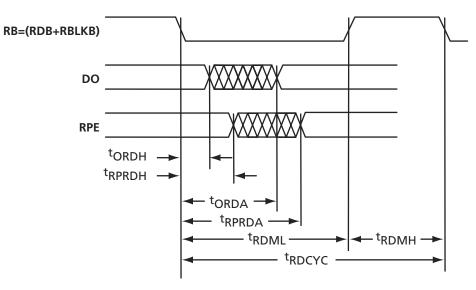

#### Figure 1-35 • Asynchronous SRAM Read, RDB Controlled

## Table 1-56T\_J = 0°C to 110°C; V\_DD = 2.3 V to 2.7 V for Commercial/industrial $T_J = -55°C$ to 150°C, $V_{DD} = 2.3$ V to 2.7 V for Military/MIL-STD-883

|                         |                                     | •    |      |       |                             |

|-------------------------|-------------------------------------|------|------|-------|-----------------------------|

| Symbol t <sub>xxx</sub> | Description                         | Min. | Max. | Units | Notes                       |

| ORDA                    | New DO access from RB $\downarrow$  | 7.5  |      | ns    |                             |

| ORDH                    | Old DO valid from RB $\downarrow$   |      | 3.0  | ns    |                             |

| RDCYC                   | Read cycle time                     | 7.5  |      | ns    |                             |

| RDMH                    | RB high phase                       | 3.0  |      | ns    | Inactive setup to new cycle |

| RDML                    | RB low phase                        | 3.0  |      | ns    | Active                      |

| RPRDA                   | New RPE access from RB $\downarrow$ | 9.5  |      | ns    |                             |

| RPRDH                   | Old RPE valid from RB $\downarrow$  |      | 3.0  | ns    |                             |

Note: All –F speed grade devices are 20% slower than the standard numbers.

#### Asynchronous Write and Synchronous Read to the Same Location

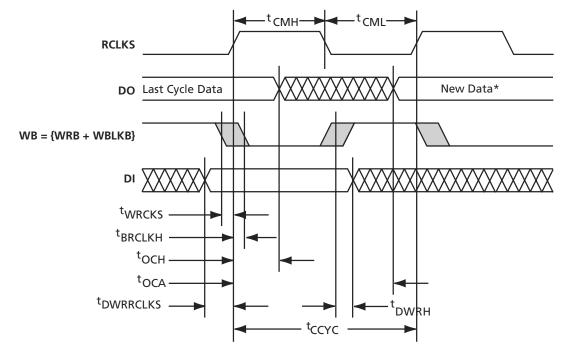

\* New data is read if WB  $\downarrow$  occurs before setup time. The stored data is read if WB  $\downarrow$  occurs after hold time.

#### Note: The plot shows the normal operation status.

| Figure 1-38 • | Asynchronous | Write and Synchronous Read to the Same Location |

|---------------|--------------|-------------------------------------------------|

|---------------|--------------|-------------------------------------------------|

## Table 1-59T<sub>J</sub> = 0°C to 110°C; V<sub>DD</sub> = 2.3 V to 2.7 V for Commercial/industrialT<sub>J</sub> = -55°C to 150°C, V<sub>DD</sub> = 2.3 V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                                    | Min. | Max. | Units | Notes                 |  |

|-------------------------|------------------------------------------------|------|------|-------|-----------------------|--|

| ССҮС                    | Cycle time                                     | 7.5  |      | ns    |                       |  |

| СМН                     | Clock high phase                               | 3.0  |      | ns    |                       |  |

| CML                     | Clock low phase                                | 3.0  |      | ns    |                       |  |

| WBRCLKS                 | WB $\downarrow$ to RCLKS $\uparrow$ setup time | -0.1 |      | ns    |                       |  |

| WBRCLKH                 | WB $\downarrow$ to RCLKS $\uparrow$ hold time  |      | 7.0  | ns    |                       |  |

| ОСН                     | Old DO valid from RCLKS $\uparrow$             |      | 3.0  | ns    | OCA/OCH displayed for |  |

| OCA                     | New DO valid from RCLKS $\uparrow$             | 7.5  |      | ns    | Access Timed Output   |  |

| DWRRCLKS                | DI to RCLKS ↑ setup time                       | 0    |      | ns    |                       |  |

| DWRH                    | DI to WB ↑ hold time                           |      | 1.5  | ns    |                       |  |

#### Notes:

- 1. This behavior is valid for Access Timed Output and Pipelined Mode Output. The table shows the timings of an Access Timed Output.

- 2. In asynchronous write and synchronous read access to the same location, the new write data will be read out if the active write signal edge occurs before or at the same time as the active read clock edge. If WB changes to low after hold time, the data will be read.

3. A setup or hold time violation will result in unknown output data.

4. All –F speed grade devices are 20% slower than the standard numbers.

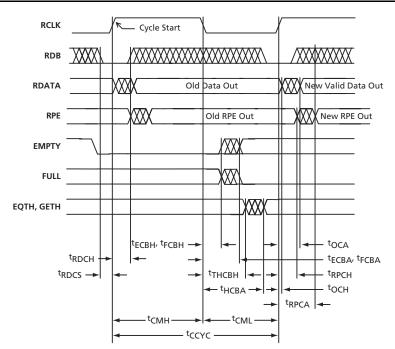

#### Synchronous FIFO Read, Pipeline Mode Outputs (Synchronous Pipelined)

#### Note: The plot shows the normal operation status.

| Figure 1-46 • | Synchronous F | IFO Read, Pipeline | Mode Outputs | (Synchronous Pipelined) |

|---------------|---------------|--------------------|--------------|-------------------------|

|---------------|---------------|--------------------|--------------|-------------------------|

## Table 1-66T\_J = 0°C to 110°C; V\_{DD} = 2.3 V to 2.7 V for Commercial/industrialT\_J = -55°C to 150°C, V\_{DD} = 2.3 V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                                                           | Min.             | Max. | Units | Notes                                                                               |

|-------------------------|-----------------------------------------------------------------------|------------------|------|-------|-------------------------------------------------------------------------------------|

| CCYC                    | Cycle time                                                            | 7.5              |      | ns    |                                                                                     |

| CMH                     | Clock high phase                                                      | 3.0              |      | ns    |                                                                                     |

| CML                     | Clock low phase                                                       | 3.0              |      | ns    |                                                                                     |

| ECBA                    | New EMPTY access from RCLKS $\downarrow$                              | 3.0 <sup>1</sup> |      | ns    |                                                                                     |

| FCBA                    | FULL $\downarrow$ access from RCLKS $\downarrow$                      | 3.0 <sup>1</sup> |      | ns    |                                                                                     |

| ЕСВН, FCBH,<br>ТНСВН    | Old EMPTY, FULL, EQTH, & GETH valid hold time from RCLKS $\downarrow$ |                  | 1.0  | ns    | Empty/full/thresh are invalid from the end of hold until the new access is complete |

| OCA                     | New DO access from RCLKS $\uparrow$                                   | 2.0              |      | ns    |                                                                                     |

| OCH                     | Old DO valid from RCLKS $\uparrow$                                    |                  | 0.75 | ns    |                                                                                     |

| RDCH                    | RDB hold from RCLKS 个                                                 | 0.5              |      | ns    |                                                                                     |

| RDCS                    | RDB setup to RCLKS ↑                                                  | 1.0              |      | ns    |                                                                                     |

| RPCA                    | New RPE access from RCLKS ↑                                           | 4.0              |      | ns    |                                                                                     |

| RPCH                    | Old RPE valid from RCLKS 个                                            |                  | 1.0  | ns    |                                                                                     |

| НСВА                    | EQTH or GETH access from RCLKS $\downarrow$                           | 4.5              |      | ns    |                                                                                     |

#### Notes:

1. At fast cycles, ECBA and FCBA = MAX (7.5 ns - CMS), 3.0 ns.

2. All –F speed grade devices are 20% slower than the standard numbers.

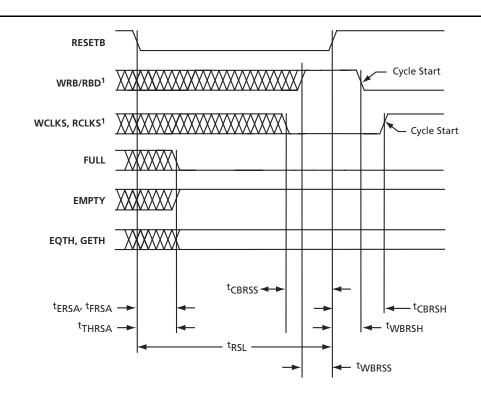

#### **FIFO Reset**

#### Notes:

1. During reset, either the enables (WRB and RBD) OR the clocks (WCLKS and RCKLS) must be low.

2. The plot shows the normal operation status.

#### Figure 1-48 • FIFO Reset

## Table 1-68T\_J = 0°C to 110°C; V\_{DD} = 2.3 V to 2.7 V for Commercial/industrialT\_J = -55°C to 150°C, V\_{DD} = 2.3 V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                                            | Min. | Max. | Units | Notes                  |

|-------------------------|--------------------------------------------------------|------|------|-------|------------------------|

| CBRSH <sup>1</sup>      | WCLKS or RCLKS $\uparrow$ hold from RESETB $\uparrow$  | 1.5  |      | ns    | Synchronous mode only  |

| CBRSS <sup>1</sup>      | WCLKS or RCLKS $\downarrow$ setup to RESETB $\uparrow$ | 1.5  |      | ns    | Synchronous mode only  |

| ERSA                    | New EMPTY $\uparrow$ access from RESETB $\downarrow$   | 3.0  |      | ns    |                        |

| FRSA                    | FULL $\downarrow$ access from RESETB $\downarrow$      | 3.0  |      | ns    |                        |

| RSL                     | RESETB low phase                                       | 7.5  |      | ns    |                        |

| THRSA                   | EQTH or GETH access from RESETB $\downarrow$           | 4.5  |      | ns    |                        |

| WBRSH <sup>1</sup>      | WB $\downarrow$ hold from RESETB $\uparrow$            | 1.5  |      | ns    | Asynchronous mode only |

| WBRSS <sup>1</sup>      | WB ↑ setup to RESETB ↑                                 | 1.5  |      | ns    | Asynchronous mode only |

#### Notes:

1. During rest, the enables (WRB and RBD) must be high OR the clocks (WCLKS and RCKLS) must be low.

2. All –F speed grade devices are 20% slower than the standard numbers.

## **Pin Description**

#### **User Pins**

#### I/O User Input/Output

The I/O pin functions as an input, output, tristate, or bidirectional buffer. Input and output signal levels are compatible with standard LVTTL and LVCMOS specifications. Unused I/O pins are configured as inputs with pull-up resistors.

#### NC No Connect

To maintain compatibility with other Actel ProASIC<sup>PLUS</sup> products, it is recommended that this pin not be connected to the circuitry on the board.

#### GL Global Pin

Low skew input pin for clock or other global signals. This pin can be configured with an internal pull-up resistor. When it is not connected to the global network or the clock conditioning circuit, it can be configured and used as a normal I/O.

#### GLMX Global Multiplexing Pin

Low skew input pin for clock or other global signals. This pin can be used in one of two special ways (refer to Actel's Using ProASIC<sup>PLUS</sup> Clock Conditioning Circuits).

When the external feedback option is selected for the PLL block, this pin is routed as the external feedback source to the clock conditioning circuit.

In applications where two different signals access the same global net at different times through the use of GLMXx and GLMXLx macros, this pin will be fixed as one of the source pins.

This pin can be configured with an internal pull-up resistor. When it is not connected to the global network or the clock conditioning circuit, it can be configured and used as any normal I/O. If not used, the GLMXx pin will be configured as an input with pull-up.

#### **Dedicated Pins**

GND Ground

Common ground supply voltage.

V<sub>DD</sub> Logic Array Power Supply Pin

2.5 V supply voltage.

V<sub>DDP</sub> I/O Pad Power Supply Pin

2.5 V or 3.3 V supply voltage.

#### TMS Test Mode Select

The TMS pin controls the use of boundary-scan circuitry. This pin has an internal pull-up resistor.

#### TCK Test Clock

Clock input pin for boundary scan (maximum 10 MHz). Actel recommends adding a nominal 20  $k\Omega$  pull-up resistor to this pin.

#### TDI Test Data In

Serial input for boundary scan. A dedicated pull-up resistor is included to pull this pin high when not being driven.

#### TDO Test Data Out

Serial output for boundary scan. Actel recommends adding a nominal  $20k\Omega$  pull-up resistor to this pin.

#### TRST Test Reset Input

Asynchronous, active-low input pin for resetting boundary-scan circuitry. This pin has an internal pull-up resistor. For more information, please refer to *Power-up Behavior of ProASIC*<sup>PLUS</sup> *Devices* application note.

#### **Special Function Pins**

#### RCK Running Clock

A free running clock is needed during programming if the programmer cannot guarantee that TCK will be uninterrupted. If not used, this pin has an internal pullup and can be left floating.

#### NPECL User Negative Input

Provides high speed clock or data signals to the PLL block. If unused, leave the pin unconnected.

#### PPECL User Positive Input

Provides high speed clock or data signals to the PLL block. If unused, leave the pin unconnected.

#### AVDD PLL Power Supply

Analog  $V_{DD}$  should be  $V_{DD}$  (core voltage) 2.5 V (nominal) and be decoupled from GND with suitable decoupling capacitors to reduce noise. For more information, refer to Actel's Using ProASIC<sup>PLUS</sup> Clock Conditioning Circuits application note. If the clock conditioning circuitry is not used in a design, AVDD can either be left floating or tied to 2.5 V.

#### AGND PLL Power Ground

The analog ground can be connected to the system ground. For more information, refer to Actel's Using ProASIC<sup>PLUS</sup> Clock Conditioning Circuits application note. If the PLLs or clock conditioning circuitry are not used in a design, AGND should be tied to GND.

#### V<sub>PP</sub> Programming Supply Pin

This pin may be connected to any voltage between GND and 16.5 V during normal operation, or it can be left unconnected.<sup>2</sup> For information on using this pin during programming, see the *In-System Programming ProASIC*<sup>PLUS</sup> Devices application note. Actel recommends floating the pin or connecting it to V<sub>DDP</sub>

#### V<sub>PN</sub> Programming Supply Pin

This pin may be connected to any voltage between 0.5V and -13.8 V during normal operation, or it can be left unconnected.<sup>3</sup> For information on using this pin during programming, see the *In-System Programming ProASIC*<sup>PLUS</sup> Devices application note. Actel recommends floating the pin or connecting it to GND.

# Recommended Design Practice for V<sub>PN</sub>/V<sub>PP</sub>

# ProASIC<sup>PLUS</sup> Devices – APA450, APA600, APA750, APA1000

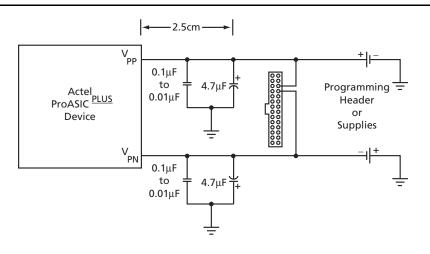

Bypass capacitors are required from  $V_{PP}$  to GND and  $V_{PN}$  to GND for all ProASIC<sup>PLUS</sup> devices during programming. During the erase cycle, ProASIC<sup>PLUS</sup> devices may have current surges on the  $V_{PP}$  and  $V_{PN}$  power supplies. The only way to maintain the integrity of the power distribution to the ProASIC<sup>PLUS</sup> device during these current surges is to counteract the inductance of the finite length conductors that distribute the power to the device. This can be accomplished by providing sufficient bypass capacitance between the  $V_{PP}$  and  $V_{PN}$  pins and GND (using the shortest paths possible). Without sufficient bypass capacitance to counteract the inductance, the  $V_{PP}$  and  $V_{PN}$  pins may incur a voltage spike beyond the voltage that the device can withstand. This issue applies to all programming configurations.

The solution prevents spikes from damaging the ProASIC<sup>PLUS</sup> devices. Bypass capacitors are required for the V<sub>PP</sub> and V<sub>PN</sub> pads. Use a 0.01  $\mu$ F to 0.1  $\mu$ F ceramic capacitor with a 25 V or greater rating. To filter low-frequency noise (decoupling), use a 4.7  $\mu$ F (low ESR, <1 < $\Omega$ , tantalum, 25 V or greater rating) capacitor. The capacitors should be located as close to the device pins as possible (within 2.5 cm is desirable). The smaller, high-frequency capacitor should be placed closer to the device pins than the larger low-frequency capacitor. The same dual-capacitor circuit should be used on both the V<sub>PP</sub> and V<sub>PN</sub> pins (Figure 1-49).

# ProASIC<sup>PLUS</sup> Devices – APA075, APA150, APA300

These devices do not require bypass capacitors on the  $V_{PP}$  and  $V_{PN}$  pins as long as the total combined distance of the programming cable and the trace length on the board is less than or equal to 30 inches. Note: For trace lengths greater than 30 inches, use the bypass capacitor recommendations in the previous section.

Figure 1-49 • ProASICPLUS V<sub>PP</sub> and V<sub>PN</sub> Capacitor Requirements

2. There is a nominal 40 k $\Omega$  pull-up resistor on V<sub>PP</sub>

3. There is a nominal 40 k pull-down resistor on  $V_{PN}$