Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                         |

|--------------------------------|-------------------------------------------------------------------------|

| Product Status                 | Active                                                                  |

| Number of LABs/CLBs            | -                                                                       |

| Number of Logic Elements/Cells | -                                                                       |

| Total RAM Bits                 | 73728                                                                   |

| Number of I/O                  | 290                                                                     |

| Number of Gates                | 300000                                                                  |

| Voltage - Supply               | 2.3V ~ 2.7V                                                             |

| Mounting Type                  | Surface Mount                                                           |

| Operating Temperature          | -55°C ~ 125°C (TC)                                                      |

| Package / Case                 | 456-BBGA                                                                |

| Supplier Device Package        | 456-PBGA (35x35)                                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/apa300-bg456m |

|                                |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Device Resources**

|         |                       |                 |                  |                  |                  | User                | · I/Os <sup>2</sup> |                 |                       |                  |                 |                 |                         |

|---------|-----------------------|-----------------|------------------|------------------|------------------|---------------------|---------------------|-----------------|-----------------------|------------------|-----------------|-----------------|-------------------------|

|         | Commercial/Industrial |                 |                  |                  |                  |                     |                     | Milita          | Military/MIL-STD-883B |                  |                 |                 |                         |

| Device  | TQFP<br>100-Pin       | TQFP<br>144-Pin | PQFP<br>208-Pin  | PBGA<br>456-Pin  | FBGA<br>144-Pin  | FBGA<br>256-Pin     | FBGA<br>484-Pin     | FBGA<br>676-Pin | FBGA<br>896-Pin       | FBGA<br>1152-Pin | CQFP<br>208-Pin | CQFP<br>352-Pin | CCGA/<br>LGA<br>624-Pin |

| APA075  | 66                    | 107             | 158              |                  | 100              |                     |                     |                 |                       |                  |                 |                 |                         |

| APA150  | 66                    |                 | 158              | 242              | 100              | 186 <sup>3</sup>    |                     |                 |                       |                  |                 |                 |                         |

| APA300  |                       |                 | 158 <sup>4</sup> | 290 <sup>4</sup> | 100 <sup>4</sup> | 186 <sup>3, 4</sup> |                     |                 |                       |                  | 158             | 248             |                         |

| APA450  |                       |                 | 158              | 344              | 100              | 186 <sup>3</sup>    | 344 <sup>3</sup>    |                 |                       |                  |                 |                 |                         |

| APA600  |                       |                 | 158 <sup>4</sup> | 356 <sup>4</sup> |                  | 186 <sup>3, 4</sup> | 370 <sup>3</sup>    | 454             |                       |                  | 158             | 248             | 440                     |

| APA750  |                       |                 | 158              | 356              |                  |                     |                     | 454             | 562 <sup>5</sup>      |                  |                 |                 |                         |

| APA1000 |                       |                 | 158 <sup>4</sup> | 356 <sup>4</sup> |                  |                     |                     |                 | 642 <sup>4, 5</sup>   | 712 <sup>5</sup> | 158             | 248             | 440                     |

Notes:

1. Package Definitions: TQFP = Thin Quad Flat Pack, PQFP = Plastic Quad Flat Pack, PBGA = Plastic Ball Grid Array, FBGA = Fine Pitch Ball Grid Array, CQFP = Ceramic Quad Flat Pack, CCGA = Ceramic Column Grid Array, LGA = Land Grid Array

2. Each pair of PECL I/Os is counted as one user I/O.

3. FG256 and FG484 are footprint-compatible packages.

4. Military Temperature Plastic Package Offering

5. FG896 and FG1152 are footprint-compatible packages.

## **General Guideline**

Maximum performance numbers in this datasheet are based on characterized data. Actel does not guarantee performance beyond the limits specified within the datasheet.

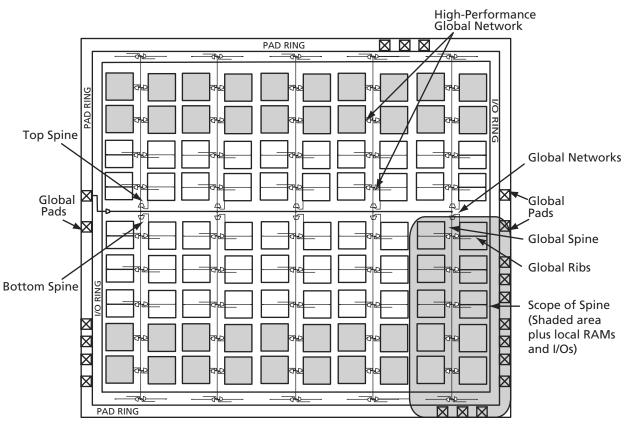

**Note:** This figure shows routing for only one global path. Figure 1-7 • High-Performance Global Network

#### Table 1-1 • Clock Spines

|                                    | APA075 | APA150 | APA300 | APA450 | APA600 | APA750 | APA1000 |

|------------------------------------|--------|--------|--------|--------|--------|--------|---------|

| Global Clock Networks (Trees)      | 4      | 4      | 4      | 4      | 4      | 4      | 4       |

| Clock Spines/Tree                  | 6      | 8      | 8      | 12     | 14     | 16     | 22      |

| Total Spines                       | 24     | 32     | 32     | 48     | 56     | 64     | 88      |

| Top or Bottom Spine Height (Tiles) | 16     | 24     | 32     | 32     | 48     | 64     | 80      |

| Tiles in Each Top or Bottom Spine  | 512    | 768    | 1,024  | 1,024  | 1,536  | 2,048  | 2,560   |

| Total Tiles                        | 3,072  | 6,144  | 8,192  | 12,288 | 21,504 | 32,768 | 56,320  |

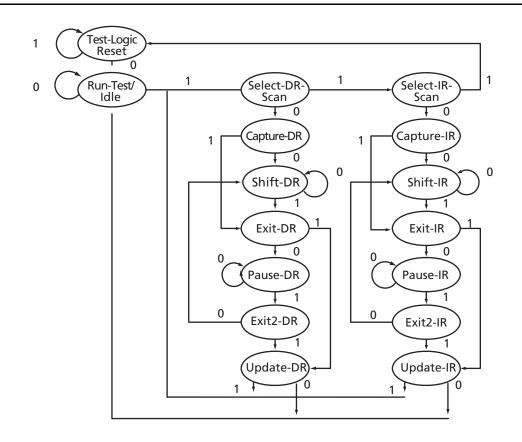

The TAP controller receives two control inputs (TMS and TCK) and generates control and clock signals for the rest of the test logic architecture. On power-up, the TAP controller enters the Test-Logic-Reset state. To guarantee a reset of the controller from any of the possible states, TMS must remain high for five TCK cycles. The TRST pin may also be used to asynchronously place the TAP controller in the Test-Logic-Reset state.

ProASIC<sup>PLUS</sup> devices support three types of test data registers: bypass, device identification, and boundary scan. The bypass register is selected when no other register needs to be accessed in a device. This speeds up test data transfer to other devices in a test data path. The 32-bit device identification register is a shift register

with four fields (lowest significant byte (LSB), ID number, part number and version). The boundary-scan register observes and controls the state of each I/O pin.

Each I/O cell has three boundary-scan register cells, each with a serial-in, serial-out, parallel-in, and parallel-out pin. The serial pins are used to serially connect all the boundary-scan register cells in a device into a boundaryscan register chain, which starts at the TDI pin and ends at the TDO pin. The parallel ports are connected to the internal core logic tile and the input, output, and control ports of an I/O buffer to capture and load data into the register to control or observe the logic state of each I/O.

Figure 1-13 • TAP Controller State Diagram

## Timing Control and Characteristics

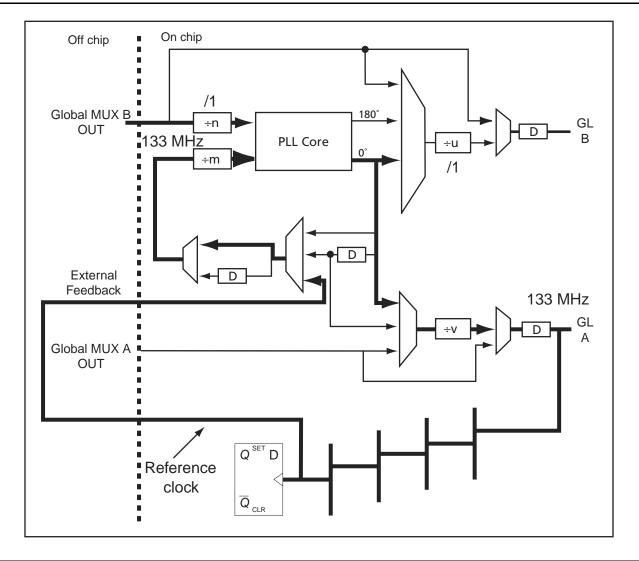

## ProASIC<sup>PLUS</sup> Clock Management System

ProASIC<sup>PLUS</sup> devices provide designers with very flexible clock conditioning capabilities. Each member of the ProASIC<sup>PLUS</sup> family contains two phase-locked loop (PLL) blocks which perform the following functions:

- Clock Phase Adjustment via Programmable Delay (250 ps steps from –7 ns to +8 ns)

- Clock Skew Minimization

- Clock Frequency Synthesis

Each PLL has the following key features:

- Input Frequency Range (f<sub>IN</sub>) = 1.5 to 180 MHz

- Feedback Frequency Range (f<sub>VCO</sub>) = 24 to 180 MHz

- Output Frequency Range (f<sub>OUT</sub>) = 8 to 180 MHz

- Output Phase Shift = 0 ° and 180 °

- Output Duty Cycle = 50%

- Low Output Jitter (max at 25°C)

- $f_{VCO}$  <10 MHz. Jitter ±1% or better

- 10 MHz <  $f_{VCO}$  < 60 MHz. Jitter ±2% or better

- f<sub>VCO</sub> > 60 MHz. Jitter ±1% or better

**Note:** Jitter(ps) = Jitter(%)\* period

For Example:

Jitter in picoseconds at 100 MHz = 0.01 \* (1/100E6) = 100 ps

• Maximum Acquisition = 80 µs for f<sub>VCO</sub> > 40 MHz Time

= 30  $\mu$ s for f<sub>VCO</sub> < 40 MHz

Low Power Consumption – 6.9 mW (max – analog supply) + 7.0µW/MHz (max – digital supply)

## **Physical Implementation**

Each side of the chip contains a clock conditioning circuit based on a 180 MHz PLL block (Figure 1-14 on page 1-14). Two global multiplexed lines extend along each side of the chip to provide bidirectional access to the PLL on that side (neither MUX can be connected to the opposite side's PLL). Each global line has optional LVPECL input pads (described below). The global lines may be driven by either the LVPECL global input pad or the outputs from the PLL block, or both. Each global line can be driven by a different output from the PLL. Unused global pins can be configured as regular I/Os or left unconnected. They default to an input with pull-up. The two signals available to drive the global networks are as follows (Figure 1-15 on page 1-15, Table 1-7 on page 1-15, and Table 1-8 on page 1-16):

## Global A (secondary clock)

- Output from Global MUX A

- Conditioned version of PLL output (f<sub>OUT</sub>) delayed or advanced

- Divided version of either of the above

- Further delayed version of either of the above (0.25 ns, 0.50 ns, or 4.00 ns delay)<sup>1</sup>

### Global B

- Output from Global MUX B

- Delayed or advanced version of f<sub>OUT</sub>

- Divided version of either of the above

- Further delayed version of either of the above (0.25 ns, 0.50 ns, or 4.00 ns delay)<sup>2</sup>

## **Functional Description**

Each PLL block contains four programmable dividers as shown in Figure 1-14 on page 1-14. These allow frequency scaling of the input clock signal as follows:

- The n divider divides the input clock by integer factors from 1 to 32.

- The m divider in the feedback path allows multiplication of the input clock by integer factors ranging from 1 to 64.

- The two dividers together can implement any combination of multiplication and division resulting in a clock frequency between 24 and 180 MHz exiting the PLL core. This clock has a fixed 50% duty cycle.

- The output frequency of the PLL core is given by the formula EQ 1-1 (f<sub>REF</sub> is the reference clock frequency):

$f_{OUT} = f_{REF} * m/n$

EQ 1-1

• The third and fourth dividers (u and v) permit the signals applied to the global network to each be further divided by integer factors ranging from 1 to 4.

The implementations shown in EQ2 and EQ3 enable the user to define a wide range of frequency multiplier and divisors.

$$f_{GLB} = m/(n*u)$$

$$EQ 1-2$$

$$f_{GLA} = m/(n*v)$$

$$EQ 1-3$$

1. This mode is available through the delay feature of the Global MUX driver.

Figure 1-20 • Using the PLL for Clock Deskewing

## Logic Tile Timing Characteristics

Timing characteristics for ProASIC<sup>PLUS</sup> devices fall into three categories: family dependent, device dependent, and design dependent. The input and output buffer characteristics are common to all ProASIC<sup>PLUS</sup> family members. Internal routing delays are device dependent. Design dependency means that actual delays are not determined until after placement and routing of the user's design are complete. Delay values may then be determined by using the Timer utility or by performing simulation with post-layout delays.

## **Critical Nets and Typical Nets**

Propagation delays are expressed only for typical nets, which are used for initial design performance evaluation. Critical net delays can then be applied to the most timing-critical paths. Critical nets are determined by net property assignment prior to place-and-route. Refer to the Actel *Designer User's Guide* or online help for details on using constraints.

## **Timing Derating**

Since ProASIC<sup>PLUS</sup> devices are manufactured with a CMOS process, device performance will vary with temperature, voltage, and process. Minimum timing parameters reflect maximum operating voltage, minimum operating temperature, and optimal process variations. Maximum timing parameters reflect minimum operating voltage, maximum operating temperature, and worst-case process variations (within process specifications). The derating factors shown in Table 1-9 should be applied to all timing data contained within this datasheet.

All timing numbers listed in this datasheet represent sample timing characteristics of ProASIC<sup>PLUS</sup> devices. Actual timing delay values are design-specific and can be derived from the Timer tool in Actel's Designer software after place-and-route.

| Table 1-9 • | Temperature and Voltage Derating Factors                                       |

|-------------|--------------------------------------------------------------------------------|

|             | (Normalized to Worst-Case Commercial, $T_J = 70^{\circ}C$ , $V_{DD} = 2.3 V$ ) |

|       | –55°C | –40°C | 0°C  | 25°C | 70°C | 85°C | 110°C | 125°C | 135°C | 150°C |

|-------|-------|-------|------|------|------|------|-------|-------|-------|-------|

| 2.3 V | 0.84  | 0.86  | 0.91 | 0.94 | 1.00 | 1.02 | 1.05  | 1.13  | 1.18  | 1.27  |

| 2.5 V | 0.81  | 0.82  | 0.87 | 0.90 | 0.95 | 0.98 | 1.01  | 1.09  | 1.13  | 1.21  |

| 2.7 V | 0.77  | 0.79  | 0.83 | 0.86 | 0.91 | 0.93 | 0.96  | 1.04  | 1.08  | 1.16  |

#### Notes:

1. The user can set the junction temperature in Designer software to be any integer value in the range of -55°C to 175°C.

2. The user can set the core voltage in Designer software to be any value between 1.4 V and 1.6 V.

## **PLL I/O Constraints**

PLL locking is guaranteed only when the following constraints are followed:

| Table 1-10 • 1 | PLL I/O | Constraints |

|----------------|---------|-------------|

|----------------|---------|-------------|

|          |         | T <sub>J</sub> ≤ −40°C                                                                                       | Value T <sub>J</sub> > –40°C                                   |

|----------|---------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| І/О Туре |         | teed only when using low drive strength and<br>locking may be inconsistent when using high<br>slew rate I/Os |                                                                |

| SSO      | APA300  | Hermetic packages $\leq$ 8 SSO                                                                               | With FIN $\leq$ 180 MHz and                                    |

|          |         | Plastic packages $\leq$ 16 SSO                                                                               | outputs switching simultaneously                               |

|          | APA600  | Hermetic packages ≤ 16 SSO                                                                                   | ,<br>,                                                         |

|          |         | Plastic packages $\leq$ 32 SSO                                                                               |                                                                |

|          | APA1000 | Hermetic packages ≤ 16 SSO                                                                                   |                                                                |

|          |         | Plastic packages $\leq$ 32 SSO                                                                               |                                                                |

|          | APA300  | Hermetic packages ≤ 12 SSO                                                                                   | With FIN $\leq$ 50 MHz and half                                |

|          |         | Plastic packages ≤ 20 SSO                                                                                    | outputs switching on positive<br>clock edge, half switching on |

|          | APA600  | Hermetic packages ≤ 32 SSO                                                                                   | the negative clock edge no less                                |

|          |         | Plastic packages $\leq$ 64 SSO                                                                               | than 10nsec later                                              |

|          | APA1000 | Hermetic packages ≤ 32 SSO                                                                                   |                                                                |

|          |         | Plastic packages $\leq$ 64 SSO                                                                               |                                                                |

#### Logic-Tile Contribution—Plogic

Plogic, the logic-tile component of AC power dissipation, is given by

$$P_{logic} = P3 * mc * Fs$$

where:

- P3 =  $1.4 \mu$ W/MHz is the average power consumption of a logic tile per MHz of its output toggling rate. The maximum output toggling rate is Fs/2.

- mc = the number of logic tiles switching during each Fs cycle

- Fs = the clock frequency

#### I/O Output Buffer Contribution—Poutputs

Poutputs, the I/O component of AC power dissipation, is given by

$$P_{outputs} = (P4 + (C_{load} * V_{DDP}^{2})) * p * Fp$$

where:

P4 =  $326 \mu$ W/MHz is the intrinsic power consumption of an output pad normalized per MHz of the output frequency. This is the total I/O current V<sub>DDP</sub>

C<sub>load</sub> = the output load

- p = the number of outputs

- Fp = the average output frequency

#### I/O Input Buffer's Buffer Contribution—P<sub>inputs</sub>

The input's component of AC power dissipation is given by

$$P_{inputs} = P8 * q * Fq$$

where:

- P8 = 29  $\mu$ W/MHz is the intrinsic power consumption of an input pad normalized per MHz of the input frequency.

- q = the number of inputs

- Fq = the average input frequency

#### PLL Contribution—P<sub>pll</sub>

$P_{p|l} = P9 * N_{p|l}$

where:

P9 = 7.5 mW. This value has been estimated at maximum PLL clock frequency.

N<sub>PII</sub> = number of PLLs used

### RAM Contribution—P<sub>memory</sub>

Finally, P<sub>memory</sub>, the memory component of AC power consumption, is given by

$$P_{memory} = P6 * N_{memory} * F_{memory} * E_{memory}$$

where:

| P6                  | = | 175 $\mu$ W/MHz is the average power consumption of a memory block per MHz of the clock                                                                     |

|---------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N <sub>memory</sub> | = | the number of RAM/FIFO blocks                                                                                                                               |

|                     |   | (1 block = 256 words * 9 bits)                                                                                                                              |

| F <sub>memory</sub> | = | the clock frequency of the memory                                                                                                                           |

| Ememory             | = | the average number of active blocks divided by the total number of blocks (N) of the memory.                                                                |

|                     |   | <ul> <li>Typical values for E<sub>memory</sub> would be 1/4 for a 1k x 8,9,16, 32 memory and 1/16 for a 4kx8, 9, 16, and 32 memory configuration</li> </ul> |

• In addition, an application-dependent component to  $E_{memory}$  can be considered. For example, for a 1kx8 memory configuration using only 1 cycle out of 2,  $E_{memory} = 1/4*1/2 = 1/8$

|                              |                                                                   |                                                                                                                           |                            |                   | lustrial/<br>D-883 <sup>1, 2</sup> | Units                                  |    |

|------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------|------------------------------------|----------------------------------------|----|

| Symbol                       | Parameter                                                         | Conditions                                                                                                                | Min.                       | Тур.              | Max.                               |                                        |    |

| V <sub>OH</sub>              | Output High Voltage<br>High Drive (OB25LPH)                       | $I_{OH} = -6 \text{ mA}$<br>$I_{OH} = -12 \text{ mA}$<br>$I_{OH} = -24 \text{ mA}$                                        |                            | 2.1<br>2.0<br>1.7 |                                    |                                        | V  |

|                              | Low Drive (OB25LPL)                                               | $I_{OH} = -3 \text{ mA}$<br>$I_{OH} = -6 \text{ mA}$<br>$I_{OH} = -8 \text{ mA}$                                          |                            | 2.1<br>1.9<br>1.7 |                                    |                                        |    |

| V <sub>OL</sub>              | Output Low Voltage<br>High Drive (OB25LPH)<br>Low Drive (OB25LPL) | $I_{OL} = 8 \text{ mA}$ $I_{OL} = 15 \text{ mA}$ $I_{OL} = 24 \text{ mA}$ $I_{OL} = 4 \text{ mA}$ $I_{OL} = 8 \text{ mA}$ |                            |                   |                                    | 0.2<br>0.4<br>0.7<br>0.2<br>0.4<br>0.7 | V  |

| V <sub>IH</sub> <sup>6</sup> | Input High Voltage                                                | I <sub>OL</sub> = 15 mA                                                                                                   |                            | 1.7               |                                    | V <sub>DDP</sub> + 0.3                 | V  |

| V <sub>IL</sub> <sup>7</sup> | Input Low Voltage                                                 |                                                                                                                           |                            | -0.3              |                                    | 0.7                                    | V  |

| R <sub>WEAKPULLUP</sub>      | Weak Pull-up Resistance<br>(OTB25LPU)                             | $V_{\rm IN} \ge 1.25 V$                                                                                                   |                            | 6                 |                                    | 56                                     | kΩ |

| HYST                         | Input Hysteresis Schmitt                                          | See Table 1-4 on page 1-9                                                                                                 |                            | 0.3               | 0.35                               | 0.45                                   | V  |

| I <sub>IN</sub>              | Input Current                                                     | with pull up ( $V_{IN} = GND$ )                                                                                           |                            | -240              |                                    | - 20                                   | μA |

|                              |                                                                   | without pull up ( $V_{IN} = GND \text{ or } V_{DD}$ )                                                                     |                            | -10               |                                    | 10                                     | μΑ |

| I <sub>DDQ</sub>             | Quiescent Supply Current                                          | $V_{IN} = GND^4 \text{ or } V_{DD}$                                                                                       | Std.                       |                   | 5.0                                | 15                                     | mA |

|                              | (standby)<br>Commercial                                           |                                                                                                                           | F <sup>3</sup>             |                   | 5.0                                | 25                                     | mA |

| I <sub>DDQ</sub>             | Quiescent Supply Current<br>(standby)<br>Industrial               | $V_{IN} = GND^4 \text{ or } V_{DD}$                                                                                       | Std.                       |                   | 5.0                                | 20                                     | mA |

| I <sub>DDQ</sub>             | Quiescent Supply Current<br>(standby)<br>Military/MIL-STD-883     | $V_{IN} = GND^4 \text{ or } V_{DD}$                                                                                       | Std.                       |                   | 5.0                                | 25                                     | mA |

| 1                            |                                                                   | $V_{\rm cND}$ or $V_{\rm cND}$                                                                                            | C+4                        | 10                | 5.0                                | 25                                     |    |

| I <sub>OZ</sub>              | Tristate Output Leakage Current                                   |                                                                                                                           | Std.<br>_F <sup>3, 5</sup> | -10<br>-10        |                                    | 10<br>100                              | μΑ |

|                              |                                                                   |                                                                                                                           | —F., , ,                   | -10               |                                    | 100                                    | μA |

#### Table 1-22 • DC Electrical Specifications (V<sub>DDP</sub> = 2.5 V $\pm$ 0.2V)

#### Notes:

1. All process conditions. Commercial/Industrial: Junction Temperature: -40 to +110°C.

2. All process conditions. Military: Junction Temperature: -55 to +150°C.

- 3. All –F parts are available only as commercial.

- 4. No pull-up resistor.

- 5. This will not exceed 2 mA total per device.

- 6. During transitions, the input signal may overshoot to  $V_{DDP}$  +1.0V for a limited time of no larger than 10% of the duty cycle.

7. During transitions, the input signal may undershoot to -1.0V for a limited time of no larger than 10% of the duty cycle.

|                  |                                                                                  |                                          |              | Commercial/Industrial/<br>Military/MIL-STD-883 <sup>1, 2</sup> |           |       |  |  |

|------------------|----------------------------------------------------------------------------------|------------------------------------------|--------------|----------------------------------------------------------------|-----------|-------|--|--|

| Symbol           | Parameter                                                                        | Conditions                               | Min.         | Тур.                                                           | Max.      | Units |  |  |

| I <sub>OSH</sub> | Output Short Circuit Current High<br>High Drive (OB25LPH)<br>Low Drive (OB25LPL) | $V_{IN} = V_{SS}$<br>$V_{IN} = V_{SS}$   | -120<br>-100 |                                                                |           | mA    |  |  |

| I <sub>OSL</sub> | Output Short Circuit Current Low<br>High Drive (OB25LPH)<br>Low Drive (OB25LPL)  | $V_{IN} = V_{DDP}$<br>$V_{IN} = V_{DDP}$ |              |                                                                | 100<br>30 | mA    |  |  |

| C <sub>I/O</sub> | I/O Pad Capacitance                                                              |                                          |              |                                                                | 10        | pF    |  |  |

| C <sub>CLK</sub> | Clock Input Pad Capacitance                                                      |                                          |              |                                                                | 10        | pF    |  |  |

#### Table 1-22 • DC Electrical Specifications (V<sub>DDP</sub> = 2.5 V $\pm$ 0.2V) (Continued)

Notes:

1. All process conditions. Commercial/Industrial: Junction Temperature: -40 to +110°C.

2. All process conditions. Military: Junction Temperature: -55 to +150°C.

3. All –F parts are available only as commercial.

4. No pull-up resistor.

5. This will not exceed 2 mA total per device.

6. During transitions, the input signal may overshoot to  $V_{DDP}$  +1.0V for a limited time of no larger than 10% of the duty cycle.

7. During transitions, the input signal may undershoot to -1.0V for a limited time of no larger than 10% of the duty cycle.

# Table 1-24DC Electrical Specifications (VVDE3.3 V $\pm$ 0.3 Vand VVDE2.5 V $\pm$ 0.2 V) (Continued)Applies to Military Temperature and MIL-STD-883B Temperature Only

|                  |                                                                                             |                                                |                 | Militar      | /MIL-S1 | D-883B <sup>1</sup> | Τ     |

|------------------|---------------------------------------------------------------------------------------------|------------------------------------------------|-----------------|--------------|---------|---------------------|-------|

| Symbol           | Parameter                                                                                   | Conditions                                     |                 | Min.         | Тур.    | Max.                | Units |

| I <sub>DDQ</sub> | Quiescent Supply Current<br>(standby)<br>Industrial                                         | $V_{IN} = GND^2 \text{ or } V_{DD}$            | Std.            |              | 5.0     | 20                  | mA    |

| I <sub>DDQ</sub> | Quiescent Supply Current<br>(standby)<br>Military                                           | $V_{IN} = GND^2 \text{ or } V_{DD}$            | Std.            |              | 5.0     | 25                  | mA    |

| I <sub>OZ</sub>  |                                                                                             | $V_{OH} = GND \text{ or } V_{DD}$              | Std.            | -10          |         | 10                  | μΑ    |

|                  | Current                                                                                     |                                                | -F <sup>3</sup> | -10          |         | 100                 | μΑ    |

| I <sub>OSH</sub> | Output Short Circuit Current<br>High<br>3.3 V High Drive (OB33P)<br>3.3 V Low Drive (OB33L) | V <sub>IN</sub> = GND<br>V <sub>IN</sub> = GND |                 | -200<br>-100 |         |                     |       |

| I <sub>OSL</sub> | Output Short Circuit Current<br>Low<br>3.3 V High Drive<br>3.3 V Low Drive                  | $V_{IN} = V_{DD}$<br>$V_{IN} = V_{DD}$         |                 |              |         | 200<br>100          |       |

| CI/O             | I/O Pad Capacitance                                                                         |                                                |                 |              |         | 10                  | pF    |

| C <sub>CLK</sub> | Clock Input Pad Capacitance                                                                 |                                                |                 |              |         | 10                  | pF    |

Notes:

1. All process conditions. Military Temperature / MIL-STD-883 Class B: Junction Temperature: -55 to +125°C.

2. No pull-up resistor required.

3. This will not exceed 2 mA total per device.

4. During transitions, the input signal may overshoot to V<sub>DDP</sub>+1.0 V for a limited time of no larger than 10% of the duty cycle.

5. During transitions, the input signal may undershoot to -1.0 V for a limited time of no larger than 10% of the duty cycle.

#### Table 1-37 • Worst-Case Military Conditions

$V_{DDP}$  = 3.0V,  $V_{DD}$  = 2.3V,  $T_{J}$  = 125°C for Military/MIL-STD-883

|            |                                                                             | Max. t <sub>INYH</sub> 1 | Max. t <sub>INYL</sub> <sup>2</sup> |       |

|------------|-----------------------------------------------------------------------------|--------------------------|-------------------------------------|-------|

| Macro Type | Description                                                                 | Std.                     | Std.                                | Units |

| IB33       | 3.3V, CMOS Input Levels <sup>3</sup> , No Pull-up Resistor                  | 0.5                      | 0.6                                 | ns    |

| IB33S      | 3.3V, CMOS Input Levels <sup>3</sup> , No Pull-up Resistor, Schmitt Trigger | 0.6                      | 0.8                                 | ns    |

#### Notes:

- 1.  $t_{INYH} = Input Pad-to-Y High$

- 2.  $t_{INYL} = Input Pad-to-Y Low$

- 3. LVTTL delays are the same as CMOS delays.

- 4. For LP Macros, V<sub>DDP</sub>=2.3V for delays.

#### Table 1-38 • Worst-Case Military Conditions

#### $V_{DDP}$ = 2.3V, $V_{DD}$ = 2.3V, $T_J$ = 125°C for Military/MIL-STD-883

|            |                                                                   | Max. t <sub>INYH</sub> 1 | Max. t <sub>INYL</sub> 2 |       |

|------------|-------------------------------------------------------------------|--------------------------|--------------------------|-------|

| Macro Type | Description                                                       | Std.                     | Std.                     | Units |

| IB25LP     | 2.5V, CMOS Input Levels <sup>3</sup> , Low Power                  | 0.9                      | 0.7                      | ns    |

| IB25LPS    | 2.5V, CMOS Input Levels <sup>3</sup> , Low Power, Schmitt Trigger | 0.8                      | 1.0                      | ns    |

#### Notes:

- 1.  $t_{INYH} = Input Pad-to-Y High$

- 2.  $t_{INYL} = Input Pad-to-Y Low$

- 3. LVTTL delays are the same as CMOS delays.

- 4. For LP Macros,  $V_{DDP}$ =2.3V for delays.

#### Table 1-41 • Worst-Case Military Conditions

$V_{DDP} = 3.0V, V_{DD} = 2.3V, T_J = 125^{\circ}C$  for Military/MIL-STD-883

|            |                                                                             | Max. t <sub>INYH</sub> 1 | Max. t <sub>INYL</sub> <sup>2</sup> |

|------------|-----------------------------------------------------------------------------|--------------------------|-------------------------------------|

| Macro Type | Description                                                                 | Std.                     | Std.                                |

| GL33       | 3.3V, CMOS Input Levels <sup>3</sup> , No Pull-up Resistor                  | 1.1                      | 1.1                                 |

| GL33S      | 3.3V, CMOS Input Levels <sup>3</sup> , No Pull-up Resistor, Schmitt Trigger | 1.1                      | 1.1                                 |

| PECL       | PPECL Input Levels                                                          | 1.1                      | 1.1                                 |

#### Notes:

- 1.  $t_{INYH} = Input Pad-to-Y High$

- 2.  $t_{INYL} = Input Pad-to-Y Low$

- 3. LVTTL delays are the same as CMOS delays.

4. For LP Macros, V<sub>DDP</sub>=2.3V for delays.

#### Table 1-42 • Worst-Case Military Conditions

## $V_{DDP} = 2.3V$ , $V_{DD} = 2.3V$ , $T_J = 125^{\circ}C$ for Military/MIL-STD-883

|            |                                                                   | Max. t <sub>INYH</sub> 1 | Max. t <sub>INYL</sub> <sup>2</sup> |

|------------|-------------------------------------------------------------------|--------------------------|-------------------------------------|

| Macro Type | Description                                                       | Std.                     | Std.                                |

| GL25LP     | 2.5V, CMOS Input Levels <sup>3</sup> , Low Power                  | 1.0                      | 1.1                                 |

| GL25LPS    | 2.5V, CMOS Input Levels <sup>3</sup> , Low Power, Schmitt Trigger | 1.4                      | 1.0                                 |

Notes:

- 1.  $t_{INYH} = Input Pad-to-Y High$

- 2.  $t_{INYL} = Input Pad-to-Y Low$

3. LVTTL delays are the same as CMOS delays.

4. For LP Macros, V<sub>DDP</sub>=2.3V for delays.

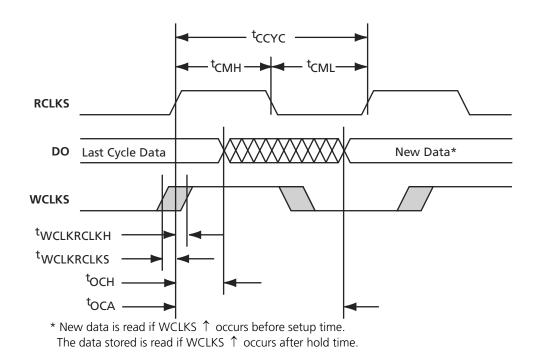

## Synchronous Write and Read to the Same Location

**Note:** The plot shows the normal operation status.

#### *Figure 1-37* • Synchronous Write and Read to the Same Location

#### Table 1-58 • $T_J = 0^{\circ}C$ to 110°C; $V_{DD} = 2.3$ V to 2.7 V for Commercial/industrial $T_J = -55^{\circ}C$ to 150°C, $V_{DD} = 2.3$ V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                                     | Min.  | Max. | Units | Notes                 |

|-------------------------|-------------------------------------------------|-------|------|-------|-----------------------|

| CCYC                    | Cycle time                                      | 7.5   |      | ns    |                       |

| СМН                     | Clock high phase                                | 3.0   |      | ns    |                       |

| CML                     | Clock low phase                                 | 3.0   |      | ns    |                       |

| WCLKRCLKS               | WCLKS $\uparrow$ to RCLKS $\uparrow$ setup time | - 0.1 |      | ns    |                       |

| WCLKRCLKH               | WCLKS $\uparrow$ to RCLKS $\uparrow$ hold time  |       | 7.0  | ns    |                       |

| ОСН                     | Old DO valid from RCLKS ↑                       |       | 3.0  | ns    | OCA/OCH displayed for |

| OCA                     | New DO valid from RCLKS ↑                       | 7.5   |      | ns    | Access Timed Output   |

#### Notes:

1. This behavior is valid for Access Timed Output and Pipelined Mode Output. The table shows the timings of an Access Timed Output.

2. During synchronous write and synchronous read access to the same location, the new write data will be read out if the active write clock edge occurs before or at the same time as the active read clock edge. The negative setup time insures this behavior for WCLKS and RCLKS driven by the same design signal.

- 3. If WCLKS changes after the hold time, the data will be read.

- 4. A setup or hold time violation will result in unknown output data.

- 5. All –F speed grade devices are 20% slower than the standard numbers.

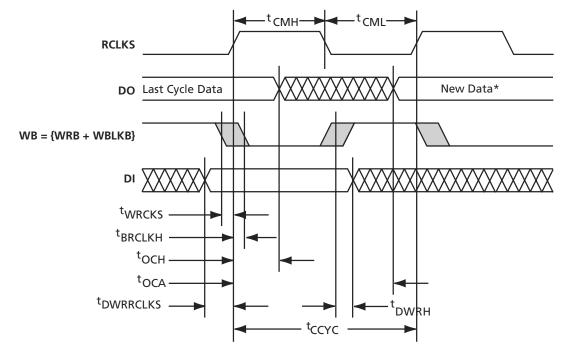

## Asynchronous Write and Synchronous Read to the Same Location

\* New data is read if WB  $\downarrow$  occurs before setup time. The stored data is read if WB  $\downarrow$  occurs after hold time.

#### Note: The plot shows the normal operation status.

| Figure 1-38 • | Asynchronous | Write and Synchronous Read to the Same Location |

|---------------|--------------|-------------------------------------------------|

|---------------|--------------|-------------------------------------------------|

# Table 1-59T<sub>J</sub> = 0°C to 110°C; V<sub>DD</sub> = 2.3 V to 2.7 V for Commercial/industrialT<sub>J</sub> = -55°C to 150°C, V<sub>DD</sub> = 2.3 V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                                    | Min. | Max. | Units | Notes                 |

|-------------------------|------------------------------------------------|------|------|-------|-----------------------|

| ССҮС                    | Cycle time                                     | 7.5  |      | ns    |                       |

| СМН                     | Clock high phase                               | 3.0  |      | ns    |                       |

| CML                     | Clock low phase                                | 3.0  |      | ns    |                       |

| WBRCLKS                 | WB $\downarrow$ to RCLKS $\uparrow$ setup time | -0.1 |      | ns    |                       |

| WBRCLKH                 | WB $\downarrow$ to RCLKS $\uparrow$ hold time  |      | 7.0  | ns    |                       |

| ОСН                     | Old DO valid from RCLKS $\uparrow$             |      | 3.0  | ns    | OCA/OCH displayed for |

| OCA                     | New DO valid from RCLKS $\uparrow$             | 7.5  |      | ns    | Access Timed Output   |

| DWRRCLKS                | DI to RCLKS ↑ setup time                       | 0    |      | ns    |                       |

| DWRH                    | DI to WB ↑ hold time                           |      | 1.5  | ns    |                       |

#### Notes:

- 1. This behavior is valid for Access Timed Output and Pipelined Mode Output. The table shows the timings of an Access Timed Output.

- 2. In asynchronous write and synchronous read access to the same location, the new write data will be read out if the active write signal edge occurs before or at the same time as the active read clock edge. If WB changes to low after hold time, the data will be read.

3. A setup or hold time violation will result in unknown output data.

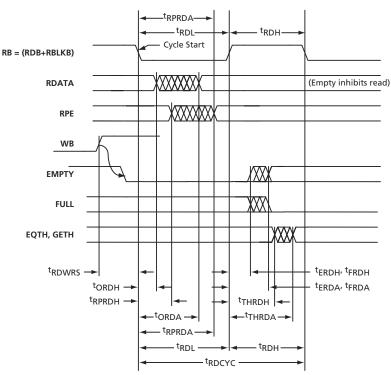

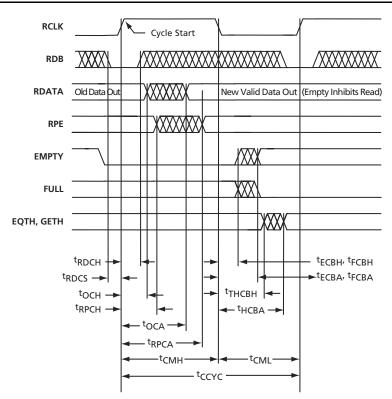

## **Asynchronous FIFO Read**

**Note:** The plot shows the normal operation status.

#### Figure 1-43 • Asynchronous FIFO Read

# Table 1-63T<sub>J</sub> = 0°C to 110°C; V<sub>DD</sub> = 2.3 V to 2.7 V for Commercial/industrialT<sub>J</sub> = -55°C to 150°C, V<sub>DD</sub> = 2.3 V to 2.7 V for Military/MIL-STD-883

| EMPTY, FULL, EQTH, & GETH valid hold<br>from RB ↑<br>EMPTY access from RB ↑ | 3.0 <sup>1</sup>                          | 0.5                                                                         | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Empty/full/thresh are invalid from the end of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                             | 3 0 <sup>1</sup>                          |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | hold until the new access is complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                             | 5.0                                       |                                                                             | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $\downarrow$ access from RB $\uparrow$                                      | 3.0 <sup>1</sup>                          |                                                                             | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DO access from RB $\downarrow$                                              | 7.5                                       |                                                                             | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DO valid from RB $\downarrow$                                               |                                           | 3.0                                                                         | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |