# E·XFL

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                         |

|--------------------------------|-------------------------------------------------------------------------|

| Product Status                 | Active                                                                  |

| Number of LABs/CLBs            |                                                                         |

| Number of Logic Elements/Cells | -                                                                       |

| Total RAM Bits                 | 73728                                                                   |

| Number of I/O                  | 158                                                                     |

| Number of Gates                | 300000                                                                  |

| Voltage - Supply               | 2.3V ~ 2.7V                                                             |

| Mounting Type                  | Surface Mount                                                           |

| Operating Temperature          | -55°C ~ 125°C (TC)                                                      |

| Package / Case                 | 208-BFCQFP with Tie Bar                                                 |

| Supplier Device Package        | 208-CQFP (75x75)                                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/apa300-cq208m |

|                                |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

### **General Description**

| ProASICPLUS Architecture                                         | . 1-2 |

|------------------------------------------------------------------|-------|

| Timing Control and Characteristics                               | 1-13  |

| Sample Implementations                                           |       |

| Adjustable Clock Delay                                           | 1-16  |

| Clock Skew Minimization                                          | 1-16  |

| PLL Electrical Specifications                                    | 1-21  |

| Design Environment                                               |       |

| ISP                                                              |       |

| Related Documents                                                | 1-29  |

| Package Thermal Characteristics                                  |       |

| Calculating Typical Power Dissipation                            |       |

| Operating Conditions                                             |       |

| Tristate Buffer Delays                                           | 1-45  |

| Output Buffer Delays                                             | 1-47  |

| Input Buffer Delays                                              | 1-49  |

| Global Input Buffer Delays                                       |       |

| Predicted Global Routing Delay                                   | 1-53  |

| Global Routing Skew                                              | 1-53  |

| Module Delays                                                    |       |

| Sample Macrocell Library Listing                                 |       |

| Embedded Memory Specifications                                   | 1-57  |

| Pin Description                                                  | 1-76  |

| Recommended Design Practice for V <sub>PN</sub> /V <sub>PP</sub> | 1-77  |

|                                                                  |       |

## Package Pin Assignments

| 100-Pin TQFP     | 2-1  |

|------------------|------|

| 144-Pin TQFP     | 2-3  |

| 208-Pin PQFP     |      |

| 208-Pin CQFP     | 2-12 |

| 352-Pin CQFP     |      |

| 456-Pin PBGA     |      |

| 144-Pin FBGA     |      |

| 256-Pin FBGA     |      |

| 484-Pin FBGA     |      |

| 676-Pin FBGA     |      |

| 896-Pin FBGA     |      |

| 1152-Pin FBGA    |      |

| 624-Pin CCGA/LGA | 2-78 |

## **Datasheet Information**

| List of Changes                                                               | 3-1 |

|-------------------------------------------------------------------------------|-----|

| Data Sheet Categories                                                         | 3-8 |

| Export Administration Regulations (EAR)                                       | 3-8 |

| Actel Safety Critical, Life Support, and High-Reliability Applications Policy | 3-8 |

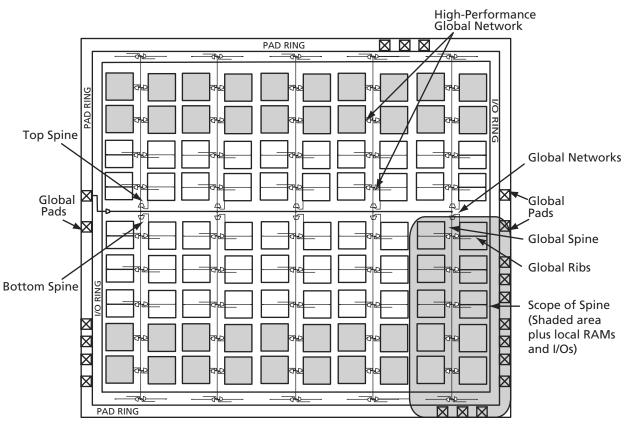

**Note:** This figure shows routing for only one global path. Figure 1-7 • High-Performance Global Network

### Table 1-1 • Clock Spines

|                                    | APA075 | APA150 | APA300 | APA450 | APA600 | APA750 | APA1000 |

|------------------------------------|--------|--------|--------|--------|--------|--------|---------|

| Global Clock Networks (Trees)      | 4      | 4      | 4      | 4      | 4      | 4      | 4       |

| Clock Spines/Tree                  | 6      | 8      | 8      | 12     | 14     | 16     | 22      |

| Total Spines                       | 24     | 32     | 32     | 48     | 56     | 64     | 88      |

| Top or Bottom Spine Height (Tiles) | 16     | 24     | 32     | 32     | 48     | 64     | 80      |

| Tiles in Each Top or Bottom Spine  | 512    | 768    | 1,024  | 1,024  | 1,536  | 2,048  | 2,560   |

| Total Tiles                        | 3,072  | 6,144  | 8,192  | 12,288 | 21,504 | 32,768 | 56,320  |

# Boundary Scan (JTAG)

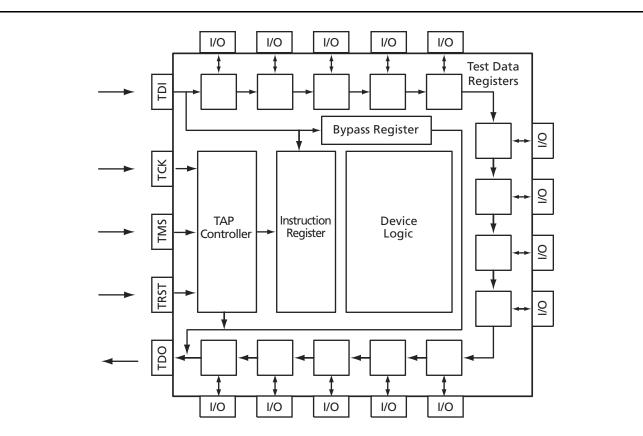

ProASIC<sup>PLUS</sup> devices are compatible with IEEE Standard 1149.1, which defines a set of hardware architecture and mechanisms for cost-effective, board-level testing. The basic ProASIC<sup>PLUS</sup> boundary-scan logic circuit is composed of the TAP (test access port), TAP controller, test data registers, and instruction register (Figure 1-12). This circuit supports all mandatory IEEE 1149.1 instructions (EXTEST, SAMPLE/PRELOAD and BYPASS) and the optional IDCODE instruction (Table 1-6).

Each test section is accessed through the TAP, which has five associated pins: TCK (test clock input), TDI and TDO (test data input and output), TMS (test mode selector) and TRST (test reset input). TMS, TDI and TRST are equipped with pull-up resistors to ensure proper operation when no input data is supplied to them. These pins are dedicated for boundary-scan test usage. Actel recommends that a nominal 20 k $\Omega$  pull-up resistor is added to TDO and TCK pins.

The TAP controller is a four-bit state machine (16 states) that operates as shown in Figure 1-13 on page 1-12. The '1's and '0's represent the values that must be present at TMS at a rising edge of TCK for the given state transition to occur. IR and DR indicate that the instruction register or the data register is operating in that state.

ProASIC<sup>PLUS</sup> devices have to be programmed at least once for complete boundary-scan functionality to be available. Prior to being programmed, EXTEST is not available. If boundary-scan functionality is required prior to programming, refer to online technical support on the Actel website and search for ProASIC<sup>PLUS</sup> BSDL.

| Figure 1-12 • ProASIC <sup>PLUS</sup> JTAG Boundary Scan | Test Logic Circuit |

|----------------------------------------------------------|--------------------|

|----------------------------------------------------------|--------------------|

### Table 1-6Boundary-Scan Opcodes

|                | Hex Opcode |

|----------------|------------|

| EXTEST         | 00         |

| SAMPLE/PRELOAD | 01         |

| IDCODE         | OF         |

| Table 1-6 • | Boundary-Scan | Opcodes |

|-------------|---------------|---------|

|-------------|---------------|---------|

|        | Hex Opcode |

|--------|------------|

| CLAMP  | 05         |

| BYPASS | FF         |

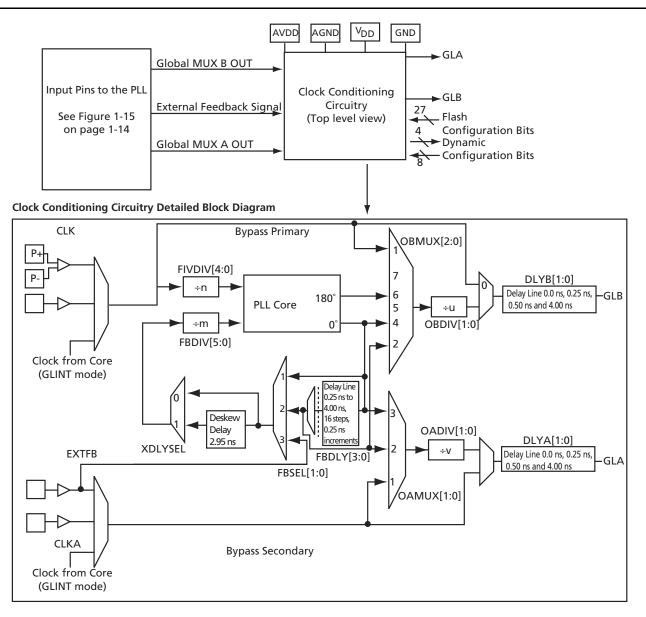

enable the user to define a wide range of frequency multipliers and divisors. The clock conditioning circuit can advance or delay the clock up to 8 ns (in increments of 0.25 ns) relative to the positive edge of the incoming reference clock. The system also allows for the selection of output frequency clock phases of 0° and 180°.

Prior to the application of signals to the rib drivers, they pass through programmable delay units, one per global network. These units permit the delaying of global signals relative to other signals to assist in the control of input set-up times. Not all possible combinations of input and output modes can be used. The degrees of freedom available in the bidirectional global pad system and in the clock conditioning circuit have been restricted. This avoids unnecessary and unwieldy design kit and software work.

### Notes:

- 1. FBDLY is a programmable delay line from 0 to 4 ns in 250 ps increments.

- 2. DLYA and DLYB are programmable delay lines, each with selectable values 0 ps, 250 ps, 500 ps, and 4 ns.

- 3. OBDIV will also divide the phase-shift since it takes place after the PLL Core.

Figure 1-14 • PLL Block – Top-Level View and Detailed PLL Block Diagram

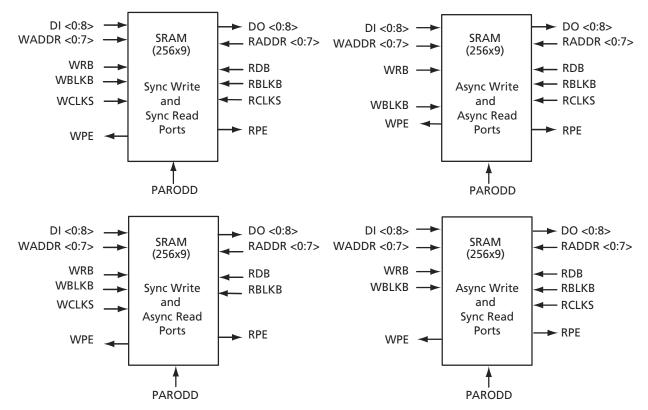

**Note:** Each RAM block contains a multiplexer (called DMUX) for each output signal, increasing design efficiency. These DMUX cells do not consume any core logic tiles and connect directly to high-speed routing resources between the RAM blocks. They are used when RAM blocks are cascaded and are automatically inserted by the software tools.

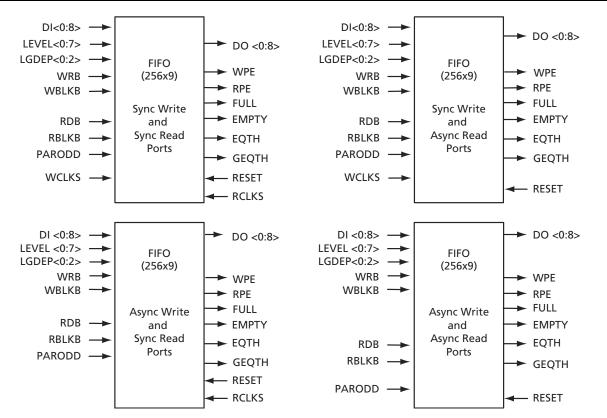

Figure 1-21 • Example SRAM Block Diagrams

| Table 1-14 • | Memory | Block SRAM | Interface | Signals |

|--------------|--------|------------|-----------|---------|

|--------------|--------|------------|-----------|---------|

| SRAM Signal | Bits | In/Out | Description                                                          |

|-------------|------|--------|----------------------------------------------------------------------|

| WCLKS       | 1    | In     | Write clock used on synchronization on write side                    |

| RCLKS       | 1    | In     | Read clock used on synchronization on read side                      |

| RADDR<0:7>  | 8    | In     | Read address                                                         |

| RBLKB       | 1    | In     | Read block select (active Low)                                       |

| RDB         | 1    | In     | Read pulse (active Low)                                              |

| WADDR<0:7>  | 8    | In     | Write address                                                        |

| WBLKB       | 1    | In     | Write block select (active Low)                                      |

| DI<0:8>     | 9    | In     | Input data bits <0:8>, <8> can be used for parity In                 |

| WRB         | 1    | In     | Write pulse (active Low)                                             |

| DO<0:8>     | 9    | Out    | Output data bits <0:8>, <8> can be used for parity Out               |

| RPE         | 1    | Out    | Read parity error (active High)                                      |

| WPE         | 1    | Out    | Write parity error (active High)                                     |

| PARODD      | 1    | In     | Selects Odd parity generation/detect when High, Even parity when Low |

Note: Not all signals shown are used in all modes.

**Note:** Each RAM block contains a multiplexer (called DMUX) for each output signal, increasing design efficiency. These DMUX cells do not consume any core logic tiles and connect directly to high-speed routing resources between the RAM blocks. They are used when RAM blocks are cascaded and are automatically inserted by the software tools.

Figure 1-22 • Basic FIFO Block Diagrams

| FIFO Signal | Bits | In/Out | Description                                                                                                                                 |

|-------------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|

| WCLKS       | 1    | In     | Write clock used for synchronization on write side                                                                                          |

| RCLKS       | 1    | In     | Read clock used for synchronization on read side                                                                                            |

| LEVEL <0:7> | 8    | In     | Direct configuration implements static flag logic                                                                                           |

| RBLKB       | 1    | In     | Read block select (active Low)                                                                                                              |

| RDB         | 1    | In     | Read pulse (active Low)                                                                                                                     |

| RESET       | 1    | In     | Reset for FIFO pointers (active Low)                                                                                                        |

| WBLKB       | 1    | In     | Write block select (active Low)                                                                                                             |

| DI<0:8>     | 9    | In     | Input data bits <0:8>, <8> will be generated parity if PARGEN is true                                                                       |

| WRB         | 1    | In     | Write pulse (active Low)                                                                                                                    |

| FULL, EMPTY | 2    | Out    | FIFO flags. FULL prevents write and EMPTY prevents read                                                                                     |

| EQTH, GEQTH | 2    | Out    | EQTH is true when the FIFO holds the number of words specified by the LEVEL signal. GEQTH is true when the FIFO holds (LEVEL) words or more |

| DO<0:8>     | 9    | Out    | Output data bits <0:8>. <8> will be parity output if PARGEN is true.                                                                        |

| RPE         | 1    | Out    | Read parity error (active High)                                                                                                             |

| WPE         | 1    | Out    | Write parity error (active High)                                                                                                            |

| LGDEP <0:2> | 3    | In     | Configures DEPTH of the FIFO to 2 (LGDEP+1)                                                                                                 |

| PARODD      | 1    | In     | Parity generation/detect – Even when Low, Odd when High                                                                                     |

| Table 1-15 • | Memory | <b>Block FIFO</b> | Interface | Signals |

|--------------|--------|-------------------|-----------|---------|

|--------------|--------|-------------------|-----------|---------|

### Logic-Tile Contribution—Plogic

Plogic, the logic-tile component of AC power dissipation, is given by

$$P_{logic} = P3 * mc * Fs$$

where:

- P3 =  $1.4 \mu$ W/MHz is the average power consumption of a logic tile per MHz of its output toggling rate. The maximum output toggling rate is Fs/2.

- mc = the number of logic tiles switching during each Fs cycle

- Fs = the clock frequency

### I/O Output Buffer Contribution—Poutputs

Poutputs, the I/O component of AC power dissipation, is given by

$$P_{outputs} = (P4 + (C_{load} * V_{DDP}^{2})) * p * Fp$$

where:

P4 =  $326 \mu$ W/MHz is the intrinsic power consumption of an output pad normalized per MHz of the output frequency. This is the total I/O current V<sub>DDP</sub>

C<sub>load</sub> = the output load

- p = the number of outputs

- Fp = the average output frequency

### I/O Input Buffer's Buffer Contribution—P<sub>inputs</sub>

The input's component of AC power dissipation is given by

$$P_{inputs} = P8 * q * Fq$$

where:

- P8 = 29  $\mu$ W/MHz is the intrinsic power consumption of an input pad normalized per MHz of the input frequency.

- q = the number of inputs

- Fq = the average input frequency

### PLL Contribution—P<sub>pll</sub>

$P_{p|l} = P9 * N_{p|l}$

where:

P9 = 7.5 mW. This value has been estimated at maximum PLL clock frequency.

N<sub>PII</sub> = number of PLLs used

### RAM Contribution—P<sub>memory</sub>

Finally, P<sub>memory</sub>, the memory component of AC power consumption, is given by

$$P_{memory} = P6 * N_{memory} * F_{memory} * E_{memory}$$

where:

| P6                  | = | 175 $\mu$ W/MHz is the average power consumption of a memory block per MHz of the clock                                                                     |

|---------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N <sub>memory</sub> | = | the number of RAM/FIFO blocks                                                                                                                               |

|                     |   | (1 block = 256 words * 9 bits)                                                                                                                              |

| F <sub>memory</sub> | = | the clock frequency of the memory                                                                                                                           |

| Ememory             | = | the average number of active blocks divided by the total number of blocks (N) of the memory.                                                                |

|                     |   | <ul> <li>Typical values for E<sub>memory</sub> would be 1/4 for a 1k x 8,9,16, 32 memory and 1/16 for a 4kx8, 9, 16, and 32 memory configuration</li> </ul> |

• In addition, an application-dependent component to  $E_{memory}$  can be considered. For example, for a 1kx8 memory configuration using only 1 cycle out of 2,  $E_{memory} = 1/4*1/2 = 1/8$

|                 |                               | Commercial/Industrial/Military/MIL-STD-883 |                 |       |  |

|-----------------|-------------------------------|--------------------------------------------|-----------------|-------|--|

| Parameter       | Condition                     | Minimum                                    | Maximum         | Units |  |

| V <sub>PP</sub> | During Programming            | 15.8                                       | 16.5            | V     |  |

|                 | Normal Operation <sup>1</sup> | 0                                          | 16.5            | V     |  |

| V <sub>PN</sub> | During Programming            | -13.8                                      | -13.2           | V     |  |

|                 | Normal Operation <sup>2</sup> | -13.8                                      | 0.5             | V     |  |

| РР              | During Programming            |                                            | 25              | mA    |  |

| I <sub>PN</sub> | During Programming            |                                            | 10              | mA    |  |

| AVDD            |                               | V <sub>DD</sub>                            | V <sub>DD</sub> | V     |  |

| AGND            |                               | GND                                        | GND             | V     |  |

### Table 1-20 • Recommended Maximum Operating Conditions Programming and PLL Supplies

Notes:

Please refer to the "VPP Programming Supply Pin" section on page 1-77 for more information.

Please refer to the "VPN Programming Supply Pin" section on page 1-77 for more information.

#### Table 1-21 • Recommended Operating Conditions

|                                        |                                      | Limits                         |                                |                                                    |  |  |  |  |  |

|----------------------------------------|--------------------------------------|--------------------------------|--------------------------------|----------------------------------------------------|--|--|--|--|--|

| Parameter                              | Symbol                               | Commercial                     | Industrial                     | Military/MIL-STD-883                               |  |  |  |  |  |

| DC Supply Voltage (2.5 V I/Os)         | $V_{\text{DD}}$ and $V_{\text{DDP}}$ | $2.5 V \pm 0.2 V$              | 2.5 V ± 0.2 V                  | 2.5 V ± 0.2 V                                      |  |  |  |  |  |

| DC Supply Voltage (3.3 V I/Os)         | V <sub>DDP</sub><br>V <sub>DD</sub>  | 3.3 V ± 0.3 V<br>2.5 V ± 0.2 V | 3.3 V ± 0.3 V<br>2.5 V ± 0.2 V | 3.3 V ± 0.3 V<br>2.5 V ± 0.2 V                     |  |  |  |  |  |

| Operating Ambient Temperature Range    | T <sub>A</sub> , T <sub>C</sub>      | 0°C to 70°C                    | –40°C to 85°C                  | –55°C (T <sub>A</sub> ) to 125°C (T <sub>C</sub> ) |  |  |  |  |  |

| Maximum Operating Junction Temperature | Tj                                   | 110°C                          | 110°C                          | 150°C                                              |  |  |  |  |  |

Note: For I/O long-term reliability, external pull-up resistors cannot be used to increase output voltage above V<sub>DDP</sub>.

| Symbol           |                                                                                  |                                          |              | Commercial/Industrial/<br>Military/MIL-STD-883 <sup>1, 2</sup> |           |       |  |  |

|------------------|----------------------------------------------------------------------------------|------------------------------------------|--------------|----------------------------------------------------------------|-----------|-------|--|--|

|                  | Parameter                                                                        | Conditions                               | Min.         | Тур.                                                           | Max.      | Units |  |  |

| I <sub>OSH</sub> | Output Short Circuit Current High<br>High Drive (OB25LPH)<br>Low Drive (OB25LPL) | $V_{IN} = V_{SS}$<br>$V_{IN} = V_{SS}$   | -120<br>-100 |                                                                |           | mA    |  |  |

| I <sub>OSL</sub> | Output Short Circuit Current Low<br>High Drive (OB25LPH)<br>Low Drive (OB25LPL)  | $V_{IN} = V_{DDP}$<br>$V_{IN} = V_{DDP}$ |              |                                                                | 100<br>30 | mA    |  |  |

| C <sub>I/O</sub> | I/O Pad Capacitance                                                              |                                          |              |                                                                | 10        | pF    |  |  |

| C <sub>CLK</sub> | Clock Input Pad Capacitance                                                      |                                          |              |                                                                | 10        | pF    |  |  |

### Table 1-22 • DC Electrical Specifications (V<sub>DDP</sub> = 2.5 V $\pm$ 0.2V) (Continued)

Notes:

1. All process conditions. Commercial/Industrial: Junction Temperature: -40 to +110°C.

2. All process conditions. Military: Junction Temperature: -55 to +150°C.

3. All –F parts are available only as commercial.

4. No pull-up resistor.

5. This will not exceed 2 mA total per device.

6. During transitions, the input signal may overshoot to  $V_{DDP}$  +1.0V for a limited time of no larger than 10% of the duty cycle.

7. During transitions, the input signal may undershoot to -1.0V for a limited time of no larger than 10% of the duty cycle.

# Table 1-23DC Electrical Specifications (VVDE3.3 V $\pm$ 0.3 Vand VVDE0.2 V(Continued)Applies to Commercial and Industrial Temperature Only

|                  |                                                                                             |                                                |                    | Comme        | rcial/In | dustrial <sup>1</sup> |       |

|------------------|---------------------------------------------------------------------------------------------|------------------------------------------------|--------------------|--------------|----------|-----------------------|-------|

| Symbol           | Parameter                                                                                   | Conditions                                     |                    | Min.         | Тур.     | Max.                  | Units |

| I <sub>OZ</sub>  |                                                                                             | $V_{OH} = GND \text{ or } V_{DD}$              | Std.               | -10          |          | 10                    | μA    |

|                  | Current                                                                                     |                                                | -F <sup>2, 4</sup> | -10          |          | 100                   | μA    |

| I <sub>OSH</sub> | Output Short Circuit Current<br>High<br>3.3 V High Drive (OB33P)<br>3.3 V Low Drive (OB33L) | V <sub>IN</sub> = GND<br>V <sub>IN</sub> = GND |                    | -200<br>-100 |          |                       |       |

| I <sub>OSL</sub> | Output Short Circuit Current<br>Low<br>3.3 V High Drive<br>3.3 V Low Drive                  | $V_{IN} = V_{DD}$<br>$V_{IN} = V_{DD}$         |                    |              |          | 200<br>100            |       |

| CI/O             | I/O Pad Capacitance                                                                         |                                                |                    |              |          | 10                    | pF    |

| C <sub>CLK</sub> | Clock Input Pad Capacitance                                                                 |                                                |                    |              |          | 10                    | pF    |

Notes:

1. All process conditions. Commercial/Industrial: Junction Temperature: -40 to +110°C.

2. All –F parts are only available as commercial.

3. No pull-up resistor required.

4. This will not exceed 2 mA total per device.

5. During transitions, the input signal may overshoot to  $V_{DDP}$ +1.0 V for a limited time of no larger than 10% of the duty cycle.

6. During transitions, the input signal may undershoot to -1.0 V for a limited time of no larger than 10% of the duty cycle.

|                  |                                    |                            |                    | Commercial/<br>Industrial <sup>2,3</sup> |                        |                     |                        |       |

|------------------|------------------------------------|----------------------------|--------------------|------------------------------------------|------------------------|---------------------|------------------------|-------|

| Symbol           | Parameter                          | Condition                  |                    | Min.                                     | Max.                   | Min.                | Max.                   | Units |

| V <sub>DD</sub>  | Supply Voltage for Core            |                            |                    | 2.3                                      | 2.7                    | 2.3                 | 2.7                    | V     |

| V <sub>DDP</sub> | Supply Voltage for I/O Ring        |                            |                    | 3.0                                      | 3.6                    | 3.0                 | 3.6                    | V     |

| V <sub>IH</sub>  | Input High Voltage                 |                            |                    | $0.5V_{DDP}$                             | V <sub>DDP</sub> + 0.5 | 0.5V <sub>DDP</sub> | V <sub>DDP</sub> + 0.5 | V     |

| V <sub>IL</sub>  | Input Low Voltage                  |                            |                    | -0.5                                     | 0.3V <sub>DDP</sub>    | -0.5                | 0.3V <sub>DDP</sub>    | V     |

| I <sub>IPU</sub> | Input Pull-up Voltage <sup>4</sup> |                            |                    | $0.7V_{\text{DDP}}$                      |                        | 0.7V <sub>DDP</sub> |                        | V     |

| I <sub>IL</sub>  | Input Leakage Current <sup>5</sup> | $0 < V_{IN} < V_{DDP}$     | Std.               | -10                                      | 10                     | -50                 | 50                     | μΑ    |

|                  |                                    |                            | -F <sup>3, 6</sup> | -10                                      | 100                    |                     |                        | μΑ    |

| V <sub>OH</sub>  | Output High Voltage                | I <sub>OUT</sub> = -500 μA |                    | $0.9V_{\text{DDP}}$                      |                        | 0.9V <sub>DDP</sub> |                        | V     |

| V <sub>OL</sub>  | Output Low Voltage                 | l <sub>OUT</sub> = 1500 μA |                    |                                          | 0.1V <sub>DDP</sub>    |                     | 0.1V <sub>DDP</sub>    | V     |

| C <sub>IN</sub>  | Input Pin Capacitance (except CLK) |                            |                    |                                          | 10                     |                     | 10                     | pF    |

| C <sub>CLK</sub> | CLK Pin Capacitance                |                            |                    | 5                                        | 12                     | 5                   | 12                     | pF    |

### Notes:

1. For PCI operation, use GL33, OTB33PH, OB33PH, IOB33PH, IB33, or IB33S macro library cell only.

2. All process conditions. Junction Temperature: -40 to +110°C for Commercial and Industrial devices and -55 to +125°C for Military.

3. All –F parts are available as commercial only.

4. This specification is guaranteed by design. It is the minimum voltage to which pull-up resistors are calculated to pull a floated network. Designers with applications sensitive to static power utilization should ensure that the input buffer is conducting minimum current at this input voltage.

5. Input leakage currents include hi-Z output leakage for all bidirectional buffers with tristate outputs.

6. The sum of the leakage currents for all inputs shall not exceed 2mA per device.

# **Tristate Buffer Delays**

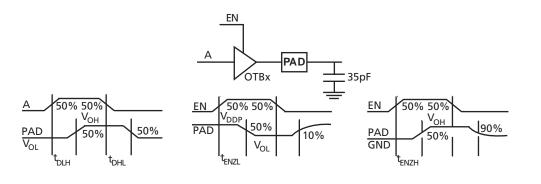

### Figure 1-26 • Tristate Buffer Delays

#### Table 1-27 • Worst-Case Commercial Conditions $V_{DDP} = 3.0 \text{ V}, V_{DD} = 2.3 \text{ V}, 35 \text{ pF load}, T_1 = 70^{\circ}\text{C}$

|            |                                               | 1    |     |      |     | 1 2  |     | - 3  | Max<br>t <sub>ENZL</sub> 4 |       |  |

|------------|-----------------------------------------------|------|-----|------|-----|------|-----|------|----------------------------|-------|--|

| Macro Type | Description                                   | Std. | -F  | Std. | -F  | Std. | -F  | Std. | -F                         | Units |  |

| OTB33PH    | 3.3 V, PCI Output Current, High Slew Rate     | 2.0  | 2.4 | 2.2  | 2.6 | 2.2  | 2.6 | 2.0  | 2.4                        | ns    |  |

| OTB33PN    | 3.3 V, High Output Current, Nominal Slew Rate | 2.2  | 2.6 | 2.9  | 3.5 | 2.4  | 2.9 | 2.1  | 2.5                        | ns    |  |

| OTB33PL    | 3.3 V, High Output Current, Low Slew Rate     | 2.5  | 3.0 | 3.2  | 3.9 | 2.7  | 3.3 | 2.8  | 3.4                        | ns    |  |

| OTB33LH    | 3.3 V, Low Output Current, High Slew Rate     | 2.6  | 3.1 | 4.0  | 4.8 | 2.8  | 3.4 | 3.0  | 3.6                        | ns    |  |

| OTB33LN    | 3.3 V, Low Output Current, Nominal Slew Rate  | 2.9  | 3.5 | 4.3  | 5.2 | 3.2  | 3.8 | 4.1  | 4.9                        | ns    |  |

| OTB33LL    | 3.3 V, Low Output Current, Low Slew Rate      | 3.0  | 3.6 | 5.6  | 6.7 | 3.3  | 3.9 | 5.5  | 6.6                        | ns    |  |

Notes:

- 1. t<sub>DLH</sub>=Data-to-Pad High

- 2. t<sub>DHL</sub>=Data-to-Pad Low

- 3. t<sub>ENZH</sub>=Enable-to-Pad, Z to High

- 4.  $t_{ENZL}$  = Enable-to-Pad, Z to Low

- 5. All –F parts are only available as commercial.

### Table 1-28 Worst-Case Commercial Conditions

$V_{DDP}$  = 2.3 V,  $V_{DD}$  = 2.3 V, 35 pF load,  $T_J$  = 70°C

|            |                                                                       | Max<br>t <sub>DLH</sub> 1 |     | t <sub>DLH</sub> <sup>1</sup> |     | Ma<br>t <sub>DH</sub> | -   | Ma<br>t <sub>EN2</sub> | 3   | Ma<br>t <sub>en</sub> | 4 |  |

|------------|-----------------------------------------------------------------------|---------------------------|-----|-------------------------------|-----|-----------------------|-----|------------------------|-----|-----------------------|---|--|

| Macro Type | Description                                                           | Std.                      | F   | Std.                          | -F  | Std.                  | -F  | Std.                   | -F  | Units                 |   |  |

| OTB25LPHH  | 2.5 V, Low Power, High Output Current, High Slew Rate <sup>5</sup>    | 2.0                       | 2.4 | 2.1                           | 2.5 | 2.3                   | 2.7 | 2.0                    | 2.4 | ns                    |   |  |

| OTB25LPHN  | 2.5 V, Low Power, High Output Current, Nominal Slew Rate <sup>5</sup> | 2.4                       | 2.9 | 3.0                           | 3.6 | 2.7                   | 3.2 | 2.1                    | 2.5 | ns                    |   |  |

| OTB25LPHL  | 2.5 V, Low Power, High Output Current, Low Slew Rate <sup>5</sup>     | 2.9                       | 3.5 | 3.2                           | 3.8 | 3.1                   | 3.8 | 2.7                    | 3.2 | ns                    |   |  |

| OTB25LPLH  | 2.5 V, Low Power, Low Output Current, High Slew Rate <sup>5</sup>     | 2.7                       | 3.3 | 4.6                           | 5.5 | 3.0                   | 3.6 | 2.6                    | 3.1 | ns                    |   |  |

### Notes:

- 1. t<sub>DLH</sub>=Data-to-Pad High

- 2. t<sub>DHL</sub>=Data-to-Pad Low

- 3.  $t_{ENZH}$ =Enable-to-Pad, Z to High

- 4.  $t_{ENZL}$  = Enable-to-Pad, Z to Low

- 5. Low power I/O work with  $V_{DDP}$ =2.5 V ±10% only.  $V_{DDP}$ =2.3 V for delays.

- 6. All –F parts are only available as commercial.

### Table 1-37 • Worst-Case Military Conditions

$V_{DDP}$  = 3.0V,  $V_{DD}$  = 2.3V,  $T_{J}$  = 125°C for Military/MIL-STD-883

|            |                                                                             | Max. t <sub>INYH</sub> 1 | Max. t <sub>INYL</sub> <sup>2</sup> |       |

|------------|-----------------------------------------------------------------------------|--------------------------|-------------------------------------|-------|

| Macro Type | Description                                                                 | Std.                     | Std.                                | Units |

| IB33       | 3.3V, CMOS Input Levels <sup>3</sup> , No Pull-up Resistor                  | 0.5                      | 0.6                                 | ns    |

| IB33S      | 3.3V, CMOS Input Levels <sup>3</sup> , No Pull-up Resistor, Schmitt Trigger | 0.6                      | 0.8                                 | ns    |

### Notes:

- 1.  $t_{INYH} = Input Pad-to-Y High$

- 2.  $t_{INYL} = Input Pad-to-Y Low$

- 3. LVTTL delays are the same as CMOS delays.

- 4. For LP Macros, V<sub>DDP</sub>=2.3V for delays.

### Table 1-38 • Worst-Case Military Conditions

### $V_{DDP}$ = 2.3V, $V_{DD}$ = 2.3V, $T_J$ = 125°C for Military/MIL-STD-883

|            |                                                                   | Max. t <sub>INYH</sub> 1 | Max. t <sub>INYL</sub> 2 |       |

|------------|-------------------------------------------------------------------|--------------------------|--------------------------|-------|

| Macro Type | Description                                                       | Std.                     | Std.                     | Units |

| IB25LP     | 2.5V, CMOS Input Levels <sup>3</sup> , Low Power                  | 0.9                      | 0.7                      | ns    |

| IB25LPS    | 2.5V, CMOS Input Levels <sup>3</sup> , Low Power, Schmitt Trigger | 0.8                      | 1.0                      | ns    |

### Notes:

- 1.  $t_{INYH} = Input Pad-to-Y High$

- 2.  $t_{INYL} = Input Pad-to-Y Low$

- 3. LVTTL delays are the same as CMOS delays.

- 4. For LP Macros,  $V_{DDP}$ =2.3V for delays.

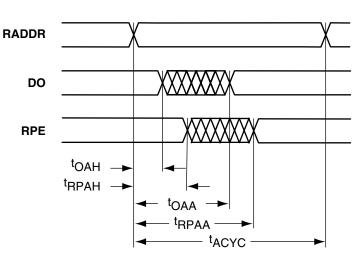

# Asynchronous SRAM Read, Address Controlled, RDB=0

### **Note:** The plot shows the normal operation status.

### Figure 1-34 • Asynchronous SRAM Read, Address Controlled, RDB=0

# Table 1-55•T\_J = 0°C to 110°C; V\_{DD} = 2.3 V to 2.7 V for Commercial/industrialT\_J = -55°C to 150°C, V\_{DD} = 2.3 V to 2.7 V for Military/MIL-STD-883B

| Symbol t <sub>xxx</sub> | Description                      | Min. | Max. | Units | Notes |

|-------------------------|----------------------------------|------|------|-------|-------|

| ACYC                    | Read cycle time                  | 7.5  |      | ns    |       |

| OAA                     | New DO access from RADDR stable  | 7.5  |      | ns    |       |

| OAH                     | Old DO hold from RADDR stable    |      | 3.0  | ns    |       |

| RPAA                    | New RPE access from RADDR stable | 10.0 |      | ns    |       |

| RPAH                    | Old RPE hold from RADDR stable   |      | 3.0  | ns    |       |

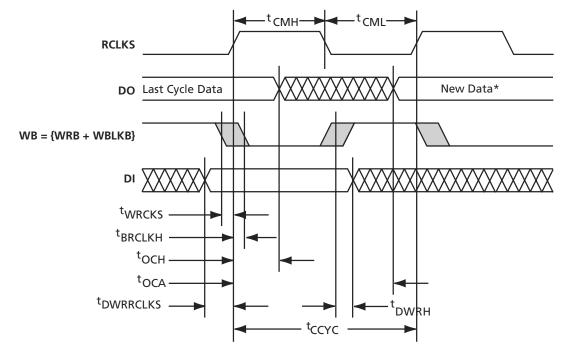

# Asynchronous Write and Synchronous Read to the Same Location

\* New data is read if WB  $\downarrow$  occurs before setup time. The stored data is read if WB  $\downarrow$  occurs after hold time.

### Note: The plot shows the normal operation status.

| Figure 1-38 • | Asynchronous | Write and Synchronous Read to the Same Location |

|---------------|--------------|-------------------------------------------------|

|---------------|--------------|-------------------------------------------------|

# Table 1-59T<sub>J</sub> = 0°C to 110°C; V<sub>DD</sub> = 2.3 V to 2.7 V for Commercial/industrialT<sub>J</sub> = -55°C to 150°C, V<sub>DD</sub> = 2.3 V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                                    | Min. | Max. | Units | Notes                                        |

|-------------------------|------------------------------------------------|------|------|-------|----------------------------------------------|

| ССҮС                    | Cycle time                                     | 7.5  |      | ns    |                                              |

| СМН                     | Clock high phase                               | 3.0  |      | ns    |                                              |

| CML                     | Clock low phase                                | 3.0  |      | ns    |                                              |

| WBRCLKS                 | WB $\downarrow$ to RCLKS $\uparrow$ setup time | -0.1 |      | ns    |                                              |

| WBRCLKH                 | WB $\downarrow$ to RCLKS $\uparrow$ hold time  |      | 7.0  | ns    |                                              |

| ОСН                     | Old DO valid from RCLKS $\uparrow$             |      | 3.0  | ns    | OCA/OCH displayed for<br>Access Timed Output |

| OCA                     | New DO valid from RCLKS $\uparrow$             | 7.5  |      | ns    |                                              |

| DWRRCLKS                | DI to RCLKS ↑ setup time                       | 0    |      | ns    |                                              |

| DWRH                    | DI to WB ↑ hold time                           |      | 1.5  | ns    |                                              |

### Notes:

- 1. This behavior is valid for Access Timed Output and Pipelined Mode Output. The table shows the timings of an Access Timed Output.

- 2. In asynchronous write and synchronous read access to the same location, the new write data will be read out if the active write signal edge occurs before or at the same time as the active read clock edge. If WB changes to low after hold time, the data will be read.

3. A setup or hold time violation will result in unknown output data.

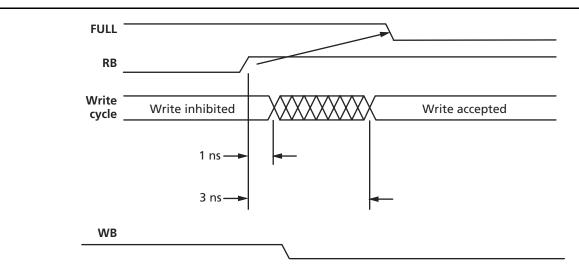

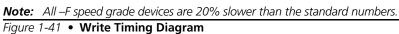

Note: All – F speed grade devices are 20% slower than the standard numbers.

Figure 1-42 • Read Timing Diagram

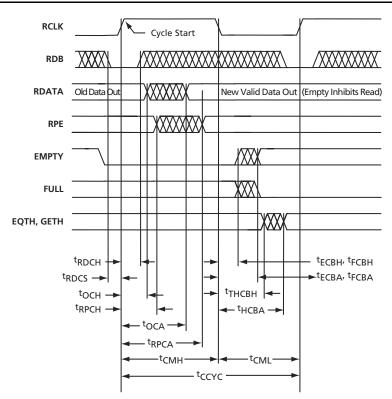

# Synchronous FIFO Read, Access Timed Output Strobe (Synchronous Transparent)

### Note: The plot shows the normal operation status.

### *Figure 1-45* • Synchronous FIFO Read, Access Timed Output Strobe (Synchronous Transparent)

# Table 1-65T<sub>J</sub> = 0°C to 110°C; V<sub>DD</sub> = 2.3 V to 2.7 V for Commercial/industrialT<sub>J</sub> = -55°C to 150°C, V<sub>DD</sub> = 2.3 V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                                                           | Min.             | Max. | Units | Notes                                                                               |

|-------------------------|-----------------------------------------------------------------------|------------------|------|-------|-------------------------------------------------------------------------------------|

| CCYC                    | Cycle time                                                            | 7.5              |      | ns    |                                                                                     |

| CMH                     | Clock high phase                                                      | 3.0              |      | ns    |                                                                                     |

| CML                     | Clock low phase                                                       | 3.0              |      | ns    |                                                                                     |

| ECBA                    | New EMPTY access from RCLKS $\downarrow$                              | 3.0 <sup>1</sup> |      | ns    |                                                                                     |

| FCBA                    | FULL $\downarrow$ access from RCLKS $\downarrow$                      | 3.0 <sup>1</sup> |      | ns    |                                                                                     |

| ЕСВН, FCBH,<br>ТНСВН    | Old EMPTY, FULL, EQTH, & GETH valid hold time from RCLKS $\downarrow$ |                  | 1.0  | ns    | Empty/full/thresh are invalid from the end of hold until the new access is complete |

| OCA                     | New DO access from RCLKS ↑                                            | 7.5              |      | ns    |                                                                                     |

| OCH                     | Old DO valid from RCLKS 1                                             |                  | 3.0  | ns    |                                                                                     |

| RDCH                    | RDB hold from RCLKS 个                                                 | 0.5              |      | ns    |                                                                                     |

| RDCS                    | RDB setup to RCLKS ↑                                                  | 1.0              |      | ns    |                                                                                     |

| RPCA                    | New RPE access from RCLKS $\uparrow$                                  | 9.5              |      | ns    |                                                                                     |

| RPCH                    | Old RPE valid from RCLKS $\uparrow$                                   |                  | 3.0  | ns    |                                                                                     |

| HCBA                    | EQTH or GETH access from RCLKS $\downarrow$                           | 4.5              |      | ns    |                                                                                     |

### Notes:

1. At fast cycles, ECBA and FCBA = MAX (7.5 ns – CMH), 3.0 ns.

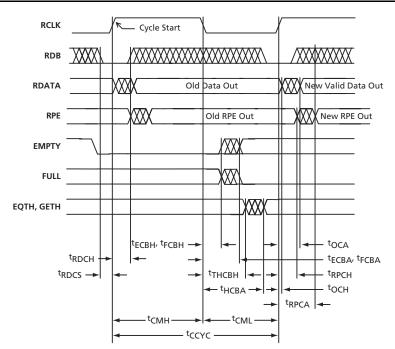

# Synchronous FIFO Read, Pipeline Mode Outputs (Synchronous Pipelined)

### Note: The plot shows the normal operation status.

| Figure 1-46 • | Synchronous F | IFO Read, Pipeline | Mode Outputs | (Synchronous Pipelined) |

|---------------|---------------|--------------------|--------------|-------------------------|

|---------------|---------------|--------------------|--------------|-------------------------|

# Table 1-66T\_J = 0°C to 110°C; V\_{DD} = 2.3 V to 2.7 V for Commercial/industrialT\_J = -55°C to 150°C, V\_{DD} = 2.3 V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                                                           | Min.             | Max. | Units | Notes                                                                               |

|-------------------------|-----------------------------------------------------------------------|------------------|------|-------|-------------------------------------------------------------------------------------|

| CCYC                    | Cycle time                                                            | 7.5              |      | ns    |                                                                                     |

| CMH                     | Clock high phase                                                      | 3.0              |      | ns    |                                                                                     |

| CML                     | Clock low phase                                                       | 3.0              |      | ns    |                                                                                     |

| ECBA                    | New EMPTY access from RCLKS $\downarrow$                              | 3.0 <sup>1</sup> |      | ns    |                                                                                     |

| FCBA                    | FULL $\downarrow$ access from RCLKS $\downarrow$                      | 3.0 <sup>1</sup> |      | ns    |                                                                                     |

| ЕСВН, FCBH,<br>ТНСВН    | Old EMPTY, FULL, EQTH, & GETH valid hold time from RCLKS $\downarrow$ |                  | 1.0  | ns    | Empty/full/thresh are invalid from the end of hold until the new access is complete |

| OCA                     | New DO access from RCLKS $\uparrow$                                   | 2.0              |      | ns    |                                                                                     |

| OCH                     | Old DO valid from RCLKS $\uparrow$                                    |                  | 0.75 | ns    |                                                                                     |

| RDCH                    | RDB hold from RCLKS 个                                                 | 0.5              |      | ns    |                                                                                     |

| RDCS                    | RDB setup to RCLKS ↑                                                  | 1.0              |      | ns    |                                                                                     |

| RPCA                    | New RPE access from RCLKS ↑                                           | 4.0              |      | ns    |                                                                                     |

| RPCH                    | Old RPE valid from RCLKS ↑                                            |                  | 1.0  | ns    |                                                                                     |

| НСВА                    | EQTH or GETH access from RCLKS $\downarrow$                           | 4.5              |      | ns    |                                                                                     |

### Notes:

1. At fast cycles, ECBA and FCBA = MAX (7.5 ns - CMS), 3.0 ns.

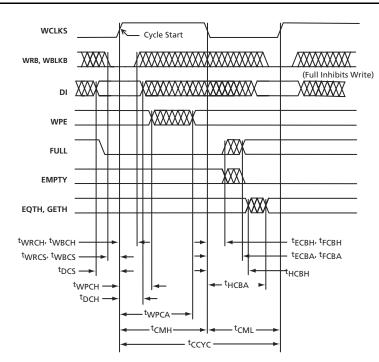

# Synchronous FIFO Write

**Note:** The plot shows the normal operation status.

### Figure 1-47 • Synchronous FIFO Write

# Table 1-67T<sub>J</sub> = 0°C to 110°C; V<sub>DD</sub> = 2.3 V to 2.7 V for Commercial/industrialT<sub>J</sub> = -55°C to 150°C, V<sub>DD</sub> = 2.3 V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                                                           | Min.             | Max. | Units | Notes                                                                               |

|-------------------------|-----------------------------------------------------------------------|------------------|------|-------|-------------------------------------------------------------------------------------|

| CCYC                    | Cycle time                                                            | 7.5              |      | ns    |                                                                                     |

| СМН                     | Clock high phase                                                      | 3.0              |      | ns    |                                                                                     |

| CML                     | Clock low phase                                                       | 3.0              |      | ns    |                                                                                     |

| DCH                     | DI hold from WCLKS ↑                                                  | 0.5              |      | ns    |                                                                                     |

| DCS                     | DI setup to WCLKS ↑                                                   | 1.0              |      | ns    |                                                                                     |

| FCBA                    | New FULL access from WCLKS $\downarrow$                               | 3.0 <sup>1</sup> |      | ns    |                                                                                     |

| ECBA                    | EMPTY $\downarrow$ access from WCLKS $\downarrow$                     | 3.0 <sup>1</sup> |      | ns    |                                                                                     |

| ЕСВН,<br>FCBH,<br>HCBH  | Old EMPTY, FULL, EQTH, & GETH valid hold time from WCLKS $\downarrow$ |                  | 1.0  | ns    | Empty/full/thresh are invalid from the end of hold until the new access is complete |

| НСВА                    | EQTH or GETH access from WCLKS $\downarrow$                           | 4.5              |      | ns    |                                                                                     |

| WPCA                    | New WPE access from WCLKS $\uparrow$                                  | 3.0              |      | ns    | WPE is invalid, while PARGEN is active                                              |

| WPCH                    | Old WPE valid from WCLKS ↑                                            |                  | 0.5  | ns    |                                                                                     |

| WRCH, WBCH              | WRB & WBLKB hold from WCLKS $\uparrow$                                | 0.5              |      | ns    |                                                                                     |

| WRCS, WBCS              | WRB & WBLKB setup to WCLKS ↑                                          | 1.0              |      | ns    |                                                                                     |

### Notes:

1. At fast cycles, ECBA and FCBA = MAX (7.5 ns – CMH), 3.0 ns.

# **Pin Description**

### **User Pins**

### I/O User Input/Output

The I/O pin functions as an input, output, tristate, or bidirectional buffer. Input and output signal levels are compatible with standard LVTTL and LVCMOS specifications. Unused I/O pins are configured as inputs with pull-up resistors.

### NC No Connect

To maintain compatibility with other Actel ProASIC<sup>PLUS</sup> products, it is recommended that this pin not be connected to the circuitry on the board.

### GL Global Pin

Low skew input pin for clock or other global signals. This pin can be configured with an internal pull-up resistor. When it is not connected to the global network or the clock conditioning circuit, it can be configured and used as a normal I/O.

### GLMX Global Multiplexing Pin

Low skew input pin for clock or other global signals. This pin can be used in one of two special ways (refer to Actel's Using ProASIC<sup>PLUS</sup> Clock Conditioning Circuits).

When the external feedback option is selected for the PLL block, this pin is routed as the external feedback source to the clock conditioning circuit.

In applications where two different signals access the same global net at different times through the use of GLMXx and GLMXLx macros, this pin will be fixed as one of the source pins.

This pin can be configured with an internal pull-up resistor. When it is not connected to the global network or the clock conditioning circuit, it can be configured and used as any normal I/O. If not used, the GLMXx pin will be configured as an input with pull-up.

# **Dedicated Pins**

GND Ground

Common ground supply voltage.

V<sub>DD</sub> Logic Array Power Supply Pin

2.5 V supply voltage.

V<sub>DDP</sub> I/O Pad Power Supply Pin

2.5 V or 3.3 V supply voltage.

### TMS Test Mode Select

The TMS pin controls the use of boundary-scan circuitry. This pin has an internal pull-up resistor.

### TCK Test Clock

Clock input pin for boundary scan (maximum 10 MHz). Actel recommends adding a nominal 20  $k\Omega$  pull-up resistor to this pin.

### TDI Test Data In

Serial input for boundary scan. A dedicated pull-up resistor is included to pull this pin high when not being driven.

### TDO Test Data Out

Serial output for boundary scan. Actel recommends adding a nominal  $20k\Omega$  pull-up resistor to this pin.

### TRST Test Reset Input

Asynchronous, active-low input pin for resetting boundary-scan circuitry. This pin has an internal pull-up resistor. For more information, please refer to *Power-up Behavior of ProASIC*<sup>PLUS</sup> *Devices* application note.

# **Special Function Pins**

### RCK Running Clock

A free running clock is needed during programming if the programmer cannot guarantee that TCK will be uninterrupted. If not used, this pin has an internal pullup and can be left floating.

### NPECL User Negative Input

Provides high speed clock or data signals to the PLL block. If unused, leave the pin unconnected.

### PPECL User Positive Input

Provides high speed clock or data signals to the PLL block. If unused, leave the pin unconnected.

### AVDD PLL Power Supply

Analog  $V_{DD}$  should be  $V_{DD}$  (core voltage) 2.5 V (nominal) and be decoupled from GND with suitable decoupling capacitors to reduce noise. For more information, refer to Actel's Using ProASIC<sup>PLUS</sup> Clock Conditioning Circuits application note. If the clock conditioning circuitry is not used in a design, AVDD can either be left floating or tied to 2.5 V.

### AGND PLL Power Ground

The analog ground can be connected to the system ground. For more information, refer to Actel's Using ProASIC<sup>PLUS</sup> Clock Conditioning Circuits application note. If the PLLs or clock conditioning circuitry are not used in a design, AGND should be tied to GND.