Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                          |

|--------------------------------|--------------------------------------------------------------------------|

| Product Status                 | Active                                                                   |

| Number of LABs/CLBs            | -                                                                        |

| Number of Logic Elements/Cells | -                                                                        |

| Total RAM Bits                 | 73728                                                                    |

| Number of I/O                  | 100                                                                      |

| Number of Gates                | 300000                                                                   |

| Voltage - Supply               | 2.3V ~ 2.7V                                                              |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | -55°C ~ 125°C (TC)                                                       |

| Package / Case                 | 144-LBGA                                                                 |

| Supplier Device Package        | 144-FPBGA (13x13)                                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/apa300-fgg144m |

|                                |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Routing Resources**

The routing structure of ProASIC<sup>PLUS</sup> devices is designed to provide high performance through a flexible fourlevel hierarchy of routing resources: ultra-fast local resources, efficient long-line resources, high-speed, very long-line resources, and high performance global networks.

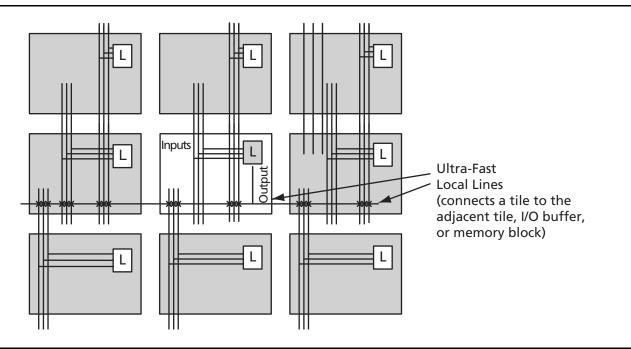

The ultra-fast local resources are dedicated lines that allow the output of each tile to connect directly to every input of the eight surrounding tiles (Figure 1-4).

The efficient long-line resources provide routing for longer distances and higher fanout connections. These resources vary in length (spanning 1, 2, or 4 tiles), run both vertically and horizontally, and cover the entire ProASIC<sup>PLUS</sup> device (Figure 1-5 on page 1-5). Each tile can drive signals onto the efficient long-line resources, which

can in turn access every input of every tile. Active buffers are inserted automatically by routing software to limit the loading effects due to distance and fanout.

The high-speed, very long-line resources, which span the entire device with minimal delay, are used to route very long or very high fanout nets. (Figure 1-6 on page 1-6).

The high-performance global networks are low-skew, high fanout nets that are accessible from external pins or from internal logic (Figure 1-7 on page 1-7). These nets are typically used to distribute clocks, resets, and other high fanout nets requiring a minimum skew. The global networks are implemented as clock trees, and signals can be introduced at any junction. These can be employed hierarchically with signals accessing every input on all tiles.

Figure 1-4 • Ultra-Fast Local Resources

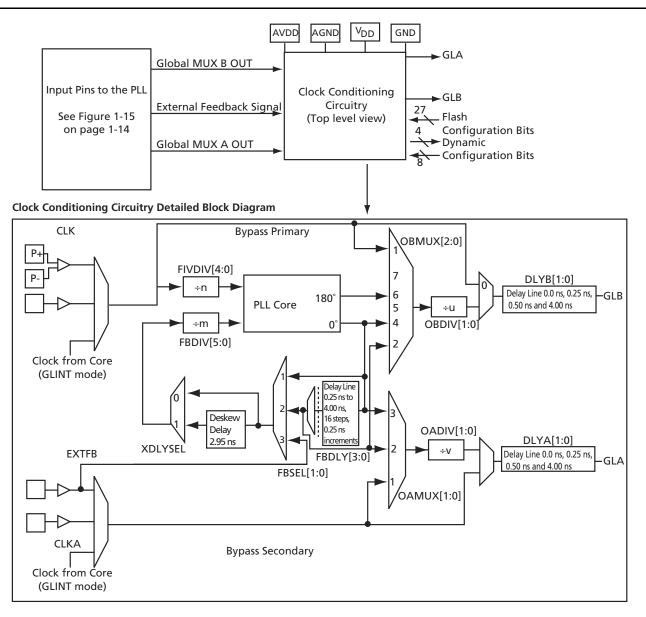

enable the user to define a wide range of frequency multipliers and divisors. The clock conditioning circuit can advance or delay the clock up to 8 ns (in increments of 0.25 ns) relative to the positive edge of the incoming reference clock. The system also allows for the selection of output frequency clock phases of 0° and 180°.

Prior to the application of signals to the rib drivers, they pass through programmable delay units, one per global network. These units permit the delaying of global signals relative to other signals to assist in the control of input set-up times. Not all possible combinations of input and output modes can be used. The degrees of freedom available in the bidirectional global pad system and in the clock conditioning circuit have been restricted. This avoids unnecessary and unwieldy design kit and software work.

### Notes:

- 1. FBDLY is a programmable delay line from 0 to 4 ns in 250 ps increments.

- 2. DLYA and DLYB are programmable delay lines, each with selectable values 0 ps, 250 ps, 500 ps, and 4 ns.

- 3. OBDIV will also divide the phase-shift since it takes place after the PLL Core.

Figure 1-14 • PLL Block – Top-Level View and Detailed PLL Block Diagram

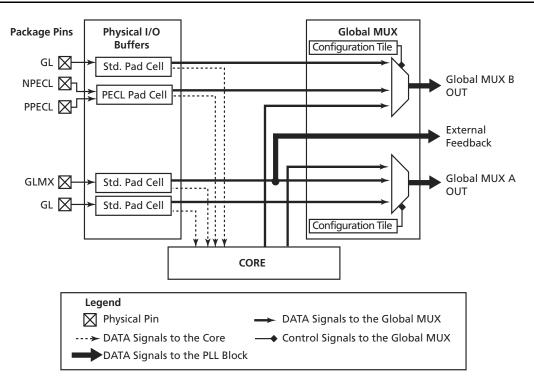

**Note:** When a signal from an I/O tile is connected to the core, it cannot be connected to the Global MUX at the same time. Figure 1-15 • Input Connectors to ProASIC<sup>PLUS</sup> Clock Conditioning Circuitry

## Table 1-7 • Clock-Conditioning Circuitry MUX Settings

| MUX     | Datapath                                           | Comments                             |

|---------|----------------------------------------------------|--------------------------------------|

| FBSEL   |                                                    |                                      |

| 1       | Internal Feedback                                  |                                      |

| 2       | Internal Feedback and Advance Clock Using FBDLY    | -0.25 to -4 ns in 0.25 ns increments |

| 3       | External Feedback (EXTFB)                          |                                      |

| XDLYSEL |                                                    |                                      |

| 0       | Feedback Unchanged                                 |                                      |

| 1       | Deskew feedback by advancing clock by system delay | Fixed delay of -2.95 ns              |

| OBMUX   | GLB                                                |                                      |

| 0       | Primary bypass, no divider                         |                                      |

| 1       | Primary bypass, use divider                        |                                      |

| 2       | Delay Clock Using FBDLY                            | +0.25 to +4 ns in 0.25 ns increments |

| 4       | Phase Shift Clock by 0°                            |                                      |

| 5       | Reserved                                           |                                      |

| 6       | Phase Shift Clock by +180°                         |                                      |

| 7       | Reserved                                           |                                      |

| OAMUX   | GLA                                                |                                      |

| 0       | Secondary bypass, no divider                       |                                      |

| 1       | Secondary bypass, use divider                      |                                      |

| 2       | Delay Clock Using FBDLY                            | +0.25 to +4 ns in 0.25 ns increments |

| 3       | Phase Shift Clock by 0°                            |                                      |

# Logic Tile Timing Characteristics

Timing characteristics for ProASIC<sup>PLUS</sup> devices fall into three categories: family dependent, device dependent, and design dependent. The input and output buffer characteristics are common to all ProASIC<sup>PLUS</sup> family members. Internal routing delays are device dependent. Design dependency means that actual delays are not determined until after placement and routing of the user's design are complete. Delay values may then be determined by using the Timer utility or by performing simulation with post-layout delays.

# **Critical Nets and Typical Nets**

Propagation delays are expressed only for typical nets, which are used for initial design performance evaluation. Critical net delays can then be applied to the most timing-critical paths. Critical nets are determined by net property assignment prior to place-and-route. Refer to the Actel *Designer User's Guide* or online help for details on using constraints.

# **Timing Derating**

Since ProASIC<sup>PLUS</sup> devices are manufactured with a CMOS process, device performance will vary with temperature, voltage, and process. Minimum timing parameters reflect maximum operating voltage, minimum operating temperature, and optimal process variations. Maximum timing parameters reflect minimum operating voltage, maximum operating temperature, and worst-case process variations (within process specifications). The derating factors shown in Table 1-9 should be applied to all timing data contained within this datasheet.

All timing numbers listed in this datasheet represent sample timing characteristics of ProASIC<sup>PLUS</sup> devices. Actual timing delay values are design-specific and can be derived from the Timer tool in Actel's Designer software after place-and-route.

| Table 1-9 • | Temperature and Voltage Derating Factors                                       |

|-------------|--------------------------------------------------------------------------------|

|             | (Normalized to Worst-Case Commercial, $T_J = 70^{\circ}C$ , $V_{DD} = 2.3 V$ ) |

|       | –55°C | –40°C | 0°C  | 25°C | 70°C | 85°C | 110°C | 125°C | 135°C | 150°C |

|-------|-------|-------|------|------|------|------|-------|-------|-------|-------|

| 2.3 V | 0.84  | 0.86  | 0.91 | 0.94 | 1.00 | 1.02 | 1.05  | 1.13  | 1.18  | 1.27  |

| 2.5 V | 0.81  | 0.82  | 0.87 | 0.90 | 0.95 | 0.98 | 1.01  | 1.09  | 1.13  | 1.21  |

| 2.7 V | 0.77  | 0.79  | 0.83 | 0.86 | 0.91 | 0.93 | 0.96  | 1.04  | 1.08  | 1.16  |

### Notes:

1. The user can set the junction temperature in Designer software to be any integer value in the range of -55°C to 175°C.

2. The user can set the core voltage in Designer software to be any value between 1.4 V and 1.6 V.

# **B** <sup>®</sup>User Security

ProASICPLUS devices have FlashLock protection bits that, FlashLockonce programmed, block the entire programmed contents from being read externally. Please refer to Table 1-11 for details on the number of bits in the key for each device. If locked, the user can only reprogram the device employing the user-defined security key. This protects the device from being read back and duplicated. Since programmed data is stored in nonvolatile memory cells (actually very small capacitors) rather than in the wiring, physical deconstruction cannot be used to compromise data. This type of security breach is further discouraged by the placement of the memory cells beneath the four metal layers (whose removal cannot be accomplished without disturbing the charge in the capacitor). This is the highest security provided in the industry. For more information, refer to Actel's Design Security in Nonvolatile Flash and Antifuse FPGAs white paper.

| Device  | Key Size |

|---------|----------|

| APA075  | 79 bits  |

| APA150  | 79 bits  |

| APA300  | 79 bits  |

| APA450  | 119 bits |

| APA600  | 167 bits |

| APA750  | 191 bits |

| APA1000 | 263 bits |

Table 1-11 • Flashlock Key Size by Device

# **Embedded Memory Floorplan**

The embedded memory is located across the top and bottom of the device in 256x9 blocks (Figure 1-1 on page 1-2). Depending on the device, up to 88 blocks are available to support a variety of memory configurations. Each block can be programmed as an independent memory array or combined (using dedicated memory routing resources) to form larger, more complex memory configurations. A single memory configuration could include blocks from both the top and bottom memory locations.

Table 1-12 • ProASIC<sup>PLUS</sup> Memory Configurations by Device

# **Embedded Memory Configurations**

The embedded memory in the ProASIC<sup>PLUS</sup> family provides great configuration flexibility (Table 1-12). Each ProASIC<sup>PLUS</sup> block is designed and optimized as a two-port memory (one read, one write). This provides 198 kbits of two-port and/or single port memory in the APA1000 device.

Each memory block can be configured as FIFO or SRAM, with independent selection of synchronous or asynchronous read and write ports (Table 1-13). Additional characteristics include programmable flags as well as parity checking and generation. Figure 1-21 on page 1-25 and Figure 1-22 on page 1-26 show the block diagrams of the basic SRAM and FIFO blocks. Table 1-14 on page 1-25 and Table 1-15 on page 1-26 describe memory block SRAM and FIFO interface signals, respectively. A single memory block is designed to operate at up to 150 MHz (standard speed grade typical conditions). Each block is comprised of 256 9-bit words (one read port, one write port). The memory blocks may be cascaded in width and/or depth to create the desired memory organization. (Figure 1-23 on page 1-27). This provides optimal bit widths of 9 (one block), 18, 36, and 72, and optimal depths of 256, 512, 768, and 1,024. Refer to Actel's SmartGen User's Guide for more information.

Figure 1-24 on page 1-27 gives an example of optimal memory usage. Ten blocks with 23,040 bits have been used to generate three arrays of various widths and depths. Figure 1-25 on page 1-27 shows how RAM blocks can be used in parallel to create extra read ports. In this example, using only 10 of the 88 available blocks of the APA1000 yields an effective 6,912 bits of multiple port RAM. The Actel SmartGen software facilitates building wider and deeper memory configurations for optimal memory usage.

|        |        |     | Maximum Width |     | Maximum Depth |   |  |

|--------|--------|-----|---------------|-----|---------------|---|--|

| Device | Bottom | Тор | D             | w   | D             | w |  |

| APA075 | 0      | 12  | 256           | 108 | 1,536         | 9 |  |

| APA150 | 0      | 16  | 256           | 144 | 2,048         | 9 |  |

| APA300 | 16     | 16  | 256           | 144 | 2,048         | 9 |  |

| APA450 | 24     | 24  | 256           | 216 | 3,072         | 9 |  |

| APA600 | 28     | 28  | 256           | 252 | 3,584         | 9 |  |

| Minimum Time at T」<br>110°C or below | Minimum Time at T <sub>J</sub><br>125°C or below | Minimum Time at T <sub>J</sub><br>135°C or below | Minimum Time at T」<br>150°C or below | Minimum<br>Performance<br>Retention (Years) |

|--------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------|---------------------------------------------|

| 100%                                 |                                                  |                                                  |                                      | 20.0                                        |

| 90%                                  | 10%                                              |                                                  |                                      | 18.2                                        |

| 75%                                  | 25%                                              |                                                  |                                      | 16                                          |

| 90%                                  |                                                  | 10%                                              |                                      | 15.4                                        |

| 50%                                  | 50%                                              |                                                  |                                      | 13.3                                        |

| 90%                                  |                                                  |                                                  | 10%                                  | 11.8                                        |

| 75%                                  |                                                  | 25%                                              |                                      | 11.4                                        |

|                                      | 100%                                             |                                                  |                                      | 10                                          |

|                                      | 90%                                              | 10%                                              |                                      | 9.1                                         |

| 50%                                  |                                                  | 50%                                              |                                      | 8                                           |

|                                      | 75%                                              | 25%                                              |                                      | 8                                           |

|                                      | 90%                                              |                                                  | 10%                                  | 7.7                                         |

| 75%                                  |                                                  |                                                  | 25%                                  | 7.3                                         |

|                                      | 50%                                              | 50%                                              |                                      | 6.7                                         |

|                                      | 75%                                              |                                                  | 25%                                  | 5.7                                         |

|                                      |                                                  | 100%                                             |                                      | 5                                           |

|                                      |                                                  | 90%                                              | 10%                                  | 4.5                                         |

| 50%                                  |                                                  |                                                  | 50%                                  | 4.4                                         |

|                                      | 50%                                              |                                                  | 50%                                  | 4                                           |

|                                      |                                                  | 75%                                              | 25%                                  | 4                                           |

|                                      |                                                  | 50%                                              | 50%                                  | 3.3                                         |

|                                      |                                                  |                                                  | 100%                                 | 2.5                                         |

Table 1-19 • Military Temperature Grade Product Performance Retention

|                              |                                                                                                             |                                                                                                                                                                     |                 | Comme                       |      |                                                                            |    |

|------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------|------|----------------------------------------------------------------------------|----|

| Symbol                       | Parameter                                                                                                   | Conditions                                                                                                                                                          | Min.            | Тур.                        | Max. | Units                                                                      |    |

| V <sub>OH</sub>              | Output High Voltage<br>3.3 V I/O, High Drive (OB33P) $I_{OH} = -14 \text{ mA}$<br>$I_{OH} = -24 \text{ mA}$ |                                                                                                                                                                     |                 | 0.9*V <sub>DDP</sub><br>2.4 |      |                                                                            | v  |

|                              | 3.3 V I/O, Low Drive (OB33L)                                                                                | I <sub>OH</sub> = –6 mA<br>I <sub>OH</sub> = –12 mA                                                                                                                 |                 | 0.9*V <sub>DDP</sub><br>2.4 |      |                                                                            |    |

| V <sub>OL</sub>              | Output Low Voltage<br>3.3 V I/O, High Drive (OB33P)<br>3.3 V I/O, Low Drive (OB33L)                         | $I_{OL} = 15 \text{ mA}$<br>$I_{OL} = 20 \text{ mA}$<br>$I_{OL} = 28 \text{ mA}$<br>$I_{OL} = 7 \text{ mA}$<br>$I_{OL} = 10 \text{ mA}$<br>$I_{OL} = 15 \text{ mA}$ |                 |                             |      | 0.1V <sub>DDP</sub><br>0.4<br>0.7<br>0.1V <sub>DDP</sub><br>0.4<br>0.7     | V  |

| V <sub>IH</sub> <sup>5</sup> | Input High Voltage<br>3.3 V Schmitt Trigger Inputs<br>3.3 V LVTTL/LVCMOS<br>2.5 V Mode                      |                                                                                                                                                                     |                 | 1.6<br>2<br>1.7             |      | V <sub>DDP</sub> + 0.3<br>V <sub>DDP</sub> + 0.3<br>V <sub>DDP</sub> + 0.3 | V  |

| V <sub>IL</sub> <sup>6</sup> | Input Low Voltage<br>3.3 V Schmitt Trigger Inputs<br>3.3 V LVTTL/LVCMOS<br>2.5 V Mode                       |                                                                                                                                                                     |                 | -0.3<br>-0.3<br>-0.3        |      | 0.8<br>0.8<br>0.7                                                          | V  |

| R <sub>WEAKPULLUP</sub>      | Weak Pull-up Resistance<br>(IOB33U)                                                                         | $V_{IN} \ge 1.5 V$                                                                                                                                                  |                 | 7                           |      | 43                                                                         | kΩ |

| R <sub>WEAKPULLUP</sub>      | Weak Pull-up Resistance<br>(IOB25U)                                                                         | $V_{IN} \ge 1.5 V$                                                                                                                                                  |                 | 7                           |      | 43                                                                         | kΩ |

| I <sub>IN</sub>              | Input Current                                                                                               | with pull up (V <sub>IN</sub> = GND)                                                                                                                                |                 | -300                        |      | -40                                                                        | μA |

|                              |                                                                                                             | without pull up ( $V_{IN} = GND \text{ or } V_{DD}$ )                                                                                                               |                 | -10                         |      | 10                                                                         | μA |

| I <sub>DDQ</sub>             | Quiescent Supply Current                                                                                    | $V_{IN} = GND^3 \text{ or } V_{DD}$                                                                                                                                 | Std.            |                             | 5.0  | 15                                                                         | mA |

|                              | (standby)<br>Commercial                                                                                     |                                                                                                                                                                     | -F <sup>2</sup> |                             | 5.0  | 25                                                                         | mA |

| I <sub>DDQ</sub>             | Quiescent Supply Current<br>(standby)<br>Industrial                                                         | $V_{IN} = GND^3 \text{ or } V_{DD}$                                                                                                                                 | Std.            |                             | 5.0  | 20                                                                         | mA |

| I <sub>DDQ</sub>             | Quiescent Supply Current<br>(standby)<br>Military                                                           | $V_{IN} = GND^3 \text{ or } V_{DD}$                                                                                                                                 | Std.            |                             | 5.0  | 25                                                                         | mA |

# Table 1-23DC Electrical Specifications (VVDP3.3 VV0.3 Vand VVDP2.5 V10.2 VVApplies to Commercial and Industrial Temperature Only

Notes:

1. All process conditions. Commercial/Industrial: Junction Temperature: -40 to +110°C.

2. All –F parts are only available as commercial.

3. No pull-up resistor required.

4. This will not exceed 2 mA total per device.

5. During transitions, the input signal may overshoot to  $V_{DDP}$  +1.0 V for a limited time of no larger than 10% of the duty cycle.

# Table 1-23DC Electrical Specifications (VVDE3.3 V $\pm$ 0.3 Vand VVDE0.2 V(Continued)Applies to Commercial and Industrial Temperature Only

|                  |                                                                                             |                                        |                    | Comme        | rcial/In | dustrial <sup>1</sup> |       |  |

|------------------|---------------------------------------------------------------------------------------------|----------------------------------------|--------------------|--------------|----------|-----------------------|-------|--|

| Symbol           | Parameter                                                                                   | Conditions                             |                    | Min.         | Тур.     | Max.                  | Units |  |

| I <sub>OZ</sub>  |                                                                                             | $V_{OH} = GND \text{ or } V_{DD}$      | Std.               | -10          |          | 10                    | μA    |  |

|                  | Current                                                                                     |                                        | -F <sup>2, 4</sup> | -10          |          | 100                   | μA    |  |

| I <sub>OSH</sub> | Output Short Circuit Current<br>High<br>3.3 V High Drive (OB33P)<br>3.3 V Low Drive (OB33L) | $V_{IN} = GND$<br>$V_{IN} = GND$       |                    | -200<br>-100 |          |                       |       |  |

| I <sub>OSL</sub> | Output Short Circuit Current<br>Low<br>3.3 V High Drive<br>3.3 V Low Drive                  | $V_{IN} = V_{DD}$<br>$V_{IN} = V_{DD}$ |                    |              |          | 200<br>100            |       |  |

| CI/O             | I/O Pad Capacitance                                                                         |                                        |                    |              |          | 10                    | pF    |  |

| C <sub>CLK</sub> | Clock Input Pad Capacitance                                                                 |                                        |                    |              |          | 10                    | pF    |  |

Notes:

1. All process conditions. Commercial/Industrial: Junction Temperature: -40 to +110°C.

2. All –F parts are only available as commercial.

3. No pull-up resistor required.

4. This will not exceed 2 mA total per device.

5. During transitions, the input signal may overshoot to  $V_{DDP}$ +1.0 V for a limited time of no larger than 10% of the duty cycle.

|                              |                                                                                        |                                                                               | Military |                             |      |                                                       |       |

|------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------|-----------------------------|------|-------------------------------------------------------|-------|

| Symbol                       | Parameter                                                                              | Conditions                                                                    |          | Min.                        | Тур. | Max.                                                  | Units |

| V <sub>OH</sub>              | Output High Voltage<br>3.3 V I/O, High Drive, High Slew<br>(OB33PH)                    | I <sub>OH</sub> = –8 mA<br>I <sub>OH</sub> = –16 mA                           |          | 0.9*V <sub>DDP</sub><br>2.4 |      |                                                       |       |

|                              | 3.3V I/O, High Drive, Normal/<br>Low Slew (OB33PN/OB33PL)                              | I <sub>OH</sub> = -3mA<br>I <sub>OH</sub> = -8mA                              |          | 0.9*V <sub>DDP</sub><br>2.4 |      |                                                       | V     |

|                              | 3.3 V I/O, Low Drive , High/<br>Normal/Low Slew (OB33LH/<br>OB33LN/OB33LL)             |                                                                               |          | 0.9*V <sub>DDP</sub><br>2.4 |      |                                                       |       |

| V <sub>OL</sub>              | Output Low Voltage<br>3.3 V I/O, High Drive, High Slew<br>(OB33PH)                     | I <sub>OL</sub> = 12 mA<br>I <sub>OL</sub> = 17 mA<br>I <sub>OL</sub> = 28 mA |          |                             |      | 0.1V <sub>DDP</sub><br>0.4<br>0.7                     |       |

|                              | 3.3V I/O, High Drive, Normal/<br>Low Slew (OB33PN/OB33PL))                             | I <sub>OL</sub> = 4 mA<br>I <sub>OL</sub> = 6 mA<br>I <sub>OL</sub> = 13 mA   |          |                             |      | 0.1V <sub>DDP</sub><br>0.4<br>0.7                     | V     |

|                              | 3.3 V I/O, Low Drive, High/<br>Normal/Low Slew (OB33LH/<br>OB33LN/OB33LL)              |                                                                               |          |                             |      | 0.1V <sub>DDP</sub><br>0.4<br>0.7                     |       |

| V <sub>IH</sub> <sup>4</sup> | Input High Voltage<br>3.3 V Schmitt Trigger Inputs<br>3.3 V LVTTL/LVCMOS<br>2.5 V Mode |                                                                               |          | 1.6<br>2<br>1.7             |      | $V_{DDP} + 0.3$<br>$V_{DDP} + 0.3$<br>$V_{DDP} + 0.3$ | V     |

| V <sub>IL</sub> <sup>5</sup> | Input Low Voltage<br>3.3 V Schmitt Trigger Inputs<br>3.3 V LVTTL/LVCMOS<br>2.5 V Mode  |                                                                               |          | -0.3<br>-0.3<br>-0.3        |      | 0.7<br>0.8<br>0.7                                     | V     |

| R <sub>WEAKPULLUP</sub>      | Weak Pull-up Resistance<br>(IOB33U)                                                    | $V_{IN} \ge 1.5 V$                                                            |          | 7                           |      | 43                                                    | kΩ    |

| R <sub>WEAKPULLUP</sub>      | Weak Pull-up Resistance<br>(IOB25U)                                                    | $V_{\rm IN} \ge 1.5 V$                                                        |          | 7                           |      | 43                                                    | kΩ    |

| I <sub>IN</sub>              | Input Current                                                                          | with pull up ( $V_{IN} = GND$ )                                               |          | -300                        |      | -40                                                   | μA    |

|                              |                                                                                        | without pull up ( $V_{IN} = GND \text{ or } V_{DD}$ )                         |          | -10                         |      | 10                                                    | μΑ    |

| I <sub>DDQ</sub>             | Quiescent Supply Current                                                               | $V_{IN} = GND^2 \text{ or } V_{DD}$                                           | Std.     |                             | 5.0  | 15                                                    | mA    |

|                              | (standby)<br>Commercial                                                                |                                                                               | –F       |                             | 5.0  | 25                                                    | mA    |

# Table 1-24DC Electrical Specifications (VVToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToToTo

## Notes:

1. All process conditions. Military Temperature / MIL-STD-883 Class B: Junction Temperature: –55 to +125°C.

2. No pull-up resistor required.

3. This will not exceed 2 mA total per device.

4. During transitions, the input signal may overshoot to V<sub>DDP</sub>+1.0 V for a limited time of no larger than 10% of the duty cycle.

# Table 1-24DC Electrical Specifications (VVDE3.3 V $\pm$ 0.3 Vand VVDE2.5 V $\pm$ 0.2 V) (Continued)Applies to Military Temperature and MIL-STD-883B Temperature Only

|                  |                                                                                             |                                                |                 | Militar      | /MIL-S1 | D-883B <sup>1</sup> | Τ     |

|------------------|---------------------------------------------------------------------------------------------|------------------------------------------------|-----------------|--------------|---------|---------------------|-------|

| Symbol           | Parameter                                                                                   | Conditions                                     |                 | Min. Typ.    |         | Max.                | Units |

| I <sub>DDQ</sub> | Quiescent Supply Current<br>(standby)<br>Industrial                                         | $V_{IN} = GND^2 \text{ or } V_{DD}$            | Std.            |              | 5.0     | 20                  | mA    |

| I <sub>DDQ</sub> | Quiescent Supply Current<br>(standby)<br>Military                                           | $V_{IN} = GND^2 \text{ or } V_{DD}$            | Std.            |              | 5.0     | 25                  | mA    |

| I <sub>OZ</sub>  |                                                                                             | $V_{OH} = GND \text{ or } V_{DD}$              | Std.            | -10          |         | 10                  | μΑ    |

|                  | Current                                                                                     |                                                | -F <sup>3</sup> | -10          |         | 100                 | μA    |

| I <sub>OSH</sub> | Output Short Circuit Current<br>High<br>3.3 V High Drive (OB33P)<br>3.3 V Low Drive (OB33L) | V <sub>IN</sub> = GND<br>V <sub>IN</sub> = GND |                 | -200<br>-100 |         |                     |       |

| I <sub>OSL</sub> | Output Short Circuit Current<br>Low<br>3.3 V High Drive<br>3.3 V Low Drive                  | $V_{IN} = V_{DD}$<br>$V_{IN} = V_{DD}$         |                 |              |         | 200<br>100          |       |

| CI/O             | I/O Pad Capacitance                                                                         |                                                |                 |              |         | 10                  | pF    |

| C <sub>CLK</sub> | Clock Input Pad Capacitance                                                                 |                                                |                 |              |         | 10                  | pF    |

Notes:

1. All process conditions. Military Temperature / MIL-STD-883 Class B: Junction Temperature: -55 to +125°C.

2. No pull-up resistor required.

3. This will not exceed 2 mA total per device.

4. During transitions, the input signal may overshoot to V<sub>DDP</sub>+1.0 V for a limited time of no larger than 10% of the duty cycle.

# **Input Buffer Delays**

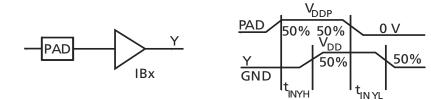

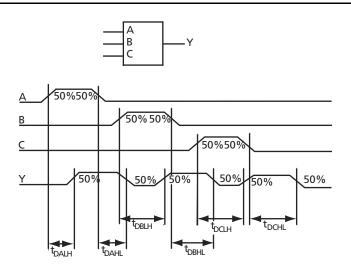

### Figure 1-28 • Input Buffer Delays

# Table 1-35 Worst-Case Commercial Conditions

V<sub>DDP</sub> = 3.0 V, V<sub>DD</sub> = 2.3 V, T<sub>J</sub> = 70°C

|            |                                                                              | Max. t <sub>INYH</sub> 1 |     | Max. |     |       |

|------------|------------------------------------------------------------------------------|--------------------------|-----|------|-----|-------|

| Macro Type | Description                                                                  | Std.                     | -F  | Std. | -F  | Units |

| IB33       | 3.3 V, CMOS Input Levels <sup>3</sup> , No Pull-up Resistor                  | 0.4                      | 0.5 | 0.6  | 0.7 | ns    |

| IB33S      | 3.3 V, CMOS Input Levels <sup>3</sup> , No Pull-up Resistor, Schmitt Trigger | 0.6                      | 0.7 | 0.8  | 0.9 | ns    |

### Notes:

- 1.  $t_{INYH} = Input Pad-to-Y High$

- 2.  $t_{INYL} = Input Pad-to-Y Low$

- 3. LVTTL delays are the same as CMOS delays.

- 4. For LP Macros, V<sub>DDP</sub>=2.3 V for delays.

- 5. All –F parts are only available as commercial.

# Table 1-36 • Worst-Case Commercial Conditions

## $V_{DDP} = 2.3 V, V_{DD} = 2.3 V, T_{J} = 70^{\circ}C$

|            |                                                                    | Max. | t <sub>INYH</sub> 1 | Max. |     |       |

|------------|--------------------------------------------------------------------|------|---------------------|------|-----|-------|

| Macro Type | Description                                                        | Std. | -F                  | Std. | -F  | Units |

| IB25LP     | 2.5 V, CMOS Input Levels <sup>3</sup> , Low Power                  |      | 1.1                 | 0.6  | 0.8 | ns    |

| IB25LPS    | 2.5 V, CMOS Input Levels <sup>3</sup> , Low Power, Schmitt Trigger |      | 0.9                 | 0.9  | 1.1 | ns    |

### Notes:

- 1.  $t_{INYH} = Input Pad-to-Y High$

- 2.  $t_{INYL} = Input Pad-to-Y Low$

- 3. LVTTL delays are the same as CMOS delays.

- 4. For LP Macros, V<sub>DDP</sub>=2.3 V for delays.

- 5. All –F parts are only available as commercial.

## Table 1-37 • Worst-Case Military Conditions

$V_{DDP}$  = 3.0V,  $V_{DD}$  = 2.3V,  $T_{J}$  = 125°C for Military/MIL-STD-883

|            |                                                                             |      | Max. t <sub>INYL</sub> <sup>2</sup> |       |

|------------|-----------------------------------------------------------------------------|------|-------------------------------------|-------|

| Macro Type | Description                                                                 | Std. | Std.                                | Units |

| IB33       | 3.3V, CMOS Input Levels <sup>3</sup> , No Pull-up Resistor                  | 0.5  | 0.6                                 | ns    |

| IB33S      | 3.3V, CMOS Input Levels <sup>3</sup> , No Pull-up Resistor, Schmitt Trigger | 0.6  | 0.8                                 | ns    |

## Notes:

- 1.  $t_{INYH} = Input Pad-to-Y High$

- 2.  $t_{INYL} = Input Pad-to-Y Low$

- 3. LVTTL delays are the same as CMOS delays.

- 4. For LP Macros, V<sub>DDP</sub>=2.3V for delays.

# Table 1-38 • Worst-Case Military Conditions

# $V_{DDP}$ = 2.3V, $V_{DD}$ = 2.3V, $T_J$ = 125°C for Military/MIL-STD-883

|            |                                                                   | Max. t <sub>INYH</sub> 1 | Max. t <sub>INYL</sub> 2 |       |

|------------|-------------------------------------------------------------------|--------------------------|--------------------------|-------|

| Macro Type | Description                                                       | Std.                     | Std.                     | Units |

| IB25LP     | 2.5V, CMOS Input Levels <sup>3</sup> , Low Power                  | 0.9                      | 0.7                      | ns    |

| IB25LPS    | 2.5V, CMOS Input Levels <sup>3</sup> , Low Power, Schmitt Trigger | 0.8                      | 1.0                      | ns    |

### Notes:

- 1.  $t_{INYH} = Input Pad-to-Y High$

- 2.  $t_{INYL} = Input Pad-to-Y Low$

- 3. LVTTL delays are the same as CMOS delays.

- 4. For LP Macros,  $V_{DDP}$ =2.3V for delays.

## Table 1-41 • Worst-Case Military Conditions

$V_{DDP} = 3.0V, V_{DD} = 2.3V, T_J = 125^{\circ}C$  for Military/MIL-STD-883

|            |                                                                             | Max. t <sub>INYH</sub> <sup>1</sup> M |      |

|------------|-----------------------------------------------------------------------------|---------------------------------------|------|

| Macro Type | Description                                                                 | Std.                                  | Std. |

| GL33       | 3.3V, CMOS Input Levels <sup>3</sup> , No Pull-up Resistor                  | 1.1                                   | 1.1  |

| GL33S      | 3.3V, CMOS Input Levels <sup>3</sup> , No Pull-up Resistor, Schmitt Trigger | 1.1                                   | 1.1  |

| PECL       | PPECL Input Levels                                                          | 1.1                                   | 1.1  |

## Notes:

- 1.  $t_{INYH} = Input Pad-to-Y High$

- 2.  $t_{INYL} = Input Pad-to-Y Low$

- 3. LVTTL delays are the same as CMOS delays.

4. For LP Macros, V<sub>DDP</sub>=2.3V for delays.

## Table 1-42 • Worst-Case Military Conditions

# $V_{DDP} = 2.3V$ , $V_{DD} = 2.3V$ , $T_J = 125^{\circ}C$ for Military/MIL-STD-883

|            |                                                                   | Max. t <sub>INYH</sub> 1 | Max. t <sub>INYL</sub> <sup>2</sup> |

|------------|-------------------------------------------------------------------|--------------------------|-------------------------------------|

| Macro Type | Description                                                       | Std.                     | Std.                                |

| GL25LP     | 2.5V, CMOS Input Levels <sup>3</sup> , Low Power                  | 1.0                      | 1.1                                 |

| GL25LPS    | 2.5V, CMOS Input Levels <sup>3</sup> , Low Power, Schmitt Trigger | 1.4                      | 1.0                                 |

Notes:

- 1.  $t_{INYH} = Input Pad-to-Y High$

- 2.  $t_{INYL} = Input Pad-to-Y Low$

3. LVTTL delays are the same as CMOS delays.

4. For LP Macros, V<sub>DDP</sub>=2.3V for delays.

# **Module Delays**

Figure 1-29 • Module Delays

# Sample Macrocell Library Listing

Table 1-47 • Worst-Case Military Conditions<sup>1</sup>

$V_{DD} = 2.3 V$ ,  $T_{J} = 70^{\circ} C$ ,  $T_{J} = 70^{\circ} C$ ,  $T_{J} = 125^{\circ} C$  for Military/MIL-STD-883

|           |                                                  |                 | S   | td. | -   | F <sup>2</sup> |       |

|-----------|--------------------------------------------------|-----------------|-----|-----|-----|----------------|-------|

| Cell Name | Description                                      |                 |     | Min | Max | Min            | Units |

| NAND2     | 2-Input NAND                                     |                 | 0.5 |     | 0.6 |                | ns    |

| AND2      | 2-Input AND                                      |                 | 0.7 |     | 0.8 |                | ns    |

| NOR3      | 3-Input NOR                                      |                 | 0.8 |     | 1.0 |                | ns    |

| MUX2L     | 2-1 MUX with Active Low Select                   |                 | 0.5 |     | 0.6 |                | ns    |

| OA21      | 2-Input OR into a 2-Input AND                    |                 | 0.8 |     | 1.0 |                | ns    |

| XOR2      | 2-Input Exclusive OR                             |                 | 0.6 |     | 0.8 |                | ns    |

| LDL       | Active Low Latch (LH/HL)                         | LH <sup>3</sup> | 0.9 |     | 1.1 |                | ns    |

|           | CLK-Q                                            | HL <sup>3</sup> | 0.8 |     | 0.9 |                | ns    |

|           | t <sub>setup</sub>                               | •               |     | 0.7 |     | 0.8            | ns    |

|           | t <sub>hold</sub>                                |                 |     | 0.1 |     | 0.2            | ns    |

| DFFL      | Negative Edge-Triggered D-type Flip-Flop (LH/HL) | LH <sup>3</sup> | 0.9 |     | 1.1 |                | ns    |

|           | CLK-Q                                            | HL <sup>3</sup> | 0.8 |     | 1.0 |                | ns    |

|           | t <sub>setup</sub>                               | •               |     | 0.6 |     | 0.7            | ns    |

|           | t <sub>hold</sub>                                |                 |     | 0.0 |     | 0.0            | ns    |

Notes:

1. Intrinsic delays have a variable component, coupled to the input slope of the signal. These numbers assume an input slope typical of local interconnect.

- 2. All –F parts are only available as commercial.

- 3. LH and HL refer to the Q transitions from Low to High and High to Low, respectively.

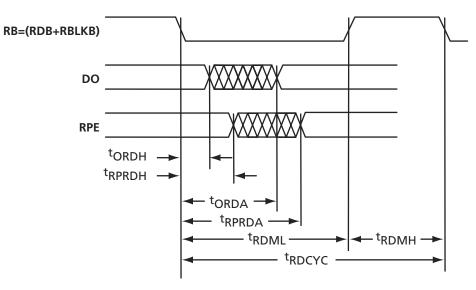

# Asynchronous SRAM Read, RDB Controlled

# **Note:** The plot shows the normal operation status.

# Figure 1-35 • Asynchronous SRAM Read, RDB Controlled

# Table 1-56T\_J = 0°C to 110°C; V\_DD = 2.3 V to 2.7 V for Commercial/industrial $T_J = -55°C$ to 150°C, $V_{DD} = 2.3$ V to 2.7 V for Military/MIL-STD-883

|                         |                                     | •    |      |       |                             |

|-------------------------|-------------------------------------|------|------|-------|-----------------------------|

| Symbol t <sub>xxx</sub> | Description                         | Min. | Max. | Units | Notes                       |

| ORDA                    | New DO access from RB $\downarrow$  | 7.5  |      | ns    |                             |

| ORDH                    | Old DO valid from RB $\downarrow$   |      | 3.0  | ns    |                             |

| RDCYC                   | Read cycle time                     | 7.5  |      | ns    |                             |

| RDMH                    | RB high phase                       | 3.0  |      | ns    | Inactive setup to new cycle |

| RDML                    | RB low phase                        | 3.0  |      | ns    | Active                      |

| RPRDA                   | New RPE access from RB $\downarrow$ | 9.5  |      | ns    |                             |

| RPRDH                   | Old RPE valid from RB $\downarrow$  |      | 3.0  | ns    |                             |

Note: All –F speed grade devices are 20% slower than the standard numbers.

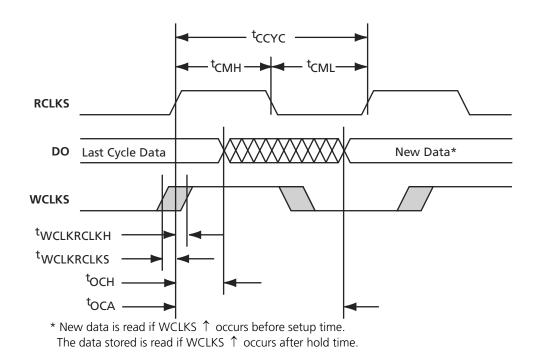

# Synchronous Write and Read to the Same Location

**Note:** The plot shows the normal operation status.

### *Figure 1-37* • Synchronous Write and Read to the Same Location

#### Table 1-58 • $T_J = 0^{\circ}C$ to 110°C; $V_{DD} = 2.3$ V to 2.7 V for Commercial/industrial $T_J = -55^{\circ}C$ to 150°C, $V_{DD} = 2.3$ V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                                     | Min.  | Max. | Units | Notes                 |

|-------------------------|-------------------------------------------------|-------|------|-------|-----------------------|

| CCYC                    | Cycle time                                      | 7.5   |      | ns    |                       |

| СМН                     | Clock high phase                                | 3.0   |      | ns    |                       |

| CML                     | Clock low phase                                 | 3.0   |      | ns    |                       |

| WCLKRCLKS               | WCLKS $\uparrow$ to RCLKS $\uparrow$ setup time | - 0.1 |      | ns    |                       |

| WCLKRCLKH               | WCLKS $\uparrow$ to RCLKS $\uparrow$ hold time  |       | 7.0  | ns    |                       |

| ОСН                     | Old DO valid from RCLKS ↑                       |       | 3.0  | ns    | OCA/OCH displayed for |

| OCA                     | New DO valid from RCLKS ↑                       | 7.5   |      | ns    | Access Timed Output   |

## Notes:

1. This behavior is valid for Access Timed Output and Pipelined Mode Output. The table shows the timings of an Access Timed Output.

2. During synchronous write and synchronous read access to the same location, the new write data will be read out if the active write clock edge occurs before or at the same time as the active read clock edge. The negative setup time insures this behavior for WCLKS and RCLKS driven by the same design signal.

- 3. If WCLKS changes after the hold time, the data will be read.

- 4. A setup or hold time violation will result in unknown output data.

- 5. All –F speed grade devices are 20% slower than the standard numbers.

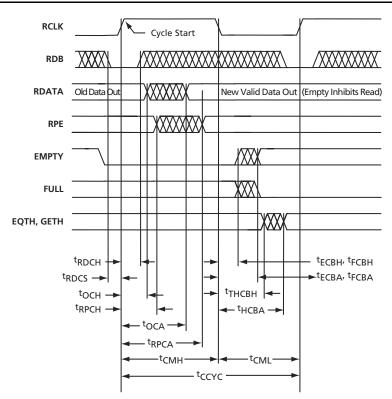

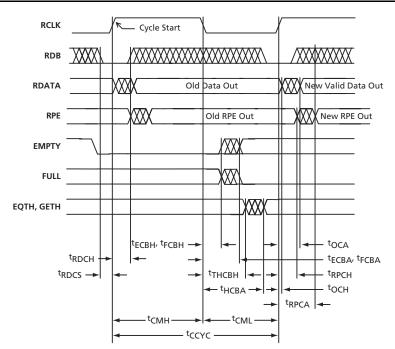

# Synchronous FIFO Read, Access Timed Output Strobe (Synchronous Transparent)

### Note: The plot shows the normal operation status.

### *Figure 1-45* • Synchronous FIFO Read, Access Timed Output Strobe (Synchronous Transparent)

# Table 1-65T<sub>J</sub> = 0°C to 110°C; V<sub>DD</sub> = 2.3 V to 2.7 V for Commercial/industrialT<sub>J</sub> = -55°C to 150°C, V<sub>DD</sub> = 2.3 V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                                                           | Min.             | Max. | Units | Notes                                                                               |

|-------------------------|-----------------------------------------------------------------------|------------------|------|-------|-------------------------------------------------------------------------------------|

| CCYC                    | Cycle time                                                            | 7.5              |      | ns    |                                                                                     |

| CMH                     | Clock high phase                                                      | 3.0              |      | ns    |                                                                                     |

| CML                     | Clock low phase                                                       | 3.0              |      | ns    |                                                                                     |

| ECBA                    | New EMPTY access from RCLKS $\downarrow$                              | 3.0 <sup>1</sup> |      | ns    |                                                                                     |

| FCBA                    | FULL $\downarrow$ access from RCLKS $\downarrow$                      | 3.0 <sup>1</sup> |      | ns    |                                                                                     |

| ЕСВН, FCBH,<br>ТНСВН    | Old EMPTY, FULL, EQTH, & GETH valid hold time from RCLKS $\downarrow$ |                  | 1.0  | ns    | Empty/full/thresh are invalid from the end of hold until the new access is complete |

| OCA                     | New DO access from RCLKS ↑                                            | 7.5              |      | ns    |                                                                                     |

| ОСН                     | Old DO valid from RCLKS 1                                             |                  | 3.0  | ns    |                                                                                     |

| RDCH                    | RDB hold from RCLKS 1                                                 | 0.5              |      | ns    |                                                                                     |

| RDCS                    | RDB setup to RCLKS ↑                                                  | 1.0              |      | ns    |                                                                                     |

| RPCA                    | New RPE access from RCLKS $\uparrow$                                  | 9.5              |      | ns    |                                                                                     |

| RPCH                    | Old RPE valid from RCLKS $\uparrow$                                   |                  | 3.0  | ns    |                                                                                     |

| HCBA                    | EQTH or GETH access from RCLKS $\downarrow$                           | 4.5              |      | ns    |                                                                                     |

### Notes:

1. At fast cycles, ECBA and FCBA = MAX (7.5 ns – CMH), 3.0 ns.

2. All –F speed grade devices are 20% slower than the standard numbers.

# Synchronous FIFO Read, Pipeline Mode Outputs (Synchronous Pipelined)

### Note: The plot shows the normal operation status.

| Figure 1-46 • | Synchronous F | IFO Read, Pipeline | Mode Outputs | (Synchronous Pipelined) |

|---------------|---------------|--------------------|--------------|-------------------------|

|---------------|---------------|--------------------|--------------|-------------------------|

# Table 1-66T\_J = 0°C to 110°C; V\_{DD} = 2.3 V to 2.7 V for Commercial/industrialT\_J = -55°C to 150°C, V\_{DD} = 2.3 V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                                                           | Min.             | Max. | Units | Notes                                                                               |

|-------------------------|-----------------------------------------------------------------------|------------------|------|-------|-------------------------------------------------------------------------------------|

| CCYC                    | Cycle time                                                            | 7.5              |      | ns    |                                                                                     |

| CMH                     | Clock high phase                                                      | 3.0              |      | ns    |                                                                                     |

| CML                     | Clock low phase                                                       | 3.0              |      | ns    |                                                                                     |

| ECBA                    | New EMPTY access from RCLKS $\downarrow$                              | 3.0 <sup>1</sup> |      | ns    |                                                                                     |

| FCBA                    | FULL $\downarrow$ access from RCLKS $\downarrow$                      | 3.0 <sup>1</sup> |      | ns    |                                                                                     |

| ЕСВН, FCBH,<br>ТНСВН    | Old EMPTY, FULL, EQTH, & GETH valid hold time from RCLKS $\downarrow$ |                  | 1.0  | ns    | Empty/full/thresh are invalid from the end of hold until the new access is complete |

| OCA                     | New DO access from RCLKS $\uparrow$                                   | 2.0              |      | ns    |                                                                                     |

| OCH                     | Old DO valid from RCLKS $\uparrow$                                    |                  | 0.75 | ns    |                                                                                     |

| RDCH                    | RDB hold from RCLKS $\uparrow$                                        | 0.5              |      | ns    |                                                                                     |

| RDCS                    | RDB setup to RCLKS ↑                                                  | 1.0              |      | ns    |                                                                                     |

| RPCA                    | New RPE access from RCLKS ↑                                           | 4.0              |      | ns    |                                                                                     |

| RPCH                    | Old RPE valid from RCLKS $\uparrow$                                   |                  | 1.0  | ns    |                                                                                     |

| НСВА                    | EQTH or GETH access from RCLKS $\downarrow$                           | 4.5              |      | ns    |                                                                                     |

## Notes:

1. At fast cycles, ECBA and FCBA = MAX (7.5 ns - CMS), 3.0 ns.

2. All –F speed grade devices are 20% slower than the standard numbers.

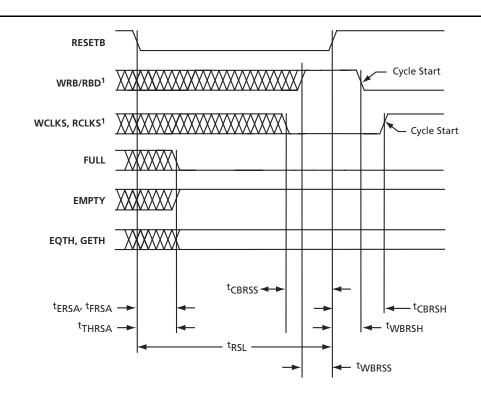

# **FIFO Reset**

### Notes:

1. During reset, either the enables (WRB and RBD) OR the clocks (WCLKS and RCKLS) must be low.

2. The plot shows the normal operation status.

# Figure 1-48 • FIFO Reset

# Table 1-68T\_J = 0°C to 110°C; V\_{DD} = 2.3 V to 2.7 V for Commercial/industrialT\_J = -55°C to 150°C, V\_{DD} = 2.3 V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                                            | Min. | Max. | Units | Notes                  |

|-------------------------|--------------------------------------------------------|------|------|-------|------------------------|

| CBRSH <sup>1</sup>      | WCLKS or RCLKS $\uparrow$ hold from RESETB $\uparrow$  | 1.5  |      | ns    | Synchronous mode only  |

| CBRSS <sup>1</sup>      | WCLKS or RCLKS $\downarrow$ setup to RESETB $\uparrow$ | 1.5  |      | ns    | Synchronous mode only  |

| ERSA                    | New EMPTY $\uparrow$ access from RESETB $\downarrow$   | 3.0  |      | ns    |                        |

| FRSA                    | FULL $\downarrow$ access from RESETB $\downarrow$      | 3.0  |      | ns    |                        |

| RSL                     | RESETB low phase                                       | 7.5  |      | ns    |                        |

| THRSA                   | EQTH or GETH access from RESETB $\downarrow$           | 4.5  |      | ns    |                        |

| WBRSH <sup>1</sup>      | WB $\downarrow$ hold from RESETB $\uparrow$            | 1.5  |      | ns    | Asynchronous mode only |

| WBRSS <sup>1</sup>      | WB $\uparrow$ setup to RESETB $\uparrow$               | 1.5  |      | ns    | Asynchronous mode only |

### Notes:

1. During rest, the enables (WRB and RBD) must be high OR the clocks (WCLKS and RCKLS) must be low.

2. All –F speed grade devices are 20% slower than the standard numbers.