# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                   |

|--------------------------------|--------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                        |

| Number of Logic Elements/Cells | -                                                                        |

| Total RAM Bits                 | 129024                                                                   |

| Number of I/O                  | 440                                                                      |

| Number of Gates                | 600000                                                                   |

| Voltage - Supply               | 2.3V ~ 2.7V                                                              |

| Mounting Type                  | Through Hole                                                             |

| Operating Temperature          | -55°C ~ 125°C (TC)                                                       |

| Package / Case                 | 624-BCCGA                                                                |

| Supplier Device Package        | 624-CCGA (32.5x32.5)                                                     |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/apa600-cgs624m |

|                                |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

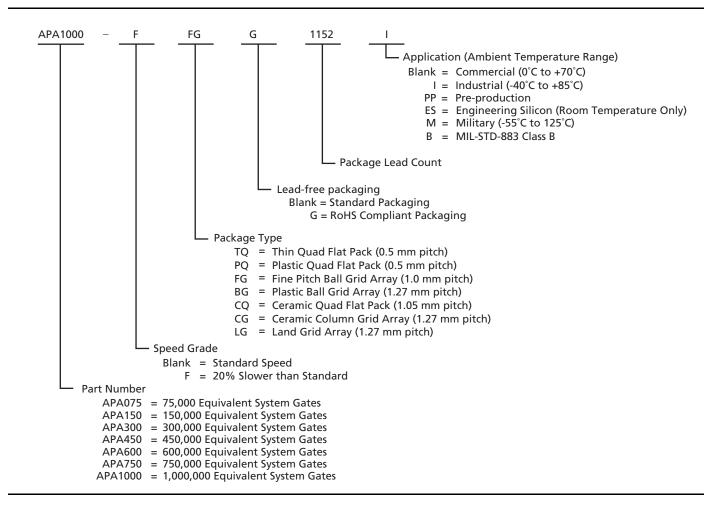

## **Ordering Information**

## **Device Resources**

|         |                       |                 |                  |                  |                  | User                | · I/Os <sup>2</sup> |                 |                     |                  |                       |                 |                         |

|---------|-----------------------|-----------------|------------------|------------------|------------------|---------------------|---------------------|-----------------|---------------------|------------------|-----------------------|-----------------|-------------------------|

|         | Commercial/Industrial |                 |                  |                  |                  |                     |                     |                 |                     | Milita           | Military/MIL-STD-883B |                 |                         |

| Device  | TQFP<br>100-Pin       | TQFP<br>144-Pin | PQFP<br>208-Pin  | PBGA<br>456-Pin  | FBGA<br>144-Pin  | FBGA<br>256-Pin     | FBGA<br>484-Pin     | FBGA<br>676-Pin | FBGA<br>896-Pin     | FBGA<br>1152-Pin | CQFP<br>208-Pin       | CQFP<br>352-Pin | CCGA/<br>LGA<br>624-Pin |

| APA075  | 66                    | 107             | 158              |                  | 100              |                     |                     |                 |                     |                  |                       |                 |                         |

| APA150  | 66                    |                 | 158              | 242              | 100              | 186 <sup>3</sup>    |                     |                 |                     |                  |                       |                 |                         |

| APA300  |                       |                 | 158 <sup>4</sup> | 290 <sup>4</sup> | 100 <sup>4</sup> | 186 <sup>3, 4</sup> |                     |                 |                     |                  | 158                   | 248             |                         |

| APA450  |                       |                 | 158              | 344              | 100              | 186 <sup>3</sup>    | 344 <sup>3</sup>    |                 |                     |                  |                       |                 |                         |

| APA600  |                       |                 | 158 <sup>4</sup> | 356 <sup>4</sup> |                  | 186 <sup>3, 4</sup> | 370 <sup>3</sup>    | 454             |                     |                  | 158                   | 248             | 440                     |

| APA750  |                       |                 | 158              | 356              |                  |                     |                     | 454             | 562 <sup>5</sup>    |                  |                       |                 |                         |

| APA1000 |                       |                 | 158 <sup>4</sup> | 356 <sup>4</sup> |                  |                     |                     |                 | 642 <sup>4, 5</sup> | 712 <sup>5</sup> | 158                   | 248             | 440                     |

Notes:

1. Package Definitions: TQFP = Thin Quad Flat Pack, PQFP = Plastic Quad Flat Pack, PBGA = Plastic Ball Grid Array, FBGA = Fine Pitch Ball Grid Array, CQFP = Ceramic Quad Flat Pack, CCGA = Ceramic Column Grid Array, LGA = Land Grid Array

2. Each pair of PECL I/Os is counted as one user I/O.

3. FG256 and FG484 are footprint-compatible packages.

4. Military Temperature Plastic Package Offering

5. FG896 and FG1152 are footprint-compatible packages.

# **General Guideline**

Maximum performance numbers in this datasheet are based on characterized data. Actel does not guarantee performance beyond the limits specified within the datasheet.

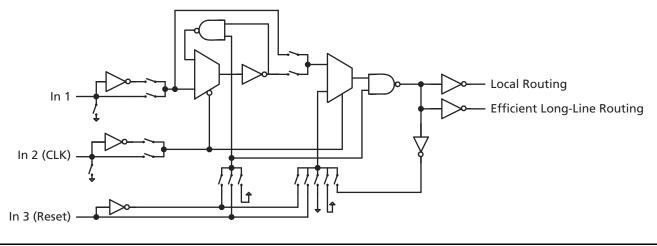

Figure 1-3 • Core Logic Tile

## Live at Power-Up

The Actel Flash-based ProASICPLUS devices support Level 0 of the live at power-up (LAPU) classification standard. This feature helps in system component initialization, executing critical tasks before the processor wakes up, setting up and configuring memory blocks, clock generation, and bus activity management. The LAPU feature of Flash-based ProASICPLUS devices greatly simplifies total system design and reduces total system cost, often eliminating the need for Complex Programmable Logic Device (CPLD) and clock generation PLLs that are used for this purpose in a system. In addition, glitches and brownouts in system power will not corrupt the ProASICPLUS device's Flash configuration, and unlike SRAM-based FPGAs, the device will not have to be reloaded when system power is restored. This enables the reduction or complete removal of the configuration PROM, expensive voltage monitor, brownout detection, and clock generator devices from the PCB design. Flash-based ProASICPLUS devices simplify total system design, and reduce cost and design risk. while increasing system reliability and improving system initialization time.

## Flash Switch

Unlike SRAM FPGAs, ProASIC<sup>PLUS</sup> uses a live-on-power-up ISP Flash switch as its programming element.

In the ProASIC<sup>PLUS</sup> Flash switch, two transistors share the floating gate, which stores the programming information. One is the sensing transistor, which is only used for writing and verification of the floating gate voltage. The other is the switching transistor. It can be used in the architecture to connect/separate routing nets or to configure logic. It is also used to erase the floating gate (Figure 1-2 on page 1-2).

## Logic Tile

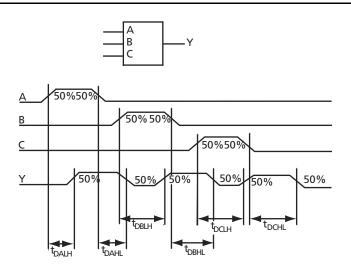

The logic tile cell (Figure 1-3) has three inputs (any or all of which can be inverted) and one output (which can connect to both ultra-fast local and efficient long-line routing resources). Any three-input, one-output logic function (except a three-input XOR) can be configured as one tile. The tile can be configured as a latch with clear or set or as a flip-flop with clear or set. Thus, the tiles can flexibly map logic and sequential gates of a design.

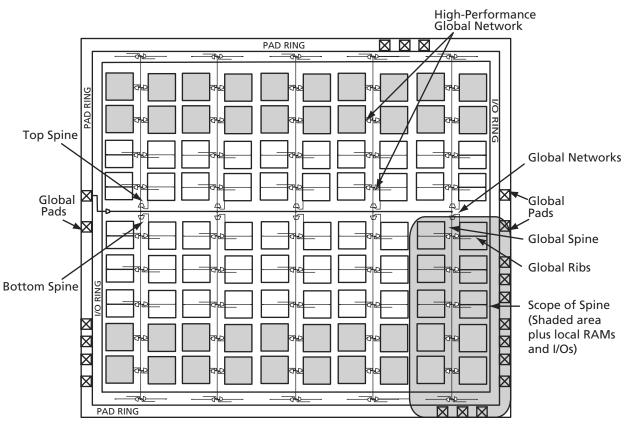

**Note:** This figure shows routing for only one global path. Figure 1-7 • High-Performance Global Network

### Table 1-1 • Clock Spines

|                                    | APA075 | APA150 | APA300 | APA450 | APA600 | APA750 | APA1000 |

|------------------------------------|--------|--------|--------|--------|--------|--------|---------|

| Global Clock Networks (Trees)      | 4      | 4      | 4      | 4      | 4      | 4      | 4       |

| Clock Spines/Tree                  | 6      | 8      | 8      | 12     | 14     | 16     | 22      |

| Total Spines                       | 24     | 32     | 32     | 48     | 56     | 64     | 88      |

| Top or Bottom Spine Height (Tiles) | 16     | 24     | 32     | 32     | 48     | 64     | 80      |

| Tiles in Each Top or Bottom Spine  | 512    | 768    | 1,024  | 1,024  | 1,536  | 2,048  | 2,560   |

| Total Tiles                        | 3,072  | 6,144  | 8,192  | 12,288 | 21,504 | 32,768 | 56,320  |

## Power-Up Sequencing

While ProASIC<sup>PLUS</sup> devices are live at power-up, the order of V<sub>DD</sub> and V<sub>DDP</sub> power-up is important during system start-up. V<sub>DD</sub> should be powered up simultaneously with V<sub>DDP</sub> on ProASIC<sup>PLUS</sup> devices. Failure to follow these guidelines may result in undesirable pin behavior during system start-up. For more information, refer to Actel's *Power-Up Behavior of ProASIC<sup>PLUS</sup> Devices* application note.

## LVPECL Input Pads

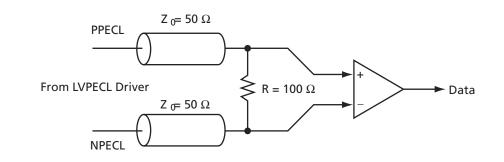

In addition to standard I/O pads and power pads, ProASIC<sup>PLUS</sup> devices have a single LVPECL input pad on both the east and west sides of the device, along with AVDD and AGND pins to power the PLL block. The LVPECL pad cell consists of an input buffer (containing a low voltage differential amplifier) and a signal and its complement, PPECL (I/P) (PECLN) and NPECL (PECLREF). The LVPECL input pad cell differs from the standard I/O cell in that it is operated from  $V_{DD}$  only.

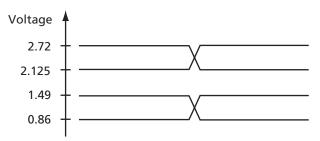

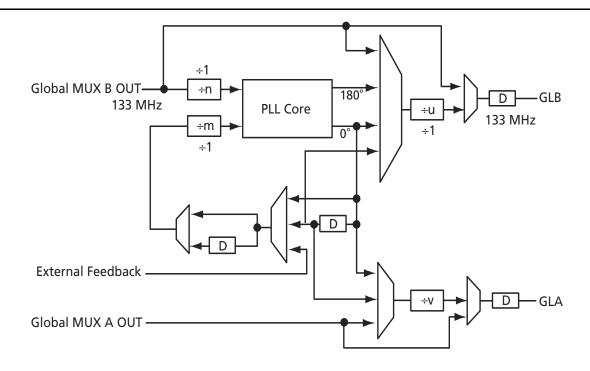

Since it is exclusively an input, it requires no output signal, output enable signal, or output configuration bits. As a special high-speed differential input, it also does not require pull ups. Recommended termination for LVPECL inputs is shown in Figure 1-10. The LVPECL pad cell compares voltages on the PPECL (I/P) pad (as illustrated in Figure 1-11) and the NPECL pad and sends the results to the global MUX (Figure 1-14 on page 1-14). This high-speed, low-skew output essentially controls the clock conditioning circuit.

LVPECLs are designed to meet LVPECL JEDEC receiver standard levels (Table 1-5).

### Figure 1-10 • Recommended Termination for LVPECL Inputs

### Figure 1-11 • LVPECL High and Low Threshold Values

### Table 1-5LVPECL Receiver Specifications

| Symbol          | Parameter                  | Min. | Мах             | Units |

|-----------------|----------------------------|------|-----------------|-------|

| V <sub>IH</sub> | Input High Voltage         | 1.49 | 2.72            | V     |

| V <sub>IL</sub> | Input Low Voltage          | 0.86 | 2.125           | V     |

| V <sub>ID</sub> | Differential Input Voltage | 0.3  | V <sub>DD</sub> | V     |

## Boundary Scan (JTAG)

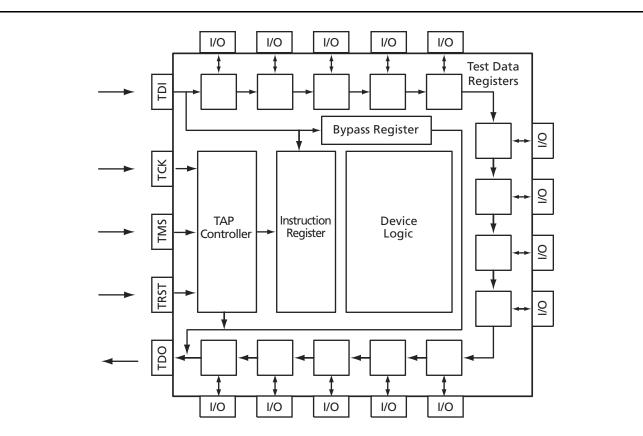

ProASIC<sup>PLUS</sup> devices are compatible with IEEE Standard 1149.1, which defines a set of hardware architecture and mechanisms for cost-effective, board-level testing. The basic ProASIC<sup>PLUS</sup> boundary-scan logic circuit is composed of the TAP (test access port), TAP controller, test data registers, and instruction register (Figure 1-12). This circuit supports all mandatory IEEE 1149.1 instructions (EXTEST, SAMPLE/PRELOAD and BYPASS) and the optional IDCODE instruction (Table 1-6).

Each test section is accessed through the TAP, which has five associated pins: TCK (test clock input), TDI and TDO (test data input and output), TMS (test mode selector) and TRST (test reset input). TMS, TDI and TRST are equipped with pull-up resistors to ensure proper operation when no input data is supplied to them. These pins are dedicated for boundary-scan test usage. Actel recommends that a nominal 20 k $\Omega$  pull-up resistor is added to TDO and TCK pins.

The TAP controller is a four-bit state machine (16 states) that operates as shown in Figure 1-13 on page 1-12. The '1's and '0's represent the values that must be present at TMS at a rising edge of TCK for the given state transition to occur. IR and DR indicate that the instruction register or the data register is operating in that state.

ProASIC<sup>PLUS</sup> devices have to be programmed at least once for complete boundary-scan functionality to be available. Prior to being programmed, EXTEST is not available. If boundary-scan functionality is required prior to programming, refer to online technical support on the Actel website and search for ProASIC<sup>PLUS</sup> BSDL.

| Figure 1-12 • ProASIC <sup>PLUS</sup> JTAG Boundary Scan | Test Logic Circuit |

|----------------------------------------------------------|--------------------|

|----------------------------------------------------------|--------------------|

### Table 1-6Boundary-Scan Opcodes

|                | Hex Opcode |

|----------------|------------|

| EXTEST         | 00         |

| SAMPLE/PRELOAD | 01         |

| IDCODE         | OF         |

| Table 1-6 • | Boundary-Scan | Opcodes |

|-------------|---------------|---------|

|-------------|---------------|---------|

|        | Hex Opcode |

|--------|------------|

| CLAMP  | 05         |

| BYPASS | FF         |

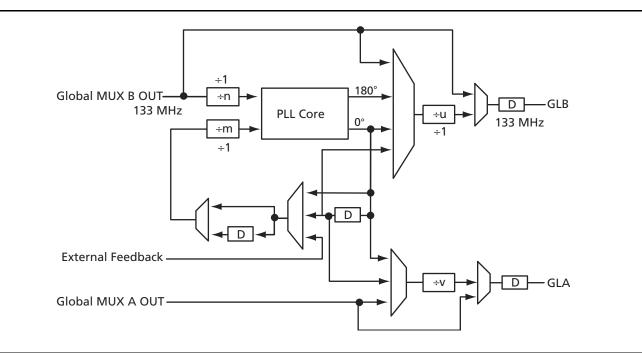

### Figure 1-18 • Using the PLL to Delay the Input Clock

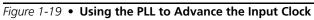

Figure 1-20 • Using the PLL for Clock Deskewing

### ProASIC<sup>PLUS</sup> Flash Family FPGAs

**Note:** Each RAM block contains a multiplexer (called DMUX) for each output signal, increasing design efficiency. These DMUX cells do not consume any core logic tiles and connect directly to high-speed routing resources between the RAM blocks. They are used when RAM blocks are cascaded and are automatically inserted by the software tools.

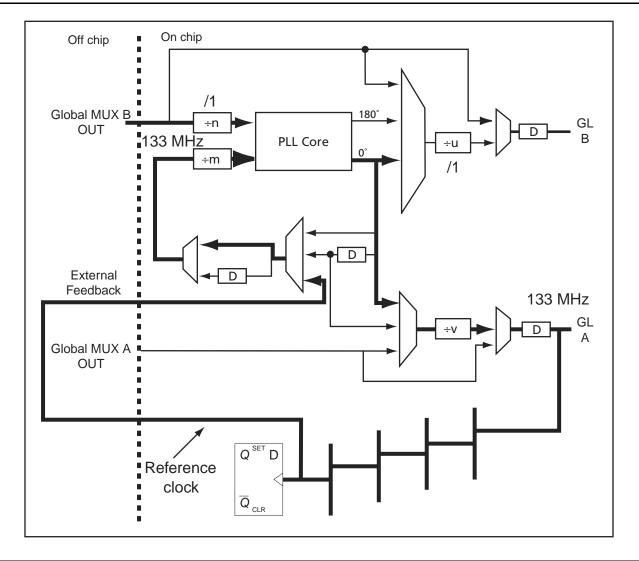

Figure 1-22 • Basic FIFO Block Diagrams

| FIFO Signal | Bits | In/Out | Description                                                                                                                                 |

|-------------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|

| WCLKS       | 1    | In     | Write clock used for synchronization on write side                                                                                          |

| RCLKS       | 1    | In     | Read clock used for synchronization on read side                                                                                            |

| LEVEL <0:7> | 8    | In     | Direct configuration implements static flag logic                                                                                           |

| RBLKB       | 1    | In     | Read block select (active Low)                                                                                                              |

| RDB         | 1    | In     | Read pulse (active Low)                                                                                                                     |

| RESET       | 1    | In     | Reset for FIFO pointers (active Low)                                                                                                        |

| WBLKB       | 1    | In     | Write block select (active Low)                                                                                                             |

| DI<0:8>     | 9    | In     | Input data bits <0:8>, <8> will be generated parity if PARGEN is true                                                                       |

| WRB         | 1    | In     | Write pulse (active Low)                                                                                                                    |

| FULL, EMPTY | 2    | Out    | FIFO flags. FULL prevents write and EMPTY prevents read                                                                                     |

| EQTH, GEQTH | 2    | Out    | EQTH is true when the FIFO holds the number of words specified by the LEVEL signal. GEQTH is true when the FIFO holds (LEVEL) words or more |

| DO<0:8>     | 9    | Out    | Output data bits <0:8>. <8> will be parity output if PARGEN is true.                                                                        |

| RPE         | 1    | Out    | Read parity error (active High)                                                                                                             |

| WPE         | 1    | Out    | Write parity error (active High)                                                                                                            |

| LGDEP <0:2> | 3    | In     | Configures DEPTH of the FIFO to 2 (LGDEP+1)                                                                                                 |

| PARODD      | 1    | In     | Parity generation/detect – Even when Low, Odd when High                                                                                     |

| Table 1-15 • | Memory | <b>Block FIFO</b> | Interface | Signals |

|--------------|--------|-------------------|-----------|---------|

|--------------|--------|-------------------|-----------|---------|

# **Design Environment**

The ProASICPLUS family of FPGAs is fully supported by both Actel's Libero® Integrated Design Environment (IDE) and Designer FPGA Development software. Actel Libero IDE is an integrated design manager that seamlessly integrates design tools while guiding the user through the design flow, managing all design and log files, and passing necessary design data among tools. Additionally, Libero IDE allows users to integrate both schematic and HDL synthesis into a single flow and verify the entire design in a single environment (see Actel's website for more information about Libero IDE). Libero IDE includes Synplify<sup>®</sup> AE from Synplicity<sup>®</sup>, ViewDraw<sup>®</sup> AE from Mentor Graphics<sup>®</sup>, ModelSim<sup>®</sup> HDL Simulator from Mentor Graphics, WaveFormer Lite™ AE from SynaptiCAD<sup>®</sup>, PALACE™ AE Physical Synthesis from Magma, and Designer software from Actel.

PALACE is an effective tool when designing with ProASIC<sup>PLUS</sup>. PALACE AE Physical Synthesis from Magma takes an EDIF netlist and optimizes the performance of ProASIC<sup>PLUS</sup> devices through a physical placement-driven process, ensuring that timing closure is easily achieved.

Actel's Designer software is a place-and-route tool that provides a comprehensive suite of back-end support tools for FPGA development. The Designer software includes the following:

- Timer a world-class integrated static timing analyzer and constraints editor that support timing-driven place-and-route

- NetlistViewer a design netlist schematic viewer

- ChipPlanner a graphical floorplanner viewer and editor

- SmartPower allows the designer to quickly estimate the power consumption of a design

- PinEditor a graphical application for editing pin assignments and I/O attributes

- I/O Attribute Editor displays all assigned and unassigned I/O macros and their attributes in a spreadsheet format

With the Designer software, a user can lock the design pins before layout while minimally impacting the results of place-and-route. Additionally, Actel's back-annotation flow is compatible with all the major simulators. Another tool included in the Designer software is the SmartGen macro builder, which easily creates popular and commonly used logic functions for implementation into your schematic or HDL design.

Actel's Designer software is compatible with the most popular FPGA design entry and verification tools from EDA vendors, such as Mentor Graphics, Synplicity, Synopsys, and Cadence Design Systems. The Designer software is available for both the Windows and UNIX operating systems.

## ISP

The user can generate \*.bit or \*.stp programming files from the Designer software and can use these files to program a device.

ProASIC<sup>PLUS</sup> devices can be programmed in-system. For more information on ISP of ProASIC<sup>PLUS</sup> devices, refer to the *In-System Programming ProASIC<sup>PLUS</sup> Devices* and *Performing Internal In-System Programming Using Actel's ProASIC<sup>PLUS</sup> Devices* application notes. Prior to being programmed for the first time, the ProASIC<sup>PLUS</sup> device I/Os are in a tristate condition with the pull-up resistor option enabled.

# **Calculating Typical Power Dissipation**

ProASIC<sup>PLUS</sup> device power is calculated with both a static and an active component. The active component is a function of both the number of tiles utilized and the system speed. Power dissipation can be calculated using the following formula:

### Total Power Consumption—P<sub>total</sub>

$\mathsf{P}_{\mathsf{total}} = \mathsf{P}_{\mathsf{dc}} + \mathsf{P}_{\mathsf{ac}}$

where:

$P_{dc} = 7 \text{ mW}$  for the APA075

8 mW for the APA150 11 mW for the APA300

12 mW for the APA450

12 mW for the APA600

13 mW for the APA750

19 mW for the APA1000

$P_{dc}$  includes the static components of  $P_{VDDP}$  +  $P_{VDD}$  +  $P_{AVDD}$

$P_{ac} = P_{clock} + P_{storage} + P_{logic} + P_{outputs} + P_{inputs} + P_{pll} + P_{memory}$

### Global Clock Contribution—P<sub>clock</sub>

$P_{clock}$ , the clock component of power dissipation, is given by the piece-wise model: for R < 15000 the model is: (P1 + (P2\*R) - (P7\*R2)) \* Fs (lightly-loaded clock trees) for R > 15000 the model is: (P10 + P11\*R) \* Fs (heavily-loaded clock trees) where:

where:

- P1 = 100  $\mu$ W/MHz is the basic power consumption of the clock tree per MHz of the clock

- $P_{2} = 1.3 \,\mu$ W/MHz is the incremental power consumption of the clock tree per storage tile also per MHz of the clock

- $P7 = 0.00003 \,\mu$ W/MHz is a correction factor for partially-loaded clock trees

- P10 = 6850  $\mu$ W/MHz is the basic power consumption of the clock tree per MHz of the clock

- $P_{11} = 0.4 \mu$ W/MHz is the incremental power consumption of the clock tree per storage tile also per MHz of the clock

- R = the number of storage tiles clocked by this clock

- Fs = the clock frequency

### Storage-Tile Contribution—P<sub>storage</sub>

P<sub>storage</sub>, the storage-tile (Register) component of AC power dissipation, is given by

P<sub>storage</sub> = P5 \* ms \* Fs

where:

- P5 =  $1.1 \,\mu$ W/MHz is the average power consumption of a storage tile per MHz of its output toggling rate. The maximum output toggling rate is Fs/2.

- ms = the number of storage tiles (Register) switching during each Fs cycle

Fs = the clock frequency

### ProASIC<sup>PLUS</sup> Flash Family FPGAs

|                 |                               | Commercial/Industria |                 |       |

|-----------------|-------------------------------|----------------------|-----------------|-------|

| Parameter       | Condition                     | Minimum              | Maximum         | Units |

| V <sub>PP</sub> | During Programming            | 15.8                 | 16.5            | V     |

|                 | Normal Operation <sup>1</sup> | 0                    | 16.5            | V     |

| V <sub>PN</sub> | During Programming            | -13.8                | -13.2           | V     |

|                 | Normal Operation <sup>2</sup> | -13.8                | 0.5             | V     |

| РР              | During Programming            |                      | 25              | mA    |

| I <sub>PN</sub> | During Programming            |                      | 10              | mA    |

| AVDD            |                               | V <sub>DD</sub>      | V <sub>DD</sub> | V     |

| AGND            |                               | GND                  | GND             | V     |

### Table 1-20 • Recommended Maximum Operating Conditions Programming and PLL Supplies

Notes:

Please refer to the "VPP Programming Supply Pin" section on page 1-77 for more information.

Please refer to the "VPN Programming Supply Pin" section on page 1-77 for more information.

#### Table 1-21 • Recommended Operating Conditions

|                                        |                                      | Limits                         |                                |                                                    |  |  |

|----------------------------------------|--------------------------------------|--------------------------------|--------------------------------|----------------------------------------------------|--|--|

| Parameter                              | Symbol                               | Commercial                     | Industrial                     | Military/MIL-STD-883                               |  |  |

| DC Supply Voltage (2.5 V I/Os)         | $V_{\text{DD}}$ and $V_{\text{DDP}}$ | 2.5 V ± 0.2 V                  | 2.5 V ± 0.2 V                  | 2.5 V ± 0.2 V                                      |  |  |

| DC Supply Voltage (3.3 V I/Os)         | V <sub>DDP</sub><br>V <sub>DD</sub>  | 3.3 V ± 0.3 V<br>2.5 V ± 0.2 V | 3.3 V ± 0.3 V<br>2.5 V ± 0.2 V | 3.3 V ± 0.3 V<br>2.5 V ± 0.2 V                     |  |  |

| Operating Ambient Temperature Range    | T <sub>A</sub> , T <sub>C</sub>      | 0°C to 70°C                    | –40°C to 85°C                  | –55°C (T <sub>A</sub> ) to 125°C (T <sub>C</sub> ) |  |  |

| Maximum Operating Junction Temperature | Tj                                   | 110°C                          | 110°C                          | 150°C                                              |  |  |

Note: For I/O long-term reliability, external pull-up resistors cannot be used to increase output voltage above V<sub>DDP</sub>.

|                  |                                    | Comme<br>Industri          |                    |                     | Military/MIL-STD- 883 <sup>2,3</sup> |                     |                        |       |

|------------------|------------------------------------|----------------------------|--------------------|---------------------|--------------------------------------|---------------------|------------------------|-------|

| Symbol           | Parameter                          | Condition                  |                    | Min.                | Max.                                 | Min.                | Max.                   | Units |

| V <sub>DD</sub>  | Supply Voltage for Core            |                            |                    | 2.3                 | 2.7                                  | 2.3                 | 2.7                    | V     |

| V <sub>DDP</sub> | Supply Voltage for I/O Ring        |                            |                    | 3.0                 | 3.6                                  | 3.0                 | 3.6                    | V     |

| V <sub>IH</sub>  | Input High Voltage                 |                            |                    | $0.5V_{\text{DDP}}$ | V <sub>DDP</sub> + 0.5               | 0.5V <sub>DDP</sub> | V <sub>DDP</sub> + 0.5 | V     |

| V <sub>IL</sub>  | Input Low Voltage                  |                            |                    | -0.5                | 0.3V <sub>DDP</sub>                  | -0.5                | 0.3V <sub>DDP</sub>    | V     |

| I <sub>IPU</sub> | Input Pull-up Voltage <sup>4</sup> |                            |                    | $0.7V_{\text{DDP}}$ |                                      | 0.7V <sub>DDP</sub> |                        | V     |

| I <sub>IL</sub>  | Input Leakage Current <sup>5</sup> | $0 < V_{IN} < V_{DDP}$     | Std.               | -10                 | 10                                   | -50                 | 50                     | μΑ    |

|                  |                                    |                            | -F <sup>3, 6</sup> | -10                 | 100                                  |                     |                        | μΑ    |

| V <sub>OH</sub>  | Output High Voltage                | I <sub>OUT</sub> = -500 μA |                    | $0.9V_{\text{DDP}}$ |                                      | 0.9V <sub>DDP</sub> |                        | V     |

| V <sub>OL</sub>  | Output Low Voltage                 | I <sub>OUT</sub> = 1500 μA |                    |                     | 0.1V <sub>DDP</sub>                  |                     | 0.1V <sub>DDP</sub>    | V     |

| C <sub>IN</sub>  | Input Pin Capacitance (except CLK) |                            |                    |                     | 10                                   |                     | 10                     | pF    |

| C <sub>CLK</sub> | CLK Pin Capacitance                |                            |                    | 5                   | 12                                   | 5                   | 12                     | рF    |

### Notes:

1. For PCI operation, use GL33, OTB33PH, OB33PH, IOB33PH, IB33, or IB33S macro library cell only.

2. All process conditions. Junction Temperature: -40 to +110°C for Commercial and Industrial devices and -55 to +125°C for Military.

3. All –F parts are available as commercial only.

4. This specification is guaranteed by design. It is the minimum voltage to which pull-up resistors are calculated to pull a floated network. Designers with applications sensitive to static power utilization should ensure that the input buffer is conducting minimum current at this input voltage.

5. Input leakage currents include hi-Z output leakage for all bidirectional buffers with tristate outputs.

6. The sum of the leakage currents for all inputs shall not exceed 2mA per device.

## **Module Delays**

Figure 1-29 • Module Delays

# Sample Macrocell Library Listing

Table 1-47 • Worst-Case Military Conditions<sup>1</sup>

$V_{DD} = 2.3 V$ ,  $T_{J} = 70^{\circ} C$ ,  $T_{J} = 70^{\circ} C$ ,  $T_{J} = 125^{\circ} C$  for Military/MIL-STD-883

|           |                                                  |                 | S   | td. | -   | F <sup>2</sup> |       |

|-----------|--------------------------------------------------|-----------------|-----|-----|-----|----------------|-------|

| Cell Name | Description                                      |                 | Max | Min | Max | Min            | Units |

| NAND2     | 2-Input NAND                                     |                 | 0.5 |     | 0.6 |                | ns    |

| AND2      | 2-Input AND                                      |                 | 0.7 |     | 0.8 |                | ns    |

| NOR3      | 3-Input NOR                                      |                 | 0.8 |     | 1.0 |                | ns    |

| MUX2L     | 2-1 MUX with Active Low Select                   |                 | 0.5 |     | 0.6 |                | ns    |

| OA21      | 2-Input OR into a 2-Input AND                    |                 | 0.8 |     | 1.0 |                | ns    |

| XOR2      | 2-Input Exclusive OR                             |                 | 0.6 |     | 0.8 |                | ns    |

| LDL       | Active Low Latch (LH/HL)                         | LH <sup>3</sup> | 0.9 |     | 1.1 |                | ns    |

|           | CLK-Q                                            | HL <sup>3</sup> | 0.8 |     | 0.9 |                | ns    |

|           | t <sub>setup</sub>                               | •               |     | 0.7 |     | 0.8            | ns    |

|           | t <sub>hold</sub>                                |                 |     | 0.1 |     | 0.2            | ns    |

| DFFL      | Negative Edge-Triggered D-type Flip-Flop (LH/HL) | LH <sup>3</sup> | 0.9 |     | 1.1 |                | ns    |

|           | CLK-Q                                            | HL <sup>3</sup> | 0.8 |     | 1.0 |                | ns    |

|           | t <sub>setup</sub>                               | •               |     | 0.6 |     | 0.7            | ns    |

|           | t <sub>hold</sub>                                |                 |     | 0.0 |     | 0.0            | ns    |

Notes:

1. Intrinsic delays have a variable component, coupled to the input slope of the signal. These numbers assume an input slope typical of local interconnect.

- 2. All –F parts are only available as commercial.

- 3. LH and HL refer to the Q transitions from Low to High and High to Low, respectively.

## Synchronous SRAM Write

**Note:** The plot shows the normal operation status.

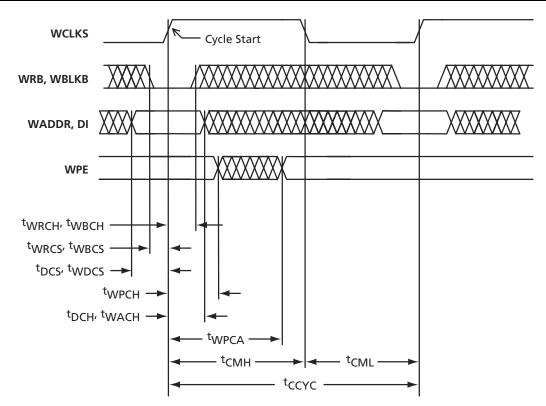

### Figure 1-36 • Synchronous SRAM Write

# Table 1-57T\_J = 0°C to 110°C; V\_{DD} = 2.3 V to 2.7 V for Commercial/industrialT\_J = -55°C to 150°C, V\_{DD} = 2.3 V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                            | Min. | Max. | Units | Notes                |

|-------------------------|----------------------------------------|------|------|-------|----------------------|

| CCYC                    | Cycle time                             | 7.5  |      | ns    |                      |

| СМН                     | Clock high phase                       | 3.0  |      | ns    |                      |

| CML                     | Clock low phase                        | 3.0  |      | ns    |                      |

| DCH                     | DI hold from WCLKS ↑                   | 0.5  |      | ns    |                      |

| DCS                     | DI setup to WCLKS ↑                    | 1.0  |      | ns    |                      |

| WACH                    | WADDR hold from WCLKS ↑                | 0.5  |      | ns    |                      |

| WDCS                    | WADDR setup to WCLKS ↑                 | 1.0  |      | ns    |                      |

| WPCA                    | New WPE access from WCLKS $\uparrow$   | 3.0  |      | ns    | WPE is invalid while |

| WPCH                    | Old WPE valid from WCLKS $\uparrow$    |      | 0.5  | ns    | PARGEN is active     |

| WRCH, WBCH              | WRB & WBLKB hold from WCLKS $\uparrow$ | 0.5  |      | ns    |                      |

| WRCS, WBCS              | WRB & WBLKB setup to WCLKS $\uparrow$  | 1.0  |      | ns    |                      |

### Notes:

1. On simultaneous read and write accesses to the same location, DI is output to DO.

2. All –F speed grade devices are 20% slower than the standard numbers.

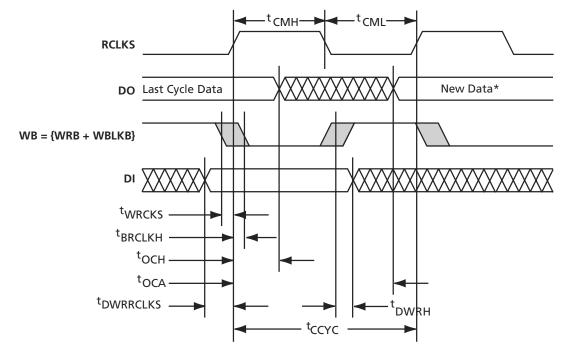

## Asynchronous Write and Synchronous Read to the Same Location

\* New data is read if WB  $\downarrow$  occurs before setup time. The stored data is read if WB  $\downarrow$  occurs after hold time.

### Note: The plot shows the normal operation status.

| Figure 1-38 • | Asynchronous | Write and Synchronous Read to the Same Location |

|---------------|--------------|-------------------------------------------------|

|---------------|--------------|-------------------------------------------------|

# Table 1-59T<sub>J</sub> = 0°C to 110°C; V<sub>DD</sub> = 2.3 V to 2.7 V for Commercial/industrialT<sub>J</sub> = -55°C to 150°C, V<sub>DD</sub> = 2.3 V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                                    | Min. | Max. | Units | Notes                 |

|-------------------------|------------------------------------------------|------|------|-------|-----------------------|

| ССҮС                    | Cycle time                                     | 7.5  |      | ns    |                       |

| СМН                     | Clock high phase                               | 3.0  |      | ns    |                       |

| CML                     | Clock low phase                                | 3.0  |      | ns    |                       |

| WBRCLKS                 | WB $\downarrow$ to RCLKS $\uparrow$ setup time | -0.1 |      | ns    |                       |

| WBRCLKH                 | WB $\downarrow$ to RCLKS $\uparrow$ hold time  |      | 7.0  | ns    |                       |

| ОСН                     | Old DO valid from RCLKS $\uparrow$             |      | 3.0  | ns    | OCA/OCH displayed for |

| OCA                     | New DO valid from RCLKS $\uparrow$             | 7.5  |      | ns    | Access Timed Output   |

| DWRRCLKS                | DI to RCLKS ↑ setup time                       | 0    |      | ns    |                       |

| DWRH                    | DI to WB ↑ hold time                           |      | 1.5  | ns    |                       |

### Notes:

- 1. This behavior is valid for Access Timed Output and Pipelined Mode Output. The table shows the timings of an Access Timed Output.

- 2. In asynchronous write and synchronous read access to the same location, the new write data will be read out if the active write signal edge occurs before or at the same time as the active read clock edge. If WB changes to low after hold time, the data will be read.

3. A setup or hold time violation will result in unknown output data.

4. All –F speed grade devices are 20% slower than the standard numbers.

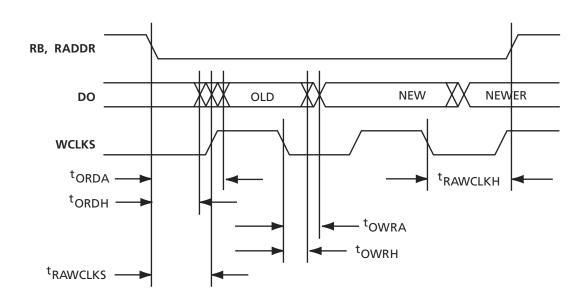

## Synchronous Write and Asynchronous Read to the Same Location

### Note: The plot shows the normal operation status.

*Figure 1-40* • Synchronous Write and Asynchronous Read to the Same Location

# Table 1-61 $T_J = 0^{\circ}C$ to 110°C; $V_{DD} = 2.3$ V to 2.7 V for Commercial/industrial $T_J = -55^{\circ}C$ to 150°C, $V_{DD} = 2.3$ V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                                    | Min. | Max. | Units | Notes |

|-------------------------|------------------------------------------------|------|------|-------|-------|

| ORDA                    | New DO access from RB $\downarrow$             | 7.5  |      | ns    |       |

| ORDH                    | Old DO valid from RB $\downarrow$              |      | 3.0  | ns    |       |

| OWRA                    | New DO access from WCLKS $\downarrow$          | 3.0  |      | ns    |       |

| OWRH                    | Old DO valid from WCLKS $\downarrow$           |      | 0.5  | ns    |       |

| RAWCLKS                 | RB $\downarrow$ or RADDR from WCLKS $\uparrow$ | 5.0  |      | ns    |       |

| RAWCLKH                 | RB $\uparrow$ or RADDR from WCLKS $\downarrow$ | 5.0  |      | ns    |       |

### Notes:

1. During an asynchronous read cycle, each write operation (synchronous or asynchronous) to the same location will automatically trigger a read operation which updates the read data.

2. Violation of RAWCLKS will disturb access to OLD data.

3. Violation of RAWCLKH will disturb access to NEWER data.

4. All –F speed grade devices are 20% slower than the standard numbers.

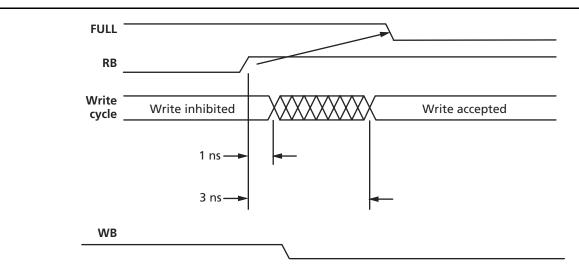

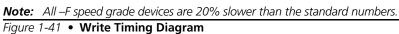

Note: All – F speed grade devices are 20% slower than the standard numbers.

Figure 1-42 • Read Timing Diagram

# **Pin Description**

## **User Pins**

### I/O User Input/Output

The I/O pin functions as an input, output, tristate, or bidirectional buffer. Input and output signal levels are compatible with standard LVTTL and LVCMOS specifications. Unused I/O pins are configured as inputs with pull-up resistors.

### NC No Connect

To maintain compatibility with other Actel ProASIC<sup>PLUS</sup> products, it is recommended that this pin not be connected to the circuitry on the board.

### GL Global Pin

Low skew input pin for clock or other global signals. This pin can be configured with an internal pull-up resistor. When it is not connected to the global network or the clock conditioning circuit, it can be configured and used as a normal I/O.

### GLMX Global Multiplexing Pin

Low skew input pin for clock or other global signals. This pin can be used in one of two special ways (refer to Actel's Using ProASIC<sup>PLUS</sup> Clock Conditioning Circuits).

When the external feedback option is selected for the PLL block, this pin is routed as the external feedback source to the clock conditioning circuit.

In applications where two different signals access the same global net at different times through the use of GLMXx and GLMXLx macros, this pin will be fixed as one of the source pins.

This pin can be configured with an internal pull-up resistor. When it is not connected to the global network or the clock conditioning circuit, it can be configured and used as any normal I/O. If not used, the GLMXx pin will be configured as an input with pull-up.

## **Dedicated Pins**

GND Ground

Common ground supply voltage.

V<sub>DD</sub> Logic Array Power Supply Pin

2.5 V supply voltage.

V<sub>DDP</sub> I/O Pad Power Supply Pin

2.5 V or 3.3 V supply voltage.

### TMS Test Mode Select

The TMS pin controls the use of boundary-scan circuitry. This pin has an internal pull-up resistor.

### TCK Test Clock

Clock input pin for boundary scan (maximum 10 MHz). Actel recommends adding a nominal 20  $k\Omega$  pull-up resistor to this pin.

### TDI Test Data In

Serial input for boundary scan. A dedicated pull-up resistor is included to pull this pin high when not being driven.

### TDO Test Data Out

Serial output for boundary scan. Actel recommends adding a nominal  $20k\Omega$  pull-up resistor to this pin.

### TRST Test Reset Input

Asynchronous, active-low input pin for resetting boundary-scan circuitry. This pin has an internal pull-up resistor. For more information, please refer to *Power-up Behavior of ProASIC*<sup>PLUS</sup> *Devices* application note.

## **Special Function Pins**

### RCK Running Clock

A free running clock is needed during programming if the programmer cannot guarantee that TCK will be uninterrupted. If not used, this pin has an internal pullup and can be left floating.

### NPECL User Negative Input

Provides high speed clock or data signals to the PLL block. If unused, leave the pin unconnected.

### PPECL User Positive Input

Provides high speed clock or data signals to the PLL block. If unused, leave the pin unconnected.

### AVDD PLL Power Supply

Analog  $V_{DD}$  should be  $V_{DD}$  (core voltage) 2.5 V (nominal) and be decoupled from GND with suitable decoupling capacitors to reduce noise. For more information, refer to Actel's Using ProASIC<sup>PLUS</sup> Clock Conditioning Circuits application note. If the clock conditioning circuitry is not used in a design, AVDD can either be left floating or tied to 2.5 V.

### AGND PLL Power Ground

The analog ground can be connected to the system ground. For more information, refer to Actel's Using ProASIC<sup>PLUS</sup> Clock Conditioning Circuits application note. If the PLLs or clock conditioning circuitry are not used in a design, AGND should be tied to GND.