Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | -                                                            |

| Number of Logic Elements/Cells | -                                                            |

| Total RAM Bits                 | 129024                                                       |

| Number of I/O                  | 248                                                          |

| Number of Gates                | 600000                                                       |

| Voltage - Supply               | 2.3V ~ 2.7V                                                  |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | -55°C ~ 125°C (TC)                                           |

| Package / Case                 | 352-BFCQFP with Tie Bar                                      |

| Supplier Device Package        | 352-CQFP (75x75)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/apa600-cq352m |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

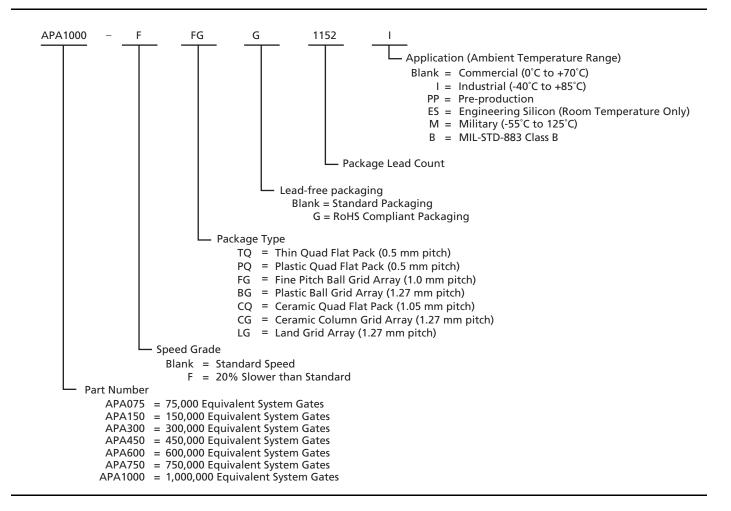

# **Ordering Information**

ii v5.8

# **Temperature Grade Offerings**

| Package | APA075 | APA150 | APA300  | APA450 | APA600  | APA750 | APA1000 |

|---------|--------|--------|---------|--------|---------|--------|---------|

| TQ100   | С, І   | С, І   |         |        |         |        |         |

| TQ144   | С, І   |        |         |        |         |        |         |

| PQ208   | С, І   | С, І   | C, I, M | С, І   | C, I, M | С, І   | C, I, M |

| BG456   |        | С, І   | C, I, M | С, І   | C, I, M | С, І   | C, I, M |

| FG144   | С, І   | С, І   | C, I, M | С, І   |         |        |         |

| FG256   |        | С, І   | C, I, M | С, І   | C, I, M |        |         |

| FG484   |        |        |         | С, І   | C, I, M |        |         |

| FG676   |        |        |         |        | C, I, M | С, І   |         |

| FG896   |        |        |         |        |         | С, І   | C, I, M |

| FG1152  |        |        |         |        |         |        | С, І    |

| CQ208   |        |        | M, B    |        | M, B    |        | M, B    |

| CQ352   |        |        | M, B    |        | M, B    |        | M, B    |

| CG624   |        |        |         |        | M, B    |        | M, B    |

**Note:** C = Commercial I = Industrial M = MilitaryB = MIL-STD-883

# **Speed Grade and Temperature Matrix**

|      | -F | Std.     |

|------|----|----------|

| С    | ✓  | ✓        |

| I    |    | ✓        |

| M, B |    | <b>√</b> |

**Note:** C = Commercial I = Industrial M = MilitaryB = MIL-STD-883

iv v5.8

### **Power-Up Sequencing**

While ProASIC PLUS devices are live at power-up, the order of  $V_{DD}$  and  $V_{DDP}$  power-up is important during system start-up.  $V_{DD}$  should be powered up simultaneously with  $V_{DDP}$  on ProASIC devices. Failure to follow these guidelines may result in undesirable pin behavior during system start-up. For more information, refer to Actel's Power-Up Behavior of ProASIC Devices application note.

### **LVPECL Input Pads**

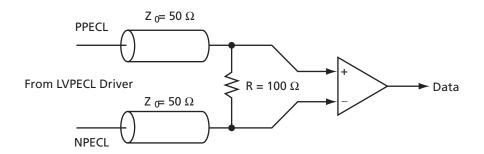

In addition to standard I/O pads and power pads, ProASICPLUS devices have a single LVPECL input pad on both the east and west sides of the device, along with AVDD and AGND pins to power the PLL block. The LVPECL pad cell consists of an input buffer (containing a

low voltage differential amplifier) and a signal and its complement, PPECL (I/P) (PECLN) and NPECL (PECLREF). The LVPECL input pad cell differs from the standard I/O cell in that it is operated from  $V_{DD}$  only.

Since it is exclusively an input, it requires no output signal, output enable signal, or output configuration bits. As a special high-speed differential input, it also does not require pull ups. Recommended termination for LVPECL inputs is shown in Figure 1-10. The LVPECL pad cell compares voltages on the PPECL (I/P) pad (as illustrated in Figure 1-11) and the NPECL pad and sends the results to the global MUX (Figure 1-14 on page 1-14). This high-speed, low-skew output essentially controls the clock conditioning circuit.

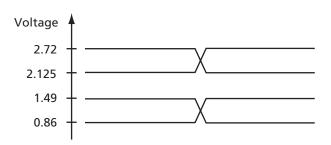

LVPECLs are designed to meet LVPECL JEDEC receiver standard levels (Table 1-5).

Figure 1-10 • Recommended Termination for LVPECL Inputs

Figure 1-11 • LVPECL High and Low Threshold Values

Table 1-5 • LVPECL Receiver Specifications

| Symbol          | Parameter                  | Min. | Max      | Units |

|-----------------|----------------------------|------|----------|-------|

| V <sub>IH</sub> | Input High Voltage         | 1.49 | 2.72     | V     |

| V <sub>IL</sub> | Input Low Voltage          | 0.86 | 2.125    | V     |

| $V_{\text{ID}}$ | Differential Input Voltage | 0.3  | $V_{DD}$ | V     |

1-10 v5.8

# Timing Control and Characteristics

# **ProASIC**PLUS Clock Management System

ProASIC<sup>PLUS</sup> devices provide designers with very flexible clock conditioning capabilities. Each member of the ProASIC<sup>PLUS</sup> family contains two phase-locked loop (PLL) blocks which perform the following functions:

- Clock Phase Adjustment via Programmable Delay (250 ps steps from -7 ns to +8 ns)

- Clock Skew Minimization

- Clock Frequency Synthesis

Each PLL has the following key features:

- Input Frequency Range (f<sub>IN</sub>) = 1.5 to 180 MHz

- Feedback Frequency Range (f<sub>VCO</sub>) = 24 to 180 MHz

- Output Frequency Range (f<sub>OUT</sub>) = 8 to 180 MHz

- Output Phase Shift = 0 ° and 180 °

- Output Duty Cycle = 50%

- Low Output Jitter (max at 25°C)

- f<sub>VCO</sub> <10 MHz. Jitter ±1% or better

- 10 MHz <  $f_{VCO}$  < 60 MHz. Jitter ±2% or better

- f<sub>VCO</sub> > 60 MHz. Jitter ±1% or better

**Note:** Jitter(ps) = Jitter(%)\* period

For Example:

Jitter in picoseconds at 100 MHz = 0.01 \* (1/100E6) = 100 ps

- Maximum Acquisition =  $80 \mu s$  for  $f_{VCO} > 40 MHz$ Time =  $30 \mu s$  for  $f_{VCO} < 40 MHz$

- Low Power Consumption 6.9 mW (max analog supply) + 7.0μW/MHz (max – digital supply)

### **Physical Implementation**

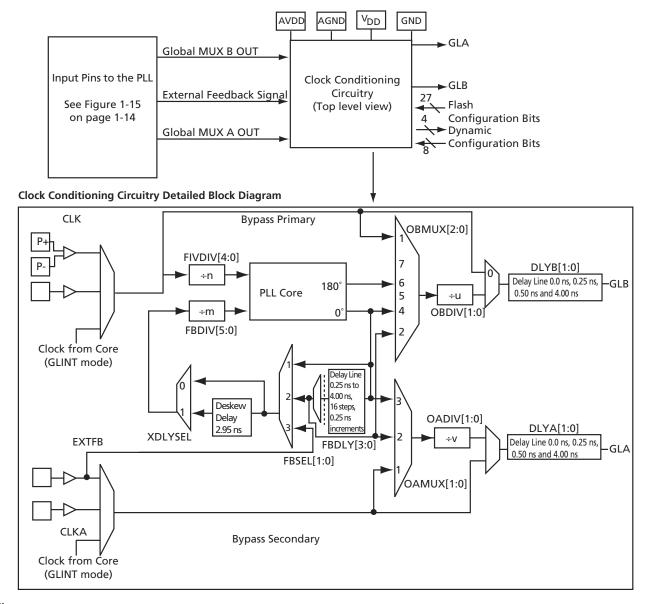

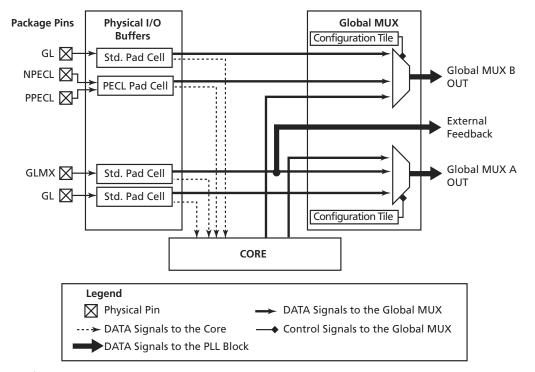

Each side of the chip contains a clock conditioning circuit based on a 180 MHz PLL block (Figure 1-14 on page 1-14). Two global multiplexed lines extend along each side of the chip to provide bidirectional access to the PLL on that side (neither MUX can be connected to the opposite side's PLL). Each global line has optional LVPECL input pads (described below). The global lines may be driven by either the LVPECL global input pad or the outputs from the PLL block, or both. Each global line can be driven by a different output from the PLL. Unused global pins can be configured as regular I/Os or left unconnected. They default to an input with pull-up. The two signals available to drive the global networks are as

follows (Figure 1-15 on page 1-15, Table 1-7 on page 1-15, and Table 1-8 on page 1-16):

### **Global A (secondary clock)**

- Output from Global MUX A

- Conditioned version of PLL output (f<sub>OUT</sub>) delayed or advanced

- Divided version of either of the above

- Further delayed version of either of the above (0.25 ns, 0.50 ns, or 4.00 ns delay)<sup>1</sup>

#### **Global B**

- Output from Global MUX B

- Delayed or advanced version of f<sub>OUT</sub>

- Divided version of either of the above

- Further delayed version of either of the above (0.25 ns, 0.50 ns, or 4.00 ns delay)<sup>2</sup>

### **Functional Description**

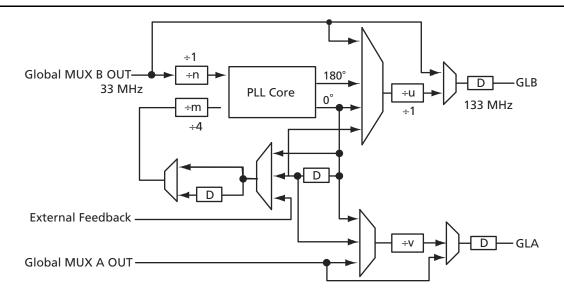

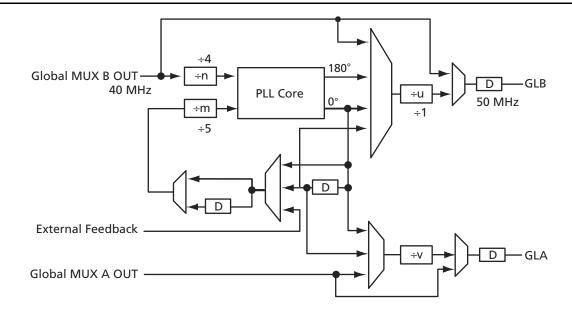

Each PLL block contains four programmable dividers as shown in Figure 1-14 on page 1-14. These allow frequency scaling of the input clock signal as follows:

- The n divider divides the input clock by integer factors from 1 to 32.

- The m divider in the feedback path allows multiplication of the input clock by integer factors ranging from 1 to 64.

- The two dividers together can implement any combination of multiplication and division resulting in a clock frequency between 24 and 180 MHz exiting the PLL core. This clock has a fixed 50% duty cycle.

- The output frequency of the PLL core is given by the formula EQ 1-1 (f<sub>REF</sub> is the reference clock frequency):

$$f_{OUT} = f_{REF} * m/n$$

EQ 1-1

• The third and fourth dividers (u and v) permit the signals applied to the global network to each be further divided by integer factors ranging from 1 to 4.

The implementations shown in EQ2 and EQ3 enable the user to define a wide range of frequency multiplier and divisors.

$$f_{GLB} = m/(n*u)$$

EQ 1-2

$$f_{GLA} = m/(n*v)$$

EQ 1-3

<sup>1.</sup> This mode is available through the delay feature of the Global MUX driver.

enable the user to define a wide range of frequency multipliers and divisors. The clock conditioning circuit can advance or delay the clock up to 8 ns (in increments of 0.25 ns) relative to the positive edge of the incoming reference clock. The system also allows for the selection of output frequency clock phases of 0° and 180°.

Prior to the application of signals to the rib drivers, they pass through programmable delay units, one per global network. These units permit the delaying of global

signals relative to other signals to assist in the control of input set-up times. Not all possible combinations of input and output modes can be used. The degrees of freedom available in the bidirectional global pad system and in the clock conditioning circuit have been restricted. This avoids unnecessary and unwieldy design kit and software work.

#### Notes:

- 1. FBDLY is a programmable delay line from 0 to 4 ns in 250 ps increments.

- 2. DLYA and DLYB are programmable delay lines, each with selectable values 0 ps, 250 ps, 500 ps, and 4 ns.

- 3. OBDIV will also divide the phase-shift since it takes place after the PLL Core.

Figure 1-14 • PLL Block – Top-Level View and Detailed PLL Block Diagram

1-14 v5.8

**Note:** When a signal from an I/O tile is connected to the core, it cannot be connected to the Global MUX at the same time. Figure 1-15 • Input Connectors to ProASIC PLUS Clock Conditioning Circuitry

Table 1-7 • Clock-Conditioning Circuitry MUX Settings

| MUX     | Datapath                                           | Comments                             |

|---------|----------------------------------------------------|--------------------------------------|

| FBSEL   |                                                    |                                      |

| 1       | Internal Feedback                                  |                                      |

| 2       | Internal Feedback and Advance Clock Using FBDLY    | −0.25 to −4 ns in 0.25 ns increments |

| 3       | External Feedback (EXTFB)                          |                                      |

| XDLYSEL | <u> </u>                                           |                                      |

| 0       | Feedback Unchanged                                 |                                      |

| 1       | Deskew feedback by advancing clock by system delay | Fixed delay of -2.95 ns              |

| OBMUX   | GLB                                                |                                      |

| 0       | Primary bypass, no divider                         |                                      |

| 1       | Primary bypass, use divider                        |                                      |

| 2       | Delay Clock Using FBDLY                            | +0.25 to +4 ns in 0.25 ns increments |

| 4       | Phase Shift Clock by 0°                            |                                      |

| 5       | Reserved                                           |                                      |

| 6       | Phase Shift Clock by +180°                         |                                      |

| 7       | Reserved                                           |                                      |

| OAMUX   | GLA                                                |                                      |

| 0       | Secondary bypass, no divider                       |                                      |

| 1       | Secondary bypass, use divider                      |                                      |

| 2       | Delay Clock Using FBDLY                            | +0.25 to +4 ns in 0.25 ns increments |

| 3       | Phase Shift Clock by 0°                            |                                      |

Figure 1-16 • Using the PLL 33 MHz In, 133 MHz Out

Figure 1-17 • Using the PLL 40 MHz In, 50 MHz Out

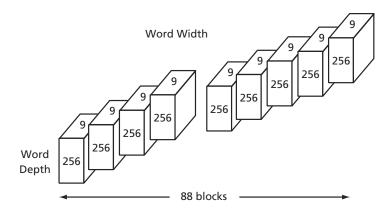

Table 1-12 ◆ ProASICPLUS Memory Configurations by Device

|         |        |     | Maximum Width |     | Maximu | m Depth |

|---------|--------|-----|---------------|-----|--------|---------|

| Device  | Bottom | Тор | D             | W   | D      | W       |

| APA750  | 32     | 32  | 256           | 288 | 4,096  | 9       |

| APA1000 | 44     | 44  | 256           | 396 | 5,632  | 9       |

*Table 1-13* • Basic Memory Configurations

| Туре | Write Access | Read Access             | Parity    | Library Cell Name |

|------|--------------|-------------------------|-----------|-------------------|

| RAM  | Asynchronous | Asynchronous            | Checked   | RAM256x9AA        |

| RAM  | Asynchronous | Asynchronous            | Generated | RAM256x9AAP       |

| RAM  | Asynchronous | Synchronous Transparent | Checked   | RAM256x9AST       |

| RAM  | Asynchronous | Synchronous Transparent | Generated | RAM256x9ASTP      |

| RAM  | Asynchronous | Synchronous Pipelined   | Checked   | RAM256x9ASR       |

| RAM  | Asynchronous | Synchronous Pipelined   | Generated | RAM256x9ASRP      |

| RAM  | Synchronous  | Asynchronous            | Checked   | RAM256x9SA        |

| RAM  | Synchronous  | Asynchronous            | Generated | RAM256xSAP        |

| RAM  | Synchronous  | Synchronous Transparent | Checked   | RAM256x9SST       |

| RAM  | Synchronous  | Synchronous Transparent | Generated | RAM256x9SSTP      |

| RAM  | Synchronous  | Synchronous Pipelined   | Checked   | RAM256x9SSR       |

| RAM  | Synchronous  | Synchronous Pipelined   | Generated | RAM256x9SSRP      |

| FIFO | Asynchronous | Asynchronous            | Checked   | FIFO256x9AA       |

| FIFO | Asynchronous | Asynchronous            | Generated | FIFO256x9AAP      |

| FIFO | Asynchronous | Synchronous Transparent | Checked   | FIFO256x9AST      |

| FIFO | Asynchronous | Synchronous Transparent | Generated | FIFO256x9ASTP     |

| FIFO | Asynchronous | Synchronous Pipelined   | Checked   | FIFO256x9ASR      |

| FIFO | Asynchronous | Synchronous Pipelined   | Generated | FIFO256x9ASRP     |

| FIFO | Synchronous  | Asynchronous            | Checked   | FIFO256x9SA       |

| FIFO | Synchronous  | Asynchronous            | Generated | FIFO256x9SAP      |

| FIFO | Synchronous  | Synchronous Transparent | Checked   | FIFO256x9SST      |

| FIFO | Synchronous  | Synchronous Transparent | Generated | FIFO256x9SSTP     |

| FIFO | Synchronous  | Synchronous Pipelined   | Checked   | FIFO256x9SSR      |

| FIFO | Synchronous  | Synchronous Pipelined   | Generated | FIFO256x9SSRP     |

1-24 v5.8

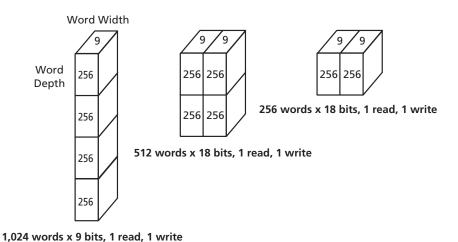

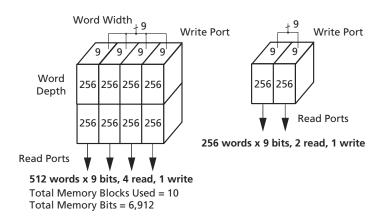

Figure 1-23 • APA1000 Memory Block Architecture

Total Memory Blocks Used = 10 Total Memory Bits = 23,040

Figure 1-24 • Example Showing Memory Arrays with Different Widths and Depths

Figure 1-25 • Multi-Port Memory Usage

# **Package Thermal Characteristics**

The ProASICPLUS family is available in several package types with a range of pin counts. Actel has selected packages based on high pin count, reliability factors, and superior thermal characteristics.

Thermal resistance defines the ability of a package to conduct heat away from the silicon, through the package to the surrounding air. Junction-to-ambient thermal resistance is measured in degrees Celsius/Watt and is represented as Theta ja  $(\Theta_{ja})$ . The lower the thermal resistance, the more efficiently a package will dissipate heat.

A package's maximum allowed power (P) is a function of maximum junction temperature  $(T_J)$ , maximum ambient operating temperature  $(T_A)$ , and junction-to-ambient thermal resistance  $\Theta_{ia}$ . Maximum junction temperature is

the maximum allowable temperature on the active surface of the IC and is 110° C. P is defined as:

$$P = \frac{T_J - T_A}{\Theta_{ja}}$$

EQ 1-4

$\Theta_{ja}$  is a function of the rate (in linear feet per minute (lfpm)) of airflow in contact with the package. When the estimated power consumption exceeds the maximum allowed power, other means of cooling, such as increasing the airflow rate, must be used. The maximum power dissipation allowed for a Military temperature device is specified as a function of  $\Theta_{jc}$ . The absolute maximum junction temperature is 150°C.

The calculation of the absolute maximum power dissipation allowed for a Military temperature application is illustrated in the following example for a 456-pin PBGA package:

$$\text{Maximum Power Allowed } = \frac{\text{Max. junction temp. (°C)} - \text{Max. case temp. (°C)}}{\theta_{jc}(°\text{C/W})} = \frac{150°\text{C} - 125°\text{C}}{3.0°\text{C/W}} = 8.333 \text{W}$$

EO 1-5

Table 1-16 • Package Thermal Characteristics

| Plastic Packages                               | Pin Count | $\theta_{ m jc}$ | Still Air | 1.0 m/s<br>200 ft./min. | 2.5 m/s<br>500 ft./min. | Units |

|------------------------------------------------|-----------|------------------|-----------|-------------------------|-------------------------|-------|

| Thin Quad Flat Pack (TQFP)                     | 100       | 14.0             | 33.5      | 27.4                    | 25.0                    | °C/W  |

| Thin Quad Flat Pack (TQFP)                     | 144       | 11.0             | 33.5      | 28.0                    | 25.7                    | °C/W  |

| Plastic Quad Flat Pack (PQFP) <sup>1</sup>     | 208       | 8.0              | 26.1      | 22.5                    | 20.8                    | °C/W  |

| PQFP with Heat spreader <sup>2</sup>           | 208       | 3.8              | 16.2      | 13.3                    | 11.9                    | °C/W  |

| Plastic Ball Grid Array (PBGA)                 | 456       | 3.0              | 15.6      | 12.5                    | 11.6                    | °C/W  |

| Fine Pitch Ball Grid Array (FBGA)              | 144       | 3.8              | 26.9      | 22.9                    | 21.5                    | °C/W  |

| Fine Pitch Ball Grid Array (FBGA)              | 256       | 3.8              | 26.6      | 22.8                    | 21.5                    | °C/W  |

| Fine Pitch Ball Grid Array (FBGA) <sup>3</sup> | 484       | 3.2              | 18.0      | 14.7                    | 13.6                    | °C/W  |

| Fine Pitch Ball Grid Array (FBGA) <sup>4</sup> | 484       | 3.2              | 20.5      | 17.0                    | 15.9                    | °C/W  |

| Fine Pitch Ball Grid Array (FBGA)              | 676       | 3.2              | 16.4      | 13.0                    | 12.0                    | °C/W  |

| Fine Pitch Ball Grid Array (FBGA)              | 896       | 2.4              | 13.6      | 10.4                    | 9.4                     | °C/W  |

| Fine Pitch Ball Grid Array (FBGA)              | 1152      | 1.8              | 12.0      | 8.9                     | 7.9                     | °C/W  |

| Ceramic Quad Flat Pack (CQFP)                  | 208       | 2.0              | 22.0      | 19.8                    | 18.0                    | °C/W  |

| Ceramic Quad Flat Pack (CQFP)                  | 352       | 2.0              | 17.9      | 16.1                    | 14.7                    | °C/W  |

| Ceramic Column Grid Array (CCGA/LGA)           | 624       | 6.5              | 8.9       | 8.5                     | 8.0                     | °C/W  |

#### Notes:

- 1. Valid for the following devices irrespective of temperature grade: APA075, APA150, and APA300

- 2. Valid for the following devices irrespective of temperature grade: APA450, APA600, APA750, and APA1000

- 3. Depopulated Array

- 4. Full array

1-30 v5.8

Table 1-22 • DC Electrical Specifications ( $V_{DDP}$  = 2.5 V  $\pm$ 0.2V) (Continued)

|                  |                                                                                  |                                       |              | Commercial/Industrial/<br>Military/MIL-STD-883 <sup>1, 2</sup> |           |       |  |  |

|------------------|----------------------------------------------------------------------------------|---------------------------------------|--------------|----------------------------------------------------------------|-----------|-------|--|--|

| Symbol           | Parameter                                                                        | Conditions                            | Min.         | Тур.                                                           | Max.      | Units |  |  |

| I <sub>OSH</sub> | Output Short Circuit Current High<br>High Drive (OB25LPH)<br>Low Drive (OB25LPL) | $V_{IN} = V_{SS}$ $V_{IN} = V_{SS}$   | -120<br>-100 |                                                                |           | mA    |  |  |

| I <sub>OSL</sub> | Output Short Circuit Current Low<br>High Drive (OB25LPH)<br>Low Drive (OB25LPL)  | $V_{IN} = V_{DDP}$ $V_{IN} = V_{DDP}$ |              |                                                                | 100<br>30 | mA    |  |  |

| C <sub>I/O</sub> | I/O Pad Capacitance                                                              |                                       |              |                                                                | 10        | pF    |  |  |

| C <sub>CLK</sub> | Clock Input Pad Capacitance                                                      |                                       |              |                                                                | 10        | pF    |  |  |

#### Notes:

- 1. All process conditions. Commercial/Industrial: Junction Temperature: -40 to +110°C.

- 2. All process conditions. Military: Junction Temperature: -55 to +150°C.

- 3. All –F parts are available only as commercial.

- 4. No pull-up resistor.

- 5. This will not exceed 2 mA total per device.

- 6. During transitions, the input signal may overshoot to  $V_{DDP}$  +1.0V for a limited time of no larger than 10% of the duty cycle.

- 7. During transitions, the input signal may undershoot to -1.0V for a limited time of no larger than 10% of the duty cycle.

1-38 v5.8

Table 1-23 • DC Electrical Specifications ( $V_{DDP}$  = 3.3 V  $\pm$ 0.3 V and  $V_{DD}$  = 2.5 V  $\pm$ 0.2 V) Applies to Commercial and Industrial Temperature Only

|                              |                                                                                       |                                                                                                                                                               |                 | Comme                       | rcial/In | dustrial <sup>1</sup>                                                      |    |

|------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------|----------|----------------------------------------------------------------------------|----|

| Symbol                       | Parameter                                                                             | Conditions                                                                                                                                                    | Min.            | Тур.                        | Max.     | Units                                                                      |    |

| V <sub>OH</sub>              | Output High Voltage<br>3.3 V I/O, High Drive (OB33P)                                  | I <sub>OH</sub> = -14 mA<br>I <sub>OH</sub> = -24 mA                                                                                                          |                 | 0.9*V <sub>DDP</sub><br>2.4 |          |                                                                            | V  |

|                              | 3.3 V I/O, Low Drive (OB33L)                                                          | $I_{OH} = -6 \text{ mA}$<br>$I_{OH} = -12 \text{ mA}$                                                                                                         |                 | 0.9*V <sub>DDP</sub><br>2.4 |          |                                                                            | ,  |

| V <sub>OL</sub>              | Output Low Voltage<br>3.3 V I/O, High Drive (OB33P)<br>3.3 V I/O, Low Drive (OB33L)   | I <sub>OL</sub> = 15 mA<br>I <sub>OL</sub> = 20 mA<br>I <sub>OL</sub> = 28 mA<br>I <sub>OL</sub> = 7 mA<br>I <sub>OL</sub> = 10 mA<br>I <sub>OL</sub> = 15 mA |                 |                             |          | 0.1V <sub>DDP</sub><br>0.4<br>0.7<br>0.1V <sub>DDP</sub><br>0.4<br>0.7     | V  |

| V <sub>IH</sub> <sup>5</sup> | Input High Voltage 3.3 V Schmitt Trigger Inputs 3.3 V LVTTL/LVCMOS 2.5 V Mode         | 10L = 13 IIIA                                                                                                                                                 |                 | 1.6<br>2<br>1.7             |          | V <sub>DDP</sub> + 0.3<br>V <sub>DDP</sub> + 0.3<br>V <sub>DDP</sub> + 0.3 | V  |

| V <sub>IL</sub> <sup>6</sup> | Input Low Voltage<br>3.3 V Schmitt Trigger Inputs<br>3.3 V LVTTL/LVCMOS<br>2.5 V Mode |                                                                                                                                                               |                 | -0.3<br>-0.3<br>-0.3        |          | 0.8<br>0.8<br>0.7                                                          | V  |

| R <sub>WEAKPULLUP</sub>      | Weak Pull-up Resistance<br>(IOB33U)                                                   | V <sub>IN</sub> ≥ 1.5 V                                                                                                                                       |                 | 7                           |          | 43                                                                         | kΩ |

| R <sub>WEAKPULLUP</sub>      | Weak Pull-up Resistance<br>(IOB25U)                                                   | V <sub>IN</sub> ≥ 1.5 V                                                                                                                                       |                 | 7                           |          | 43                                                                         | kΩ |

| I <sub>IN</sub>              | Input Current                                                                         | with pull up ( $V_{IN} = GND$ )                                                                                                                               |                 | -300                        |          | -40                                                                        | μΑ |

|                              |                                                                                       | without pull up ( $V_{IN} = GND \text{ or } V_{DD}$ )                                                                                                         |                 | -10                         |          | 10                                                                         | μΑ |

| I <sub>DDQ</sub>             | Quiescent Supply Current                                                              | $V_{IN} = GND^3$ or $V_{DD}$                                                                                                                                  | Std.            |                             | 5.0      | 15                                                                         | mA |

|                              | (standby)<br>Commercial                                                               |                                                                                                                                                               | -F <sup>2</sup> |                             | 5.0      | 25                                                                         | mA |

| I <sub>DDQ</sub>             | Quiescent Supply Current<br>(standby)<br>Industrial                                   | $V_{IN} = GND^3$ or $V_{DD}$                                                                                                                                  | Std.            |                             | 5.0      | 20                                                                         | mA |

| I <sub>DDQ</sub>             | Quiescent Supply Current<br>(standby)<br>Military                                     | $V_{IN} = GND^3$ or $V_{DD}$                                                                                                                                  | Std.            |                             | 5.0      | 25                                                                         | mA |

#### Notes:

- 1. All process conditions. Commercial/Industrial: Junction Temperature: -40 to +110°C.

- 2. All –F parts are only available as commercial.

- 3. No pull-up resistor required.

- 4. This will not exceed 2 mA total per device.

- 5. During transitions, the input signal may overshoot to  $V_{DDP}$  +1.0 V for a limited time of no larger than 10% of the duty cycle.

- 6. During transitions, the input signal may undershoot to -1.0 V for a limited time of no larger than 10% of the duty cycle.

Table 1-23 • DC Electrical Specifications ( $V_{DDP}$  = 3.3 V  $\pm$ 0.3 V and  $V_{DD}$  = 2.5 V  $\pm$ 0.2 V) (Continued) Applies to Commercial and Industrial Temperature Only

|                  |                                                                                             |                                     |                     | Comme        | rcial/In | dustrial <sup>1</sup> |       |

|------------------|---------------------------------------------------------------------------------------------|-------------------------------------|---------------------|--------------|----------|-----------------------|-------|

| Symbol           | Parameter                                                                                   | Conditions                          |                     | Min.         | Тур.     | Max.                  | Units |

| I <sub>OZ</sub>  | · · · · · · · · · · · · · · · · · · ·                                                       | $V_{OH} = GND \text{ or } V_{DD}$   | Std.                | -10          |          | 10                    | μΑ    |

|                  | Current                                                                                     |                                     | -F <sup>2</sup> , 4 | -10          |          | 100                   | μΑ    |

| l <sub>OSH</sub> | Output Short Circuit Current<br>High<br>3.3 V High Drive (OB33P)<br>3.3 V Low Drive (OB33L) | $V_{IN} = GND$<br>$V_{IN} = GND$    |                     | -200<br>-100 |          |                       |       |

| I <sub>OSL</sub> | Output Short Circuit Current<br>Low<br>3.3 V High Drive<br>3.3 V Low Drive                  | $V_{IN} = V_{DD}$ $V_{IN} = V_{DD}$ |                     |              |          | 200<br>100            |       |

| C <sub>I/O</sub> | I/O Pad Capacitance                                                                         |                                     |                     |              |          | 10                    | pF    |

| C <sub>CLK</sub> | Clock Input Pad Capacitance                                                                 |                                     |                     |              |          | 10                    | pF    |

#### Notes:

- 1. All process conditions. Commercial/Industrial: Junction Temperature: -40 to +110°C.

- 2. All –F parts are only available as commercial.

- 3. No pull-up resistor required.

- 4. This will not exceed 2 mA total per device.

- 5. During transitions, the input signal may overshoot to  $V_{DDP}$  +1.0 V for a limited time of no larger than 10% of the duty cycle.

- 6. During transitions, the input signal may undershoot to -1.0 V for a limited time of no larger than 10% of the duty cycle.

1-40 v5.8

Table 1-24 • DC Electrical Specifications ( $V_{DDP}$  = 3.3 V  $\pm$ 0.3 V and  $V_{DD}$  = 2.5 V  $\pm$ 0.2 V) (Continued) Applies to Military Temperature and MIL-STD-883B Temperature Only

|                  |                                                                                             |                                     |                 |              |      | Military/MIL-STD-883B <sup>1</sup> |       |  |  |

|------------------|---------------------------------------------------------------------------------------------|-------------------------------------|-----------------|--------------|------|------------------------------------|-------|--|--|

| Symbol           | Parameter                                                                                   | Conditions                          |                 | Min.         | Тур. | Мах.                               | Units |  |  |

| I <sub>DDQ</sub> | Quiescent Supply Current<br>(standby)<br>Industrial                                         | $V_{IN} = GND^2 \text{ or } V_{DD}$ | Std.            |              | 5.0  | 20                                 | mA    |  |  |

| I <sub>DDQ</sub> | Quiescent Supply Current<br>(standby)<br>Military                                           | $V_{IN} = GND^2 \text{ or } V_{DD}$ | Std.            |              | 5.0  | 25                                 | mA    |  |  |

| I <sub>OZ</sub>  |                                                                                             | $V_{OH} = GND \text{ or } V_{DD}$   | Std.            | -10          |      | 10                                 | μΑ    |  |  |

|                  | Current                                                                                     |                                     | -F <sup>3</sup> | -10          |      | 100                                | μΑ    |  |  |

| I <sub>OSH</sub> | Output Short Circuit Current<br>High<br>3.3 V High Drive (OB33P)<br>3.3 V Low Drive (OB33L) | $V_{IN} = GND$<br>$V_{IN} = GND$    |                 | -200<br>-100 |      |                                    |       |  |  |

| I <sub>OSL</sub> | Output Short Circuit Current<br>Low<br>3.3 V High Drive<br>3.3 V Low Drive                  | $V_{IN} = V_{DD}$ $V_{IN} = V_{DD}$ |                 |              |      | 200<br>100                         |       |  |  |

| C <sub>I/O</sub> | I/O Pad Capacitance                                                                         |                                     |                 |              |      | 10                                 | рF    |  |  |

| C <sub>CLK</sub> | Clock Input Pad Capacitance                                                                 |                                     |                 |              |      | 10                                 | pF    |  |  |

#### Notes:

- 1. All process conditions. Military Temperature / MIL-STD-883 Class B: Junction Temperature: -55 to +125°C.

- 2. No pull-up resistor required.

- 3. This will not exceed 2 mA total per device.

- 4. During transitions, the input signal may overshoot to  $V_{DDP}$  +1.0 V for a limited time of no larger than 10% of the duty cycle.

- 5. During transitions, the input signal may undershoot to -1.0 V for a limited time of no larger than 10% of the duty cycle.

1-42 v5.8

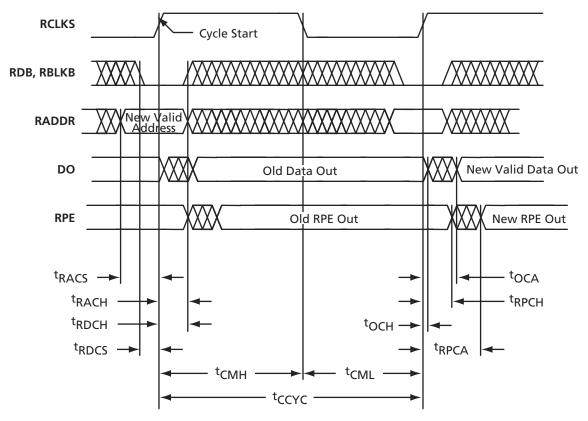

### **Synchronous SRAM Read, Pipeline Mode Outputs (Synchronous Pipelined)**

**Note:** The plot shows the normal operation status.

Figure 1-32 • Synchronous SRAM Read, Pipeline Mode Outputs (Synchronous Pipelined)

Table 1-53 •  $T_J = 0$ °C to 110°C;  $V_{DD} = 2.3$  V to 2.7 V for Commercial/industrial  $T_J = 0$ °C to 150°C,  $V_{DD} = 2.3$  V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                 | Min. | Max. | Units | Notes |

|-------------------------|-----------------------------|------|------|-------|-------|

| CCYC                    | Cycle time                  | 7.5  |      | ns    |       |

| CMH                     | Clock high phase            | 3.0  |      | ns    |       |

| CML                     | Clock low phase             | 3.0  |      | ns    |       |

| OCA                     | New DO access from RCLKS ↑  | 2.0  |      | ns    |       |

| ОСН                     | Old DO valid from RCLKS ↑   |      | 0.75 | ns    |       |

| RACH                    | RADDR hold from RCLKS ↑     | 0.5  |      | ns    |       |

| RACS                    | RADDR setup to RCLKS ↑      | 1.0  |      | ns    |       |

| RDCH                    | RDB hold from RCLKS ↑       | 0.5  |      | ns    |       |

| RDCS                    | RDB setup to RCLKS ↑        | 1.0  |      | ns    |       |

| RPCA                    | New RPE access from RCLKS ↑ | 4.0  |      | ns    |       |

| RPCH                    | Old RPE valid from RCLKS ↑  |      | 1.0  | ns    |       |

**Note:** All –F speed grade devices are 20% slower than the standard numbers.

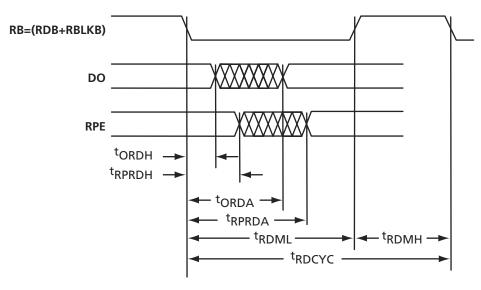

### **Asynchronous SRAM Read, RDB Controlled**

**Note:** The plot shows the normal operation status.

Figure 1-35 • Asynchronous SRAM Read, RDB Controlled

Table 1-56 •  $T_J = 0$ °C to 110°C;  $V_{DD} = 2.3$  V to 2.7 V for Commercial/industrial  $T_J = -55$ °C to 150°C,  $V_{DD} = 2.3$  V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description              | Min. | Max. | Units | Notes                       |

|-------------------------|--------------------------|------|------|-------|-----------------------------|

| ORDA                    | New DO access from RB ↓  | 7.5  |      | ns    |                             |

| ORDH                    | Old DO valid from RB ↓   |      | 3.0  | ns    |                             |

| RDCYC                   | Read cycle time          | 7.5  |      | ns    |                             |

| RDMH                    | RB high phase            | 3.0  |      | ns    | Inactive setup to new cycle |

| RDML                    | RB low phase             | 3.0  |      | ns    | Active                      |

| RPRDA                   | New RPE access from RB ↓ | 9.5  |      | ns    |                             |

| RPRDH                   | Old RPE valid from RB ↓  |      | 3.0  | ns    |                             |

Note: All –F speed grade devices are 20% slower than the standard numbers.

1-62 v5.8

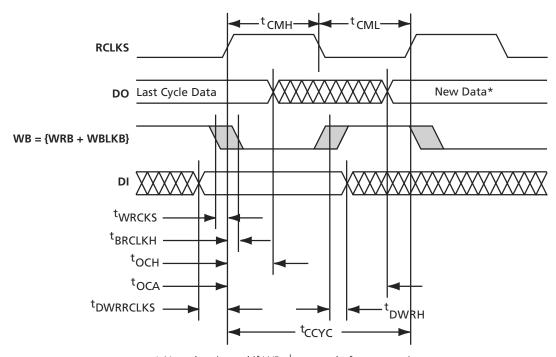

### **Asynchronous Write and Synchronous Read to the Same Location**

\* New data is read if WB ↓ occurs before setup time.

The stored data is read if WB ↓ occurs after hold time.

**Note:** The plot shows the normal operation status.

Figure 1-38 • Asynchronous Write and Synchronous Read to the Same Location

Table 1-59 •  $T_J = 0$ °C to 110°C;  $V_{DD} = 2.3$  V to 2.7 V for Commercial/industrial  $T_J = -55$ °C to 150°C,  $V_{DD} = 2.3$  V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                | Min. Max. |     | Units | Notes                 |  |

|-------------------------|----------------------------|-----------|-----|-------|-----------------------|--|

| CCYC                    | Cycle time                 | 7.5       |     | ns    |                       |  |

| CMH                     | Clock high phase           | 3.0       |     | ns    |                       |  |

| CML                     | Clock low phase            | 3.0       |     | ns    |                       |  |

| WBRCLKS                 | WB ↓ to RCLKS ↑ setup time | -0.1      |     | ns    |                       |  |

| WBRCLKH                 | WB ↓ to RCLKS ↑ hold time  |           | 7.0 | ns    |                       |  |

| ОСН                     | Old DO valid from RCLKS ↑  |           | 3.0 | ns    | OCA/OCH displayed for |  |

| OCA                     | New DO valid from RCLKS ↑  | 7.5       |     | ns    | Access Timed Output   |  |

| DWRRCLKS                | DI to RCLKS ↑ setup time   | 0         |     | ns    |                       |  |

| DWRH                    | DI to WB ↑ hold time       |           | 1.5 | ns    |                       |  |

#### Notes:

- 1. This behavior is valid for Access Timed Output and Pipelined Mode Output. The table shows the timings of an Access Timed Output.

- 2. In asynchronous write and synchronous read access to the same location, the new write data will be read out if the active write signal edge occurs before or at the same time as the active read clock edge. If WB changes to low after hold time, the data will be read.

- 3. A setup or hold time violation will result in unknown output data.

- 4. All -F speed grade devices are 20% slower than the standard numbers.

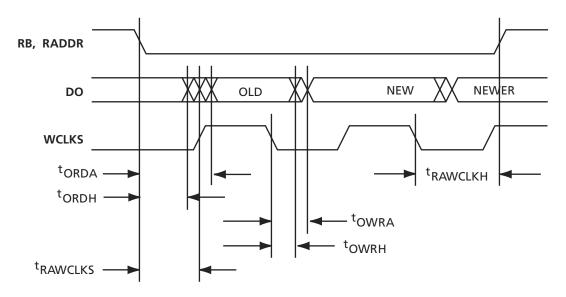

### Synchronous Write and Asynchronous Read to the Same Location

**Note:** The plot shows the normal operation status.

Figure 1-40 • Synchronous Write and Asynchronous Read to the Same Location

Table 1-61 •  $T_J = 0$ °C to 110°C;  $V_{DD} = 2.3$  V to 2.7 V for Commercial/industrial  $T_J = -55$ °C to 150°C,  $V_{DD} = 2.3$  V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                | Min. | Max. | Units | Notes |

|-------------------------|----------------------------|------|------|-------|-------|

| ORDA                    | New DO access from RB ↓    | 7.5  |      | ns    |       |

| ORDH                    | Old DO valid from RB ↓     |      | 3.0  | ns    |       |

| OWRA                    | New DO access from WCLKS ↓ | 3.0  |      | ns    |       |

| OWRH                    | Old DO valid from WCLKS ↓  |      | 0.5  | ns    |       |

| RAWCLKS                 | RB ↓ or RADDR from WCLKS ↑ | 5.0  |      | ns    |       |

| RAWCLKH                 | RB ↑ or RADDR from WCLKS ↓ | 5.0  |      | ns    |       |

#### Notes:

- 1. During an asynchronous read cycle, each write operation (synchronous or asynchronous) to the same location will automatically trigger a read operation which updates the read data.

- 2. Violation of RAWCLKS will disturb access to OLD data.

- 3. Violation of RAWCLKH will disturb access to NEWER data.

- 4. All -F speed grade devices are 20% slower than the standard numbers.

### **Asynchronous FIFO Full and Empty Transitions**

The asynchronous FIFO accepts writes and reads while not full or not empty. When the FIFO is full, all writes are inhibited. Conversely, when the FIFO is empty, all reads are inhibited. A problem is created if the FIFO is written to during the transition from full to not full, or read during the transition from empty to not empty. The exact time at which the write or read operation changes from inhibited to accepted after the read (write) signal which causes the transition from full or empty to not full or not empty is indeterminate. For slow cycles, this indeterminate period starts 1 ns after the RB (WB) transition, which deactivates full or not empty and ends 3 ns after the RB (WB) transition. For fast cycles, the indeterminate period ends 3 ns (7.5 ns – RDL (WRL)) after the RB (WB) transition, whichever is later (Table 1-1 on page 1-7).

The timing diagram for write is shown in Figure 1-38 on page 1-65. The timing diagram for read is shown in Figure 1-39 on page 1-66. For basic SRAM configurations, see Table 1-14 on page 1-25. When reset is asserted, the

empty flag will be asserted, the counters will reset, the outputs go to zero, but the internal RAM is not erased.

#### **Enclosed Timing Diagrams – FIFO Mode:**

The following timing diagrams apply only to single cell; they are not applicable to cascaded cells. For more information, refer to the *ProASIC*<sup>PLUS</sup> *RAMIFIFO Blocks* application note.

- "Asynchronous FIFO Read" section on page 1-70

- "Asynchronous FIFO Write" section on page 1-71

- "Synchronous FIFO Read, Access Timed Output Strobe (Synchronous Transparent)" section on page 1-72

- "Synchronous FIFO Read, Pipeline Mode Outputs (Synchronous Pipelined)" section on page 1-73

- "Synchronous FIFO Write" section on page 1-74

- "FIFO Reset" section on page 1-75

Table 1-62 • Memory Block FIFO Interface Signals

| FIFO Signal  | Bits | In/Out | Description                                                                                                                                 |

|--------------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|

| WCLKS        | 1    | In     | Write clock used for synchronization on write side                                                                                          |

| RCLKS        | 1    | In     | Read clock used for synchronization on read side                                                                                            |

| LEVEL <0:7>* | 8    | In     | Direct configuration implements static flag logic                                                                                           |

| RBLKB        | 1    | In     | Read block select (active Low)                                                                                                              |

| RDB          | 1    | In     | Read pulse (active Low)                                                                                                                     |

| RESET        | 1    | In     | Reset for FIFO pointers (active Low)                                                                                                        |

| WBLKB        | 1    | In     | Write block select (active Low)                                                                                                             |

| DI<0:8>      | 9    | In     | Input data bits <0:8>, <8> will be generated if PARGEN is true                                                                              |

| WRB          | 1    | In     | Write pulse (active Low)                                                                                                                    |

| FULL, EMPTY  | 2    | Out    | FIFO flags. FULL prevents write and EMPTY prevents read                                                                                     |

| EQTH, GEQTH* | 2    | Out    | EQTH is true when the FIFO holds the number of words specified by the LEVEL signal. GEQTH is true when the FIFO holds (LEVEL) words or more |

| DO<0:8>      | 9    | Out    | Output data bits <0:8>                                                                                                                      |

| RPE          | 1    | Out    | Read parity error (active High)                                                                                                             |

| WPE          | 1    | Out    | Write parity error (active High)                                                                                                            |

| LGDEP <0:2>  | 3    | ln     | Configures DEPTH of the FIFO to 2 (LGDEP+1)                                                                                                 |

| PARODD       | 1    | ln     | Selects Odd parity generation/detect when high, Even when low                                                                               |

**Note:** \*LEVEL is always eight bits (0000.0000, 0000.0001). That means for values of DEPTH greater than 256, not all values will be possible, e.g. for DEPTH=512, the LEVEL can only have the values 2, 4, . . . , 512. The LEVEL signal circuit will generate signals that indicate whether the FIFO is exactly filled to the value of LEVEL (EQTH) or filled equal or higher (GEQTH) than the specified LEVEL. Since counting starts at 0, EQTH will become true when the FIFO holds (LEVEL+1) words for 512-bit FIFOs.

1-68 v5.8

### **Pin Description**

#### **User Pins**

#### I/O User Input/Output

The I/O pin functions as an input, output, tristate, or bidirectional buffer. Input and output signal levels are compatible with standard LVTTL and LVCMOS specifications. Unused I/O pins are configured as inputs with pull-up resistors.

#### NC No Connect

To maintain compatibility with other Actel ProASIC PLUS products, it is recommended that this pin not be connected to the circuitry on the board.

#### GL Global Pin

Low skew input pin for clock or other global signals. This pin can be configured with an internal pull-up resistor. When it is not connected to the global network or the clock conditioning circuit, it can be configured and used as a normal I/O.

#### GLMX Global Multiplexing Pin

Low skew input pin for clock or other global signals. This pin can be used in one of two special ways (refer to Actel's *Using ProASIC PLUS Clock Conditioning Circuits*).

When the external feedback option is selected for the PLL block, this pin is routed as the external feedback source to the clock conditioning circuit.

In applications where two different signals access the same global net at different times through the use of GLMXx and GLMXLx macros, this pin will be fixed as one of the source pins.

This pin can be configured with an internal pull-up resistor. When it is not connected to the global network or the clock conditioning circuit, it can be configured and used as any normal I/O. If not used, the GLMXx pin will be configured as an input with pull-up.

#### **Dedicated Pins**

#### GND Ground

Common ground supply voltage.

V<sub>DD</sub> Logic Array Power Supply Pin

2.5 V supply voltage.

V<sub>DDP</sub> I/O Pad Power Supply Pin

2.5 V or 3.3 V supply voltage.

#### TMS Test Mode Select

The TMS pin controls the use of boundary-scan circuitry. This pin has an internal pull-up resistor.

#### TCK Test Clock

Clock input pin for boundary scan (maximum 10 MHz). Actel recommends adding a nominal 20 k $\Omega$  pull-up resistor to this pin.

#### TDI Test Data In

Serial input for boundary scan. A dedicated pull-up resistor is included to pull this pin high when not being driven.

#### TDO Test Data Out

Serial output for boundary scan. Actel recommends adding a nominal  $20k\Omega$  pull-up resistor to this pin.

#### TRST Test Reset Input

Asynchronous, active-low input pin for resetting boundary-scan circuitry. This pin has an internal pull-up resistor. For more information, please refer to *Power-up Behavior of ProASICPLUS Devices* application note.

### **Special Function Pins**

#### RCK Running Clock

A free running clock is needed during programming if the programmer cannot guarantee that TCK will be uninterrupted. If not used, this pin has an internal pullup and can be left floating.

#### NPECL User Negative Input

Provides high speed clock or data signals to the PLL block. If unused, leave the pin unconnected.

#### PPECL User Positive Input

Provides high speed clock or data signals to the PLL block. If unused, leave the pin unconnected.

#### AVDD PLL Power Supply

Analog  $V_{DD}$  should be  $V_{DD}$  (core voltage) 2.5 V (nominal) and be decoupled from GND with suitable decoupling capacitors to reduce noise. For more information, refer to Actel's *Using ProASICPLUS Clock Conditioning Circuits* application note. If the clock conditioning circuitry is not used in a design, AVDD can either be left floating or tied to 2.5 V.

#### AGND PLL Power Ground

The analog ground can be connected to the system ground. For more information, refer to Actel's *Using ProASICPLUS Clock Conditioning Circuits* application note. If the PLLs or clock conditioning circuitry are not used in a design, AGND should be tied to GND.