Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                         |

|--------------------------------|-------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                |

| Number of LABs/CLBs            | -                                                                       |

| Number of Logic Elements/Cells | -                                                                       |

| Total RAM Bits                 | 129024                                                                  |

| Number of I/O                  | 158                                                                     |

| Number of Gates                | 600000                                                                  |

| Voltage - Supply               | 2.3V ~ 2.7V                                                             |

| Mounting Type                  | Surface Mount                                                           |

| Operating Temperature          | -55°C ~ 125°C (TC)                                                      |

| Package / Case                 | 208-BFQFP                                                               |

| Supplier Device Package        | 208-PQFP (28x28)                                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/apa600-pq208m |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

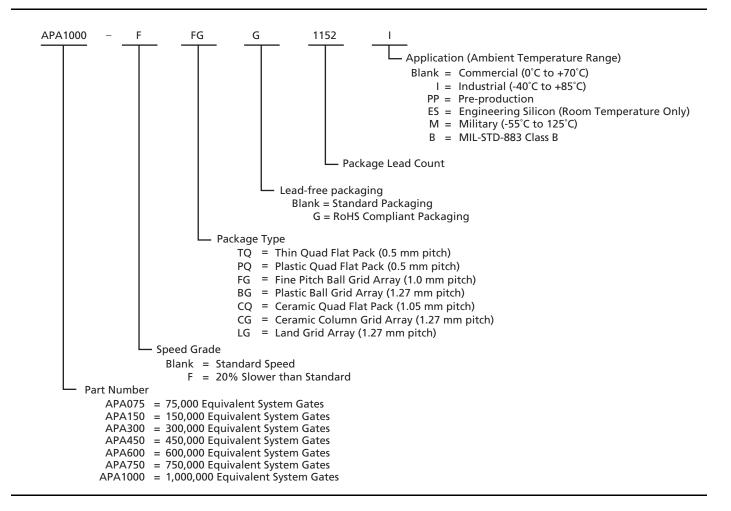

# **Ordering Information**

ii v5.8

# **Device Resources**

|         | User I/Os <sup>2</sup> |                 |                  |                  |                  |                     |                  |                 |                     |                  |                 |                 |                         |

|---------|------------------------|-----------------|------------------|------------------|------------------|---------------------|------------------|-----------------|---------------------|------------------|-----------------|-----------------|-------------------------|

|         | Commercial/Industrial  |                 |                  |                  |                  |                     |                  |                 | Milita              | ry/MIL-S1        | D-883B          |                 |                         |

| Device  | TQFP<br>100-Pin        | TQFP<br>144-Pin | PQFP<br>208-Pin  | PBGA<br>456-Pin  | FBGA<br>144-Pin  | FBGA<br>256-Pin     | FBGA<br>484-Pin  | FBGA<br>676-Pin | FBGA<br>896-Pin     | FBGA<br>1152-Pin | CQFP<br>208-Pin | CQFP<br>352-Pin | CCGA/<br>LGA<br>624-Pin |

| APA075  | 66                     | 107             | 158              |                  | 100              |                     |                  |                 |                     |                  |                 |                 |                         |

| APA150  | 66                     |                 | 158              | 242              | 100              | 186 <sup>3</sup>    |                  |                 |                     |                  |                 |                 |                         |

| APA300  |                        |                 | 158 <sup>4</sup> | 290 <sup>4</sup> | 100 <sup>4</sup> | 186 <sup>3, 4</sup> |                  |                 |                     |                  | 158             | 248             |                         |

| APA450  |                        |                 | 158              | 344              | 100              | 186 <sup>3</sup>    | 344 <sup>3</sup> |                 |                     |                  |                 |                 |                         |

| APA600  |                        |                 | 158 <sup>4</sup> | 356 <sup>4</sup> |                  | 186 <sup>3, 4</sup> | 370 <sup>3</sup> | 454             |                     |                  | 158             | 248             | 440                     |

| APA750  |                        |                 | 158              | 356              |                  |                     |                  | 454             | 562 <sup>5</sup>    |                  |                 |                 |                         |

| APA1000 |                        |                 | 158 <sup>4</sup> | 356 <sup>4</sup> |                  |                     |                  |                 | 642 <sup>4, 5</sup> | 712 <sup>5</sup> | 158             | 248             | 440                     |

#### Notes:

- 1. Package Definitions: TQFP = Thin Quad Flat Pack, PQFP = Plastic Quad Flat Pack, PBGA = Plastic Ball Grid Array, FBGA = Fine Pitch Ball Grid Array, CQFP = Ceramic Quad Flat Pack, CCGA = Ceramic Column Grid Array, LGA = Land Grid Array

- 2. Each pair of PECL I/Os is counted as one user I/O.

- 3. FG256 and FG484 are footprint-compatible packages.

- 4. Military Temperature Plastic Package Offering

- 5. FG896 and FG1152 are footprint-compatible packages.

# **General Guideline**

Maximum performance numbers in this datasheet are based on characterized data. Actel does not guarantee performance beyond the limits specified within the datasheet.

v5.8 iii

# **General Description**

The ProASIC PLUS family of devices, Actel's second-generation Flash FPGAs, offers enhanced performance over Actel's ProASIC family. It combines the advantages of ASICs with the benefits of programmable devices through nonvolatile Flash technology. This enables engineers to create high-density systems using existing ASIC or FPGA design flows and tools. In addition, the ProASIC family offers a unique clock conditioning circuit based on two on-board phase-locked loops (PLLs). The family offers up to one million system gates, supported with up to 198 kbits of two-port SRAM and up to 712 user I/Os, all providing 50 MHz PCI performance.

Advantages to the designer extend beyond performance. Unlike SRAM-based FPGAs, four levels of routing hierarchy simplify routing, while the use of Flash technology allows all functionality to be live at powerup. No external boot PROM is required to support device programming. While on-board security mechanisms prevent access to the program information. reprogramming can be performed in-system to support future design iterations and field upgrades. The device's architecture mitigates the complexity of ASIC migration at higher user volume. This makes ProASICPLUS a costeffective solution for applications in the networking, communications, computing, and avionics markets.

The ProASIC family achieves its nonvolatility and reprogrammability through an advanced Flash-based 0.22  $\mu m$  LVCMOS process with four layers of metal. Standard CMOS design techniques are used to implement logic and control functions, including the PLLs and LVPECL inputs. This results in predictable performance compatible with gate arrays.

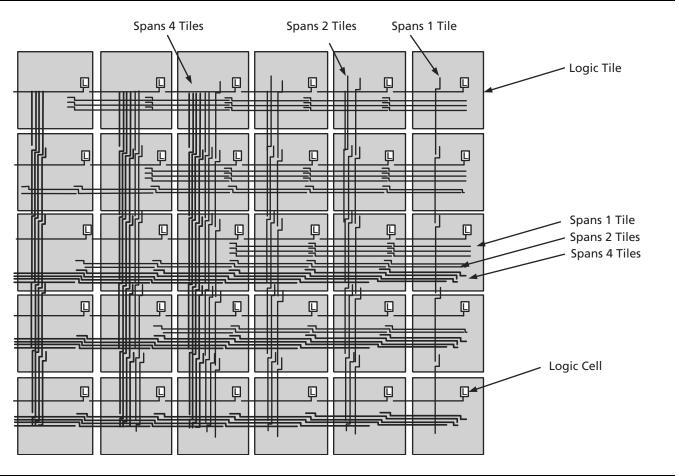

The ProASICPLUS architecture provides granularity comparable to gate arrays. The device core consists of a Sea-of-Tiles™. Each tile can be configured as a flip-flop, latch, or three-input/one-output logic function by programming the appropriate Flash switches. The

combination of fine granularity, flexible routing resources, and abundant Flash switches allow 100% utilization and over 95% routability for highly congested designs. Tiles and larger functions are interconnected through a four-level routing hierarchy.

Embedded two-port SRAM blocks with built-in FIFO/RAM control logic can have user-defined depths and widths. Users can also select programming for synchronous or asynchronous operation, as well as parity generations or checking.

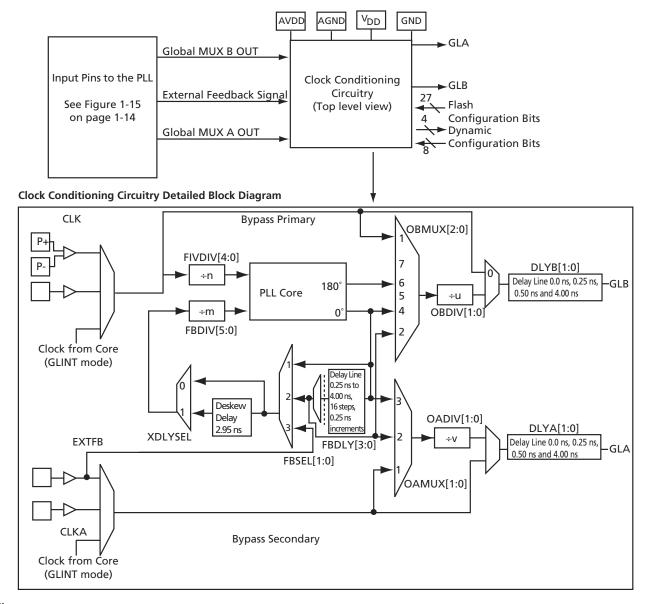

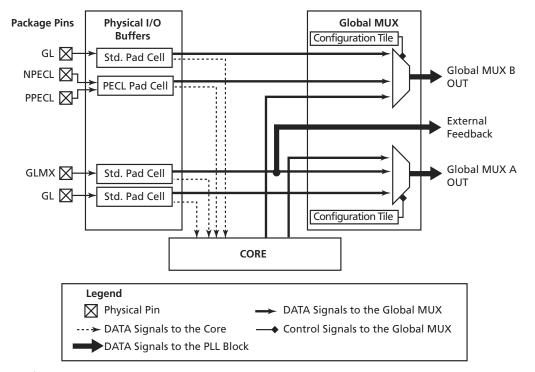

The unique clock conditioning circuitry in each device includes two clock conditioning blocks. Each block provides a PLL core, delay lines, phase shifts (0° and 180°), and clock multipliers/dividers, as well as the circuitry needed to provide bidirectional access to the PLL. The PLL block contains four programmable frequency dividers which allow the incoming clock signal to be divided by a wide range of factors from 1 to 64. The clock conditioning circuit also delays or advances the incoming reference clock up to 8 ns (in increments of 0.25 ns). The PLL can be configured internally or externally during operation without redesigning or reprogramming the part. In addition to the PLL, there are two LVPECL differential input pairs to accommodate high-speed clock and data inputs.

To support customer needs for more comprehensive, lower-cost, board-level testing, Actel's ProASICPLUS devices are fully compatible with IEEE Standard 1149.1 for test access port and boundary-scan test architecture. For more information concerning the Flash FPGA implementation, please refer to the "Boundary Scan (JTAG)" section on page 1-11.

ProASICPLUS devices are available in a variety of highperformance plastic packages. Those packages and the performance features discussed above are described in more detail in the following sections.

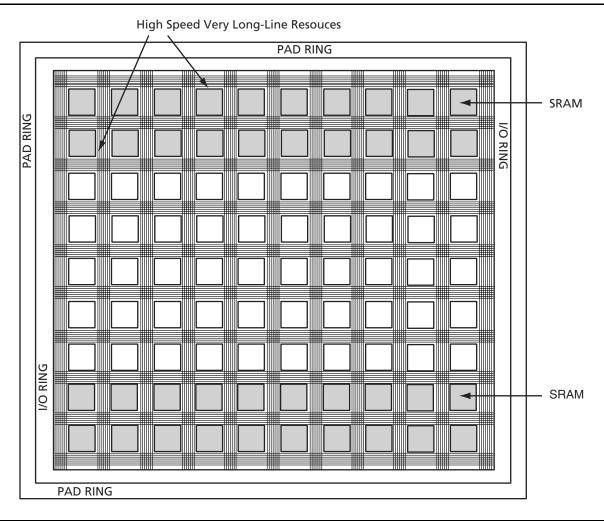

Figure 1-5 • Efficient Long-Line Resources

Figure 1-6 • High-Speed, Very Long-Line Resources

## **Clock Resources**

The ProASICPLUS family offers powerful and flexible control of circuit timing through the use of analog circuitry. Each chip has two clock conditioning blocks containing a phase-locked loop (PLL) core, delay lines, phase shifter (0° and 180°), clock multiplier/dividers, and all the circuitry needed for the selection and interconnection of inputs to the global network (thus providing bidirectional access to the PLL). This permits the PLL block to drive inputs and/or outputs via the two global lines on each side of the chip (four total lines). This circuitry is discussed in more detail in the "ProASICPLUS Clock Management System" section on page 1-13.

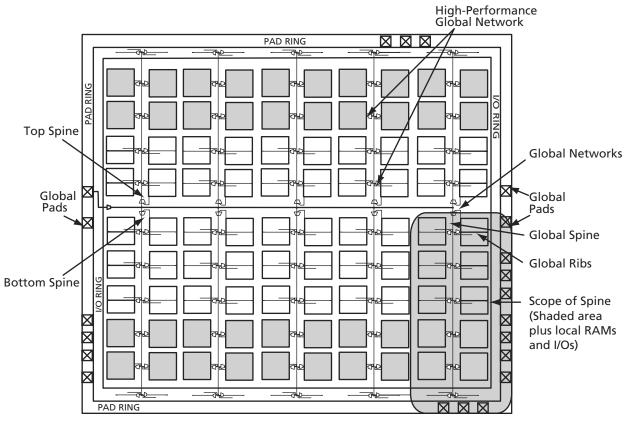

### **Clock Trees**

One of the main architectural benefits of ProASICPLUS is the set of power- and delay-friendly global networks. ProASICPLUS offers four global trees. Each of these trees is based on a network of spines and ribs that reach all the tiles in their regions (Figure 1-7 on page 1-7). This flexible clock tree architecture allows users to map up to 88 different internal/external clocks in an APA1000 device. Details on the clock spines and various numbers of the family are given in Table 1-1 on page 1-7.

The flexible use of the ProASICPLUS clock spine allows the designer to cope with several design requirements. Users implementing clock-resource intensive applications can easily route external or gated internal clocks using global routing spines. Users can also drastically reduce delay penalties and save buffering resources by mapping critical high fanout nets to spines. For design hints on using these features, refer to Actel's *Efficient Use of ProASIC Clock Trees* application note.

1-6 v5.8

**Note:** This figure shows routing for only one global path.

Figure 1-7 • High-Performance Global Network

*Table 1-1* ● Clock Spines

|                                    | APA075 | APA150 | APA300 | APA450 | APA600 | APA750 | APA1000 |

|------------------------------------|--------|--------|--------|--------|--------|--------|---------|

| Global Clock Networks (Trees)      | 4      | 4      | 4      | 4      | 4      | 4      | 4       |

| Clock Spines/Tree                  | 6      | 8      | 8      | 12     | 14     | 16     | 22      |

| Total Spines                       | 24     | 32     | 32     | 48     | 56     | 64     | 88      |

| Top or Bottom Spine Height (Tiles) | 16     | 24     | 32     | 32     | 48     | 64     | 80      |

| Tiles in Each Top or Bottom Spine  | 512    | 768    | 1,024  | 1,024  | 1,536  | 2,048  | 2,560   |

| Total Tiles                        | 3,072  | 6,144  | 8,192  | 12,288 | 21,504 | 32,768 | 56,320  |

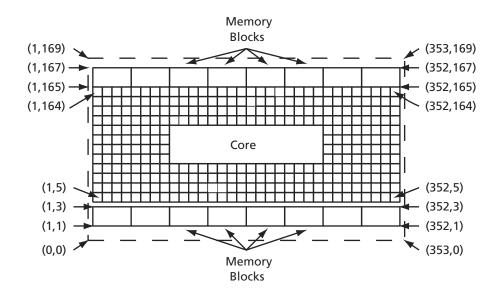

# **Array Coordinates**

During many place-and-route operations in Actel's Designer software tool, it is possible to set constraints that require array coordinates.

Table 1-2 is provided as a reference. The array coordinates are measured from the lower left (0,0). They can be used in region constraints for specific groups of core cells, I/Os, and RAM blocks. Wild cards are also allowed.

I/O and cell coordinates are used for placement constraints. Two coordinate systems are needed because there is not a one-to-one correspondence between I/O

cells and core cells. In addition, the I/O coordinate system changes depending on the die/package combination.

Core cell coordinates start at the lower left corner (represented as (1,1)) or at (1,5) if memory blocks are present at the bottom. Memory coordinates use the same system and are indicated in Table 1-2. The memory coordinates for an APA1000 are illustrated in Figure 1-8. For more information on how to use constraints, see the *Designer User's Guide* or online help for ProASICPLUS software tools.

*Table 1-2* ● Array Coordinates

|         |      | Lo | gic Tile |     | Me             | mory Rows               |      |          |  |

|---------|------|----|----------|-----|----------------|-------------------------|------|----------|--|

|         | Min. |    | Max.     |     | Bottom         | Тор                     | All  |          |  |

| Device  | х    | у  | х        | у   | У              | У                       | Min. | Мах.     |  |

| APA075  | 1    | 1  | 96       | 32  | _              | (33,33) or (33, 35)     | 0,0  | 97, 37   |  |

| APA150  | 1    | 1  | 128      | 48  | _              | (49,49) or (49, 51)     | 0,0  | 129, 53  |  |

| APA300  | 1    | 5  | 128      | 68  | (1,1) or (1,3) | (69,69) or (69, 71)     | 0,0  | 129, 73  |  |

| APA450  | 1    | 5  | 192      | 68  | (1,1) or (1,3) | (69,69) or (69, 71)     | 0,0  | 193, 73  |  |

| APA600  | 1    | 5  | 224      | 100 | (1,1) or (1,3) | (101,101) or (101, 103) | 0,0  | 225, 105 |  |

| APA750  | 1    | 5  | 256      | 132 | (1,1) or (1,3) | (133,133) or (133, 135) | 0,0  | 257, 137 |  |

| APA1000 | 1    | 5  | 352      | 164 | (1,1) or (1,3) | (165,165) or (165, 167) | 0,0  | 353, 169 |  |

Figure 1-8 • Core Cell Coordinates for the APA1000

1-8 v5.8

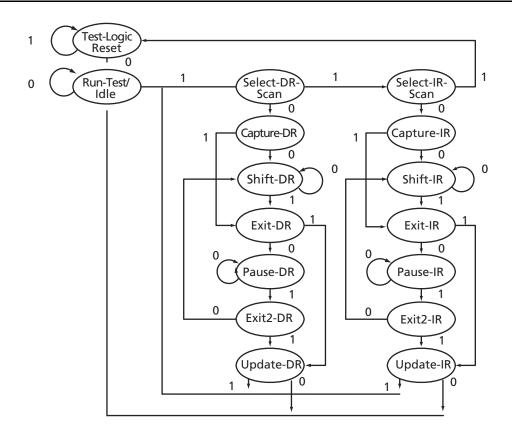

The TAP controller receives two control inputs (TMS and TCK) and generates control and clock signals for the rest of the test logic architecture. On power-up, the TAP controller enters the Test-Logic-Reset state. To guarantee a reset of the controller from any of the possible states, TMS must remain high for five TCK cycles. The TRST pin may also be used to asynchronously place the TAP controller in the Test-Logic-Reset state.

ProASICPLUS devices support three types of test data registers: bypass, device identification, and boundary scan. The bypass register is selected when no other register needs to be accessed in a device. This speeds up test data transfer to other devices in a test data path. The 32-bit device identification register is a shift register

with four fields (lowest significant byte (LSB), ID number, part number and version). The boundary-scan register observes and controls the state of each I/O pin.

Each I/O cell has three boundary-scan register cells, each with a serial-in, serial-out, parallel-in, and parallel-out pin. The serial pins are used to serially connect all the boundary-scan register cells in a device into a boundary-scan register chain, which starts at the TDI pin and ends at the TDO pin. The parallel ports are connected to the internal core logic tile and the input, output, and control ports of an I/O buffer to capture and load data into the register to control or observe the logic state of each I/O.

Figure 1-13 • TAP Controller State Diagram

1-12 v5.8

enable the user to define a wide range of frequency multipliers and divisors. The clock conditioning circuit can advance or delay the clock up to 8 ns (in increments of 0.25 ns) relative to the positive edge of the incoming reference clock. The system also allows for the selection of output frequency clock phases of 0° and 180°.

Prior to the application of signals to the rib drivers, they pass through programmable delay units, one per global network. These units permit the delaying of global

signals relative to other signals to assist in the control of input set-up times. Not all possible combinations of input and output modes can be used. The degrees of freedom available in the bidirectional global pad system and in the clock conditioning circuit have been restricted. This avoids unnecessary and unwieldy design kit and software work.

#### Notes:

- 1. FBDLY is a programmable delay line from 0 to 4 ns in 250 ps increments.

- 2. DLYA and DLYB are programmable delay lines, each with selectable values 0 ps, 250 ps, 500 ps, and 4 ns.

- 3. OBDIV will also divide the phase-shift since it takes place after the PLL Core.

Figure 1-14 • PLL Block – Top-Level View and Detailed PLL Block Diagram

1-14 v5.8

**Note:** When a signal from an I/O tile is connected to the core, it cannot be connected to the Global MUX at the same time. Figure 1-15 • Input Connectors to ProASIC PLUS Clock Conditioning Circuitry

Table 1-7 • Clock-Conditioning Circuitry MUX Settings

| MUX     | Datapath                                           | Comments                             |

|---------|----------------------------------------------------|--------------------------------------|

| FBSEL   |                                                    |                                      |

| 1       | Internal Feedback                                  |                                      |

| 2       | Internal Feedback and Advance Clock Using FBDLY    | −0.25 to −4 ns in 0.25 ns increments |

| 3       | External Feedback (EXTFB)                          |                                      |

| XDLYSEL |                                                    |                                      |

| 0       | Feedback Unchanged                                 |                                      |

| 1       | Deskew feedback by advancing clock by system delay | Fixed delay of -2.95 ns              |

| OBMUX   | GLB                                                |                                      |

| 0       | Primary bypass, no divider                         |                                      |

| 1       | Primary bypass, use divider                        |                                      |

| 2       | Delay Clock Using FBDLY                            | +0.25 to +4 ns in 0.25 ns increments |

| 4       | Phase Shift Clock by 0°                            |                                      |

| 5       | Reserved                                           |                                      |

| 6       | Phase Shift Clock by +180°                         |                                      |

| 7       | Reserved                                           |                                      |

| OAMUX   | GLA                                                |                                      |

| 0       | Secondary bypass, no divider                       |                                      |

| 1       | Secondary bypass, use divider                      |                                      |

| 2       | Delay Clock Using FBDLY                            | +0.25 to +4 ns in 0.25 ns increments |

| 3       | Phase Shift Clock by 0°                            |                                      |

## Logic-Tile Contribution—Plogic

Plogic, the logic-tile component of AC power dissipation, is given by

$$P_{logic} = P3 * mc * Fs$$

where:

P3 =  $1.4 \mu W/MHz$  is the average power consumption of a logic tile per MHz of its output toggling rate. The maximum output toggling rate is Fs/2.

mc = the number of logic tiles switching during each Fs cycle

Fs = the clock frequency

## I/O Output Buffer Contribution—Poutputs

Poutputs, the I/O component of AC power dissipation, is given by

$$P_{\text{outputs}} = (P4 + (C_{\text{load}} * V_{\text{DDP}}^2)) * p * Fp$$

where:

P4 =  $326 \mu W/MHz$  is the intrinsic power consumption of an output pad normalized per MHz of the output frequency. This is the total I/O current  $V_{DDP}$

$C_{load}$  = the output load

p = the number of outputs

Fp = the average output frequency

# I/O Input Buffer's Buffer Contribution—Pinputs

The input's component of AC power dissipation is given by

$$P_{inputs} = P8 * q * Fq$$

where:

P8 =  $29 \mu W/MHz$  is the intrinsic power consumption of an input pad normalized per MHz of the input frequency.

q = the number of inputs

Fq = the average input frequency

#### PLL Contribution—Ppll

$$P_{\text{pll}} = P9 * N_{\text{pll}}$$

where:

P9 = 7.5 mW. This value has been estimated at maximum PLL clock frequency.

N<sub>DII</sub> = number of PLLs used

# RAM Contribution—P<sub>memory</sub>

Finally, P<sub>memory</sub>, the memory component of AC power consumption, is given by

$$P_{memory} = P6 * N_{memory} * F_{memory} * E_{memory}$$

where:

P6 =  $175 \mu W/MHz$  is the average power consumption of a memory block per MHz of the clock

N<sub>memory</sub> = the number of RAM/FIFO blocks (1 block = 256 words \* 9 bits)

$F_{memory}$  = the clock frequency of the memory

E<sub>memory</sub> = the average number of active blocks divided by the total number of blocks (N) of the memory.

• Typical values for E<sub>memory</sub> would be 1/4 for a 1k x 8,9,16, 32 memory and 1/16 for a 4kx8, 9, 16, and 32 memory configuration

• In addition, an application-dependent component to  $E_{memory}$  can be considered. For example, for a 1kx8 memory configuration using only 1 cycle out of 2,  $E_{memory} = 1/4*1/2 = 1/8$

1-32 v5.8

The following is an APA750 example using a shift register design with 13,440 storage tiles (Register) and 0 logic tiles. This design has one clock at 10 MHz, and 24 outputs toggling at 5 MHz. We then calculate the various components as follows:

## **P**clock

=>

$$P_{clock} = (P1 + (P2*R) - (P7*R^2)) * Fs = 121.5 mW$$

#### P<sub>storage</sub>

ms = 13,440 (in a shift register 100% of storage tiles are toggling at each clock cycle and Fs = 10 MHz)

### P<sub>logic</sub>

$$=> P_{logic} = 0 \text{ mW}$$

## Poutputs

$$C_{load} = 40 pF$$

$$V_{DDP} = 3.3 V$$

$$p = 24$$

$$Fp = 5 MHz$$

$$=> P_{outputs} = (P4 + (C_{load} * V_{DDP}^2)) * p * Fp = 91.4 mW$$

## Pinputs

$$q = 1$$

$$Fq = 10 MHz$$

$$=> P_{inputs} = P8 * q * Fq = 0.3 mW$$

# P<sub>memory</sub>

$N_{memory} = 0$  (no RAM/FIFO blocks in this shift register)

#### $P_{ac}$

# P<sub>total</sub>

$$P_{dc} + P_{ac} = 374 \text{ mW (typical)}$$

Table 1-24 • DC Electrical Specifications ( $V_{DDP}$  = 3.3 V  $\pm$ 0.3 V and  $V_{DD}$  = 2.5 V  $\pm$ 0.2 V) Applies to Military Temperature and MIL-STD-883B Temperature Only

|                              |                                                                                        |                                                                                |                                                    | Military                    | /MIL-S                            | TD-883B <sup>1</sup>                                  |       |

|------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------|-----------------------------------|-------------------------------------------------------|-------|

| Symbol                       | Parameter                                                                              | Conditions                                                                     |                                                    | Min.                        | Тур.                              | Max.                                                  | Units |

| V <sub>OH</sub>              | Output High Voltage<br>3.3 V I/O, High Drive, High Slew<br>(OB33PH)                    | I <sub>OH</sub> = -8 mA<br>I <sub>OH</sub> = -16 mA                            |                                                    | 0.9*V <sub>DDP</sub><br>2.4 |                                   |                                                       |       |

|                              | 3.3V I/O, High Drive, Normal/<br>Low Slew (OB33PN/OB33PL)                              | $I_{OH} = -3mA$ $I_{OH} = -8mA$                                                |                                                    | 0.9*V <sub>DDP</sub><br>2.4 |                                   |                                                       | V     |

|                              | 3.3 V I/O, Low Drive , High/<br>Normal/Low Slew (OB33LH/<br>OB33LN/OB33LL)             |                                                                                | $_{DH} = -3 \text{ mA}$<br>$_{DH} = -8 \text{ mA}$ |                             |                                   |                                                       |       |

| V <sub>OL</sub>              | Output Low Voltage<br>3.3 V I/O, High Drive, High Slew<br>(OB33PH)                     | I <sub>OL</sub> = 12 mA<br>I <sub>OL</sub> = 17 mA<br>I <sub>OL</sub> = 28 mA  |                                                    |                             |                                   | 0.1V <sub>DDP</sub><br>0.4<br>0.7                     |       |

|                              | 3.3V I/O, High Drive, Normal/<br>Low Slew (OB33PN/OB33PL))                             | $I_{OL} = 4 \text{ mA}$<br>$I_{OL} = 6 \text{ mA}$<br>$I_{OL} = 13 \text{ mA}$ |                                                    |                             | 0.1V <sub>DDP</sub><br>0.4<br>0.7 | V                                                     |       |

|                              | 3.3 V I/O, Low Drive, High/<br>Normal/Low Slew (OB33LH/<br>OB33LN/OB33LL)              |                                                                                |                                                    |                             | 0.1V <sub>DDP</sub><br>0.4<br>0.7 |                                                       |       |

| V <sub>IH</sub> <sup>4</sup> | Input High Voltage<br>3.3 V Schmitt Trigger Inputs<br>3.3 V LVTTL/LVCMOS<br>2.5 V Mode |                                                                                |                                                    | 1.6<br>2<br>1.7             |                                   | $V_{DDP} + 0.3$<br>$V_{DDP} + 0.3$<br>$V_{DDP} + 0.3$ | >     |

| V <sub>IL</sub> <sup>5</sup> | Input Low Voltage<br>3.3 V Schmitt Trigger Inputs<br>3.3 V LVTTL/LVCMOS<br>2.5 V Mode  |                                                                                |                                                    | -0.3<br>-0.3<br>-0.3        |                                   | 0.7<br>0.8<br>0.7                                     | V     |

| R <sub>WEAKPULLUP</sub>      | Weak Pull-up Resistance<br>(IOB33U)                                                    | V <sub>IN</sub> ≥ 1.5 V                                                        |                                                    | 7                           |                                   | 43                                                    | kΩ    |

| R <sub>WEAKPULLUP</sub>      | Weak Pull-up Resistance<br>(IOB25U)                                                    | V <sub>IN</sub> ≥ 1.5 V                                                        |                                                    | 7                           |                                   | 43                                                    | kΩ    |

| I <sub>IN</sub>              | Input Current                                                                          | with pull up ( $V_{IN} = GND$ )                                                |                                                    | -300                        |                                   | -40                                                   | μΑ    |

|                              |                                                                                        | without pull up ( $V_{IN} = GND \text{ or } V_{DD}$ )                          |                                                    | -10                         |                                   | 10                                                    | μΑ    |

| $I_{DDQ}$                    | Quiescent Supply Current                                                               | $V_{IN} = GND^2$ or $V_{DD}$                                                   | Std.                                               |                             | 5.0                               | 15                                                    | mA    |

|                              | (standby)<br>Commercial                                                                | <br>                                                                           |                                                    |                             | 5.0                               | 25                                                    | mA    |

#### Notes:

- 1. All process conditions. Military Temperature / MIL-STD-883 Class B: Junction Temperature: -55 to +125°C.

- 2. No pull-up resistor required.

- 3. This will not exceed 2 mA total per device.

- 4. During transitions, the input signal may overshoot to  $V_{DDP}$  +1.0 V for a limited time of no larger than 10% of the duty cycle.

- 5. During transitions, the input signal may undershoot to -1.0 V for a limited time of no larger than 10% of the duty cycle.

Table 1-25 • DC Specifications (3.3 V PCI Operation)<sup>1</sup>

|                  |                                    |                            |                    |                     | nercial/<br>trial <sup>2,3</sup> | Military/MII        | L-STD- 883 <sup>2,3</sup> |       |

|------------------|------------------------------------|----------------------------|--------------------|---------------------|----------------------------------|---------------------|---------------------------|-------|

| Symbol           | Parameter                          | Condition                  |                    | Min.                | Max.                             | Min.                | Max.                      | Units |

| $V_{DD}$         | Supply Voltage for Core            |                            |                    | 2.3                 | 2.7                              | 2.3                 | 2.7                       | V     |

| $V_{DDP}$        | Supply Voltage for I/O Ring        |                            |                    | 3.0                 | 3.6                              | 3.0                 | 3.6                       | V     |

| V <sub>IH</sub>  | Input High Voltage                 |                            |                    | 0.5V <sub>DDP</sub> | V <sub>DDP</sub> + 0.5           | 0.5V <sub>DDP</sub> | V <sub>DDP</sub> + 0.5    | V     |

| V <sub>IL</sub>  | Input Low Voltage                  |                            |                    | -0.5                | 0.3V <sub>DDP</sub>              | -0.5                | 0.3V <sub>DDP</sub>       | V     |

| I <sub>IPU</sub> | Input Pull-up Voltage <sup>4</sup> |                            |                    | 0.7V <sub>DDP</sub> |                                  | 0.7V <sub>DDP</sub> |                           | V     |

| I <sub>IL</sub>  | Input Leakage Current <sup>5</sup> | $0 < V_{IN} < V_{DDP}$     | Std.               | -10                 | 10                               | -50                 | 50                        | μА    |

|                  |                                    |                            | −F <sup>3, 6</sup> | -10                 | 100                              |                     |                           | μΑ    |

| V <sub>OH</sub>  | Output High Voltage                | I <sub>OUT</sub> = -500 μA | •                  | 0.9V <sub>DDP</sub> |                                  | 0.9V <sub>DDP</sub> |                           | V     |

| V <sub>OL</sub>  | Output Low Voltage                 | I <sub>OUT</sub> = 1500 μA |                    |                     | 0.1V <sub>DDP</sub>              |                     | 0.1V <sub>DDP</sub>       | V     |

| C <sub>IN</sub>  | Input Pin Capacitance (except CLK) |                            |                    |                     | 10                               |                     | 10                        | pF    |

| C <sub>CLK</sub> | CLK Pin Capacitance                |                            |                    | 5                   | 12                               | 5                   | 12                        | pF    |

#### Notes:

- 1. For PCI operation, use GL33, OTB33PH, OB33PH, IOB33PH, IB33, or IB33S macro library cell only.

- 2. All process conditions. Junction Temperature: -40 to +110°C for Commercial and Industrial devices and -55 to +125°C for Military.

- 3. All –F parts are available as commercial only.

- 4. This specification is guaranteed by design. It is the minimum voltage to which pull-up resistors are calculated to pull a floated network. Designers with applications sensitive to static power utilization should ensure that the input buffer is conducting minimum current at this input voltage.

- 5. Input leakage currents include hi-Z output leakage for all bidirectional buffers with tristate outputs.

- 6. The sum of the leakage currents for all inputs shall not exceed 2mA per device.

*Table 1-37* • Worst-Case Military Conditions

$V_{DDP}$  = 3.0V,  $V_{DD}$  = 2.3V,  $T_J$  = 125°C for Military/MIL-STD-883

|            |                                                                             | Max. t <sub>INYH</sub> 1 | Max. t <sub>INYL</sub> 2 |       |

|------------|-----------------------------------------------------------------------------|--------------------------|--------------------------|-------|

| Macro Type | Description                                                                 | Std.                     | Std.                     | Units |

| IB33       | 3.3V, CMOS Input Levels <sup>3</sup> , No Pull-up Resistor                  | 0.5                      | 0.6                      | ns    |

| IB33S      | 3.3V, CMOS Input Levels <sup>3</sup> , No Pull-up Resistor, Schmitt Trigger | 0.6                      | 0.8                      | ns    |

#### Notes:

- 1.  $t_{INYH} = Input Pad-to-Y High$

- 2.  $t_{INYL} = Input Pad-to-Y Low$

- 3. LVTTL delays are the same as CMOS delays.

- 4. For LP Macros, V<sub>DDP</sub>=2.3V for delays.

*Table 1-38* • Worst-Case Military Conditions

$V_{DDP}$  = 2.3V,  $V_{DD}$  = 2.3V,  $T_{J}$  = 125°C for Military/MIL-STD-883

|            |                                                                   | Max. t <sub>INYH</sub> 1 | Max. t <sub>INYL</sub> 2 |       |

|------------|-------------------------------------------------------------------|--------------------------|--------------------------|-------|

| Macro Type | Description                                                       | Std.                     | Std.                     | Units |

| IB25LP     | 2.5V, CMOS Input Levels <sup>3</sup> , Low Power                  | 0.9                      | 0.7                      | ns    |

| IB25LPS    | 2.5V, CMOS Input Levels <sup>3</sup> , Low Power, Schmitt Trigger | 0.8                      | 1.0                      | ns    |

#### Notes:

- 1.  $t_{INYH} = Input Pad-to-Y High$

- 2.  $t_{INYL} = Input Pad-to-Y Low$

- 3. LVTTL delays are the same as CMOS delays.

- 4. For LP Macros,  $V_{DDP}$ =2.3V for delays.

1-50 v5.8

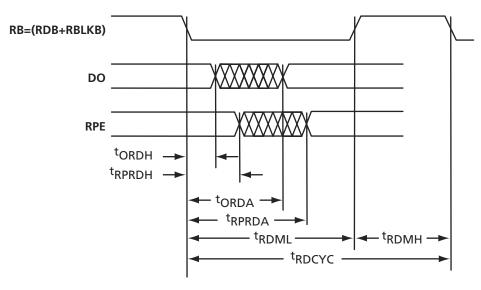

# **Asynchronous SRAM Read, RDB Controlled**

**Note:** The plot shows the normal operation status.

Figure 1-35 • Asynchronous SRAM Read, RDB Controlled

Table 1-56 •  $T_J = 0$ °C to 110°C;  $V_{DD} = 2.3$  V to 2.7 V for Commercial/industrial  $T_J = -55$ °C to 150°C,  $V_{DD} = 2.3$  V to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description              | Min. | Max. | Units | Notes                       |

|-------------------------|--------------------------|------|------|-------|-----------------------------|

| ORDA                    | New DO access from RB ↓  | 7.5  |      | ns    |                             |

| ORDH                    | Old DO valid from RB ↓   |      | 3.0  | ns    |                             |

| RDCYC                   | Read cycle time          | 7.5  |      | ns    |                             |

| RDMH                    | RB high phase            | 3.0  |      | ns    | Inactive setup to new cycle |

| RDML                    | RB low phase             | 3.0  |      | ns    | Active                      |

| RPRDA                   | New RPE access from RB ↓ | 9.5  |      | ns    |                             |

| RPRDH                   | Old RPE valid from RB ↓  |      | 3.0  | ns    |                             |

Note: All –F speed grade devices are 20% slower than the standard numbers.

1-62 v5.8

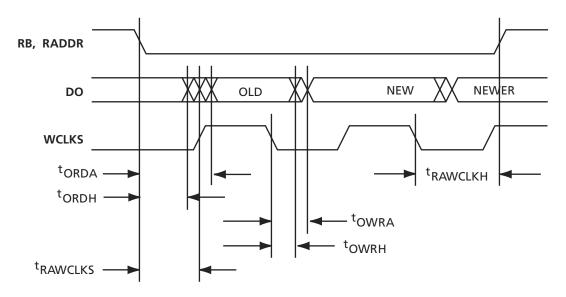

# Synchronous Write and Asynchronous Read to the Same Location

**Note:** The plot shows the normal operation status.

Figure 1-40 • Synchronous Write and Asynchronous Read to the Same Location

Table 1-61 •  $T_J = 0^{\circ}\text{C}$  to 110°C;  $V_{DD} = 2.3 \text{ V}$  to 2.7 V for Commercial/industrial  $T_J = -55^{\circ}\text{C}$  to 150°C,  $V_{DD} = 2.3 \text{ V}$  to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                | Min. | Max. | Units | Notes |

|-------------------------|----------------------------|------|------|-------|-------|

| ORDA                    | New DO access from RB ↓    | 7.5  |      | ns    |       |

| ORDH                    | Old DO valid from RB ↓     |      | 3.0  | ns    |       |

| OWRA                    | New DO access from WCLKS ↓ | 3.0  |      | ns    |       |

| OWRH                    | Old DO valid from WCLKS ↓  |      | 0.5  | ns    |       |

| RAWCLKS                 | RB ↓ or RADDR from WCLKS ↑ | 5.0  |      | ns    |       |

| RAWCLKH                 | RB ↑ or RADDR from WCLKS ↓ | 5.0  |      | ns    |       |

#### Notes:

- 1. During an asynchronous read cycle, each write operation (synchronous or asynchronous) to the same location will automatically trigger a read operation which updates the read data.

- 2. Violation of RAWCLKS will disturb access to OLD data.

- 3. Violation of RAWCLKH will disturb access to NEWER data.

- 4. All –F speed grade devices are 20% slower than the standard numbers.

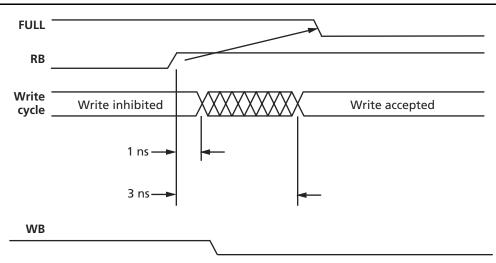

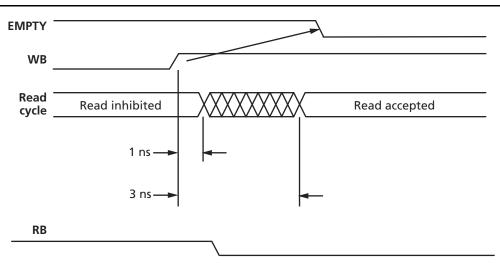

# **Asynchronous FIFO Full and Empty Transitions**

The asynchronous FIFO accepts writes and reads while not full or not empty. When the FIFO is full, all writes are inhibited. Conversely, when the FIFO is empty, all reads are inhibited. A problem is created if the FIFO is written to during the transition from full to not full, or read during the transition from empty to not empty. The exact time at which the write or read operation changes from inhibited to accepted after the read (write) signal which causes the transition from full or empty to not full or not empty is indeterminate. For slow cycles, this indeterminate period starts 1 ns after the RB (WB) transition, which deactivates full or not empty and ends 3 ns after the RB (WB) transition. For fast cycles, the indeterminate period ends 3 ns (7.5 ns – RDL (WRL)) after the RB (WB) transition, whichever is later (Table 1-1 on page 1-7).

The timing diagram for write is shown in Figure 1-38 on page 1-65. The timing diagram for read is shown in Figure 1-39 on page 1-66. For basic SRAM configurations, see Table 1-14 on page 1-25. When reset is asserted, the

empty flag will be asserted, the counters will reset, the outputs go to zero, but the internal RAM is not erased.

## **Enclosed Timing Diagrams – FIFO Mode:**

The following timing diagrams apply only to single cell; they are not applicable to cascaded cells. For more information, refer to the *ProASIC*<sup>PLUS</sup> *RAMIFIFO Blocks* application note.

- "Asynchronous FIFO Read" section on page 1-70

- "Asynchronous FIFO Write" section on page 1-71

- "Synchronous FIFO Read, Access Timed Output Strobe (Synchronous Transparent)" section on page 1-72

- "Synchronous FIFO Read, Pipeline Mode Outputs (Synchronous Pipelined)" section on page 1-73

- "Synchronous FIFO Write" section on page 1-74

- "FIFO Reset" section on page 1-75

Table 1-62 • Memory Block FIFO Interface Signals

| FIFO Signal  | Bits | In/Out | Description                                                                                                                                 |

|--------------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|

| WCLKS        | 1    | In     | Write clock used for synchronization on write side                                                                                          |

| RCLKS        | 1    | In     | Read clock used for synchronization on read side                                                                                            |

| LEVEL <0:7>* | 8    | In     | Direct configuration implements static flag logic                                                                                           |

| RBLKB        | 1    | In     | Read block select (active Low)                                                                                                              |

| RDB          | 1    | In     | Read pulse (active Low)                                                                                                                     |

| RESET        | 1    | In     | Reset for FIFO pointers (active Low)                                                                                                        |

| WBLKB        | 1    | In     | Write block select (active Low)                                                                                                             |

| DI<0:8>      | 9    | In     | Input data bits <0:8>, <8> will be generated if PARGEN is true                                                                              |

| WRB          | 1    | In     | Write pulse (active Low)                                                                                                                    |

| FULL, EMPTY  | 2    | Out    | FIFO flags. FULL prevents write and EMPTY prevents read                                                                                     |

| EQTH, GEQTH* | 2    | Out    | EQTH is true when the FIFO holds the number of words specified by the LEVEL signal. GEQTH is true when the FIFO holds (LEVEL) words or more |

| DO<0:8>      | 9    | Out    | Output data bits <0:8>                                                                                                                      |

| RPE          | 1    | Out    | Read parity error (active High)                                                                                                             |

| WPE          | 1    | Out    | Write parity error (active High)                                                                                                            |

| LGDEP <0:2>  | 3    | In     | Configures DEPTH of the FIFO to 2 (LGDEP+1)                                                                                                 |

| PARODD       | 1    | ln     | Selects Odd parity generation/detect when high, Even when low                                                                               |

**Note:** \*LEVEL is always eight bits (0000.0000, 0000.0001). That means for values of DEPTH greater than 256, not all values will be possible, e.g. for DEPTH=512, the LEVEL can only have the values 2, 4, . . . , 512. The LEVEL signal circuit will generate signals that indicate whether the FIFO is exactly filled to the value of LEVEL (EQTH) or filled equal or higher (GEQTH) than the specified LEVEL. Since counting starts at 0, EQTH will become true when the FIFO holds (LEVEL+1) words for 512-bit FIFOs.

1-68 v5.8

**Note:** All –F speed grade devices are 20% slower than the standard numbers.

Figure 1-41 • Write Timing Diagram

**Note:** All –F speed grade devices are 20% slower than the standard numbers.

Figure 1-42 • Read Timing Diagram

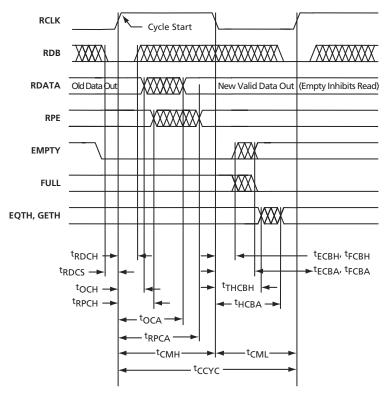

# Synchronous FIFO Read, Access Timed Output Strobe (Synchronous Transparent)

**Note:** The plot shows the normal operation status.

Figure 1-45 • Synchronous FIFO Read, Access Timed Output Strobe (Synchronous Transparent)

Table 1-65 •  $T_J = 0^{\circ}\text{C}$  to 110°C;  $V_{DD} = 2.3 \text{ V}$  to 2.7 V for Commercial/industrial  $T_J = -55^{\circ}\text{C}$  to 150°C,  $V_{DD} = 2.3 \text{ V}$  to 2.7 V for Military/MIL-STD-883

| Symbol t <sub>xxx</sub> | Description                                                           | Min.             | Мах. | Units | Notes                                                                               |

|-------------------------|-----------------------------------------------------------------------|------------------|------|-------|-------------------------------------------------------------------------------------|

| CCYC                    | Cycle time                                                            | 7.5              |      | ns    |                                                                                     |

| CMH                     | Clock high phase                                                      | 3.0              |      | ns    |                                                                                     |

| CML                     | Clock low phase                                                       | 3.0              |      | ns    |                                                                                     |

| ECBA                    | New EMPTY access from RCLKS ↓                                         | 3.0 <sup>1</sup> |      | ns    |                                                                                     |

| FCBA                    | FULL ↓ access from RCLKS ↓                                            | 3.0 <sup>1</sup> |      | ns    |                                                                                     |

| ECBH, FCBH,<br>THCBH    | Old EMPTY, FULL, EQTH, & GETH valid hold time from RCLKS $\downarrow$ |                  | 1.0  | ns    | Empty/full/thresh are invalid from the end of hold until the new access is complete |

| OCA                     | New DO access from RCLKS ↑                                            | 7.5              |      | ns    |                                                                                     |

| OCH                     | Old DO valid from RCLKS ↑                                             |                  | 3.0  | ns    |                                                                                     |

| RDCH                    | RDB hold from RCLKS ↑                                                 | 0.5              |      | ns    |                                                                                     |

| RDCS                    | RDB setup to RCLKS ↑                                                  | 1.0              |      | ns    |                                                                                     |

| RPCA                    | New RPE access from RCLKS ↑                                           | 9.5              |      | ns    |                                                                                     |

| RPCH                    | Old RPE valid from RCLKS ↑                                            |                  | 3.0  | ns    |                                                                                     |

| НСВА                    | EQTH or GETH access from RCLKS ↓                                      | 4.5              |      | ns    |                                                                                     |

#### Notes:

- 1. At fast cycles, ECBA and FCBA = MAX (7.5 ns CMH), 3.0 ns.

- 2. All –F speed grade devices are 20% slower than the standard numbers.

1-72 v5.8