Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 67MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                            |

| Number of I/O              | 38                                                                           |

| Program Memory Size        | 128KB (128K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 32K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                 |

| Data Converters            | A/D 1x20b, 1x12b; D/A 4x8b                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 68-VFQFN Exposed Pad                                                         |

| Supplier Device Package    | 68-QFN (8x8)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c5867lti-lp025 |

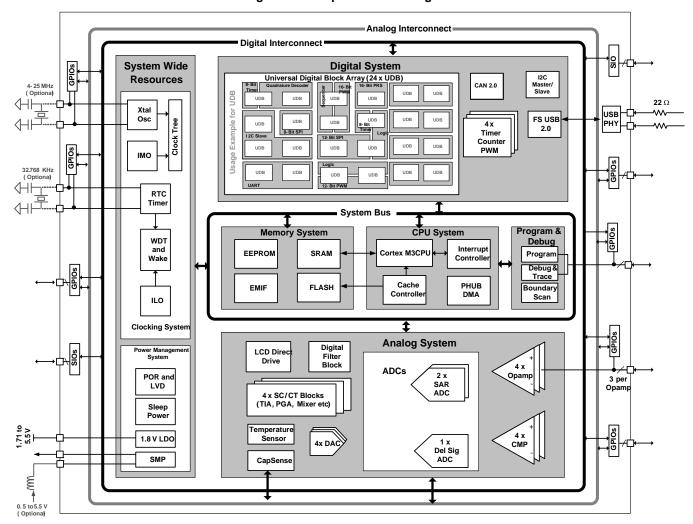

# 1. Architectural Overview

Introducing the CY8C58LP family of ultra low power, flash Programmable System-on-Chip (PSoC) devices, part of a scalable 8-bit PSoC 3 and 32-bit PSoC 5LP platform. The CY8C58LP family provides configurable blocks of analog, digital, and interconnect circuitry around a CPU subsystem. The combination of a CPU with a flexible analog subsystem, digital subsystem, routing, and I/O enables a high level of integration in a wide variety of consumer, industrial, and medical applications.

Figure 1-1. Simplified Block Diagram

Figure 1-1 illustrates the major components of the CY8C58LP family. They are:

- ARM Cortex-M3 CPU subsystem

- Nonvolatile subsystem

- Programming, debug, and test subsystem

- Inputs and outputs

- Clocking

- Power

- Digital subsystem

- Analog subsystem

PSoC's digital subsystem provides half of its unique configurability. It connects a digital signal from any peripheral to any pin through the digital system interconnect (DSI). It also provides functional flexibility through an array of small, fast, low power UDBs. PSoC Creator provides a library of pre-built and tested standard digital peripherals (UART, SPI, LIN, PRS, CRC, timer, counter, PWM, AND, OR, and so on) that are mapped to the UDB array. You can also easily create a digital circuit using boolean primitives by means of graphical design entry. Each UDB contains programmable array logic (PAL)/programmable logic device (PLD) functionality, together with a small state machine engine to support a wide variety of peripherals.

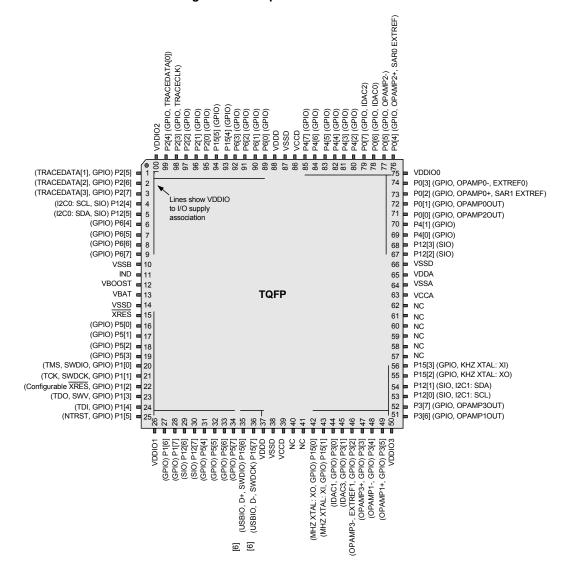

Figure 2-4. 100-pin TQFP Part Pinout

Table 2-1. V<sub>DDIO</sub> and Port Pin Associations

| VDDIO  | Port Pins                            |

|--------|--------------------------------------|

| VDDIO0 | P0[7:0], P4[7:0], P12[3:2]           |

| VDDIO1 | P1[7:0], P5[7:0], P12[7:6]           |

| VDDIO2 | P2[7:0], P6[7:0], P12[5:4], P15[5:4] |

| VDDIO3 | P3[7:0], P12[1:0], P15[3:0]          |

| VDDD   | P15[7:6] (USB D+, D-)                |

<sup>5.</sup> Pins are Do Not Use (DNU) on devices without USB. The pin must be left floating.

# 3. Pin Descriptions

**IDAC0, IDAC1, IDAC2, IDAC3.** Low-resistance output pin for high-current DACs (IDAC).

**Opamp0out, Opamp1out, Opamp2out, Opamp3out.** High current output of uncommitted opamp.<sup>[7]</sup>

**Extref0**, **Extref1**. External reference input to the analog system. **SAR0 EXTREF**, **SAR1 EXTREF**. External references for SAR ADCs

**Opamp0-, Opamp1-, Opamp2-, Opamp3-.** Inverting input to uncommitted opamp.

**Opamp0+, Opamp1+, Opamp2+, Opamp3+.** Noninverting input to uncommitted opamp.

**GPIO.** Provides interfaces to the CPU, digital peripherals, analog peripherals, interrupts, LCD segment drive, and CapSense. $^{[7]}$

**I2C0:** SCL, **I2C1:** SCL. I<sup>2</sup>C SCL line providing wake from sleep on an address match. Any I/O pin can be used for I<sup>2</sup>C SCL if wake from sleep is not required.

**I2C0: SDA, I2C1: SDA.** I<sup>2</sup>C SDA line providing wake from sleep on an address match. Any I/O pin can be used for I<sup>2</sup>C SDA if wake from sleep is not required.

**Ind.** Inductor connection to boost pump.

kHz XTAL: Xo, kHz XTAL: Xi. 32.768-kHz crystal oscillator pin.

MHz XTAL: Xo, MHz XTAL: Xi. 4 to 25-MHz crystal oscillator pin.

**nTRST.** Optional JTAG Test Reset programming and debug port connection to reset the JTAG connection.

**SIO.** Provides interfaces to the CPU, digital peripherals and interrupts with a programmable high threshold voltage, analog comparator, high sink current, and high impedance state when the device is unpowered.

**SWDCK.** SWD Clock programming and debug port connection.

**SWDIO.** SWD Input and Output programming and debug port connection.

**TCK.** JTAG Test Clock programming and debug port connection.

TDI. JTAG Test Data In programming and debug port connection.

**TDO.** JTAG Test Data Out programming and debug port connection.

**TMS.** JTAG Test Mode Select programming and debug port connection.

**TRACECLK.** Cortex-M3 TRACEPORT connection, clocks TRACEDATA pins.

**TRACEDATA[3:0].** Cortex-M3 TRACEPORT connections, output data.

SWV. SWV output.

**USBIO, D+.** Provides D+ connection directly to a USB 2.0 bus. May be used as a digital I/O pin; it is powered from VDDD instead of from a VDDIO. Pins are Do Not Use (DNU) on devices without USB.

**USBIO, D-.** Provides D- connection directly to a USB 2.0 bus. May be used as a digital I/O pin; it is powered from VDDD instead of from a VDDIO. Pins are Do Not Use (DNU) on devices without USB.

VBOOST. Power sense connection to boost pump.

**VBAT.** Battery supply to boost pump.

VCCA. Output of the analog core regulator or the input to the analog core. Requires a 1uF capacitor to VSSA. The regulator output is not designed to drive external circuits. Note that if you use the device with an external core regulator (externally regulated mode), the voltage applied to this pin must not exceed the allowable range of 1.71 V to 1.89 V. When using the internal core regulator, (internally regulated mode, the default), do not tie any power to this pin. For details see Power System on page 26.

VCCD. Output of the digital core regulator or the input to the digital core. The two VCCD pins must be shorted together, with the trace between them as short as possible, and a 1uF capacitor to VSSD. The regulator output is not designed to drive external circuits. Note that if you use the device with an external core regulator (externally regulated mode), the voltage applied to this pin must not exceed the allowable range of 1.71 V to 1.89 V. When using the internal core regulator (internally regulated mode, the default), do not tie any power to this pin. For details see Power System on page 26.

VDDA. Supply for all analog peripherals and analog core regulator. VDDA must be the highest voltage present on the device. All other supply pins must be less than or equal to VDDA.

**VDDD.** Supply for all digital peripherals and digital core regulator. VDDD must be less than or equal to VDDA.

VSSA. Ground for all analog peripherals.

**VSSB.** Ground connection for boost pump.

**VSSD.** Ground for all digital logic and I/O pins.

**VDDIO0, VDDIO1, VDDIO2, VDDIO3.** Supply for I/O pins. Each VDDIO must be tied to a valid operating voltage (1.71 V to 5.5 V), and must be less than or equal to VDDA.

**XRES.** External reset pin. Active low with internal pull-up.

### Note

Document Number: 001-84932 Rev. \*L Page 12 of 139

$<sup>\</sup>label{eq:commended} \textbf{7.} \quad \text{GPIOs with opamp outputs are not recommended for use with CapSense}.$

### 6.2.1 Power Modes

PSoC 5LP devices have four different power modes, as shown in Table 6-2 and Table 6-3. The power modes allow a design to easily provide required functionality and processing power while simultaneously minimizing power consumption and maximizing battery life in low power and portable devices.

PSoC 5LP power modes, in order of decreasing power consumption are:

- Active

- Alternate active

- Sleep

- Hibernate

Table 6-2. Power Modes

Active is the main processing mode. Its functionality is configurable. Each power controllable subsystem is enabled or disabled by using separate power configuration template registers. In alternate active mode, fewer subsystems are enabled, reducing power. In sleep mode most resources are disabled regardless of the template settings. Sleep mode is optimized to provide timed sleep intervals and RTC functionality. The lowest power mode is hibernate, which retains register and SRAM state, but no clocks, and allows wakeup only from I/O pins. Figure 6-5 illustrates the allowable transitions between power modes. Sleep and hibernate modes should not be entered until all VDDIO supplies are at valid voltage levels.

| <b>Power Modes</b>  | Description                                                                                                                                                                                                   | <b>Entry Condition</b>                     | Wakeup Source                                           | Active Clocks           | Regulator                                                                                                             |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Active              | Primary mode of operation, all peripherals available (programmable)                                                                                                                                           | Wakeup, reset,<br>manual register<br>entry | Any interrupt                                           | Any (program-<br>mable) | All regulators available. Digital and analog regulators can be disabled if external regulation used.                  |

| Alternate<br>Active | Similar to Active mode, and is<br>typically configured to have<br>fewer peripherals active to<br>reduce power. One possible<br>configuration is to use the UDBs<br>for processing, with the CPU<br>turned off | Manual register<br>entry                   | Any interrupt                                           | Any (program-<br>mable) | All regulators available. Digital and analog regulators can be disabled if external regulation used.                  |

| Sleep               | All subsystems automatically disabled                                                                                                                                                                         | Manual register<br>entry                   | Comparator,<br>PICU, I <sup>2</sup> C, RTC,<br>CTW, LVD | ILO/kHzECO              | Both digital and analog regulators buzzed. Digital and analog regulators can be disabled if external regulation used. |

| Hibernate           | All subsystems automatically disabled Lowest power consuming mode with all peripherals and internal regulators disabled, except hibernate regulator is enabled Configuration and memory contents retained     | Manual register<br>entry                   | PICU                                                    |                         | Only hibernate regulator active.                                                                                      |

Table 6-3. Power Modes Wakeup Time and Power Consumption

| Sleep<br>Modes      | Wakeup<br>Time | Current<br>(Typ)      | Code<br>Execution | Digital<br>Resources | Analog<br>Resources | Clock Sources<br>Available | Wakeup Sources                                          | Reset<br>Sources  |

|---------------------|----------------|-----------------------|-------------------|----------------------|---------------------|----------------------------|---------------------------------------------------------|-------------------|

| Active              | -              | 3.1 mA <sup>[8]</sup> | Yes               | All                  | All                 | All                        | _                                                       | All               |

| Alternate<br>Active | _              | _                     | User<br>defined   | All                  | All                 | All                        | _                                                       | All               |

| Sleep               | <25 µs         | 2 μΑ                  | No                | I <sup>2</sup> C     | Comparator          | ILO/kHzECO                 | Comparator, PICU,<br>I <sup>2</sup> C, RTC, CTW,<br>LVD | XRES, LVD,<br>WDR |

| Hibernate           | <200 µs        | 300 nA                | No                | None                 | None                | None                       | PICU                                                    | XRES              |

### Note

Document Number: 001-84932 Rev. \*L Page 28 of 139

<sup>8.</sup> Bus clock off. Execute from CPU instruction buffer at 6 MHz. See Table 11-2 on page 68.

The USBIO pins (P15[7] and P15[6]), when enabled for I/O mode, have limited drive mode control. The drive mode is set using the PRT15.DM0[7, 6] register. A resistive pull option is also available at the USBIO pins, which can be enabled using the PRT15.DM1[7, 6] register. When enabled for USB mode, the drive mode control has no impact on the configuration of the USB pins. Unlike the GPIO and SIO configurations, the port wide configuration registers do not configure the USB drive mode bits. Table 6-7 shows the drive mode configuration for the USBIO pins.

Table 6-7. USBIO Drive Modes (P15[7] and P15[6])

| PRT15.DM1[7,6]<br>Pull up enable | PRT15.DM0[7,6]<br>Drive Mode enable | PRT15.DR[7,6] = 1 | PRT15.DR[7,6] = 0 | Description                   |

|----------------------------------|-------------------------------------|-------------------|-------------------|-------------------------------|

| 0                                | 0                                   | High Z            | Strong Low        | Open Drain, Strong Low        |

| 0                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

| 1                                | 0                                   | Res High (5k)     | Strong Low        | Resistive Pull Up, Strong Low |

| 1                                | 1                                   | Strong High       | Strong Low        | Strong Outputs                |

### ■ High impedance analog

The default reset state with both the output driver and digital input buffer turned off. This prevents any current from flowing in the I/O's digital input buffer due to a floating voltage. This state is recommended for pins that are floating or that support an analog voltage. High impedance analog pins do not provide digital input functionality.

To achieve the lowest chip current in sleep modes, all I/Os must either be configured to the high impedance analog mode, or have their pins driven to a power supply rail by the PSoC device or by external circuitry.

# ■ High impedance digital

The input buffer is enabled for digital signal input. This is the standard high impedance (HiZ) state recommended for digital inputs.

# ■ Resistive pull-up or resistive pull-down

Resistive pull-up or pull-down, respectively, provides a series resistance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. Interfacing to mechanical switches is a common application for these modes. Resistive pull-up and pull-down are not available with SIO in regulated output mode.

Open drain, drives high and open drain, drives low Open drain modes provide high impedance in one of the data states and strong drive in the other. Pins can be used for digital input and output in these modes. A common application for these modes is driving the I<sup>2</sup>C bus signal lines.

# ■ Strong drive

Provides a strong CMOS output drive in either high or low state. This is the standard output mode for pins. Strong Drive mode pins must not be used as inputs under normal circumstances. This mode is often used to drive digital output signals or external FETs.

# ■ Resistive pull-up and pull-down

Similar to the resistive pull-up and resistive pull-down modes except the pin is always in series with a resistor. The high data

state is pull-up while the low data state is pull-down. This mode is most often used when other signals that may cause shorts can drive the bus. Resistive pull-up and pull-down are not available with SIO in regulated output mode.

### 6.4.2 Pin Registers

Registers to configure and interact with pins come in two forms that may be used interchangeably.

All I/O registers are available in the standard port form, where each bit of the register corresponds to one of the port pins. This register form is efficient for quickly reconfiguring multiple port pins at the same time.

I/O registers are also available in pin form, which combines the eight most commonly used port register bits into a single register for each pin. This enables very fast configuration changes to individual pins with a single register write.

## 6.4.3 Bidirectional Mode

High speed bidirectional capability allows pins to provide both the high impedance digital drive mode for input signals and a second user selected drive mode such as strong drive (set using PRTxDM[2:0] registers) for output signals on the same pin, based on the state of an auxiliary control bus signal. The bidirectional capability is useful for processor busses and communications interfaces such as the SPI Slave MISO pin that requires dynamic hardware control of the output buffer.

The auxiliary control bus routes up to 16 UDB or digital peripheral generated output enable signals to one or more pins.

### 6.4.4 Slew Rate Limited Mode

GPIO and SIO pins have fast and slow output slew rate options for strong and open drain drive modes, not resistive drive modes. Because it results in reduced EMI, the slow edge rate option is recommended for signals that are not speed critical, generally less than 1 MHz. The fast slew rate is for signals between 1 MHz and 33 MHz. The slew rate is individually configurable for each pin, and is set by the PRTxSLW registers.

Document Number: 001-84932 Rev. \*L Page 37 of 139

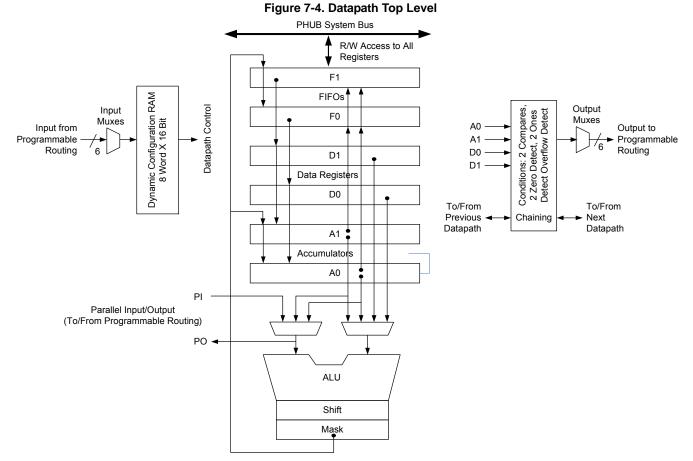

### 7.2.2.1 Working Registers

The datapath contains six primary working registers, which are accessed by CPU firmware or DMA during normal operation.

Table 7-1. Working Datapath Registers

| Name      | Function       | Description                                                                                                                                                                                               |

|-----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0 and A1 | Accumulators   | These are sources and sinks for the ALU and also sources for the compares.                                                                                                                                |

| D0 and D1 | Data Registers | These are sources for the ALU and sources for the compares.                                                                                                                                               |

| F0 and F1 | FIFOs          | These are the primary interface to the system bus. They can be a data source for the data registers and accumulators or they can capture data from the accumulators or ALU. Each FIFO is four bytes deep. |

# 7.2.2.2 Dynamic Configuration RAM

Dynamic configuration is the ability to change the datapath function and internal configuration on a cycle-by-cycle basis, under sequencer control. This is implemented using the 8-word x 16-bit configuration RAM, which stores eight unique 16-bit wide configurations. The address input to this RAM controls the

sequence, and can be routed from any block connected to the UDB routing matrix, most typically PLD logic, I/O pins, or from the outputs of this or other datapath blocks.

### ALU

The ALU performs eight general purpose functions. They are:

- Increment

- Decrement

- Add

- Subtract

- Logical AND

- Logical OR

- Logical XOR

- Pass, used to pass a value through the ALU to the shift register, mask, or another UDB register

Independent of the ALU operation, these functions are available:

- Shift left

- Shift right

- Nibble swap

- Bitwise OR mask

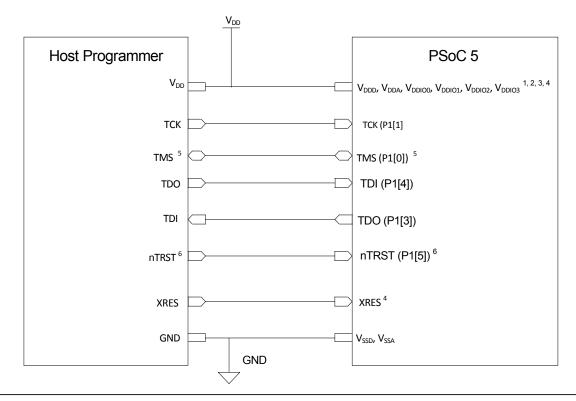

Figure 9-1. JTAG Interface Connections between PSoC 5LP and Programmer

- <sup>1</sup> The voltage levels of Host Programmer and the PSoC 5 voltage domains involved in Programming should be same. The Port 1 JTAG pins and XRES pin are powered by V<sub>DDIO1</sub>. So, V<sub>DDIO1</sub> of PSoC 5 should be at same voltage level as host V<sub>DD</sub>. Rest of PSoC 5 voltage domains (V<sub>DDD</sub>, V<sub>DDA</sub>, V<sub>DDIO2</sub>, V<sub>DDIO3</sub>) need not be at the same voltage level as host Programmer.

- <sup>2</sup> Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 5.

- <sup>3</sup> For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 5. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

- <sup>4</sup> For JTAG Programming, Device reset can also be done without connecting to the XRES pin or Power cycle mode by using the TMS,TCK,TDI, TDO pins of PSoC 5, and writing to a specific register. But this requires that the DPS setting in NVL is not equal to "Debug Ports Disabled".

- <sup>5</sup> By default, PSoC 5 is configured for 4-wire JTAG mode unless user changes the DPS setting. So the TMS pin is unidirectional. But if the DPS setting is changed to non-JTAG mode, the TMS pin in JTAG is bi-directional as the SWD Protocol has to be used for acquiring the PSoC 5 device initially. After switching from SWD to JTAG mode, the TMS pin will be uni-directional. In such a case, unidirectional buffer should not be used on TMS line.

- <sup>6</sup> nTRST JTAG pin (P1[5]) cannot be used to reset the JTAG TAP controlller during first time programming of PSoC 5 as the default setting is 4-wire JTAG (nTRST disabled). Use the TMS, TCK pins to do a reset of JTAG TAP controller.

Document Number: 001-84932 Rev. \*L Page 62 of 139

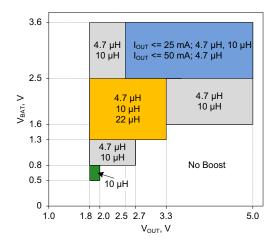

Table 11-7. Recommended External Components for Boost Circuit

| Parameter          | Description                                                        | Conditions     | Min  | Тур  | Max  | Units |

|--------------------|--------------------------------------------------------------------|----------------|------|------|------|-------|

| L <sub>BOOST</sub> | Boost inductor                                                     | 4.7 μH nominal | 3.7  | 4.7  | 5.7  | μH    |

|                    |                                                                    | 10 μH nominal  | 8.0  | 10.0 | 12.0 | μH    |

|                    |                                                                    | 22 μH nominal  | 17.0 | 22.0 | 27.0 | μΗ    |

| C <sub>BOOST</sub> | Total capacitance sum of $V_{DDD}$ , $V_{DDA}$ , $V_{DDIO}^{[32]}$ |                | 17.0 | 26.0 | 31.0 | μF    |

| C <sub>BAT</sub>   | Battery filter capacitor                                           |                | 17.0 | 22.0 | 27.0 | μF    |

| l <sub>F</sub>     | Schottky diode average forward current                             |                | 1.0  | _    | 1    | Α     |

| V <sub>R</sub>     | Schottky reverse voltage                                           |                | 20.0 | _    | _    | V     |

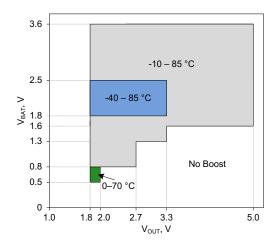

Figure 11-8.  $T_A$  range over  $V_{BAT}$  and  $V_{OUT}$

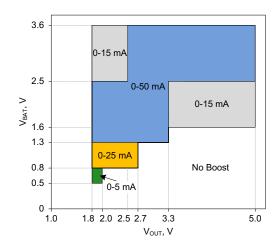

Figure 11-9. I<sub>OUT</sub> range over V<sub>BAT</sub> and V<sub>OUT</sub>

Figure 11-10.  $L_{\mbox{\footnotesize{BOOST}}}$  values over  $V_{\mbox{\footnotesize{BAT}}}$  and  $V_{\mbox{\footnotesize{OUT}}}$

32. Based on device characterization (Not production tested).

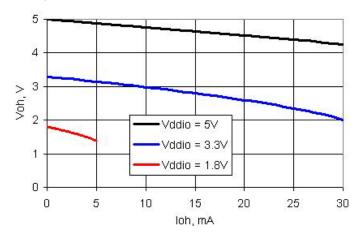

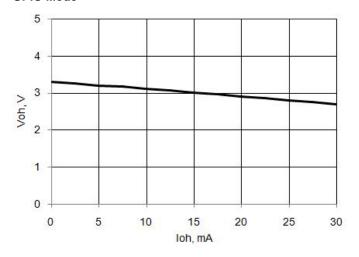

Figure 11-17. SIO Output High Voltage and Current, Unregulated Mode

Figure 11-18. SIO Output Low Voltage and Current, Unregulated Mode

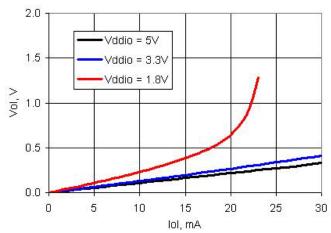

Figure 11-19. SIO Output High Voltage and Current, Regulated Mode

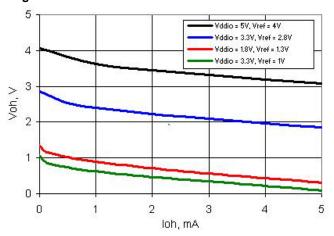

Figure 11-22. USBIO Output High Voltage and Current, GPIO Mode

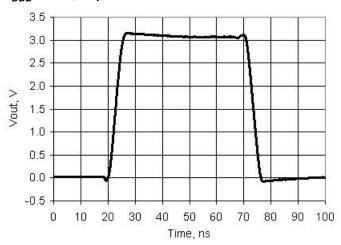

Figure 11-23. USBIO Output Rise and Fall Times, GPIO Mode,  $\rm V_{DDD} = 3.3~V,\,25~pF~Load$

Table 11-14. USBIO AC Specifications<sup>[41]</sup>

| Parameter | Description                                                 | Conditions                                           | Min        | Тур | Max           | Units |

|-----------|-------------------------------------------------------------|------------------------------------------------------|------------|-----|---------------|-------|

| Tdrate    | Full-speed data rate average bit rate                       |                                                      | 12 – 0.25% | 12  | 12 +<br>0.25% | MHz   |

| Tjr1      | Receiver data jitter tolerance to next transition           |                                                      | -8         | _   | 8             | ns    |

| Tjr2      | Receiver data jitter tolerance to pair transition           |                                                      | <b>-</b> 5 | _   | 5             | ns    |

| Tdj1      | Driver differential jitter to next transition               |                                                      | -3.5       | -   | 3.5           | ns    |

| Tdj2      | Driver differential jitter to pair transition               |                                                      | -4         | -   | 4             | ns    |

| Tfdeop    | Source jitter for differential transition to SE0 transition |                                                      | -2         | _   | 5             | ns    |

| Tfeopt    | Source SE0 interval of EOP                                  |                                                      | 160        | -   | 175           | ns    |

| Tfeopr    | Receiver SE0 interval of EOP                                |                                                      | 82         | -   | -             | ns    |

| Tfst      | Width of SE0 interval during differential transition        |                                                      | _          | _   | 14            | ns    |

| Fgpio_out | GPIO mode output operating frequency                        | $3 \text{ V} \leq \text{V}_{DDD} \leq 5.5 \text{ V}$ | _          | -   | 20            | MHz   |

|           |                                                             | V <sub>DDD</sub> = 1.71 V                            | _          | -   | 6             | MHz   |

| Tr_gpio   | Rise time, GPIO mode, $10\%/90\% V_{DDD}$                   | V <sub>DDD</sub> > 3 V, 25 pF load                   | _          | -   | 12            | ns    |

|           |                                                             | V <sub>DDD</sub> = 1.71 V, 25 pF load                | _          | -   | 40            | ns    |

| Tf_gpio   | Fall time, GPIO mode, 90%/10% V <sub>DDD</sub>              | V <sub>DDD</sub> > 3 V, 25 pF load                   | -          | _   | 12            | ns    |

|           |                                                             | V <sub>DDD</sub> = 1.71 V, 25 pF load                | _          | -   | 40            | ns    |

<sup>41.</sup> Based on device characterization (Not production tested).

Table 11-22. Delta-sigma ADC Sample Rates, Range = ±1.024 V

| Resolution, Bits | Continuous |        | Multi- | Sample | Multi-Sai | mple Turbo |

|------------------|------------|--------|--------|--------|-----------|------------|

| Resolution, Bits | Min        | Max    | Min    | Max    | Min       | Max        |

| 8                | 8000       | 384000 | 1911   | 91701  | 1829      | 87771      |

| 9                | 6400       | 307200 | 1543   | 74024  | 1489      | 71441      |

| 10               | 5566       | 267130 | 1348   | 64673  | 1307      | 62693      |

| 11               | 4741       | 227555 | 1154   | 55351  | 1123      | 53894      |

| 12               | 4000       | 192000 | 978    | 46900  | 956       | 45850      |

| 13               | 3283       | 157538 | 806    | 38641  | 791       | 37925      |

| 14               | 2783       | 133565 | 685    | 32855  | 674       | 32336      |

| 15               | 2371       | 113777 | 585    | 28054  | 577       | 27675      |

| 16               | 2000       | 48000  | 495    | 11861  | 489       | 11725      |

| 17               | 500        | 12000  | 124    | 2965   | 282       | 6766       |

| 18               | 125        | 3000   | 31     | 741    | 105       | 2513       |

| 19               | 16         | 375    | 4      | 93     | 15        | 357        |

| 20               | 8          | 187.5  | 2      | 46     | 8         | 183        |

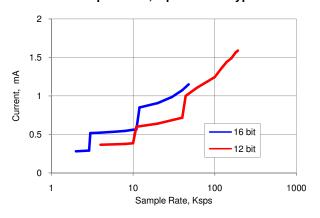

Figure 11-33. Delta-sigma ADC IDD vs sps, Range = ±1.024 V, Continuous Sample Mode, Input Buffer Bypassed

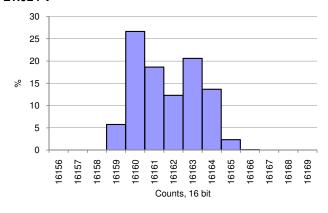

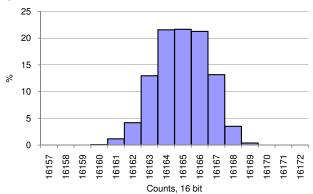

Figure 11-35. Delta-sigma ADC Noise Histogram, 1000 Samples, 16-bit, 48 ksps, Ext Ref,  $V_{IN} = V_{REF}/2$ , Range =  $\pm 1.024$  V

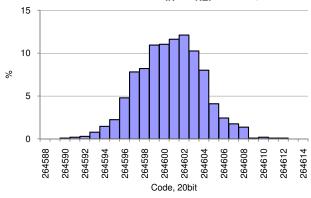

Figure 11-34. Delta-sigma ADC Noise Histogram, 1000 Samples, 20-Bit, 187 sps, Ext Ref,  $V_{IN} = V_{REF}/2$ , Range =  $\pm 1.024$  V

Figure 11-36. Delta-sigma ADC Noise Histogram, 1000 Samples, 16-bit, 48 ksps, Int Ref, V<sub>IN</sub> = V<sub>REF</sub>/2, Range = ±1.024 V

# 11.5.4 SAR ADC

# Table 11-28. SAR ADC DC Specifications

| Parameter       | Description                                        | Conditions                                                                                                              | Min       | Тур | Max             | Units |

|-----------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------|-----|-----------------|-------|

|                 | Resolution                                         |                                                                                                                         | -         | _   | 12              | bits  |

|                 | Number of channels – single-ended                  |                                                                                                                         | -         | _   | No of<br>GPIO   |       |

|                 | Number of channels – differential                  | Differential pair is formed using a pair of neighboring GPIO.                                                           | _         | _   | No of<br>GPIO/2 |       |

|                 | Monotonicity <sup>[52]</sup>                       |                                                                                                                         | Yes       | -   | -               |       |

| Ge              | Gain error <sup>[53]</sup>                         | External reference                                                                                                      | -         | _   | ±0.1            | %     |

| V <sub>OS</sub> | Input offset voltage                               |                                                                                                                         | -         | _   | ±2              | mV    |

| I <sub>DD</sub> | Current consumption <sup>[52]</sup>                |                                                                                                                         | -         | _   | 1               | mA    |

|                 | Input voltage range – single-ended <sup>[52]</sup> |                                                                                                                         | $V_{SSA}$ | _   | $V_{DDA}$       | V     |

|                 | Input voltage range – differential <sup>[52]</sup> |                                                                                                                         | $V_{SSA}$ | -   | $V_{DDA}$       | V     |

| PSRR            | Power supply rejection ratio <sup>[52]</sup>       |                                                                                                                         | 70        | _   | -               | dB    |

| CMRR            | Common mode rejection ratio                        |                                                                                                                         | 70        | _   | -               | dB    |

| INL             | Integral non linearity <sup>[52]</sup>             | V <sub>DDA</sub> 1.71 to 5.5 V, 1 Msps, V <sub>REF</sub> 1 to 5.5 V, bypassed at ExtRef pin                             | -         | _   | +2/–1.5         | LSB   |

|                 |                                                    | V <sub>DDA</sub> 2.0 to 3.6 V, 1 Msps, V <sub>REF</sub> 2 to V <sub>DDA</sub> , bypassed at ExtRef pin                  | -         | _   | ±1.2            | LSB   |

|                 |                                                    | V <sub>DDA</sub> 1.71 to 5.5 V, 500 ksps,<br>V <sub>REF</sub> 1 to 5.5 V, bypassed at<br>ExtRef pin                     | -         | _   | ±1.3            | LSB   |

| DNL             | Differential non linearity <sup>[52]</sup>         | V <sub>DDA</sub> 1.71 to 5.5 V, 1 Msps, V <sub>REF</sub> 1 to 5.5 V, bypassed at ExtRef pin                             | _         | _   | +2/–1           | LSB   |

|                 |                                                    | V <sub>DDA</sub> 2.0 to 3.6 V, 1 Msps, V <sub>REF</sub> 2 to V <sub>DDA</sub> , bypassed at ExtRef pin No missing codes | -         | _   | 1.7/–0.99       | LSB   |

|                 |                                                    | V <sub>DDA</sub> 1.71 to 5.5 V, 500 ksps,<br>V <sub>REF</sub> 1 to 5.5 V, bypassed at<br>ExtRef pin<br>No missing codes | -         | _   | +2/-0.99        | LSB   |

| R <sub>IN</sub> | Input resistance <sup>[52]</sup>                   |                                                                                                                         | _         | 180 | _               | kΩ    |

Document Number: 001-84932 Rev. \*L Page 94 of 139

<sup>52.</sup> Based on device characterization (Not production tested).

53. For total analog system Idd < 5 mA, depending on package used. With higher total analog system currents it is recommended that the SAR ADC be used in differential mode.</li>

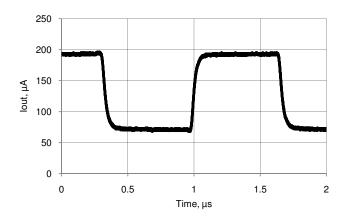

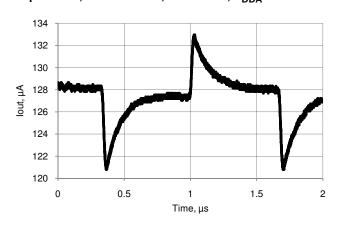

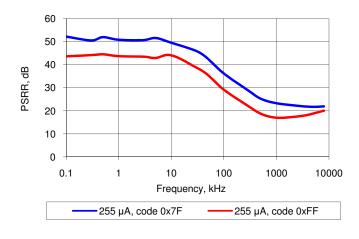

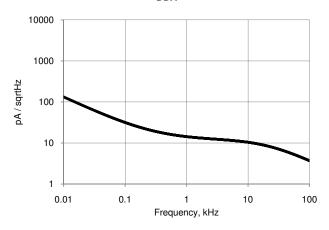

Table 11-35. IDAC AC Specifications<sup>[62]</sup>

| Parameter           | Description              | Conditions                                                                        | Min | Тур | Max | Units     |

|---------------------|--------------------------|-----------------------------------------------------------------------------------|-----|-----|-----|-----------|

| F <sub>DAC</sub>    | Update rate              |                                                                                   | -   | -   | 8   | Msps      |

| T <sub>SETTLE</sub> | Settling time to 0.5 LSB | Range = 31.875 $\mu$ A, full scale transition, fast mode, 600 $\Omega$ 15-pF load | _   | _   | 125 | ns        |

|                     |                          | Range = 255 $\mu$ A, full scale transition, fast mode, 600 $\Omega$ 15-pF load    | -   | _   | 125 | ns        |

|                     | Current noise            | Range = 255 µA, source mode, fast mode, Vdda = 5 V, 10 kHz                        | -   | 340 | -   | pA/sqrtHz |

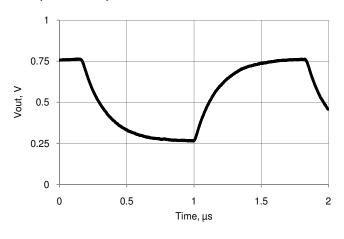

Figure 11-57. IDAC Step Response, Codes 0x40 - 0xC0, 255- $\mu A$  Mode, Source Mode, Fast Mode,  $V_{DDA}a=5$  V

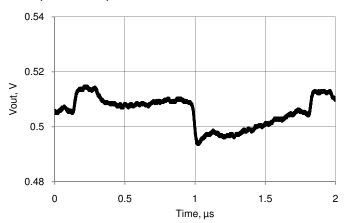

Figure 11-58. IDAC Glitch Response, Codes 0x7F - 0x80, 255 μA Mode, Source Mode, Fast Mode, V<sub>DDA</sub> = 5 V

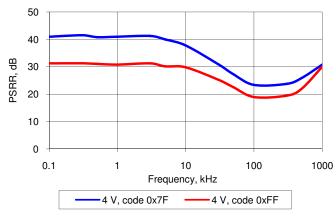

Figure 11-59. IDAC PSRR vs Frequency

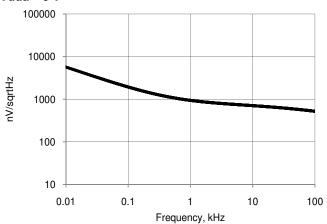

Figure 11-60. IDAC Current Noise, 255  $\mu$ A Mode, Source Mode, Fast Mode, V<sub>DDA</sub> = 5 V

62. Based on device characterization (Not production tested).

Table 11-37. VDAC AC Specifications [64]

| Parameter        | Description                            | Conditions                                 | Min | Тур  | Max  | Units     |

|------------------|----------------------------------------|--------------------------------------------|-----|------|------|-----------|

| F <sub>DAC</sub> | Update rate                            | 1 V scale                                  | _   | _    | 1000 | ksps      |

|                  |                                        | 4 V scale                                  | _   | _    | 250  | ksps      |

| TsettleP         | Settling time to 0.1%, step 25% to 75% | 1 V scale, Cload = 15 pF                   | -   | 0.45 | 1    | μs        |

|                  |                                        | 4 V scale, Cload = 15 pF                   | _   | 0.8  | 3.2  | μs        |

| TsettleN         | Settling time to 0.1%, step 75% to 25% | 1 V scale, Cload = 15 pF                   | -   | 0.45 | 1    | μs        |

|                  |                                        | 4 V scale, Cload = 15 pF                   | _   | 0.7  | 3    | μs        |

|                  | Voltage noise                          | Range = 1 V, fast mode, Vdda = 5 V, 10 kHz | _   | 750  | _    | nV/sqrtHz |

Figure 11-69. VDAC Step Response, Codes 0x40 - 0xC0, 1 V Mode, Fast Mode, Vdda = 5 V

Figure 11-70. VDAC Glitch Response, Codes 0x7F - 0x80, 1 V Mode, Fast Mode, Vdda = 5 V

Figure 11-71. VDAC PSRR vs Frequency

Figure 11-72. VDAC Voltage Noise, 1 V Mode, Fast Mode, Vdda = 5 V

64. Based on device characterization (Not production tested).

# 11.6.2 Counter

The following specifications apply to the Timer/Counter/PWM peripheral, in counter mode. Counters can also be implemented in UDBs; for more information, see the Counter component datasheet in PSoC Creator.

# Table 11-49. Counter DC Specifications<sup>[72]</sup>

| Parameter | Description               | Conditions                                      | Min | Тур | Max | Units |

|-----------|---------------------------|-------------------------------------------------|-----|-----|-----|-------|

|           | Block current consumption | 16-bit counter, at listed input clock frequency | _   | _   | _   | μA    |

|           | 3 MHz                     |                                                 | _   | 15  | _   | μA    |

|           | 12 MHz                    |                                                 | _   | 60  | _   | μA    |

|           | 48 MHz                    |                                                 | -   | 260 | -   | μA    |

|           | 80 MHz                    |                                                 | -   | 360 | -   | μA    |

# Table 11-50. Counter AC Specifications<sup>[72]</sup>

| Parameter | Description                        | Conditions | Min | Тур | Max   | Units |

|-----------|------------------------------------|------------|-----|-----|-------|-------|

|           | Operating frequency                |            | DC  | _   | 80.01 | MHz   |

|           | Capture pulse <sup>[73]</sup>      |            | 15  | _   | _     | ns    |

|           | Resolution <sup>[73]</sup>         |            | 15  | _   | _     | ns    |

|           | Pulse width <sup>[73]</sup>        |            | 15  | _   | _     | ns    |

|           | Pulse width (external)             |            | 30  |     |       | ns    |

|           | Enable pulse width <sup>[73]</sup> |            | 15  | _   | _     | ns    |

|           | Enable pulse width (external)      |            | 30  | _   | _     | ns    |

|           | Reset pulse width <sup>[73]</sup>  |            | 15  | _   | _     | ns    |

|           | Reset pulse width (external)       |            | 30  | _   | _     | ns    |

Document Number: 001-84932 Rev. \*L Page 112 of 139

<sup>72.</sup> Based on device characterization (Not production tested).73. For correct operation, the minimum Timer/Counter/PWM input pulse width is the period of bus clock.

# 11.8 PSoC System Resources

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C and T<sub>J</sub>  $\leq$  120 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

## 11.8.1 POR with Brown Out

For brown out detect in regulated mode,  $V_{DDD}$  and  $V_{DDA}$  must be  $\geq 2.0$  V. Brown out detect is not available in externally regulated mode

Table 11-71. Precise Low-Voltage Reset (PRES) with Brown Out DC Specifications

| Parameter | Description          | Conditions   | Min  | Тур | Max  | Units |

|-----------|----------------------|--------------|------|-----|------|-------|

| PRESR     | Rising trip voltage  | Factory trim | 1.64 | -   | 1.68 | V     |

| PRESF     | Falling trip voltage |              | 1.62 | _   | 1.66 | V     |

# Table 11-72. Power-On-Reset (POR) with Brown Out AC Specifications<sup>[90]</sup>

| Parameter               | Description Conditions                        |            | Min | Тур | Max | Units |

|-------------------------|-----------------------------------------------|------------|-----|-----|-----|-------|

| PRES_TR <sup>[91]</sup> | Response time                                 |            | _   | _   | 0.5 | μs    |

|                         | V <sub>DDD</sub> /V <sub>DDA</sub> droop rate | Sleep mode | -   | 5   | _   | V/sec |

## 11.8.2 Voltage Monitors

## Table 11-73. Voltage Monitors DC Specifications

| Parameter | Description              | Conditions | Min  | Тур  | Max  | Units |

|-----------|--------------------------|------------|------|------|------|-------|

| LVI       | Trip voltage             |            |      |      |      |       |

|           | LVI_A/D_SEL[3:0] = 0000b |            | 1.68 | 1.73 | 1.77 | V     |

|           | LVI_A/D_SEL[3:0] = 0001b |            | 1.89 | 1.95 | 2.01 | V     |

|           | LVI_A/D_SEL[3:0] = 0010b |            | 2.14 | 2.20 | 2.27 | V     |

|           | LVI_A/D_SEL[3:0] = 0011b |            | 2.38 | 2.45 | 2.53 | V     |

|           | LVI_A/D_SEL[3:0] = 0100b |            | 2.62 | 2.71 | 2.79 | V     |

|           | LVI_A/D_SEL[3:0] = 0101b |            | 2.87 | 2.95 | 3.04 | V     |

|           | LVI_A/D_SEL[3:0] = 0110b |            | 3.11 | 3.21 | 3.31 | V     |

|           | LVI_A/D_SEL[3:0] = 0111b |            | 3.35 | 3.46 | 3.56 | V     |

|           | LVI_A/D_SEL[3:0] = 1000b |            | 3.59 | 3.70 | 3.81 | V     |

|           | LVI_A/D_SEL[3:0] = 1001b |            | 3.84 | 3.95 | 4.07 | V     |

|           | LVI_A/D_SEL[3:0] = 1010b |            | 4.08 | 4.20 | 4.33 | V     |

|           | LVI_A/D_SEL[3:0] = 1011b |            | 4.32 | 4.45 | 4.59 | V     |

|           | LVI_A/D_SEL[3:0] = 1100b |            | 4.56 | 4.70 | 4.84 | V     |

|           | LVI_A/D_SEL[3:0] = 1101b |            | 4.83 | 4.98 | 5.13 | V     |

|           | LVI_A/D_SEL[3:0] = 1110b |            | 5.05 | 5.21 | 5.37 | V     |

|           | LVI_A/D_SEL[3:0] = 1111b |            | 5.30 | 5.47 | 5.63 | V     |

| HVI       | Trip voltage             |            | 5.57 | 5.75 | 5.92 | V     |

# Table 11-74. Voltage Monitors AC Specifications

| Parameter              | Description   | Conditions | Min | Тур | Max | Units |

|------------------------|---------------|------------|-----|-----|-----|-------|

| LVI_tr <sup>[91]</sup> | Response time |            | _   | _   | 1   | μs    |

### Notes

90. Based on device characterization (Not production tested).

91. This value is calculated, not measured.

Document Number: 001-84932 Rev. \*L Page 120 of 139

# 11.8.5 SWD Interface

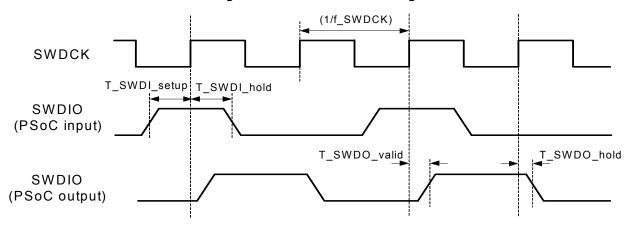

# Figure 11-80. SWD Interface Timing

Table 11-77. SWD Interface AC Specifications<sup>[95]</sup>

| Parameter    | Description                         | Conditions                                                                        | Min | Тур | Max                 | Units |

|--------------|-------------------------------------|-----------------------------------------------------------------------------------|-----|-----|---------------------|-------|

| f_SWDCK      | SWDCLK frequency                    | $3.3 \text{ V} \leq \text{V}_{DDD} \leq 5 \text{ V}$                              | -   | _   | 12 <sup>[96]</sup>  | MHz   |

|              |                                     | 1.71 V ≤ V <sub>DDD</sub> < 3.3 V                                                 | _   | _   | 7 <sup>[96]</sup>   | MHz   |

|              |                                     | $1.71~\text{V} \leq \text{V}_{DDD} \leq 3.3~\text{V},~\text{SWD over}$ USBIO pins | _   | _   | 5.5 <sup>[96]</sup> | MHz   |

| T_SWDI_setup | SWDIO input setup before SWDCK high | T = 1/f_SWDCK max                                                                 | T/4 | _   | _                   |       |

| T_SWDI_hold  | SWDIO input hold after SWDCK high   | T = 1/f_SWDCK max                                                                 | T/4 | _   | _                   |       |

| T_SWDO_valid | SWDCK high to SWDIO output          | T = 1/f_SWDCK max                                                                 | -   | _   | T/2                 |       |

| T_SWDO_hold  | SWDIO output hold after SWDCK high  | T = 1/f_SWDCK max                                                                 | 1   | _   | _                   | ns    |

### 11.8.6 TPIU Interface

Table 11-78. TPIU Interface AC Specifications<sup>[95]</sup>

| Parameter | Description                    | Conditions | Min | Тур | Max                | Units |

|-----------|--------------------------------|------------|-----|-----|--------------------|-------|

|           | TRACEPORT (TRACECLK) frequency |            | _   | _   | 33 <sup>[97]</sup> | MHz   |

|           | SWV bit rate                   |            | _   | _   | 33 <sup>[97]</sup> | Mbit  |

### Notes

<sup>95.</sup> Based on device characterization (Not production tested).

<sup>96.</sup> f\_SWDCK must also be no more than 1/3 CPU clock frequency.

<sup>97.</sup> TRACEPORT signal frequency and bit rate are limited by GPIO output frequency, see Table 11-9 on page 77.

# **Document History Page** (continued)

| Revision | Number: 00 | Orig. of<br>Change   | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|------------|----------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *H       | 4698847    | AVER /<br>MKEA / GJV | 03/24/2015         | Updated Features: Added "Extended temperature parts: –40 to 105 °C" as indented under "Temperature range (ambient)" under "Operating characteristics".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          |            |                      |                    | Updated System Integration: Updated Power System: Updated Boost Converter: Updated entire section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |            |                      |                    | Updated Electrical Specifications: Replaced "Specifications are valid for $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ and $T_{J} \le 100~^{\circ}\text{C}$ except where noted." with "Specifications are valid for $-40~^{\circ}\text{C} \le T_{A} \le 105~^{\circ}\text{c}$ and $T_{J} \le 120~^{\circ}\text{C}$ , except where noted." in all instances. Updated Device Level Specifications: Updated Table 11-2: Added details of $I_{DD}$ parameter corresponding to "T = 105 °C". Updated Figure 11-3 and Figure 11-4. Updated Power Regulators: Updated Inductive Boost Regulator: Updated Table 11-6: Updated details of $V_{BAT}$ , $I_{OUT}$ , $V_{OUT}$ , $V_{BCD}$ , |

|          |            |                      |                    | Removed V <sub>OUT</sub> : V <sub>BAT</sub> parameter and its details. Removed Table "Inductive Boost Regulator AC Specifications". Updated Table 11-7: Updated details of L <sub>BOOST</sub> , C <sub>BOOST</sub> parameters. Added C <sub>BAT</sub> parameter and its details. Added Figure 11-8, Figure 11-9, Figure 11-10, Figure 11-11, Figure 11-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |            |                      |                    | Figure 11-13, Figure 11-14. Removed Figure "Efficiency vs $I_{OUT}$ $V_{BOOST}$ = 3.3 V, $L_{BOOST}$ = 10 $\mu$ H". Removed Figure "Efficiency vs $I_{OUT}$ $V_{BOOST}$ = 3.3 V, $L_{BOOST}$ = 22 $\mu$ H". Updated Analog Peripherals: Updated Opamp: Updated Figure 11-26.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          |            |                      |                    | Updated Delta-Sigma ADC: Updated Table 11-20: Added details of CMRRb parameter corresponding to condition "T <sub>A</sub> ≤ 105 °c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |            |                      |                    | Updated Table 11-21: Added details of SINAD16int parameter corresponding to condition " $T_A \le 105$ °C".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |            |                      |                    | Updated Voltage Reference: Updated Table 11-27: Added details of V <sub>REF</sub> parameter corresponding to condition "105 °C". Updated Figure 11-39. Updated Current Digital-to-analog Converter (IDAC):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |            |                      |                    | Updated Figure 11-51, Figure 11-52, Figure 11-53, Figure 11-54, Figure 11-55, Figure 11-56. Updated Voltage Digital to Analog Converter (VDAC): Updated Figure 11-63, Figure 11-64, Figure 11-65, Figure 11-66,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |            |                      |                    | Figure 11-67, Figure 11-68. Updated Programmable Gain Amplifier: Updated Table 11-43: Added details of BW1 parameter corresponding to condition "T <sub>A</sub> ≤ 105 °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |            |                      |                    | Updated Figure 11-74. Updated Temperature Sensor: Updated Table 11-44: Replaced 85 °C with 105 °C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Document Number: 001-84932 Rev. \*L Page 136 of 139

# **Document History Page** (continued)