#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 80MHz                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                       |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                            |

| Number of I/O              | 62                                                                           |

| Program Memory Size        | 256KB (256K x 8)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 2K x 8                                                                       |

| RAM Size                   | 64K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                 |

| Data Converters            | A/D 1x20b, 2x12b; D/A 4x8b                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-LQFP                                                                     |

| Supplier Device Package    | 100-TQFP (14x14)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c5888axq-lp096 |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

In addition to the flexibility of the UDB array, PSoC also provides configurable digital blocks targeted at specific functions. For the CY8C58LP family, these blocks can include four 16-bit timers, counters, and PWM blocks; I<sup>2</sup>C slave, master, and multimaster; Full-Speed USB; and Full CAN 2.0.

For more details on the peripherals see the Example Peripherals on page 40 of this datasheet. For information on UDBs, DSI, and other digital blocks, see the Digital Subsystem on page 40 of this datasheet.

PSoC's analog subsystem is the second half of its unique configurability. All analog performance is based on a highly accurate absolute voltage reference with less than 0.1% error over temperature and voltage. The configurable analog subsystem includes:

- Analog muxes

- Comparators

- Analog mixers

- Voltage references

- ADCs

- DACs

- Digital filter block (DFB)

All GPIO pins can route analog signals into and out of the device using the internal analog bus. This allows the device to interface up to 62 discrete analog signals. One of the ADCs in the analog subsystem is a fast, accurate, configurable delta-sigma ADC with these features:

- Less than 100-µV offset

- A gain error of 0.2%

- Integral non linearity (INL) less than ±2 LSB

- Differential non linearity (DNL) less than ±1 LSB

- SINAD better than 84 dB in 16-bit mode

This converter addresses a wide variety of precision analog applications including some of the most demanding sensors.

The CY8C58LP family also offers up to two SAR ADCs. Featuring 12-bit conversions at up to 1 M samples per second, they also offer low nonlinearity and offset errors and SNR better than 70 dB. They are well-suited for a variety of higher speed analog applications.

The output of any of the ADCs can optionally feed the programmable DFB via DMA without CPU intervention. You can configure the DFB to perform IIR and FIR digital filters and several user defined custom functions. The DFB can implement filters with up to 64 taps. It can perform a 48-bit multiply-accumulate (MAC) operation in one clock cycle.

Four high-speed voltage or current DACs support 8-bit output signals at an update rate of up to 8 Msps. They can be routed out of any GPIO pin. You can create higher resolution voltage PWM DAC outputs using the UDB array. This can be used to create a pulse width modulated (PWM) DAC of up to 10 bits, at up to 48 kHz. The digital DACs in each UDB support PWM, PRS, or delta-sigma algorithms with programmable widths.

In addition to the ADCs, DACs, and DFB, the analog subsystem provides multiple:

- Comparators

- Uncommitted opamps

- Configurable switched capacitor/continuous time (SC/CT) blocks. These support:

- Transimpedance amplifiers

- Programmable gain amplifiers

- Mixers

- Delta Other similar analog components

See the "Analog Subsystem" section on page 51 of this datasheet for more details.

PSoC's CPU subsystem is built around a 32-bit three-stage pipelined ARM Cortex-M3 processor running at up to 80 MHz. The Cortex-M3 includes a tightly integrated nested vectored interrupt controller (NVIC) and various debug and trace modules. The overall CPU subsystem includes a DMA controller, flash cache, and RAM. The NVIC provides low latency, nested interrupts, and tail-chaining of interrupts and other features to increase the efficiency of interrupt handling. The DMA controller enables peripherals to exchange data without CPU involvement. This allows the CPU to run slower (saving power) or use those CPU cycles to improve the performance of firmware algorithms. The flash cache also reduces system power consumption by allowing less frequent flash access.

PSoC's nonvolatile subsystem consists of flash, byte-writeable EEPROM, and nonvolatile configuration options. It provides up to 256 KB of on-chip flash. The CPU can reprogram individual blocks of flash, enabling boot loaders. You can enable an ECC for high reliability applications. A powerful and flexible protection model secures the user's sensitive information, allowing selective memory block locking for read and write protection. Two KB of byte-writable EEPROM is available on-chip to store application data. Additionally, selected configuration options such as boot speed and pin drive mode are stored in nonvolatile memory. This allows settings to activate immediately after POR.

The three types of PSoC I/O are extremely flexible. All I/Os have many drive modes that are set at POR. PSoC also provides up to four I/O voltage domains through the V<sub>DDIO</sub> pins. Every GPIO has analog I/O, LCD drive, CapSense, flexible interrupt generation, slew rate control, and digital I/O capability. The SIOs on PSoC allow  $V_{OH}$  to be set independently of  $V_{DDIO}$  when used as outputs. When SIOs are in input mode they are high impedance. This is true even when the device is not powered or when the pin voltage goes above the supply voltage. This makes the SIO ideally suited for use on an I<sup>2</sup>C bus where the PSoC may not be powered when other devices on the bus are. The SIO pins also have high current sink capability for applications such as LED drives. The programmable input threshold feature of the SIO can be used to make the SIO function as a general purpose analog comparator. For devices with FS USB, the USB physical interface is also provided (USBIO). When not using USB, these pins may also be used for limited digital functionality and device programming. All the features of the PSoC I/Os are covered in detail in the I/O System and Routing on page 33 of this datasheet.

# 3. Pin Descriptions

**IDAC0, IDAC1, IDAC2, IDAC3.** Low-resistance output pin for high-current DACs (IDAC).

**Opamp0out, Opamp1out, Opamp2out, Opamp3out.** High current output of uncommitted opamp.<sup>[7]</sup>

Extref0, Extref1. External reference input to the analog system.

SAR0 EXTREF, SAR1 EXTREF. External references for SAR ADCs

**Opamp0-, Opamp1-, Opamp2-, Opamp3-.** Inverting input to uncommitted opamp.

**Opamp0+, Opamp1+, Opamp2+, Opamp3+.** Noninverting input to uncommitted opamp.

**GPIO.** Provides interfaces to the CPU, digital peripherals, analog peripherals, interrupts, LCD segment drive, and CapSense.<sup>[7]</sup>

**I2C0: SCL, I2C1: SCL.** I<sup>2</sup>C SCL line providing wake from sleep on an address match. Any I/O pin can be used for I<sup>2</sup>C SCL if wake from sleep is not required.

**I2C0: SDA, I2C1: SDA.**  $I^2C$  SDA line providing wake from sleep on an address match. Any I/O pin can be used for  $I^2C$  SDA if wake from sleep is not required.

Ind. Inductor connection to boost pump.

kHz XTAL: Xo, kHz XTAL: Xi. 32.768-kHz crystal oscillator pin.

**MHz XTAL: Xo, MHz XTAL: Xi.** 4 to 25-MHz crystal oscillator pin.

**nTRST.** Optional JTAG Test Reset programming and debug port connection to reset the JTAG connection.

**SIO.** Provides interfaces to the CPU, digital peripherals and interrupts with a programmable high threshold voltage, analog comparator, high sink current, and high impedance state when the device is unpowered.

**SWDCK.** SWD Clock programming and debug port connection.

**SWDIO.** SWD Input and Output programming and debug port connection.

**TCK.** JTAG Test Clock programming and debug port connection.

**TDI.** JTAG Test Data In programming and debug port connection.

**TDO.** JTAG Test Data Out programming and debug port connection.

**TMS.** JTAG Test Mode Select programming and debug port connection.

**TRACECLK.** Cortex-M3 TRACEPORT connection, clocks TRACEDATA pins.

**TRACEDATA[3:0].** Cortex-M3 TRACEPORT connections, output data.

SWV. SWV output.

**USBIO**, **D+.** Provides D+ connection directly to a USB 2.0 bus. May be used as a digital I/O pin; it is powered from VDDD instead of from a VDDIO. Pins are Do Not Use (DNU) on devices without USB.

**USBIO**, **D-.** Provides D- connection directly to a USB 2.0 bus. May be used as a digital I/O pin; it is powered from VDDD instead of from a VDDIO. Pins are Do Not Use (DNU) on devices without USB.

VBOOST. Power sense connection to boost pump.

VBAT. Battery supply to boost pump.

VCCA. Output of the analog core regulator or the input to the analog core. Requires a 1uF capacitor to VSSA. The regulator output is not designed to drive external circuits. Note that if you use the device with an external core regulator (externally regulated mode), the voltage applied to this pin must not exceed the allowable range of 1.71 V to 1.89 V. When using the internal core regulator, (internally regulated mode, the default), do not tie any power to this pin. For details see Power System on page 26.

VCCD. Output of the digital core regulator or the input to the digital core. The two VCCD pins must be shorted together, with the trace between them as short as possible, and a 1uF capacitor to VSSD. The regulator output is not designed to drive external circuits. Note that if you use the device with an external core regulator (externally regulated mode), the voltage applied to this pin must not exceed the allowable range of 1.71 V to 1.89 V. When using the internal core regulator (internally regulated mode, the default), do not tie any power to this pin. For details see Power System on page 26.

VDDA. Supply for all analog peripherals and analog core regulator. VDDA must be the highest voltage present on the device. All other supply pins must be less than or equal to VDDA.

**VDDD.** Supply for all digital peripherals and digital core regulator. VDDD must be less than or equal to VDDA.

VSSA. Ground for all analog peripherals.

**VSSB.** Ground connection for boost pump.

VSSD. Ground for all digital logic and I/O pins.

**VDDIO0, VDDIO1, VDDIO2, VDDIO3.** Supply for I/O pins. Each VDDIO must be tied to a valid operating voltage (1.71 V to 5.5 V), and must be less than or equal to VDDA.

XRES. External reset pin. Active low with internal pull-up.

Note

7. GPIOs with opamp outputs are not recommended for use with CapSense.

#### 4.3.4.2 Auto Repeat DMA

Auto repeat DMA is typically used when a static pattern is repetitively read from system memory and written to a peripheral. This is done with a single TD that chains to itself.

#### 4.3.4.3 Ping Pong DMA

A ping pong DMA case uses double buffering to allow one buffer to be filled by one client while another client is consuming the data previously received in the other buffer. In its simplest form, this is done by chaining two TDs together so that each TD calls the opposite TD when complete.

#### 4.3.4.4 Circular DMA

Circular DMA is similar to ping pong DMA except it contains more than two buffers. In this case there are multiple TDs; after the last TD is complete it chains back to the first TD.

#### 4.3.4.5 Indexed DMA

In an indexed DMA case, an external master requires access to locations on the system bus as if those locations were shared memory. As an example, a peripheral may be configured as an SPI or I<sup>2</sup>C slave where an address is received by the external master. That address becomes an index or offset into the internal system bus memory space. This is accomplished with an initial "address fetch" TD that reads the target address location from the peripheral and writes that value into a subsequent TD in the chain. This modifies the TD chain on the fly. When the "address fetch" TD completes it moves on to the next TD, which has the new address information embedded in it. This TD then carries out the data transfer with the address location required by the external master.

#### 4.3.4.6 Scatter Gather DMA

In the case of scatter gather DMA, there are multiple noncontiguous sources or destinations that are required to effectively carry out an overall DMA transaction. For example, a packet may need to be transmitted off of the device and the packet elements, including the header, payload, and trailer, exist

in various noncontiguous locations in memory. Scatter gather DMA allows the segments to be concatenated together by using multiple TDs in a chain. The chain gathers the data from the multiple locations. A similar concept applies for the reception of data onto the device. Certain parts of the received data may need to be scattered to various locations in memory for software processing convenience. Each TD in the chain specifies the location for each discrete element in the chain.

#### 4.3.4.7 Packet Queuing DMA

Packet queuing DMA is similar to scatter gather DMA but specifically refers to packet protocols. With these protocols, there may be separate configuration, data, and status phases associated with sending or receiving a packet.

For instance, to transmit a packet, a memory mapped configuration register can be written inside a peripheral, specifying the overall length of the ensuing data phase. The CPU can set up this configuration information anywhere in system memory and copy it with a simple TD to the peripheral. After the configuration phase, a data phase TD (or a series of data phase TDs) can begin (potentially using scatter gather). When the data phase TD(s) finish, a status phase TD can be invoked that reads some memory mapped status information from the peripheral and copies it to a location in system memory specified by the CPU for later inspection. Multiple sets of configuration, data, and status phase "subchains" can be strung together to create larger chains that transmit multiple packets in this way. A similar concept exists in the opposite direction to receive the packets.

#### 4.3.4.8 Nested DMA

One TD may modify another TD, as the TD configuration space is memory mapped similar to any other peripheral. For example, a first TD loads a second TD's configuration and then calls the second TD. The second TD moves data as required by the application. When complete, the second TD calls the first TD, which again updates the second TD's configuration. This process repeats as often as necessary.

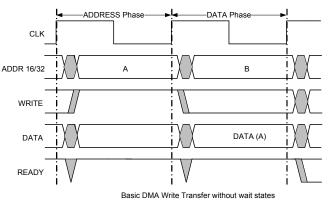

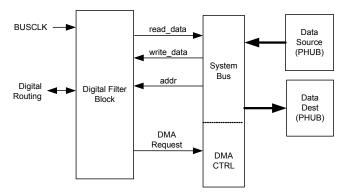

## 7.9 Digital Filter Block

Some devices in the CY8C58LP family of devices have a dedicated HW accelerator block used for digital filtering. The DFB has a dedicated multiplier and accumulator that calculates a 24-bit by 24-bit multiply accumulate in one system clock cycle. This enables the mapping of a direct form FIR filter that approaches a computation rate of one FIR tap for each clock cycle. The MCU can implement any of the functions performed by this block, but at a slower rate that consumes significant MCU bandwidth.

The PSoC Creator interface provides a wizard to implement FIR and IIR digital filters with coefficients for LPF, BPF, HPF, Notch and arbitrary shape filters. 64 pairs of data and coefficients are stored. This enables a 64 tap FIR filter or up to 4 16 tap filters of either FIR or IIR formulation.

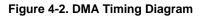

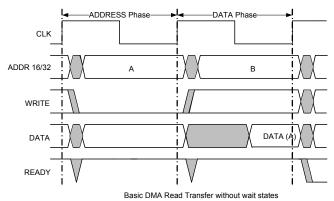

The typical use model is for data to be supplied to the DFB over the system bus from another on-chip system data source such as an ADC. The data typically passes through main memory or is directly transferred from another chip resource through DMA. The DFB processes this data and passes the result to another on chip resource such as a DAC or main memory through DMA on the system bus.

Data movement in or out of the DFB is typically controlled by the system DMA controller but can be moved directly by the MCU.

# 8. Analog Subsystem

The analog programmable system creates application specific combinations of both standard and advanced analog signal processing blocks. These blocks are then interconnected to each other and also to any pin on the device, providing a high level of design flexibility and IP security. The features of the analog subsystem are outlined here to provide an overview of capabilities and architecture.

- Flexible, configurable analog routing architecture provided by analog globals, analog mux bus, and analog local buses

- High resolution Delta-Sigma ADC

- Two successive approximation (SAR) ADCs

- Four 8-bit DACs that provide either voltage or current output

- Four comparators with optional connection to configurable LUT outputs

- Four configurable switched capacitor/continuos time (SC/CT) blocks for functions that include opamp, unity gain buffer, programmable gain amplifier, transimpedance amplifier, and mixer

- Four opamps for internal use and connection to GPIO that can be used as high current output buffers

- CapSense subsystem to enable capacitive touch sensing

- Precision reference for generating an accurate analog voltage for internal analog blocks

#### 8.7.1 LCD Segment Pin Driver

Each GPIO pin contains an LCD driver circuit. The LCD driver buffers the appropriate output of the LCD DAC to directly drive the glass of the LCD. A register setting determines whether the pin is a common or segment. The pin's LCD driver then selects one of the six bias voltages to drive the I/O pin, as appropriate for the display data.

#### 8.7.2 Display Data Flow

The LCD segment driver system reads display data and generates the proper output voltages to the LCD glass to produce the desired image. Display data resides in a memory buffer in the system SRAM. Each time you need to change the common and segment driver voltages, the next set of pixel data moves from the memory buffer into the Port Data Registers via DMA.

#### 8.7.3 UDB and LCD Segment Control

A UDB is configured to generate the global LCD control signals and clocking. This set of signals is routed to each LCD pin driver through a set of dedicated LCD global routing channels. In addition to generating the global LCD control signals, the UDB also produces a DMA request to initiate the transfer of the next frame of LCD data.

#### 8.7.4 LCD DAC

The LCD DAC generates the contrast control and bias voltage for the LCD system. The LCD DAC produces up to five LCD drive voltages plus ground, based on the selected bias ratio. The bias voltages are driven out to GPIO pins on a dedicated LCD bias bus, as required.

#### 8.8 CapSense

The CapSense system provides a versatile and efficient means for measuring capacitance in applications such as touch sense buttons, sliders, proximity detection, etc. The CapSense system uses a configuration of system resources, including a few hardware functions primarily targeted for CapSense. Specific resource usage is detailed in the CapSense component in PSoC Creator.

A capacitive sensing method using a Delta-Sigma Modulator (CSD) is used. It provides capacitance sensing using a switched capacitor technique with a delta-sigma modulator to convert the sensing current to a digital code.

#### 8.9 Temp Sensor

Die temperature is used to establish programming parameters for writing flash. Die temperature is measured using a dedicated sensor based on a forward biased transistor. The temperature sensor has its own auxiliary ADC.

## 8.10 DAC

The CY8C58LP parts contain four Digital to Analog Convertors (DACs). Each DAC is 8-bit and can be configured for either voltage or current output. The DACs support CapSense, power supply regulation, and waveform generation. Each DAC has the following features.

- Adjustable voltage or current output in 255 steps

- Programmable step size (range selection)

- Eight bits of calibration to correct ± 25% of gain error

- Source and sink option for current output

- 8 Msps conversion rate for current output

- 1 Msps conversion rate for voltage output

- Monotonic in nature

- Data and strobe inputs can be provided by the CPU or DMA, or routed directly from the DSI

- Dedicated low-resistance output pin for high-current mode

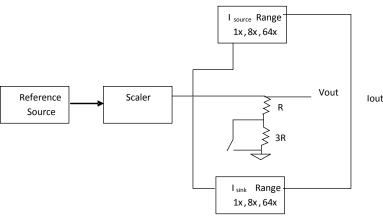

## Figure 8-12. DAC Block Diagram

#### 8.10.1 Current DAC

The current DAC (IDAC) can be configured for the ranges 0 to 31.875  $\mu$ A, 0 to 255  $\mu$ A, and 0 to 2.04 mA. The IDAC can be configured to source or sink current.

#### 8.10.2 Voltage DAC

For the voltage DAC (VDAC), the current DAC output is routed through resistors. The two ranges available for the VDAC are 0 to 1.02 V and 0 to 4.08 V. In voltage mode any load connected to the output of a DAC should be purely capacitive (the output of the VDAC is not buffered).

#### Table 11-2. DC Specifications (continued)

| Parameter                       | Description                                                                                                                                                                                      | Conditio                                                          | ns         | Min | Тур | Max | Units |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------|-----|-----|-----|-------|

| I <sub>DD</sub> <sup>[22]</sup> | Sleep Mode <sup>[23]</sup>                                                                                                                                                                       | •                                                                 |            |     |     |     |       |

|                                 |                                                                                                                                                                                                  | V <sub>DD</sub> = V <sub>DDIO</sub> =<br>4.5–5.5 V                | T = -40 °C | _   | 1.9 | 3.1 | μA    |

|                                 |                                                                                                                                                                                                  | 4.5–5.5 V                                                         | T = 25 °C  | -   | 2.4 | 3.6 |       |

|                                 |                                                                                                                                                                                                  |                                                                   | T = 85 °C  | _   | 5   | 16  |       |

|                                 | CPU = OFF<br>RTC = ON (= ECO32K ON in low-power mode)                                                                                                                                            |                                                                   | T = 105 °C | _   | 5   | 16  |       |

|                                 | RTC = ON (= ECO32K ON, in low-power mode)<br>Sleep timer = ON (= ILO ON at 1 kHz) <sup>[24]</sup>                                                                                                | V <sub>DD</sub> = V <sub>DDIO</sub> =<br>2.7–3.6 V                | T = -40 °C | _   | 1.7 | 3.1 |       |

|                                 | WDT = OFF<br>I <sup>2</sup> C Wake = OFF                                                                                                                                                         | 2.7–3.6 V                                                         | T = 25 °C  | -   | 2   | 3.6 |       |

|                                 | Comparator = OFF                                                                                                                                                                                 | T                                                                 | T = 85 °C  | _   | 4.2 | 16  |       |

|                                 | POR = ON                                                                                                                                                                                         |                                                                   | T = 105 °C | _   | 4.2 | 16  |       |

|                                 | Boost = OFF<br>SIO pins in single ended input, unregulated output mode                                                                                                                           |                                                                   | T = -40 °C | _   | 1.6 | 3.1 | -     |

|                                 |                                                                                                                                                                                                  | 1.71–1.95 V                                                       | T = 25 °C  | _   | 1.9 | 3.6 |       |

|                                 |                                                                                                                                                                                                  |                                                                   | T = 85 °C  | _   | 4.2 | 16  |       |

|                                 |                                                                                                                                                                                                  | Т                                                                 | T = 105 °C | _   | 4.2 | 16  |       |

|                                 | Comparator = ON<br>CPU = OFF<br>RTC = OFF<br>Sleep timer = OFF<br>WDT = OFF<br>I <sup>2</sup> C Wake = OFF<br>POR = ON<br>Boost = OFF<br>SIO pins in single ended input, unregulated output mode | V <sub>DD</sub> = V <sub>DDD</sub> =<br>2.7–3.6 V <sup>[25]</sup> | T = 25 °C  | _   | 3   | 4.2 | μΑ    |

|                                 | I <sup>2</sup> C Wake = ON<br>CPU = OFF<br>RTC = OFF<br>Sleep timer = OFF<br>WDT = OFF<br>Comparator = OFF<br>POR = ON<br>Boost = OFF<br>SIO pins in single ended input, unregulated output mode | V <sub>DD</sub> = V <sub>DDD</sub> =<br>2.7-3.6 V <sup>[25]</sup> | T = 25 °C  | _   | 1.7 | 3.6 | μΑ    |

Notes

- Notes

22. The current consumption of additional peripherals that are implemented only in programmed logic blocks can be found in their respective datasheets, available in PSoC Creator, the integrated design environment. To estimate total current, find CPU current at frequency of interest and add peripheral currents for your particular system from the device datasheet and component datasheets.

23. If V<sub>CCD</sub> and V<sub>CCA</sub> are externally regulated, the voltage difference between V<sub>CCD</sub> and V<sub>CCA</sub> must be less than 50 mV.

24. Sleep timer generates periodic interrupts to wake up the CPU. This specification applies only to those times that the CPU is off.

25. Based on device characterization (Not production tested).

| Parameter          | Description                                                                 | Conditions     | Min  | Тур  | Max  | Units |

|--------------------|-----------------------------------------------------------------------------|----------------|------|------|------|-------|

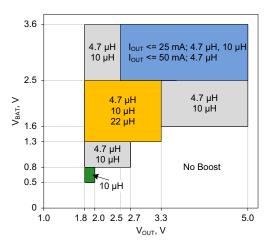

| L <sub>BOOST</sub> | Boost inductor                                                              | 4.7 μH nominal | 3.7  | 4.7  | 5.7  | μH    |

|                    |                                                                             | 10 μH nominal  | 8.0  | 10.0 | 12.0 | μH    |

|                    |                                                                             | 22 μH nominal  | 17.0 | 22.0 | 27.0 | μH    |

| C <sub>BOOST</sub> | Total capacitance sum of $V_{DDD}$ , $V_{DDA}$ , $V_{DDIO}$ <sup>[32]</sup> |                | 17.0 | 26.0 | 31.0 | μF    |

| C <sub>BAT</sub>   | Battery filter capacitor                                                    |                | 17.0 | 22.0 | 27.0 | μF    |

| I <sub>F</sub>     | Schottky diode average<br>forward current                                   |                | 1.0  | _    | -    | A     |

| V <sub>R</sub>     | Schottky reverse voltage                                                    |                | 20.0 | -    | -    | V     |

#### Table 11-7. Recommended External Components for Boost Circuit

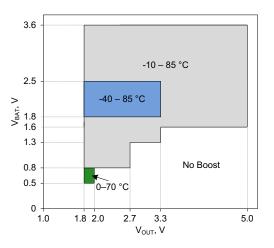

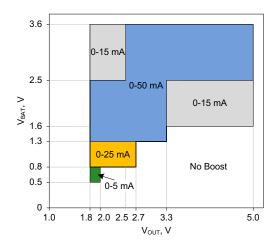

## Figure 11-8. $T_{A}$ range over $V_{BAT}\,$ and $V_{OUT}$

## Figure 11-10. L\_{BOOST} values over $V_{BAT}$ and $V_{OUT}$

## Figure 11-9. $I_{OUT}$ range over $V_{BAT}$ and $V_{OUT}$

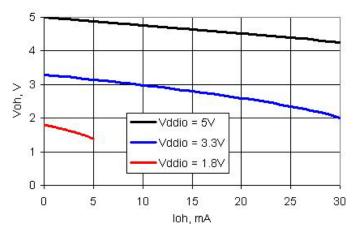

Figure 11-17. SIO Output High Voltage and Current, Unregulated Mode

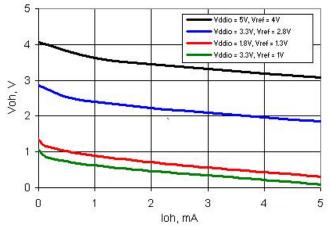

Figure 11-19. SIO Output High Voltage and Current, Regulated Mode

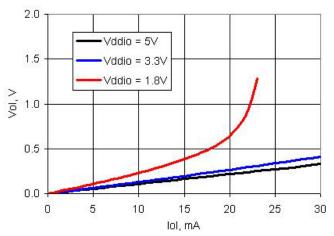

Figure 11-18. SIO Output Low Voltage and Current, Unregulated Mode

# Table 11-11 SIO AC Specifications<sup>[39]</sup>

| Parameter | Description                                                                                        | Conditions                               | Min | Тур | Max | Units |

|-----------|----------------------------------------------------------------------------------------------------|------------------------------------------|-----|-----|-----|-------|

| TriseF    | Rise time in fast strong mode (90/10%)                                                             | Cload = 25 pF, $V_{DDIO}$ = 3.3 V        | -   | -   | 12  | ns    |

| TfallF    | Fall time in fast strong mode (90/10%)                                                             | Cload = 25 pF, $V_{DDIO}$ = 3.3 V        | -   | -   | 12  | ns    |

| TriseS    | Rise time in slow strong mode (90/10%)                                                             | Cload = 25 pF, $V_{DDIO}$ = 3.0 V        | -   | -   | 75  | ns    |

| TfallS    | Fall time in slow strong mode (90/10%)                                                             | Cload = 25 pF, $V_{DDIO}$ = 3.0 V        | -   | -   | 60  | ns    |

|           | SIO output operating frequency                                                                     |                                          |     |     |     |       |

|           | 2.7 V < V <sub>DDIO</sub> < 5.5 V, Unregu-<br>lated output (GPIO) mode, fast<br>strong drive mode  | 90/10% V <sub>DDIO</sub> into 25 pF      | _   | -   | 33  | MHz   |

|           | 1.71 V < V <sub>DDIO</sub> < 2.7 V, Unregu-<br>lated output (GPIO) mode, fast<br>strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF      | -   | -   | 16  | MHz   |

|           | 3.3 V < V <sub>DDIO</sub> < 5.5 V, Unregu-<br>lated output (GPIO) mode, slow<br>strong drive mode  | 90/10% V <sub>DDIO</sub> into 25 pF      | -   | -   | 5   | MHz   |

| Fsioout   | 1.71 V < V <sub>DDIO</sub> < 3.3 V, Unregu-<br>lated output (GPIO) mode, slow<br>strong drive mode | 90/10% V <sub>DDIO</sub> into 25 pF      | -   | -   | 4   | MHz   |

|           | 2.7 V < V <sub>DDIO</sub> < 5.5 V, Regulated<br>output mode, fast strong drive<br>mode             | Output continuously switching into 25 pF | -   | -   | 20  | MHz   |

|           | 1.71 V < V <sub>DDIO</sub> < 2.7 V, Regulated<br>output mode, fast strong drive<br>mode            | Output continuously switching into 25 pF | -   | -   | 10  | MHz   |

|           | 1.71 V < V <sub>DDIO</sub> < 5.5 V, Regulated<br>output mode, slow strong drive<br>mode            | Output continuously switching into 25 pF | _   | -   | 2.5 | MHz   |

| Fsioin    | SIO input operating frequency                                                                      | · · · · ·                                |     |     |     | •     |

| 3011      | 1.71 V <u>&lt;</u> V <sub>DDIO</sub> <u>&lt;</u> 5.5 V                                             | 90/10% V <sub>DDIO</sub>                 | _   | -   | 33  | MHz   |

<sup>39.</sup> Based on device characterization (Not production tested).

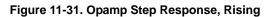

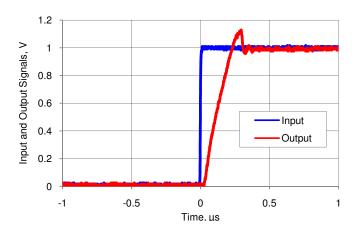

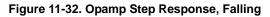

Table 11-19. Opamp AC Specifications<sup>[44]</sup>

| Parameter      | Description            | Conditions                                   | Min | Тур | Max | Units     |

|----------------|------------------------|----------------------------------------------|-----|-----|-----|-----------|

| GBW            | Gain-bandwidth product | Power mode = minimum, 15 pF load             | 1   | -   | -   | MHz       |

|                |                        | Power mode = low, 15 pF load                 | 2   | -   | -   | MHz       |

|                |                        | Power mode = medium, 200 pF load             | 1   | -   | -   | MHz       |

|                |                        | Power mode = high, 200 pF load               | 3   | _   | -   | MHz       |

| SR             | Slew rate, 20% - 80%   | Power mode = minimum, 15 pF load             | 1.1 | -   | -   | V/µs      |

|                |                        | Power mode = low, 15 pF load                 | 1.1 | -   | -   | V/µs      |

|                |                        | Power mode = medium, 200 pF load             | 0.9 | -   | -   | V/µs      |

|                |                        | Power mode = high, 200 pF load               | 3   | -   | -   | V/µs      |

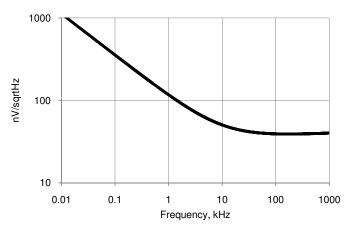

| e <sub>n</sub> | Input noise density    | Power mode = high, Vdda = 5 V, at<br>100 kHz | _   | 45  | -   | nV/sqrtHz |

# Figure 11-30. Opamp Noise vs Frequency, Power Mode = High, Vdda = 5V

Note 44. Based on device characterization (Not production tested).

## 11.6.3 Pulse Width Modulation

**CYPRESS**

The following specifications apply to the Timer/Counter/PWM peripheral, in PWM mode. PWM components can also be implemented in UDBs; for more information, see the PWM component datasheet in PSoC Creator.

## Table 11-51. PWM DC Specifications<sup>[74]</sup>

| Parameter | Description               | Conditions                                  | Min | Тур | Max | Units |

|-----------|---------------------------|---------------------------------------------|-----|-----|-----|-------|

|           | Block current consumption | 16-bit PWM, at listed input clock frequency | _   | _   | -   | μA    |

|           | 3 MHz                     |                                             | -   | 15  | -   | μA    |

|           | 12 MHz                    |                                             | -   | 60  | _   | μA    |

|           | 48 MHz                    |                                             | -   | 260 | _   | μA    |

|           | 80 MHz                    |                                             | _   | 360 | -   | μA    |

## Table 11-52. PWM AC Specifications<sup>[74]</sup>

| Parameter | Description                        | Conditions | Min | Тур | Max   | Units |

|-----------|------------------------------------|------------|-----|-----|-------|-------|

|           | Operating frequency                |            | DC  | -   | 80.01 | MHz   |

|           | Pulse width <sup>[75]</sup>        |            | 15  | -   | -     | ns    |

|           | Pulse width (external)             |            | 30  | -   | -     | ns    |

|           | Kill pulse width <sup>[75]</sup>   |            | 15  | -   | -     | ns    |

|           | Kill pulse width (external)        |            | 30  | -   | -     | ns    |

|           | Enable pulse width <sup>[75]</sup> |            | 15  | -   | -     | ns    |

|           | Enable pulse width (external)      |            | 30  | -   | -     | ns    |

|           | Reset pulse width <sup>[75]</sup>  |            | 15  | -   | -     | ns    |

|           | Reset pulse width (external)       |            | 30  | -   | -     | ns    |

## 11.6.4 <sup>2</sup>C

## Table 11-53. Fixed I<sup>2</sup>C DC Specifications<sup>[74]</sup>

| Parameter | Description               | Conditions                       | Min | Тур | Max | Units |

|-----------|---------------------------|----------------------------------|-----|-----|-----|-------|

|           | Block current consumption | Enabled, configured for 100 kbps | -   | -   | 250 | μA    |

|           |                           | Enabled, configured for 400 kbps | -   | -   | 260 | μA    |

## Table 11-54. Fixed I<sup>2</sup>C AC Specifications<sup>[76]</sup>

| Parameter | Description | Conditions | Min | Тур | Max | Units |

|-----------|-------------|------------|-----|-----|-----|-------|

|           | Bit rate    |            | -   | -   | 1   | Mbps  |

11.6.5 Controller Area Network

## Table 11-55. CAN DC Specifications<sup>[74, 77]</sup>

| Parameter       | Description               | Conditions | Min | Тур | Max | Units |

|-----------------|---------------------------|------------|-----|-----|-----|-------|

| I <sub>DD</sub> | Block current consumption |            | 1   | -   | 200 | μA    |

## Table 11-56. CAN AC Specifications<sup>[74, 77]</sup>

| Parameter | Description | Conditions          | Min | Тур | Max | Units |

|-----------|-------------|---------------------|-----|-----|-----|-------|

|           | Bit rate    | Minimum 8 MHz clock | -   | -   | 1   | Mbit  |

#### Notes

74. Based on device characterization (Not production tested).

75. For correct operation, the minimum Timer/Counter/PWM input pulse width is the period of bus clock.

76. Rise/fall time matching (TR) not guaranteed, see Table 11-15 on page 84. 77. Refer to ISO 11898 specification for details.

## 11.6.8 Universal Digital Blocks (UDBs)

PSoC Creator provides a library of pre-built and tested standard digital peripherals (UART, SPI, LIN, PRS, CRC, timer, counter, PWM, AND, OR, and so on) that are mapped to the UDB array. See the component datasheets in PSoC Creator for full AC/DC specifications, APIs, and example code.

## Table 11-60. UDB AC Specifications<sup>[79]</sup>

| Parameter              | Description                                                   | Conditions                                       | Min | Тур | Max   | Units |

|------------------------|---------------------------------------------------------------|--------------------------------------------------|-----|-----|-------|-------|

| Datapath Per           | formance                                                      |                                                  |     |     |       |       |

| F <sub>MAX_TIMER</sub> | Maximum frequency of 16-bit timer in a UDB pair               |                                                  | -   | -   | 67.01 | MHz   |

| F <sub>MAX_ADDER</sub> | Maximum frequency of 16-bit adder in a UDB pair               |                                                  | -   | -   | 67.01 | MHz   |

| F <sub>MAX_CRC</sub>   | Maximum frequency of 16-bit<br>CRC/PRS in a UDB pair          |                                                  | -   | -   | 67.01 | MHz   |

| PLD Perform            | ance                                                          |                                                  |     |     |       |       |

| F <sub>MAX_PLD</sub>   | Maximum frequency of a two-pass<br>PLD function in a UDB pair |                                                  | _   | -   | 67.01 | MHz   |

| Clock to Outp          | but Performance                                               |                                                  |     |     |       |       |

| t <sub>CLK_OUT</sub>   | Propagation delay for clock in to data out, see Figure 11-76. | 25 °C, $V_{DDD} \ge 2.7 V$                       | -   | 20  | 25    | ns    |

| t <sub>CLK_OUT</sub>   | Propagation delay for clock in to data out, see Figure 11-76. | Worst-case placement, routing, and pin selection | _   | -   | 55    | ns    |

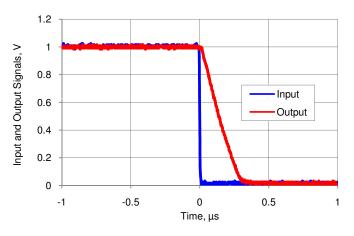

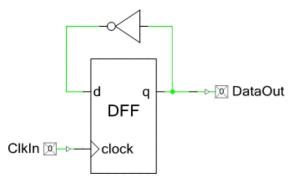

#### Figure 11-76. Clock to Output Performance

Note

<sup>79.</sup> Based on device characterization (Not production tested).

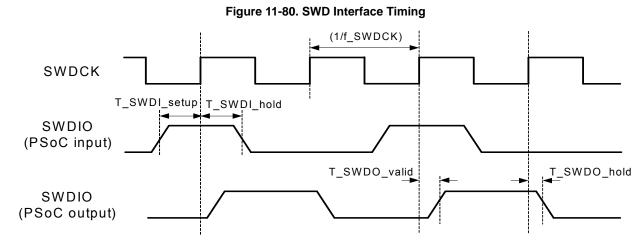

## 11.8.5 SWD Interface

## Table 11-77. SWD Interface AC Specifications<sup>[95]</sup>

| Parameter    | Description                         | Conditions                                         | Min | Тур | Max                 | Units |

|--------------|-------------------------------------|----------------------------------------------------|-----|-----|---------------------|-------|

| f_SWDCK      | SWDCLK frequency                    | $3.3~V \leq V_{DDD} \leq 5~V$                      | -   | -   | 12 <sup>[96]</sup>  | MHz   |

|              |                                     | $1.71~V \leq V_{DDD} < 3.3~V$                      | -   | -   | 7 <sup>[96]</sup>   | MHz   |

|              |                                     | 1.71 V $\leq$ V_{DDD} < 3.3 V, SWD over USBIO pins | -   | -   | 5.5 <sup>[96]</sup> | MHz   |

| T_SWDI_setup | SWDIO input setup before SWDCK high | T = 1/f_SWDCK max                                  | T/4 | -   | -                   |       |

| T_SWDI_hold  | SWDIO input hold after SWDCK high   | T = 1/f_SWDCK max                                  | T/4 | -   | -                   |       |

| T_SWDO_valid | SWDCK high to SWDIO output          | T = 1/f_SWDCK max                                  | -   | -   | T/2                 |       |

| T_SWDO_hold  | SWDIO output hold after SWDCK high  | T = 1/f_SWDCK max                                  | 1   | -   | _                   | ns    |

## 11.8.6 TPIU Interface

## Table 11-78. TPIU Interface AC Specifications<sup>[95]</sup>

| Parameter | Description                    | Conditions | Min | Тур | Max                | Units |

|-----------|--------------------------------|------------|-----|-----|--------------------|-------|

|           | TRACEPORT (TRACECLK) frequency |            | -   | -   | 33 <sup>[97]</sup> | MHz   |

|           | SWV bit rate                   |            | _   | -   | 33 <sup>[97]</sup> | Mbit  |

Notes

95. Based on device characterization (Not production tested).

96. f\_SWDCK must also be no more than 1/3 CPU clock frequency.

97. TRACEPORT signal frequency and bit rate are limited by GPIO output frequency, see Table 11-9 on page 77.

## 11.9 Clocking

Specifications are valid for –40 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C and T<sub>J</sub>  $\leq$  120 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted. Unless otherwise specified, all charts and graphs show typical values

11.9.1 Internal Main Oscillator

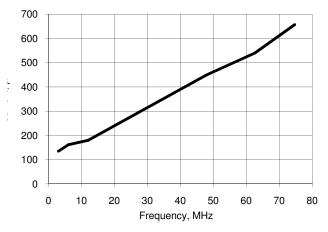

#### Table 11-79. IMO DC Specifications<sup>[98]</sup>

| Parameter | Description           | Conditions                         | Min | Тур | Max | Units |  |  |  |

|-----------|-----------------------|------------------------------------|-----|-----|-----|-------|--|--|--|

|           | Supply current        |                                    |     |     |     |       |  |  |  |

|           | 74.7 MHz              |                                    | -   | _   | 730 | μA    |  |  |  |

|           | 62.6 MHz              |                                    | I   | _   | 600 | μA    |  |  |  |

|           | 48 MHz                |                                    | -   | _   | 500 | μA    |  |  |  |

| lcc_imo   | 24 MHz – USB mode     | With oscillator locking to USB bus | -   | _   | 500 | μA    |  |  |  |

|           | 24 MHz – non-USB mode |                                    | I   | _   | 300 | μA    |  |  |  |

|           | 12 MHz                |                                    | -   | _   | 200 | μA    |  |  |  |

|           | 6 MHz                 |                                    | -   | _   | 180 | μA    |  |  |  |

|           | 3 MHz                 |                                    | -   | _   | 150 | μA    |  |  |  |

## Figure 11-81. IMO Current vs. Frequency

Table 11-80. IMO AC Specifications

| Parameter                        | Description                                                         | Conditions                                                                                                                     | Min   | Тур | Max  | Units |  |  |

|----------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------|-----|------|-------|--|--|

|                                  | IMO frequency stability (with factory trim)                         |                                                                                                                                |       |     |      |       |  |  |

|                                  | 74.7 MHz                                                            |                                                                                                                                | -7    | _   | 7    | %     |  |  |

|                                  | 62.6 MHz                                                            |                                                                                                                                | -7    | I   | 7    | %     |  |  |

|                                  | 48 MHz                                                              |                                                                                                                                | -5    | I   | 5    | %     |  |  |

|                                  | 24 MHz – non-USB mode                                               |                                                                                                                                | -4    | -   | 4    | %     |  |  |

| 1001                             | 24 MHz – USB mode                                                   | With oscillator locking to USB bus                                                                                             | -0.25 | -   | 0.25 | %     |  |  |

| F <sub>IMO</sub> <sup>[99]</sup> | 12 MHz                                                              |                                                                                                                                | -3    | -   | 3    | %     |  |  |

|                                  | 6 MHz                                                               |                                                                                                                                | -2    | -   | 2    | %     |  |  |

|                                  | 3 MHz                                                               | 0 °C to 70 °C                                                                                                                  | -1    | I   | 1    | %     |  |  |

|                                  |                                                                     | –40 °C to 105 °C                                                                                                               | -1.5  | I   | 1.5  | %     |  |  |

|                                  | 3-MHz frequency stability after typical<br>PCB assembly post-reflow | Typical (non-optimized) board layout and 250 °C solder reflow. Device may be calibrated after assembly to improve performance. | -     | ±2% | _    | %     |  |  |

#### Note

98. Based on device characterization (Not production tested).

## Table 11-80. IMO AC Specifications (continued)

| Parameter |                                        | Conditions                                   | Min | Тур | Max | Units |

|-----------|----------------------------------------|----------------------------------------------|-----|-----|-----|-------|

|           | Startup time <sup>[100]</sup>          | From enable (during normal system operation) | -   | -   | 13  | μs    |

|           | Jitter (peak to peak) <sup>[100]</sup> |                                              |     |     |     |       |

| Јр-р      | F = 24 MHz                             |                                              | -   | 0.9 | -   | ns    |

|           | F = 3 MHz                              |                                              | -   | 1.6 | -   | ns    |

|           | Jitter (long term) <sup>[101]</sup>    |                                              |     |     |     |       |

| Jperiod   | F = 24 MHz                             |                                              | -   | 0.9 | -   | ns    |

|           | F = 3 MHz                              |                                              | -   | 12  | -   | ns    |

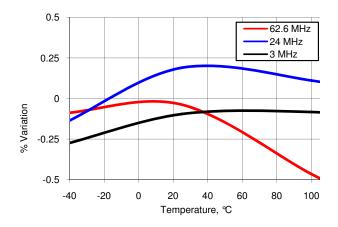

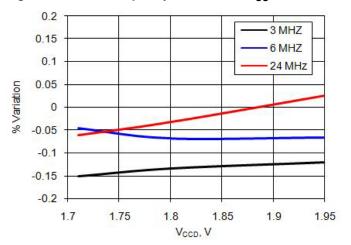

#### Figure 11-82. IMO Frequency Variation vs. Temperature

## Figure 11-83. IMO Frequency Variation vs. V<sub>CC</sub>

Notes

99. F<sub>IMO</sub> is measured after packaging, and thus accounts for substrate and die attach stresses. 100.Based on device characterization (Not production tested).

101.Based on device characterization (Not production tested). USBIO pins tied to ground (VSSD).

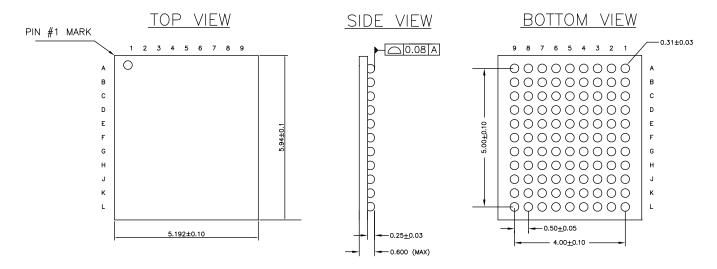

## Figure 13-3. WLCSP Package (5.192 × 5.940 × 0.6 mm) Package Outline

NOTES:

1. REFERENCE JEDEC Publication 95: Design Guide 4.18

2. ALL DIMENSIONS ARE IN MILLIMETERS

001-88034 \*B

# 14. Acronyms

## Table 14-1. Acronyms Used in this Document

| Acronym | Description                                                                                             |

|---------|---------------------------------------------------------------------------------------------------------|

| abus    | analog local bus                                                                                        |

| ADC     | analog-to-digital converter                                                                             |

| AG      | analog global                                                                                           |

| АНВ     | AMBA (advanced microcontroller bus archi-<br>tecture) high-performance bus, an ARM data<br>transfer bus |

| ALU     | arithmetic logic unit                                                                                   |

| AMUXBUS | analog multiplexer bus                                                                                  |

| API     | application programming interface                                                                       |

| APSR    | application program status register                                                                     |

| ARM®    | advanced RISC machine, a CPU architecture                                                               |

| ATM     | automatic thump mode                                                                                    |

| BW      | bandwidth                                                                                               |

| CAN     | Controller Area Network, a communications protocol                                                      |

| CMRR    | common-mode rejection ratio                                                                             |

| CPU     | central processing unit                                                                                 |

| CRC     | cyclic redundancy check, an error-checking protocol                                                     |

| DAC     | digital-to-analog converter, see also IDAC, VDAC                                                        |

| DFB     | digital filter block                                                                                    |

| DIO     | digital input/output, GPIO with only digital capabilities, no analog. See GPIO.                         |

| DMA     | direct memory access, see also TD                                                                       |

| DNL     | differential nonlinearity, see also INL                                                                 |

| DNU     | do not use                                                                                              |

| DR      | port write data registers                                                                               |

| DSI     | digital system interconnect                                                                             |

| DWT     | data watchpoint and trace                                                                               |

| ECC     | error correcting code                                                                                   |

| ECO     | external crystal oscillator                                                                             |

| EEPROM  | electrically erasable programmable read-only<br>memory                                                  |

| EMI     | electromagnetic interference                                                                            |

| EMIF    | external memory interface                                                                               |

| EOC     | end of conversion                                                                                       |

| EOF     | end of frame                                                                                            |

| EPSR    | execution program status register                                                                       |

| ESD     | electrostatic discharge                                                                                 |

| ETM     | embedded trace macrocell                                                                                |

## Table 14-1. Acronyms Used in this Document (continued)

| Acronym                  | Description                                            |

|--------------------------|--------------------------------------------------------|

| FIR                      | finite impulse response, see also IIR                  |

| FPB                      | flash patch and breakpoint                             |

| FS                       | full-speed                                             |

| GPIO                     | general-purpose input/output, applies to a PSoC pin    |

| HVI                      | high-voltage interrupt, see also LVI, LVD              |

| IC                       | integrated circuit                                     |

| IDAC                     | current DAC, see also DAC, VDAC                        |

| IDE                      | integrated development environment                     |

| I <sup>2</sup> C, or IIC | Inter-Integrated Circuit, a communications protocol    |

| lir                      | infinite impulse response, see also FIR                |

| ILO                      | internal low-speed oscillator, see also IMO            |

| IMO                      | internal main oscillator, see also ILO                 |

| INL                      | integral nonlinearity, see also DNL                    |

| I/O                      | input/output, see also GPIO, DIO, SIO, USBIO           |

| IPOR                     | initial power-on reset                                 |

| IPSR                     | interrupt program status register                      |

| IRQ                      | interrupt request                                      |

| ITM                      | instrumentation trace macrocell                        |

| LCD                      | liquid crystal display                                 |

| LIN                      | Local Interconnect Network, a communications protocol. |

| LR                       | link register                                          |

| LUT                      | lookup table                                           |

| LVD                      | low-voltage detect, see also LVI                       |

| LVI                      | low-voltage interrupt, see also HVI                    |

| LVTTL                    | low-voltage transistor-transistor logic                |

| MAC                      | multiply-accumulate                                    |

| MCU                      | microcontroller unit                                   |

| MISO                     | master-in slave-out                                    |

| NC                       | no connect                                             |

| NMI                      | nonmaskable interrupt                                  |

| NRZ                      | non-return-to-zero                                     |

| NVIC                     | nested vectored interrupt controller                   |

| NVL                      | nonvolatile latch, see also WOL                        |

| opamp                    | operational amplifier                                  |

| PAL                      | programmable array logic, see also PLD                 |

| PC                       | program counter                                        |

| РСВ                      | printed circuit board                                  |

| PGA                      | programmable gain amplifier                            |

# **15. Document Conventions**

## 15.1 Units of Measure

## Table 15-1. Units of Measure

| Symbol | Unit of Measure        |

|--------|------------------------|

| °C     | degrees Celsius        |

| dB     | decibels               |

| fF     | femtofarads            |

| Hz     | hertz                  |

| KB     | 1024 bytes             |

| kbps   | kilobits per second    |

| Khr    | kilohours              |

| kHz    | kilohertz              |

| kΩ     | kilohms                |

| ksps   | kilosamples per second |

| LSB    | least significant bit  |

| Mbps   | megabits per second    |

| MHz    | megahertz              |

| MΩ     | megaohms               |

| Msps   | megasamples per second |

| μA     | microamperes           |

| μF     | microfarads            |

| μH     | microhenrys            |

| μs     | microseconds           |

| μV     | microvolts             |

| μW     | microwatts             |

| mA     | milliamperes           |

| ms     | milliseconds           |

| mV     | millivolts             |

| nA     | nanoamperes            |

| ns     | nanoseconds            |

| nV     | nanovolts              |

| Ω      | ohms                   |

| pF     | picofarads             |

| ppm    | parts per million      |

| ps     | picoseconds            |

| s      | seconds                |

| sps    | samples per second     |

| sqrtHz | square root of hertz   |

| V      | volts                  |

# **Document History Page**

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | 3825653 | MKEA               | 12/07/2012         | Datasheet for new CY8C58LP family                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| *A       | 3897878 | MKEA               | 02/07/2013         | Updated characterization footnotes in Electrical Specifications.<br>Updated conditions for SAR ADC INL and DNL specifications in Table 11-20<br>Changed number of opamps in Ordering Information<br>Removed Preliminary status<br>Removed references to CAN.<br>Updated INL VIDAC spec.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| *B       | 3902085 | MKEA               | 02/12/2013         | Changed Hibernate wakeup time from 125 $\mu s$ to 200 $\mu s$ in Table 6-3 and Table 11-3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| *C       | 3917994 | MKEA               | 01/03/2013         | Added Controller Area Network (CAN) content.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| *D       | 4114902 | MKEA               | 09/30/2013         | Added information about 1 KB cache in Features.<br>Added warning on reset devices in the EEPROM section.<br>Added DBGEN field in Table 5-3.<br>Deleted statement about repeat start from the I <sup>2</sup> C section.<br>Removed T <sub>STG</sub> spec from Table 11-1 and added a note clarifying the<br>maximum storage temperature range.<br>Updated chip Idd, regulator, opamp, delta-sigma ADC, SAR ADC, IDAC, and<br>VDAC graphs.<br>Added min and max values for the Regulator Output Capacitor parameter.<br>Updated C <sub>IN</sub> specs in GPIO DC Specifications and SIO DC Specifications.<br>Updated rise and fall time specs in Fast Strong mode in Table 11-9, and<br>deleted related graphs.<br>Added I <sub>IB</sub> parameter in Opamp DC Specifications<br>Updated Vos spec conditions and changed TCVos max value from 0.55 to 1<br>in Table 11-20.<br>Updated Voltage Reference Specifications and IMO AC Specifications.<br>Updated F <sub>IMO</sub> spec (3 MHz).<br>Updated 100-TQFP package diagram.<br>Added Appendix for CSP package (preliminary). |

| *E       | 4225729 | MKEA               | 12/20/2013         | Added SIO Comparator Specifications.<br>Changed T <sub>HIBERNATE</sub> wakeup spec from 200 to 150 µs.<br>Updated CSP package details and ordering information.<br>Added 80 MHz parts in Table 12-1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| *F       | 4386988 | MKEA               | 05/22/2014         | Updated General Description and Features.<br>Added More Information and PSoC Creator sections.<br>Updated JTAG IDs in Ordering Information.<br>Updated 100-TQFP package diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| *G       | 4587100 | MKEA               | 12/08/2014         | Added link to AN72845 in Note 3.<br>Updated interrupt priority numbers in <i>Section 4.4.</i><br>Updated <i>Section 5.4</i> to clarify the factory default values of EEPROM.<br>Corrected ECCEN settings in Table 5-3.<br>Updated <i>Section 6.1.1</i> and <i>Section 6.1.2.</i><br>Added a note below Figure 6-4.<br>Updated Figure 6-11.<br>Changed 'Control Store RAM' to 'Dynamic Configuration RAM' in Figure 7-4<br>and changed <i>Section 7.2.2.2</i> heading to 'Dynamic Configuration RAM'.<br>Updated <i>Section 7.8.</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# Sales, Solutions, and Legal Information

## Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products

| ARM <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Internet of Things                                    | cypress.com/iot        |

| Memory                                                | cypress.com/memory     |

| Microcontrollers                                      | cypress.com/mcu        |

| PSoC                                                  | cypress.com/psoc       |

| Power Management ICs                                  | cypress.com/pmic       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless Connectivity                                 | cypress.com/wireless   |

## **PSoC<sup>®</sup> Solutions**

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 001-84932 Rev. \*L

<sup>©</sup> Cypress Semiconductor Corporation, 2012-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and other countries intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software is no form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware solely for use with Cypress hardware product. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.