Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

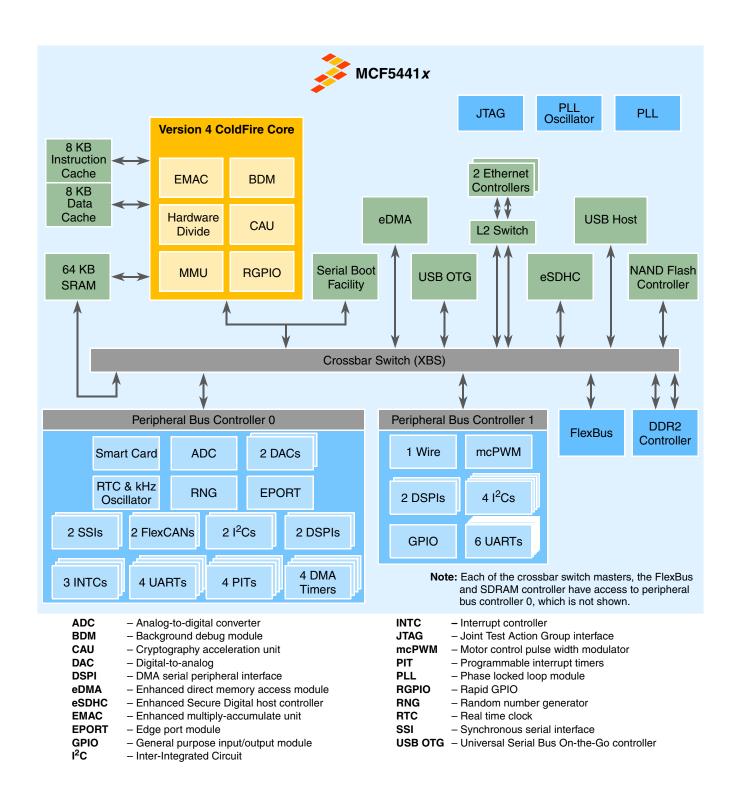

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                                     |

|----------------------------|-----------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                              |

| Core Processor             | Coldfire V4                                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                                  |

| Speed                      | 250MHz                                                                                              |

| Connectivity               | 1-Wire®, CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, SmartCard, SPI, SSI, UART/USART, USB, USB OTC |

| Peripherals                | DMA, PWM, WDT                                                                                       |

| Number of I/O              | 87                                                                                                  |

| Program Memory Size        | -                                                                                                   |

| Program Memory Type        | ROMIess                                                                                             |

| EEPROM Size                | -                                                                                                   |

| RAM Size                   | 64K x 8                                                                                             |

| /oltage - Supply (Vcc/Vdd) | 1.14V ~ 1.32V                                                                                       |

| Data Converters            | A/D 8x12b; D/A 2x12b                                                                                |

| Oscillator Type            | Internal                                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                   |

| Mounting Type              | Surface Mount                                                                                       |

| Package / Case             | 256-LBGA                                                                                            |

| Supplier Device Package    | 256-MAPBGA (17x17)                                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcf54418cmj250                              |

# **Table of Contents**

| 1 | MCF:  | 5441x family comparison4                             |   |       | 4.15.2 eSDHC electrical DC characteristics      | 38 |

|---|-------|------------------------------------------------------|---|-------|-------------------------------------------------|----|

|   | 1.1   | Ordering information                                 |   | 4.16  | SIM timing specifications                       | 38 |

| 2 | Hard  | ware design considerations5                          |   |       | 4.16.1 General timing requirements              | 39 |

|   | 2.1   | Power filtering                                      |   |       | 4.16.2 Reset sequence                           | 39 |

|   | 2.2   | Supply voltage sequencing                            |   |       | 4.16.3 Power-down sequence                      |    |

|   |       | 2.2.1 Power-up sequence8                             |   | 4.17  | SSI timing specifications                       | 41 |

|   |       | 2.2.2 Power-down sequence8                           |   | 4.18  | 12-bit ADC specifications                       |    |

|   | 2.3   | Power consumption specifications                     |   |       | 12-bit DAC timing specifications                |    |

| 3 | Pin a | ssignments and reset states9                         |   |       | mcPWM timing specifications                     |    |

|   | 3.1   | Signal multiplexing9                                 |   | 4.21  | I <sup>2</sup> C timing specifications          | 45 |

|   | 3.2   | Pinout—196 MAPBGA                                    |   |       | Ethernet assembly timing specifications         |    |

|   | 3.3   | Pinout—256 MAPBGA                                    |   |       | 4.22.1 Receive signal timing specifications     | 47 |

| 4 | Elect | rical characteristics21                              |   |       | 4.22.2 Transmit signal timing specifications    | 47 |

|   | 4.1   | Absolute maximum ratings                             |   |       | 4.22.3 Asynchronous input signal timing         |    |

|   | 4.2   | Thermal characteristics22                            |   |       | specifications                                  | 48 |

|   | 4.3   | ESD protection                                       |   |       | 4.22.4 MDIO serial management timing            |    |

|   | 4.4   | Static latch-up (LU)                                 |   |       | specifications                                  | 48 |

|   | 4.5   | DC electrical specifications23                       |   | 4.23  | 32-bit timer module timing specifications       | 49 |

|   | 4.6   | Output pad loading and slew rate                     |   | 4.24  | DSPI timing specifications                      | 49 |

|   | 4.7   | DDR pad drive strengths26                            |   | 4.25  |                                                 |    |

|   | 4.8   | Oscillator and PLL electrical characteristics        |   | 4.26  | 1-Wire timing specifications                    | 53 |

|   | 4.9   | Reset timing specifications                          |   | 4.27  | General purpose I/O timing specifications       | 53 |

|   | 4.10  | FlexBus timing specifications                        |   | 4.28  | Rapid general purpose I/O timing specifications | 53 |

|   | 4.11  | NAND flash controller (NFC) timing specifications 30 |   | 4.29  | JTAG and boundary scan timing specifications    | 54 |

|   | 4.12  | DDR SDRAM controller timing specifications           |   | 4.30  | Debug AC timing specifications                  | 56 |

|   | 4.13  | USB transceiver timing specifications                | 5 | Pack  | age information                                 | 57 |

|   |       | ULPI timing specifications35                         | 6 | Prod  | uct documentation                               | 57 |

|   | 4.15  | eSDHC timing specifications36                        | 7 | Revis | sion history                                    | 58 |

|   |       | 4.15.1 eSDHC timing specifications                   |   |       |                                                 |    |

Table 1. MCF5441x family configurations (continued)

| Module                                           | MCF54410      | MCF54415 | MCF54416 | MCF54417  | MCF54418 |

|--------------------------------------------------|---------------|----------|----------|-----------|----------|

| NAND flash controller                            | •             | •        | •        | •         | •        |

| 1-Wire <sup>®</sup> interface                    | •             | •        | •        | •         | •        |

| Serial boot facility                             | •             | •        | •        | •         | •        |

| Watchdog timer                                   | •             | •        | •        | •         | •        |

| Interrupt controllers (INTC)                     | 3             | 3        | 3        | 3         | 3        |

| Edge port module (EPORT)                         | 3 IRQs        | 5 IRQs   | 5 IRQs   | 5 IRQs    | 5 IRQs   |

| Rapid GPIO pins                                  | 9             | 16       | 16       | 16        | 16       |

| General-purpose I/O (GPIO) pins                  | 48            | 87       | 87       | 87        | 87       |

| JTAG - IEEE <sup>®</sup> 1149.1 Test Access Port | •             | •        | •        | •         | •        |

| Package                                          | 196<br>MAPBGA |          |          | 56<br>BGA |          |

## 1.1 Ordering information

Table 2. Orderable part numbers

| Freescale Part<br>Number | Description             |             | Speed   | Temperature  |

|--------------------------|-------------------------|-------------|---------|--------------|

| MCF54410CMF250           | MCF54410 Microprocessor | 196 MAPBGA  |         |              |

| MCF54415CMJ250           | MCF54415 Microprocessor |             |         |              |

| MCF54416CMJ250           | MCF54416 Microprocessor | 256 MAPBGA  | 250 MHz | –40 to +85°C |

| MCF54417CMJ250           | MCF54417 Microprocessor | 230 MAI BOA |         |              |

| MCF54418CMJ250           | MCF54418 Microprocessor |             |         |              |

# 2 Hardware design considerations

## 2.1 Power filtering

To further enhance noise isolation, an external filter is strongly recommended for the analog  $V_{DD}$  pins (VDDA\_PLL and VDDA\_DAC\_ADC). The filter shown in Figure 1 should be connected between the board 3.3 V (nominal) supply and the analog pins. The resistor and capacitors should be placed as close to the dedicated analog  $V_{DD}$  pin as possible. The 10  $\Omega$  resistor in the given filter is required.

MCF5441x ColdFire Microprocessor Data Sheet, Rev. 8

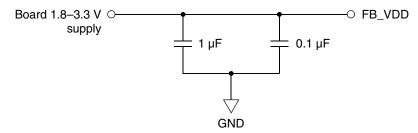

Figure 5 shows an example for bypassing the FlexBus power supply for the MPU. This bypass should be applied to as many FB VDD signals as routing allows. Each one should be placed as close to the ball as possible.

Figure 5. FB\_VDD power filter

## 2.2 Supply voltage sequencing

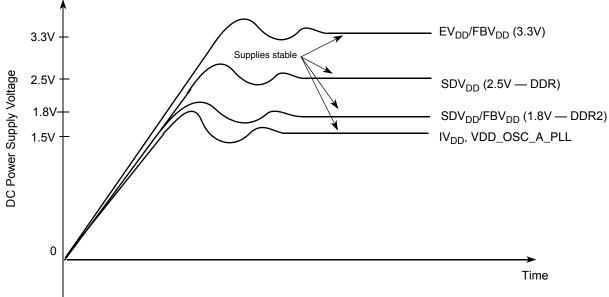

Figure 6 shows requirements in the sequencing of the I/O  $V_{DD}$  (EV $_{DD}$ ), FlexBus  $V_{DD}$  (FBV $_{DD}$ ), SDRAM  $V_{DD}$  (SDV $_{DD}$ ), PLL  $V_{DD}$  (VDD\_OSC\_A\_PLL), and internal logic/core  $V_{DD}$  (IV $_{DD}$ ).

Notes:

### Figure 6. Supply voltage sequencing and separation cautions

The relationships between FBV<sub>DD</sub>, SDV<sub>DD</sub> and EV<sub>DD</sub> are non-critical during power-up and power-down sequences. FBV<sub>DD</sub> (1.8 – 3.3V), SDV<sub>DD</sub> (2.5V or 1.8V) and EV<sub>DD</sub> are specified relative to IV<sub>DD</sub>.

#### NOTE

All I/O VDD pins must be powered on when the device is functioning, except when in standby mode.

In standby mode, all I/O VDD pins, except VSTBY RTC (battery), can be switched off.

MCF5441x ColdFire Microprocessor Data Sheet, Rev. 8

Input voltage must not be greater than the supply voltage (EV<sub>DD</sub>, FBV<sub>DD</sub>, SDV<sub>DD</sub>, IV<sub>DD</sub>, or PV<sub>DD</sub>) by more than 0.5V at any time, including during power-up.

<sup>&</sup>lt;sup>2</sup> Use 25 V/millisecond or slower rise time for all supplies.

#### Hardware design considerations

### 2.2.1 Power-up sequence

If  $EV_{DD}/FBV_{DD}/SDV_{DD}$  are powered up with the  $IV_{DD}$  at 0 V, the sense circuits in the I/O pads cause all pad output drivers connected to the  $EV_{DD}/FBV_{DD}/SDV_{DD}$  to be in a high impedance state. There is no limit on how long after  $EV_{DD}/FBV_{DD}/SDV_{DD}$  powers up before  $IV_{DD}$  must power up.  $IV_{DD}$  should not lead the  $EV_{DD}$ ,  $FBV_{DD}$ , or  $SDV_{DD}$  by more than 0.4 V during power ramp-up, or there will be high current in the internal ESD protection diodes. The rise times on the power supplies should be slower than 25 V/millisecond to avoid turning on the internal ESD protection clamp diodes.

### 2.2.2 Power-down sequence

If  $IV_{DD}/PV_{DD}$  are powered down first, sense circuits in the I/O pads cause all output drivers to be in a high impedance state. There is no limit on how long after  $IV_{DD}$  and  $PV_{DD}$  power down before  $EV_{DD}$ ,  $FBV_{DD}$ , or  $SDV_{DD}$  must power down.  $IV_{DD}$  should not lag  $EV_{DD}$ ,  $FBV_{DD}$ , or  $SDV_{DD}$  going low by more than 0.4 V during power down or there will be undesired high current in the ESD protection diodes. There are no requirements for the fall times of the power supplies.

The recommended power down sequence is as follows:

- 1. Drop IV<sub>DD</sub>/PV<sub>DD</sub> to 0 V.

- 2. Drop  $EV_{DD}/FBV_{DD}/SDV_{DD}$  supplies.

## 2.3 Power consumption specifications

Table 3. Estimated power consumption specifications

| Characteristic                                                                                                                                                                                                                         | Symbol                   | Typical                                     | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------------------|------|

| Core operating supply current (nominal 1.2 V) <sup>1</sup> Run mode Wait mode Doze mode Stop00 mode Stop01 mode Stop02 mode Stop03 mode                                                                                                | IVDD                     | 127<br>33<br>32<br>9.3<br>9.2<br>3.6<br>3.4 | mA   |

| FlexBus operating supply current Run mode (application dependent) Wait mode Doze mode Stop00 mode Stop01, Stop02, Stop03 mode                                                                                                          | FBVDD                    | 80<br>49<br>42<br>40<br>28                  | mA   |

| SDRAM operating supply current (DDR2 at 1.8 V)  Isys(DQ) [×8, 2×DQS]  Isys(WR) [×8, 2×DQS]  Isys(RD) [×8, 2×DQS]  SDRAM input reference current  Isys(REF)  SDRAM termination current  Isys(termRD)  Total SDIDD MPU side <sup>2</sup> | SDVDD<br>SDVREF<br>SDVTT | 3<br>15<br>15<br>1.3<br>41<br>75            | mA   |

| Oscillator/PLL operating supply current (nominal 3.3 V) Run, Wait, Doze, Stop00, Stop01 mode Stop02 mode Stop03 mode                                                                                                                   | VDD_OSC_A_PLL            | 10<br>6<br>1                                | mA   |

MCF5441x ColdFire Microprocessor Data Sheet, Rev. 8

Table 4. Special-case default signal functionality

| Pin                                               | Default signal                                       |

|---------------------------------------------------|------------------------------------------------------|

| FB_CLK, FB_OE, FB_R/W, FB_BE/BWE[1:0], FB_CS[5:4] | FB_CLK, FB_OE, FB_R/W,<br>FB_BE/BWE[1:0], FB_CS[5:4] |

| FB_ALE                                            | FB_ALE or FB_TS<br>(depending on RCON[3])            |

| FB_BE/BWE3                                        | Boot from NFC, NF_ALE. Otherwise, FB_BE/BWE3.        |

| FB_BE/BWE2                                        | Boot from NFC, NF_CLE. Otherwise, FB_BE/BWE2.        |

| FB_CS1                                            | Boot from NFC, NFC_CE. Otherwise, GPIO.              |

| FB_CS0                                            | Boot from FlexBus, FB_CS0.<br>Otherwise, GPIO.       |

| FB_TA                                             | Boot from NFC, NFC_R/B. Otherwise, FB_TA.            |

| ALLPST, PST[3:0],<br>DDATA[3:0]                   | ALLPST, PST[3:0], DDATA[3:0]                         |

### **NOTE**

While most modules and functionalities between the 196 and 256 MAPBGA package are the same, the following modules have been removed from 196 MAPBGA for pin space:

UART2, UART6, UART9, PWM, SSI1, SIM1, USB HOST, IRQ6, IRQ3, IRQ2, FLEXCAN1, I2C1, ADC, DAC.

Other modifications to the 196 MAPBGA package are:

- SDRAMC One address line, SD\_A14, is removed.

- SDHC Number of data lines for eSDHC have been reduced to 4 instead of 8.

- MAC Only MAC0\_RMII mode is implemented.

Table 5. MCF5441x Signal information and muxing

| Signal name            | GPIO  | Alternate 1 | Alternate 2 | Pullup (U) <sup>1</sup><br>Pulldown (D) | Direction <sup>2</sup> | Voltage domain | Pad type <sup>3</sup> | 196 MAPBGA | 256 MAPBGA |  |

|------------------------|-------|-------------|-------------|-----------------------------------------|------------------------|----------------|-----------------------|------------|------------|--|

|                        | Reset |             |             |                                         |                        |                |                       |            |            |  |

| RESET                  | _     | _           | _           | U                                       | I                      | EVDD           | ssr                   | K14        | K15        |  |

| RSTOUT                 | _     | _           | _           | _                                       | 0                      | EVDD           | msr                   | P12        | L16        |  |

|                        | Clock |             |             |                                         |                        |                |                       |            |            |  |

| EXTAL/<br>RMII_REF_CLK | _     | _           | _           | _                                       | l <sup>4</sup>         | EVDD           | ae                    | G14        | G16        |  |

MCF5441x ColdFire Microprocessor Data Sheet, Rev. 8

### Pin assignments and reset states

Table 5. MCF5441x Signal information and muxing (continued)

| Signal name                                | GPIO    | Alternate 1        | Alternate 2                     | Pullup (U) <sup>1</sup><br>Pulldown (D) | Direction <sup>2</sup> | Voltage domain | Pad type <sup>3</sup> | 196 MAPBGA                            | 256 MAPBGA                           |  |

|--------------------------------------------|---------|--------------------|---------------------------------|-----------------------------------------|------------------------|----------------|-----------------------|---------------------------------------|--------------------------------------|--|

| XTAL                                       | _       | _                  | _                               | _                                       | 0                      | EVDD           | ae                    | H14                                   | H16                                  |  |

| Mode selection                             |         |                    |                                 |                                         |                        |                |                       |                                       |                                      |  |

| BOOTMOD[1:0]                               | _       | _                  | _                               | T —                                     | ı                      | EVDD           | msr                   | G5,H5                                 | K5, L5                               |  |

| ,                                          |         |                    | FlexBus                         | •                                       |                        |                |                       | •                                     |                                      |  |

| FB_AD[31:24]/<br>NFC_IO[15:8] <sup>5</sup> | _       | _                  | _                               | _                                       | I/O                    | FBVDD          | fsr                   | A10, A9,<br>B9, C9, A8,<br>B8, C8, A7 | B9, C8, A9,<br>B8, D8, A8,<br>D7, B7 |  |

| FB_AD[23:16]/<br>NFC_IO[7:0] <sup>5</sup>  | _       | _                  | _                               | _                                       | I/O                    | FBVDD          | fsr                   | B7, C7, C6,<br>B6, A6, A5,<br>B5, A4  | C7, A7, D6,<br>A6, B6, D5,<br>C6, A5 |  |

| FB_AD[15:10]                               | _       | _                  | _                               | 6                                       | I/O                    | FBVDD          | fsr                   | C5, A3, B4,<br>C4, B3, A2             | B5, A4, A3,<br>D4, B4, C5            |  |

| FB_AD[9:8]                                 | _       | _                  | _                               | U <sup>7</sup>                          | I/O                    | FBVDD          | fsr                   | B2, C3                                | C4, B3                               |  |

| FB_AD[7:0]                                 | _       | _                  | _                               | _                                       | I/O                    | FBVDD          | fsr                   | D4, B1, C2,<br>D3, C1, D2,<br>E3, D1  | C3, E4, D3,<br>E3, A2, B2,<br>C2, F3 |  |

| FB_ALE                                     | PA7     | FB_TS              | _                               | _                                       | 0                      | FBVDD          | fsr                   | E2                                    | D2                                   |  |

| FB_OE/<br>NFC_RE                           | PA6     | FB_TBST/<br>NFC_RE | _                               | _                                       | 0                      | FBVDD          | fsr                   | H1                                    | F1                                   |  |

| FB_R/W/<br>NFC_WE                          | PA5     | _                  | _                               | _                                       | 0                      | FBVDD          | fsr                   | H2                                    | G2                                   |  |

| FB_TA                                      | PA4     | _                  | NFC_R/B                         | U <sup>8</sup>                          | 0                      | FBVDD          | fsr                   | НЗ                                    | НЗ                                   |  |

| FB_BE/BWE3                                 | PA3     | FB_CS3             | FB_A1/<br>NFC_ALE <sup>9</sup>  | _                                       | 0                      | FBVDD          | fsr                   | F3                                    | C1                                   |  |

| FB_BE/BWE2                                 | PA2     | FB_CS2             | FB_A0/<br>NFC_CLE <sup>10</sup> | _                                       | 0                      | FBVDD          | fsr                   | E1                                    | E2                                   |  |

| FB_BE/BWE[1:0]                             | PA[1:0] | FB_TSIZ[1:0]       | _                               | _                                       | 0                      | FBVDD          | fsr                   | F2, F1                                | D1, F4                               |  |

| FB_CLK                                     | PB7     | _                  | _                               | _                                       | 0                      | FBVDD          | fsr                   | G1                                    | G1                                   |  |

| FB_CS5                                     | PB6     | DACK1              | _                               | -                                       | 0                      | FBVDD          | fsr                   | _                                     | F2                                   |  |

| FB_CS4                                     | PB5     | DREQ1              | _                               | -                                       | 0                      | FBVDD          | fsr                   | _                                     | B1                                   |  |

| FB_CS1                                     | PB4     | _                  | NFC_CE                          | _                                       | 0                      | FBVDD          | fsr                   | G3                                    | E1                                   |  |

| FB_CS0                                     | PB3     | _                  | _                               | _                                       | 0                      | FBVDD          | fsr                   | G2                                    | G3                                   |  |

| ,                                          |         | •                  | I <sup>2</sup> C 0              | 1                                       | •                      |                |                       |                                       | ı                                    |  |

| I2C0_SCL                                   | PB2     | UART8_TXD          | CAN0_TX                         |                                         | I/O                    | EVDD           | ssr                   | H12                                   | G15                                  |  |

| I2C0_SDA                                   | PB1     | UART8_RXD          | CAN0_RX                         | _                                       | I/O                    | EVDD           | ssr                   | G12                                   | G14                                  |  |

### Pin assignments and reset states

Table 5. MCF5441x Signal information and muxing (continued)

| Signal name GPIO      |     | Alternate 1 | ternate 1 Alternate 2   |     | Direction <sup>2</sup> | Voltage domain       | Pad type <sup>3</sup> | 196 MAPBGA | 256 MAPBGA |

|-----------------------|-----|-------------|-------------------------|-----|------------------------|----------------------|-----------------------|------------|------------|

|                       |     | Externa     | al interrupts port      |     |                        |                      |                       |            |            |

| ĪRQ7                  | PC6 | _           | _                       | _   | I                      | EVDD                 | ssr                   | G10        | F12        |

| ĪRQ6                  | PC5 | _           | USB_CLKIN <sup>11</sup> | _   | I                      | EVDD                 | ssr                   | _          | N1         |

| ĪRQ4                  | PC4 | DREQ0       | _                       | _   | I                      | EVDD                 | ssr                   | E11        | F14        |

| ĪRQ3                  | PC3 | DSPI0_PCS3  | USBH_VBUS_EN            | _   | I                      | EVDD                 | ssr                   |            | M1         |

| ĪRQ2                  | PC2 | DSPI0_PCS2  | USBH_VBUS_OC            | _12 | I                      | EVDD                 | ssr                   | _          | M2         |

| ĪRQ1                  | PC1 | _           | _                       | _   | I                      | EVDD                 | ssr                   | E13        | F13        |

|                       |     | US          | B On-the-Go             |     | 1                      | I                    | I                     | l          |            |

| USBO_DM               | _   | _           | _                       | _   | I/O                    | VDD_<br>USB0         | ae                    | B13        | A14        |

| USBO_DP               | _   | _           | _                       | _   | I/O                    | VDD_<br>USB0         | ae                    | A13        | B14        |

|                       |     |             | USB host                |     |                        |                      |                       |            |            |

| USBH_DM               | _   | _           | _                       | _   | I/O                    | VDD_<br>USBH         | ae                    | _          | A15        |

| USBH_DP               | _   | _           | _                       | _   | I/O                    | VDD_<br>USBH         | ae                    | _          | B15        |

|                       |     |             | ADC                     | •   |                        |                      | I.                    |            | •          |

| ADC_IN7/<br>DAC1_OUT  | _   | _           | _                       | _   | I                      | VDDA_<br>DAC_<br>ADC | ae                    | _          | К3         |

| ADC_IN[6:4]           | _   | _           | _                       | _   | I                      | VDDA_<br>ADC         | ae                    | _          | H2, J3, G4 |

| ADC_IN3/<br>DAC0_OUT  | _   | _           | _                       | _   | I                      | VDDA_<br>DAC_<br>ADC | ae                    | _          | K4         |

| ADC_IN[2:0]           | _   | _           | _                       | _   | I                      | VDDA_<br>ADC         | ae                    | _          | J2, J1, H1 |

|                       |     | Re          | al time clock           | •   | •                      | •                    |                       |            | •          |

| RTC_EXTAL             | _   | _           | _                       | _   | l <sup>4</sup>         | VSTBY                | ae                    | B14        | B16        |

| RTC_XTAL              | _   | _           | _                       | _   | 0                      | VSTBY                | ae                    | C14        | C16        |

|                       | L   | D           | SPI0/SBF <sup>13</sup>  | 1   | 1                      | ı                    | ı                     | 1          |            |

| DSPI0_PCS1/<br>SBF_CS | PC0 | _           | _                       | _   | I/O                    | EVDD                 | msr                   | К3         | L1         |

### Pin assignments and reset states

- <sup>21</sup> Configurable pull that is enabled and pulled down after reset.

- <sup>22</sup> The ALLPST signal is available only on the 196 MAPBGA package and allows limited debug trace functionality compared to the 256 MAPBGA package.

- <sup>23</sup> If JTAG\_EN is asserted, these pins default to Alternate 1 (JTAG) functionality. The GPIO module is not responsible for assigning these pins.

- <sup>24</sup> VSTBY is for optional standby lithium battery. If not used, connect to EVDD.

## 3.2 Pinout—196 MAPBGA

The pinout for the MCF54410 package is shown below.

|   | 1              | 2              | 3              | 4            | 5            | 6           | 7            | 8           | 9            | 10          | 11             | 12             | 13                    | 14                    |   |

|---|----------------|----------------|----------------|--------------|--------------|-------------|--------------|-------------|--------------|-------------|----------------|----------------|-----------------------|-----------------------|---|

| A | GND            | FB_<br>AD10    | FB_<br>AD14    | FB_<br>AD16  | FB_<br>AD18  | FB_<br>AD19 | FB_<br>AD24  | FB_<br>AD27 | FB_<br>AD30  | FB_<br>AD31 | SSI0_<br>TXD   | SSI0_<br>MCLK  | USB_<br>DPLS          | GND                   | A |

| В | FB_<br>AD6     | FB_<br>AD9     | FB_<br>AD11    | FB_<br>AD13  | FB_<br>AD17  | FB_<br>AD20 | FB_<br>AD23  | FB_<br>AD26 | FB_<br>AD29  | U1_<br>RXD  | U0_<br>TXD     | SSI0_<br>RXD   | USB_<br>DMNS          | RTC_<br>EXTAL         | В |

| С | FB_<br>AD3     | FB_<br>AD5     | FB_<br>AD8     | FB_<br>AD12  | FB_<br>AD15  | FB_<br>AD21 | FB_<br>AD22  | FB_<br>AD25 | FB_<br>AD28  | U1_<br>TXD  | U0_<br>RXD     | U0RTS_<br>B    | SSI0_<br>FS           | RTC_<br>XTAL          | С |

| D | FB_<br>AD0     | FB_<br>AD2     | FB_<br>AD4     | FB_<br>AD7   | FBVDD        | FBVDD       | FBVDD        | GND         | CVDD         | CVDD        | U1RTS_<br>B    | U1CTS_<br>B    | SSI0_<br>BCLK         | GND                   | D |

| E | FB_BE2<br>_B   | FB_ALE         | FB_<br>AD1     | FBVDD        |              |             |              | GND         | CVDD         | CVDD        | IRQ4_B         | U0CTS_<br>B    | IRQ1_B                | VSTBY                 | E |

| F | FB_BE0<br>_B   | FB_BE1<br>_B   | FB_BE3<br>_B   | EVDD         | EVDD         | EVDD        | EVDD         | GND         | CVDD         | CVDD        | VDD_<br>USBO   | CVDD           | VSS_OS<br>C_A_PL<br>L | VDD_OS<br>C_A_PL<br>L | F |

| G | FB_CLK         | FB_CS0<br>_B   | FB_CS1<br>_B   | GND          | BOOT<br>MOD1 | EVDD        | EVDD         | GND         | GND          | IRQ7_B      | GND            | I2C0_<br>SDA   | T3IN                  | EXTAL                 | G |

| н | FB_OE_<br>B    | FB_RW_<br>B    | FB_TA_<br>B    | GND          | BOOT<br>MOD0 | EVDD        | EVDD         | GND         | GND          | GND         | GND            | I2C0_<br>SCL   | T1IN                  | XTAL                  | н |

| J | DSPI0_<br>PCS0 | DSPI0_<br>SOUT | DSPI0_<br>SCK  | SD_BA1       | EVDD         | EVDD        | GND          | GND         | GND          | GND         | GND            | T2IN           | TOIN                  | GND                   | J |

| K | SD_A1          | DSPI0_<br>SIN  | DSPI0_<br>PCS1 | SD_CAS<br>_B | GND          | GND         | SDVDD        | SDVDD       | SDVDD        | TEST        | GND            | ALLPST         | TMS                   | RSTIN_<br>B           | ĸ |

| L | SD_A9          | SD_A10         | SD_A5          | SD_A4        | SDVDD        | SDVDD       | SDVDD        | SD_VTT      | TRST_B       | TDI         | RM110_<br>TXD0 | RM110_<br>TXD1 | TDO                   | TCLK                  | L |

| М | SD_A12         | SD_A7          | SD_A11         | SD_RAS<br>_B | SD_CS_<br>B  | SD_BA2      | SD_D0        | SD_D2       | SD_D4        | SD_D6       | OWIO           | RMII0_<br>RXER | RMII0_<br>CRS_DV      | RMII0_<br>MDIO        | М |

| N | SD_A3          | SD_A2          | SD_A0          | SD_A8        | SD_WE_<br>B  | SD_CKE      | SD_DQM       | SD_D1       | SD_VRE<br>F  | SD_D5       | JTAG_E<br>N    | RMII0_<br>TXEN | RMII0_<br>RXD0        | RMII0_<br>MDC         | N |

| P | GND            | SD_A6          | SD_A13         | SD_BA0       | SD_ODT       | SD_CLK      | SD_CLK_<br>B | SD_DQS      | SD_DQS<br>_B | SD_D3       | SD_D7          | RSTOUT<br>_B   | RMII0_<br>RXD1        | GND                   | Р |

|   | 1              | 2              | 3              | 4            | 5            | 6           | 7            | 8           | 9            | 10          | 11             | 12             | 13                    | 14                    |   |

Figure 7. MCF54410 Pinout (196 MAPBGA)

### 4 Electrical characteristics

This document contains electrical specification tables and reference timing diagrams for the MCF5441x microprocessor. This section contains detailed information on AC/DC electrical characteristics and AC timing specifications.

#### NOTE

The specifications for this device in any other document are superseded by the specifications in this document.

## 4.1 Absolute maximum ratings

Table 6. Absolute maximum ratings 1, 2

| Rating                                                                                     | Symbol                                               | Pin name      | Value        | Units |

|--------------------------------------------------------------------------------------------|------------------------------------------------------|---------------|--------------|-------|

| External I/O pad supply voltage                                                            | EV <sub>DD</sub>                                     | EVDD          | -0.3 to +4.0 | V     |

| Internal logic supply voltage                                                              | IV <sub>DD</sub>                                     | IVDD          | -0.5 to +2.0 | V     |

| FlexBus I/O pad supply voltage                                                             | FBV <sub>DD</sub>                                    | FB_VDD        | -0.3 to +4.0 | V     |

| SDRAM I/O pad supply voltage                                                               | SDV <sub>DD</sub>                                    | SD_VDD        | -0.3 to +4.0 | V     |

| PLL supply voltage                                                                         | PV <sub>DD</sub>                                     | VDD_OSC_A_PLL | -0.3 to +4.0 | V     |

| USB OTG supply voltage                                                                     | USBV <sub>DD</sub>                                   | VDD_USBO      | -0.3 to +4.0 | V     |

| USB host supply voltage                                                                    | USBV <sub>DD</sub>                                   | VDD_USBH      | -0.3 to +4.0 | V     |

| ADC supply voltage                                                                         | $AV_DD$                                              | VDDA_ADC      | -0.3 to +4.0 | V     |

| DAC and ADC supply voltage                                                                 | _                                                    | VDDA_DAC_ADC  | -0.3 to +4.0 | V     |

| RTC standby supply voltage                                                                 | RTCV <sub>STBY</sub>                                 | VSTBY_RTC     | -0.3 to +4.0 | V     |

| Digital input voltage <sup>3</sup>                                                         | V <sub>IN</sub>                                      | _             | -0.3 to +3.6 | V     |

| Instantaneous maximum current<br>Single pin limit (applies to all pins) <sup>3, 4, 5</sup> | I <sub>DD</sub>                                      | _             | 25           | mA    |

| Operating temperature range (packaged)                                                     | T <sub>A</sub><br>(T <sub>L</sub> – T <sub>H</sub> ) | _             | -40 to +85   | °C    |

| Storage temperature range                                                                  | T <sub>stg</sub>                                     | _             | −55 to +150  | °C    |

Functional operating conditions are given in Table 11. Absolute maximum ratings are stress ratings only, and functional operation at the maximum is not guaranteed. Continued operation at these levels may affect device reliability or cause permanent damage to the device.

This device contains circuitry protecting against damage due to high static voltage or electrical fields. However, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Immunity to static and electrical fields is enhanced if unused inputs are tied to an appropriate logic voltage level (e.g., V<sub>SS</sub> or EV<sub>DD</sub>).

Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, and then use the larger of the two values.

$<sup>^4</sup>$  All functional non-supply pins are internally clamped to  $V_{SS}$  and  $EV_{DD}$  .

Power supply must maintain regulation within operating  $EV_{DD}$ ,  $FBV_{DD}$ , and  $SDV_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current  $(V_{in} > EV_{DD}, FBV_{DD}, or SDV_{DD})$  is greater than  $I_{DD}$ , the injection current may flow out of  $EV_{DD}$ ,  $FBV_{DD}$ , or  $SDV_{DD}$  and could result in external power supply going out of regulation. Ensure the external  $EV_{DD}$ ,  $FBV_{DD}$ , or  $SDV_{DD}$  load shunts current greater than maximum injection current. This is the greatest risk when the MPU is not consuming power (for example, no clock).

Table 12. Output pad slew rates (continued)

| Pad type <sup>1</sup> | Slew rate select field value | Drive load<br>(pF) | Rise/fall time<br>(ns) |

|-----------------------|------------------------------|--------------------|------------------------|

| msr                   | 11                           | 50                 | 1.2                    |

|                       | 11                           | 200                | 6                      |

|                       | 10                           | 50                 | 9                      |

|                       | 10                           | 200                | 14                     |

|                       | 01                           | 50                 | 17                     |

|                       | O1                           | 200                | 23                     |

|                       | 00                           | 50                 | 110                    |

|                       | 00                           | 200                | 120                    |

| fsr                   | 11                           | 50                 | 1.1                    |

|                       | 11                           | 200                | 2.6                    |

|                       | 10                           | 50                 | 2.4                    |

|                       | 10                           | 200                | 5                      |

|                       | 01                           | 50                 | 5                      |

|                       | O1                           | 200                | 8                      |

|                       | 00                           | 50                 | 16                     |

|                       |                              | 200                | 21                     |

The ae pads are used for USB communication and are governed by usb.org specifications. They are not included in this table.

## 4.7 DDR pad drive strengths

The DDR pins on the MCF5441x devices have programmable drive strengths. Table 13 lists the drive strengths for pins based on the value programmed into the appropriate field of the drive strength control register. Refer to Table 5 for a list of the external signals to pad connections.

#### NOTE

For a single device drive, this setting should be 00 to enable Half Strength mode. High strength is intended for multiple device drives (DIMM).

Table 13. DDR pad drive strengths

| Pad type | Drive strength select field value | Drive strength          |

|----------|-----------------------------------|-------------------------|

| st       | 00                                | Half strength 1.8V DDR2 |

|          | 01                                | Full strength 1.8V DDR2 |

|          | 10                                | Reserved                |

|          | 11                                | Reserved                |

### 4.8 Oscillator and PLL electrical characteristics

Reference Figure 9 for crystal circuits.

**Table 14. PLL electrical characteristics**

| Num | Characteristic                                                                                                                                      | Symbol                                           | Min                                | Max                                                                                   | Unit                                         |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------|

| 1   | PLL Reference Frequency Range <sup>1</sup> Crystal reference External reference                                                                     | f <sub>ref_crystal</sub><br>f <sub>ref_ext</sub> | 14 <sup>1</sup><br>14 <sup>1</sup> | 50 <sup>1</sup><br>50 <sup>1</sup>                                                    | MHz<br>MHz                                   |

| 2   | Core frequency<br>FB_CLK frequency <sup>2</sup> (MISCCR2[FBHALF] = 0)                                                                               | f <sub>sys</sub><br>f <sub>sys/2</sub>           | 120<br>60                          | 250<br>100                                                                            | MHz<br>MHz                                   |

| 3   | VCO frequency                                                                                                                                       | f <sub>vco</sub>                                 | 240                                | 500                                                                                   | MHz                                          |

| 4   | DCC frequency <sup>3</sup>                                                                                                                          | f <sub>DCC</sub>                                 | 300                                | 500                                                                                   | MHz                                          |

| 5   | Crystal start-up time <sup>4, 5</sup>                                                                                                               | t <sub>cst</sub>                                 | _                                  | 10                                                                                    | ms                                           |

| 6   | EXTAL input high voltage<br>External and limp modes                                                                                                 | V <sub>IHEXT</sub>                               | EV <sub>IH</sub>                   | EVDD                                                                                  | V                                            |

| 7   | EXTAL input low voltage<br>External and limp modes                                                                                                  | V <sub>ILEXT</sub>                               | 0                                  | EV <sub>IL</sub>                                                                      | V                                            |

| 8   | PLL lock time <sup>4, 6</sup>                                                                                                                       | t <sub>lpII</sub>                                | _                                  | 50                                                                                    | ms                                           |

| 9   | Duty cycle of reference <sup>4</sup>                                                                                                                | t <sub>dc</sub>                                  | -45%                               | +45%                                                                                  | %                                            |

| 10  | Crystal capacitive load                                                                                                                             | C <sub>L</sub>                                   | _                                  | From crystal spec                                                                     | pF                                           |

| 11  | Feedback resistor                                                                                                                                   | R <sub>F</sub>                                   | 10                                 | _                                                                                     | MΩ                                           |

| 12  | Series resistor                                                                                                                                     | R <sub>S</sub>                                   | 0                                  | 200                                                                                   | Ω                                            |

| 13  | Discrete load capacitance for XTAL                                                                                                                  | C <sub>L_XTAL</sub>                              | _                                  | $\begin{array}{c} 2 \times C_L - \\ C_{S\_XTAL} - \\ C_{PCB\_XTAL}^7 \end{array}$     | pF                                           |

| 14  | Discrete load capacitance for EXTAL                                                                                                                 | C <sub>L_EXTAL</sub>                             | _                                  | 2 × C <sub>L</sub> -<br>C <sub>S_EXTAL</sub> -<br>C <sub>PCB_EXTAL</sub> <sup>7</sup> | pF                                           |

| 15  | FB_CLK period jitter, <sup>4, 5, 7, 8,</sup> Measured at f <sub>SYS</sub> Max<br>Peak-to-peak jitter (clock edge to clock edge)<br>Long term jitter | C <sub>jitter</sub>                              | _<br>_                             | 10<br>0.1                                                                             | % f <sub>sys/3</sub><br>% f <sub>sys/3</sub> |

These reference value ranges are for after a PLL predivider (PREDIV), which can be programmed to 1, 2, 4, 8, or 16. The PREDIV value can be set while booting from serial flash. In parallel reset configuration, the PREDIV value is set to one. In this mode, if the input frequency results in an out of range reference frequency, boot the processor in limp mode, set the proper PREDIV and multiplier settings, and switch to PLL mode.

<sup>&</sup>lt;sup>2</sup> All internal registers retain data at 0 Hz.

<sup>&</sup>lt;sup>3</sup> Required only for DDR2 memory.

<sup>&</sup>lt;sup>4</sup> This parameter is guaranteed by characterization before qualification rather than 100% tested.

Proper PC board layout procedures must be followed to achieve specifications.

<sup>6</sup> This specification is the PLL lock time only and does not include oscillator start-up time.

$<sup>^7</sup>$  C<sub>PCB EXTAL</sub> and C<sub>PCB XTAL</sub> are the measured PCB stray capacitances on EXTAL and XTAL, respectively.

Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>sys</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the PLL circuitry via PLL V<sub>DD</sub>, EV<sub>DD</sub>, and V<sub>SS</sub> and variation in crystal oscillator frequency increase the Cjitter percentage for a given interval.

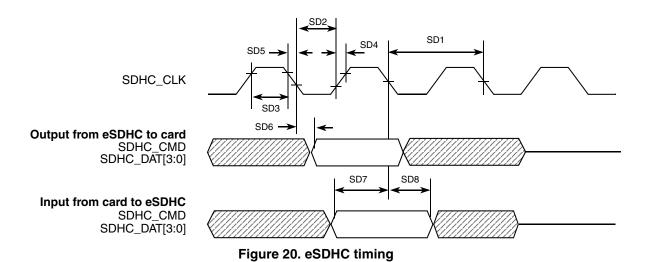

## 4.15.1 eSDHC timing specifications

Figure 20 depicts the timing of eSDHC, and Table 20 lists the eSDHC timing characteristics.

Table 20. eSDHC interface timing specifications

| ID      | Parameter                                                             | Symbols                      | Min | Max | Unit |  |  |

|---------|-----------------------------------------------------------------------|------------------------------|-----|-----|------|--|--|

| Card In | put Clock                                                             |                              |     | 1   |      |  |  |

| SD1     | Clock frequency (low speed)                                           | f <sub>PP</sub> <sup>1</sup> | 0   | 400 | kHz  |  |  |

|         | Clock frequency (SD/SDIO full speed)                                  | f <sub>PP</sub> <sup>2</sup> | 0   | 40  | MHz  |  |  |

|         | Clock frequency (MMC full speed)                                      | f <sub>PP</sub> <sup>3</sup> | 0   | 20  | MHz  |  |  |

|         | Clock frequency (identification mode)                                 | f <sub>OD</sub> <sup>4</sup> | 100 | 400 | kHz  |  |  |

| SD2     | Clock low time                                                        | t <sub>WL</sub>              | 7   | _   | ns   |  |  |

| SD3     | Clock high time                                                       | t <sub>WH</sub>              | 7   | _   | ns   |  |  |

| SD4     | Clock rise time                                                       | t <sub>TLH</sub>             | _   | 3   | ns   |  |  |

| SD5     | Clock fall time                                                       | t <sub>THL</sub>             | _   | 3   | ns   |  |  |

| eSDHC   | Output / card inputs SDHC_CMD, SDHC_DAT (reference                    | ce to SDHC_CL                | K)  |     |      |  |  |

| SD6     | eSDHC output delay (output valid)                                     | t <sub>OD</sub>              | -5  | 5   | ns   |  |  |

| eSDHC   | eSDHC Input / card outputs SDHC_CMD, SDHC_DAT (reference to SDHC_CLK) |                              |     |     |      |  |  |

| SD7     | eSDHC input setup time                                                | t <sub>ISU</sub>             | 5   | _   | ns   |  |  |

| SD8     | eSDHC input hold time                                                 | t <sub>IH</sub>              | 0   | _   | ns   |  |  |

<sup>&</sup>lt;sup>1</sup> In low speed mode, card clock must be lower than 400 kHz, voltage ranges from 2.7 to 3.6 V.

$<sup>^4\,</sup>$  In card identification mode, card clock must be 100 kHz– 400 kHz, voltage ranges from 2.7 to 3.6 V.

MCF5441x ColdFire Microprocessor Data Sheet, Rev. 8

<sup>&</sup>lt;sup>2</sup> In normal data transfer mode for SD/SDIO card, clock frequency can be any value from 0 to 25 MHz.

<sup>&</sup>lt;sup>3</sup> In normal data transfer mode for MMC card, clock frequency can be any value from 0 to 20 MHz.

### 4.15.2 eSDHC electrical DC characteristics

Table 21 lists the eSDHC electrical DC characteristics.

Table 21. MMC/SD interface electrical specifications

| Num      | Parameter             | Design value | Min                     | Max                     | Unit | Condition/remark                              |

|----------|-----------------------|--------------|-------------------------|-------------------------|------|-----------------------------------------------|

| Bus sigr | nal line load         |              |                         |                         |      |                                               |

| 7        | Pull-up resistance    | 47           | 10                      | 100                     | kΩ   | Internal PU                                   |

| 8        | Open drain resistance | NA           | NA                      | NA                      | kΩ   | For MMC cards only                            |

| Open dra | ain signal level      | <b>-</b>     |                         |                         |      | For MMC cards only                            |

| 9        | Output high voltage   |              | V <sub>DD</sub> – 0.2   |                         | V    | I <sub>OH</sub> = -100 μA                     |

| 10       | Output low voltage    |              |                         | 0.3                     | V    | I <sub>OL</sub> = 2 mA                        |

| Bus sigr | nal levels            | •            |                         |                         |      |                                               |

| 11       | Output high voltage   |              | 0.75 x V <sub>DD</sub>  |                         | V    | $I_{OH} = -100 \ \mu A \ @V_{DD} \ min$       |

| 12       | Output low voltage    |              |                         | 0.125 x V <sub>DD</sub> | V    | I <sub>OL</sub> = 100 μA @V <sub>DD</sub> min |

| 13       | Input high voltage    |              | 0.625 x V <sub>DD</sub> | V <sub>DD</sub> + 3     | V    |                                               |

| 14       | Input low voltage     |              | V <sub>SS</sub> - 0.3   | 0.25 x V <sub>DD</sub>  | V    |                                               |

## 4.16 SIM timing specifications

Each SIM card interface consist of a total of 12 pins (two separate ports of six pins each. Mostly one port with 5 pins is used).

The interface is meant to be used with synchronous SIM cards. This means that the SIM module provides a clock for the SIM card to use. The frequency of this clock is normally 372 times the data rate on the TX/RX pins, however SIM module can work with CLK equal to 16 times the data rate on TX/RX pins.

There is no timing relationship between the clock and the data. The clock that the SIM module provides to the SIM card is used by the SIM card to recover the clock from the data, like a standard UART. All six (or five when a bidirectional TXRX is used) of the pins for each half of the SIM module are asynchronous to each other. There are no required timing relationships between the signals in normal mode. However, there are some in reset and power down sequences.

All SIM signals use pad type pad\_msr. SIM timing is fairly relaxed compared to other interfaces and can be met at 50 pF loading with any slew rate setting other than 00.1

MCF5441x ColdFire Microprocessor Data Sheet, Rev. 8

<sup>1.</sup> These timing parameters are specified assuming maximum operating frequency and the fastest pad slew rate setting (11). When operating this interface at lower frequencies, increase the slew rate by using the 10, 01, or 00 setting to increase edge rise and fall times, thus reducing EMI.

Table 24. SSI timing — master modes<sup>1</sup>

| Num | Description                                  | Symbol            | Min   | Max | Units             | Notes |

|-----|----------------------------------------------|-------------------|-------|-----|-------------------|-------|

| S1  | SSI_MCLK cycle time                          | t <sub>MCLK</sub> | 15.15 |     | ns                | 2     |

| S2  | SSI_MCLK pulse width high / low              |                   | 45%   | 55% | t <sub>MCLK</sub> |       |

| S3  | SSI_BCLK cycle time                          | t <sub>BCLK</sub> | 80    | _   | ns                | 3     |

| S4  | SSI_BCLK pulse width                         |                   | 45%   | 55% | t <sub>BCLK</sub> |       |

| S5  | SSI_BCLK to SSI_FS output valid              |                   | _     | 15  | ns                |       |

| S6  | SSI_BCLK to SSI_FS output invalid            |                   | 0     | _   | ns                |       |

| S7  | SSI_BCLK to SSI_TXD valid                    |                   | _     | 15  | ns                |       |

| S8  | SSI_BCLK to SSI_TXD invalid / high impedance |                   | 0     | _   | ns                |       |

| S9  | SSI_RXD / SSI_FS input setup before SSI_BCLK |                   | 15    | _   | ns                |       |

| S10 | SSI_RXD / SSI_FS input hold after SSI_BCLK   |                   | 0     | _   | ns                |       |

<sup>&</sup>lt;sup>1</sup> All timings specified with a capacitive load of 25pF.

Table 25. SSI timing — slave modes<sup>1</sup>

| Num | Description                                                      | Symbol            | Min | Max | Units             | Notes |

|-----|------------------------------------------------------------------|-------------------|-----|-----|-------------------|-------|

| S11 | SSI_BCLK cycle time                                              | t <sub>BCLK</sub> | 80  |     | ns                |       |

| S12 | SSI_BCLK pulse width high / low                                  |                   | 45% | 55% | t <sub>BCLK</sub> |       |

| S13 | SSI_FS input setup before SSI_BCLK                               |                   | 10  |     | ns                |       |

| S14 | SSI_FS input hold after SSI_BCLK                                 |                   | 2   |     | ns                |       |

| S15 | SSI_BCLK to SSI_TXD / SSI_FS output valid                        |                   |     | 15  | ns                |       |

| S16 | S16 SSI_BCLK to SSI_TXD / SSI_FS output invalid / high impedance |                   | 0   | 1   | ns                |       |

| S17 | S17 SSI_RXD setup before SSI_BCLK                                |                   | 15  |     | ns                |       |

| S18 | SSI_RXD hold after SSI_BCLK                                      |                   | 2   | _   | ns                |       |

<sup>&</sup>lt;sup>1</sup> All timings specified with a capacitive load of 25pF.

<sup>&</sup>lt;sup>2</sup> SSI\_BCLK can be generated from SSI\_CLKIN or a divided version of the internal system clock (f<sub>sys</sub>).

<sup>3</sup> SSI\_BCLK can be derived from SSI\_CLKIN or a divided version of the internal system clock (f<sub>sys</sub>).

53

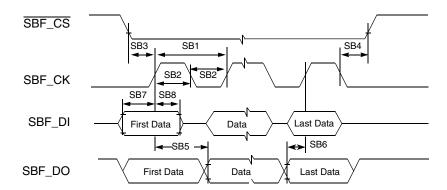

## 4.25 SBF timing specifications

The Serial boot facility (SBF) provides a means to read configuration information and system boot code from a broad array of SPI-compatible EEPROMs, flashes, FRAMs, nVSRAMs, etc. Table 37 provides the AC timing specifications for the SBF.

All SBF signals use pad type pad\_msr. The following timing specifications assume a pad slew rate setting of 11 and a load of 50 pF.<sup>1</sup>

| Name | Characteristic                | Symbol             | Min                      | Max  | Unit               | Notes |

|------|-------------------------------|--------------------|--------------------------|------|--------------------|-------|

| _    | SBF_CK frequency              | f <sub>SBFCK</sub> |                          | 62.5 | MHz                |       |

| SB1  | SBF_CK cycle time             | t <sub>SBFCK</sub> | 16.67                    | _    | ns                 | 1     |

| SB2  | SBF_CK high/low time          | _                  | 30%                      | _    | t <sub>SBFCK</sub> |       |

| SB3  | SBF_CS to SBF_CK delay        | _                  | t <sub>SBFCK</sub> - 2.0 | _    | ns                 |       |

| SB4  | SBF_CK to SBF_CS delay        | _                  | t <sub>SBFCK</sub> - 2.0 | _    | ns                 |       |

| SB5  | SBF_CK to SBF_DO valid        | _                  | _                        | 5    | ns                 |       |

| SB6  | SBF_CK to SBF_DO invalid      | _                  | <b>-</b> 5               | _    | ns                 |       |

| SB7  | SBF_DI to SBF_SCK input setup | _                  | 10                       | _    | ns                 |       |

| SB8  | SBF_CK to SBF_DI input hold   | _                  | 0                        | _    | ns                 |       |

Table 37. SBF AC timing specifications

At reset, the SBF\_CK cycle time is  $t_{REF} \times 60$ . The first byte of data read from the serial memory contains a divider value that is used to set the SBF\_CK cycle time for the duration of the serial boot process.

Figure 34. SBF timing

<sup>1.</sup> These timing parameters are specified assuming maximum operating frequency and the fastest pad slew rate setting (11). When operating this interface at lower frequencies, increase the slew rate by using the 10, 01, or 00 setting to increase edge rise and fall times, thus reducing EMI.

MCF5441x ColdFire Microprocessor Data Sheet, Rev. 8

#### **Electrical characteristics**

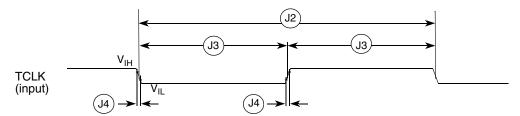

Figure 37. Test clock input timing

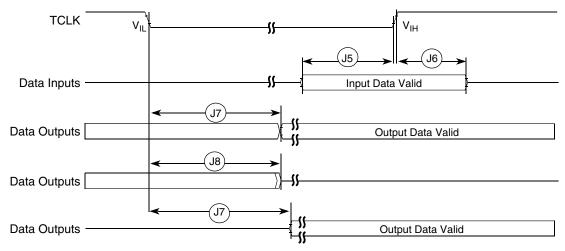

Figure 38. Boundary scan (JTAG) timing

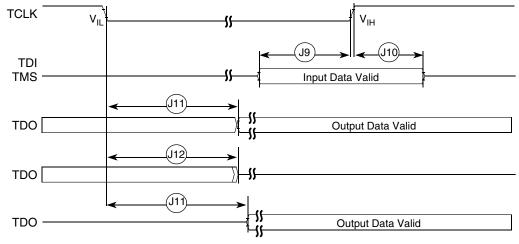

Figure 39. Test access port timing

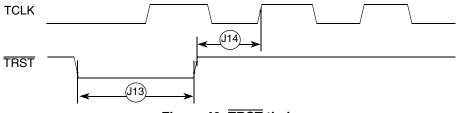

Figure 40. TRST timing

MCF5441x ColdFire Microprocessor Data Sheet, Rev. 8

#### **Package information**

# 5 Package information

The latest package outline drawings are available on the product summary pages on http://www.freescale.com/coldfire. Table 42 lists the case outline numbers per device. Use these numbers in the web page's keyword search engine to find the latest package outline drawings.

**Table 42. Package information**

| Device   | Package type | Case outline numbers |

|----------|--------------|----------------------|

| MCF54410 | 196 MAPBGA   | 98ASA00321D          |

| MCF54415 |              |                      |

| MCF54416 | 256 MAPBGA   | 98ARH98219A          |

| MCF54417 |              | 90ANN90219A          |

| MCF54418 |              |                      |

## 6 Product documentation

Documentation is available from a local Freescale distributor, a Freescale sales office, the Freescale Literature Distribution Center, or through the Freescale world-wide web address at http://www.freescale.com/coldfire.

#### How to Reach Us:

**Home Page:**

www.freescale.com

Web Support:

http://www.freescale.com/support

**USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

+1-800-521-6274 or +1-480-768-2130

www.freescale.com/support

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

For Literature Requests Only: Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: MCF54418

Rev. 8 06/2012 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see <a href="http://www.freescale.com">http://www.freescale.com</a> or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2011-2012. All rights reserved.