#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | Н8/300Н                                                                     |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 18MHz                                                                       |

| Connectivity               | SCI, SmartCard                                                              |

| Peripherals                | DMA, PWM, WDT                                                               |

| Number of I/O              | 55                                                                          |

| Program Memory Size        | 128KB (128K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-BQFP                                                                     |

| Supplier Device Package    | 80-QFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df3039f18v |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table 2.8Branching Instructions

| Instruction                                           | Size | Function                                                                                                     |                                  |                           |  |  |

|-------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------------|--|--|

| Bcc                                                   | —    | Branches to a specified address if a specified condition is true. The branching conditions are listed below. |                                  |                           |  |  |

|                                                       |      | Mnemonic                                                                                                     | Description                      | Condition                 |  |  |

|                                                       |      | BRA (BT)                                                                                                     | Always (true)                    | Always                    |  |  |

|                                                       |      | BRN (BF)                                                                                                     | Never (false)                    | Never                     |  |  |

|                                                       |      | BHI                                                                                                          | High                             | $C \lor Z = 0$            |  |  |

|                                                       |      | BLS                                                                                                          | Low or same                      | C ∨ Z = 1                 |  |  |

|                                                       |      | Bcc (BHS)                                                                                                    | Carry clear (high or same)       | C = 0                     |  |  |

|                                                       |      | BCS (BLO)                                                                                                    | Carry set (low)                  | C = 1                     |  |  |

|                                                       |      | BNE                                                                                                          | Not equal                        | Z = 0                     |  |  |

|                                                       |      | BEQ                                                                                                          | Equal                            | Z = 1                     |  |  |

|                                                       |      | BVC                                                                                                          | Overflow clear                   | V = 0                     |  |  |

|                                                       |      | BVS                                                                                                          | Overflow set                     | V = 1                     |  |  |

|                                                       |      | BPL                                                                                                          | Plus                             | N = 0                     |  |  |

|                                                       |      | BMI                                                                                                          | Minus                            | N = 1                     |  |  |

|                                                       |      | BGE                                                                                                          | Greater or equal                 | $N \oplus V = 0$          |  |  |

|                                                       |      | BLT                                                                                                          | Less than                        | N ⊕ V = 1                 |  |  |

|                                                       |      | BGT                                                                                                          | Greater than                     | $Z \lor (N \oplus V) = 0$ |  |  |

|                                                       |      | BLE                                                                                                          | Less or equal                    | $Z \lor (N \oplus V) = 1$ |  |  |

|                                                       |      |                                                                                                              |                                  |                           |  |  |

| JMP                                                   | _    | Branches unconditionally to a specified address                                                              |                                  |                           |  |  |

| BSR — Branches to a subroutine at a specified address |      |                                                                                                              |                                  |                           |  |  |

| JSR                                                   | _    | Branches to a se                                                                                             | ubroutine at a specified address |                           |  |  |

| RTS                                                   | _    | Returns from a subroutine                                                                                    |                                  |                           |  |  |

BCLR, BNOT, and BTST instructions) or immediate (3-bit) addressing mode to specify a bit number in the operand.

# Table 2.11 Addressing Modes

| No. | Addressing Mode                       | Symbol                   |

|-----|---------------------------------------|--------------------------|

| 1   | Register direct                       | Rn                       |

| 2   | Register indirect                     | @ERn                     |

| 3   | Register indirect with displacement   | @(d:16, ERn)/@d:24, ERn) |

| 4   | Register indirect with post-increment | @Ern+                    |

|     | Register indirect with pre-decrement  | @-ERn                    |

| 5   | Absolute address                      | @aa:8/@aa:16/@aa:24      |

| 6   | Immediate                             | #xx:8/#xx:16/#xx:32      |

| 7   | Program-counter relative              | @(d:8, PC)/@(d:16, PC)   |

| 8   | Memory indirect                       | @@aa:8                   |

# 1. Register Direct—Rn

The register field of the instruction code specifies an 8-, 16-, or 32-bit register containing the operand. R0H to R7H and R0L to R7L can be specified as 8-bit registers. R0 to R7 and E0 to E7 can be specified as 16-bit registers. ER0 to ER7 can be specified as 32-bit registers.

# 2. Register Indirect—@ERn

The register field of the instruction code specifies an address register (ERn), the lower 24 bits of which contain the address of the operand.

# 3. Register Indirect with Displacement—@(d:16, ERn) or @(d:24, ERn)

A 16-bit or 24-bit displacement contained in the instruction code is added to the contents of an address register (ERn) specified by the register field of the instruction, and the lower 24 bits of the sum specify the address of a memory operand. A 16-bit displacement is sign-extended when added.

# Section 4 Exception Handling

# 4.1 Overview

# 4.1.1 Exception Handling Types and Priority

As table 4.1 indicates, exception handling may be caused by a reset, trap instruction, or interrupt. Exception handling is prioritized as shown in table 4.1. If two or more exceptions occur simultaneously, they are accepted and processed in priority order. Trap instruction exceptions are accepted at all times in the program execution state.

| Table 4.1 | Exception | Types and | Priority |

|-----------|-----------|-----------|----------|

|-----------|-----------|-----------|----------|

| Priority | Exception Type           | Start of Exception Handling                                                                                                |  |  |  |  |

|----------|--------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| High     | Reset                    | Starts immediately after a low-to-high transition at the RES pin                                                           |  |  |  |  |

|          | Interrupt                | Interrupt requests are handled when execution of the current instruction or handling of the current exception is completed |  |  |  |  |

| Low      | Trap instruction (TRAPA) | Started by execution of a trap instruction (TRAPA)                                                                         |  |  |  |  |

# 4.1.2 Exception Handling Operation

Exceptions originate from various sources. Trap instructions and interrupts are handled as follows.

- 1. The program counter (PC) and condition code register (CCR) are pushed onto the stack.

- 2. The CCR interrupt mask bit is set to 1.

- 3. A vector address corresponding to the exception source is generated, and program execution starts from the address indicated in the vector address.

For a reset exception, steps 2 and 3 above are carried out.

# Renesas

Bit 3—User Bit Enable (UE): Selects whether to use the UI bit in CCR as a user bit or an interrupt mask bit.

| Bit 3<br>UE | Description                                 |                 |

|-------------|---------------------------------------------|-----------------|

| 0           | UI bit in CCR is used as interrupt mask bit |                 |

| 1           | UI bit in CCR is used as user bit           | (Initial value) |

# Bit 2—NMI Edge Select (NMIEG): Selects the NMI input edge.

| Bit 2<br>NMIEG | Description                                         |                 |

|----------------|-----------------------------------------------------|-----------------|

| 0              | Interrupt is requested at falling edge of NMI input | (Initial value) |

| 1              | Interrupt is requested at rising edge of NMI input  |                 |

### 6.3.3 Wait Modes

Four wait modes can be selected for each area as shown in table 6.4.

| ASTCR    | WCER     | v        | WCR      |             |                        |  |

|----------|----------|----------|----------|-------------|------------------------|--|

| ASTn Bit | WCEn Bit | WMS1 Bit | WMS0 Bit | WSC Control | Wait Mode              |  |

| 0        | _        | —        | _        | Disabled    | No wait states         |  |

| 1        | 0        | _        | _        | Disabled    | Pin wait mode 0        |  |

|          | 1        | 0        | 0        | Enabled     | Programmable wait mode |  |

|          |          |          | 1        | Enabled     | No wait states         |  |

|          |          | 1        | 0        | Enabled     | Pin wait mode 1        |  |

|          |          |          | 1        | Enabled     | Pin auto-wait mode     |  |

### Table 6.4 Wait Mode Selection

Note: n = 0 to 7

The ASTn and WCEn bits can be set independently for each area. Bits WMS1 and WMS0 apply to all areas. All areas for which WSC control is enabled operate in the same wait mode.

# Renesas

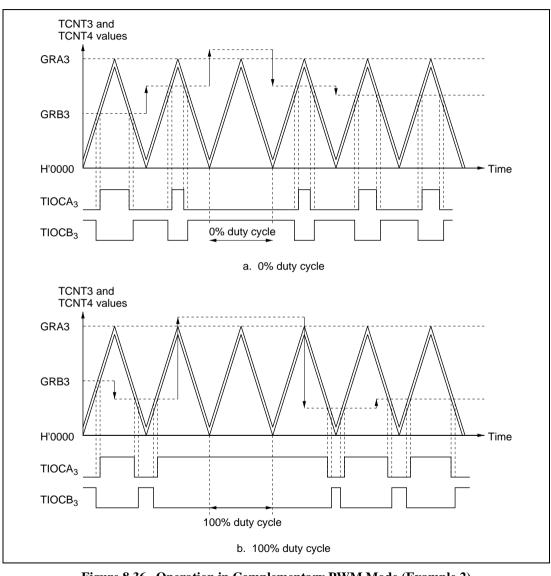

Figure 8.36 shows examples of waveforms with 0% and 100% duty cycles (in one phase) in complementary PWM mode. In this example the outputs change at compare match with GRB3, so waveforms with duty cycles of 0% or 100% can be output by setting GRB3 to a value larger than GRA3. The duty cycle can be changed easily during operation by use of the buffer registers. For further information see section 8.4.8, Buffering.

Figure 8.36 Operation in Complementary PWM Mode (Example 2) (when OLS3 = OLS4 = 1)

### 9.1.3 TPC Pins

Table 9.1 summarizes the TPC output pins.

# Table 9.1 TPC Pins

| Name Symbol I    |                      | I/O       | Function             |

|------------------|----------------------|-----------|----------------------|

| TPC output 0     | TP <sub>o</sub>      | Output    | Group 0 pulse output |

| TPC output 1     | TP <sub>1</sub>      | Output    |                      |

| TPC output 2     |                      | Output    |                      |

| TPC output 3     | TP <sub>3</sub>      | Output    |                      |

| TPC output 4     | TP <sub>4</sub>      | Output    | Group 1 pulse output |

| TPC output 5     | TP <sub>5</sub>      | Output    |                      |

| TPC output 6     | TP <sub>6</sub>      | Output    |                      |

| TPC output 7     | TP <sub>7</sub>      | Output    |                      |

| TPC output 8     | TP <sub>8</sub>      | Output    | Group 2 pulse output |

| TPC output 9     | TP <sub>9</sub>      | Output    |                      |

| TPC output 10    | TP <sub>10</sub>     | Output    |                      |

| TPC output 11    | TP <sub>11</sub>     | Output    |                      |

| TPC output 12    | TP <sub>12</sub>     | Output    | Group 3 pulse output |

| TPC output 13    | TP <sub>13</sub>     | Output    |                      |

| (TPC output 14)* | (TP <sub>14</sub> )* | (Output)* |                      |

| TPC output 15    | TP <sub>15</sub>     | Output    |                      |

Note: \* Since this LSI does not have this pin, this signal cannot be output to the outside.

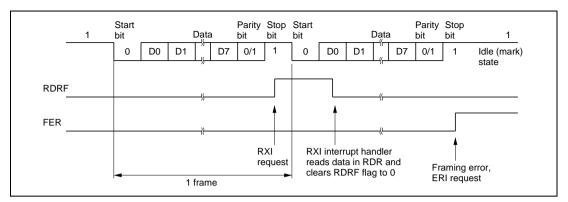

Figure 11.8 shows an example of SCI receive operation in asynchronous mode.

# Figure 11.8 Example of SCI Receive Operation (8-Bit Data with Parity and One Stop Bit)

### 11.3.3 Multiprocessor Communication

The multiprocessor communication function enables several processors to share a single serial communication line. The processors communicate in asynchronous mode using a format with an additional multiprocessor bit (multiprocessor format).

In multiprocessor communication, each receiving processor is addressed by an ID. A serial communication cycle consists of an ID-sending cycle that identifies the receiving processor, and a data-sending cycle. The multiprocessor bit distinguishes ID-sending cycles from data-sending cycles.

The transmitting processor starts by sending the ID of the receiving processor with which it wants to communicate as data with the multiprocessor bit set to 1. Next the transmitting processor sends transmit data with the multiprocessor bit cleared to 0.

Receiving processors skip incoming data until they receive data with the multiprocessor bit set to 1. When they receive data with the multiprocessor bit set to 1, receiving processors compare the data with their IDs. The receiving processor with a matching ID continues to receive further incoming data. Processors with IDs not matching the received data skip further incoming data until they again receive data with the multiprocessor bit set to 1. Multiple processors can send and receive data in this way.

Figure 11.9 shows an example of communication among different processors using a multiprocessor format.

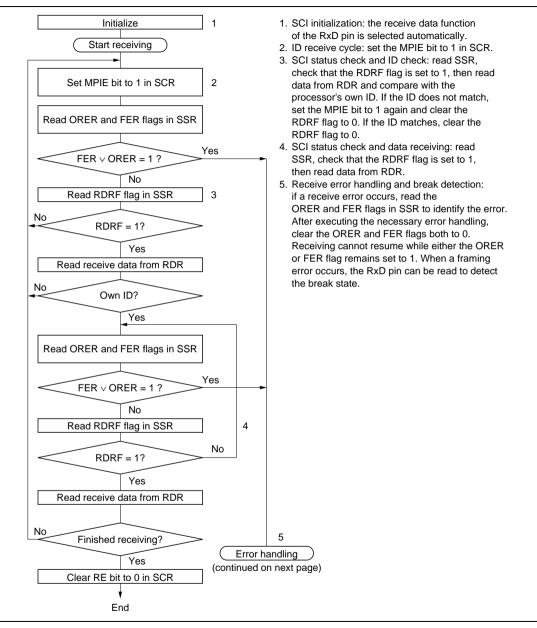

**Receiving Multiprocessor Serial Data:** Figure 11.12 shows a sample flowchart for receiving multiprocessor serial data and indicates the procedure to follow.

#### Renesas

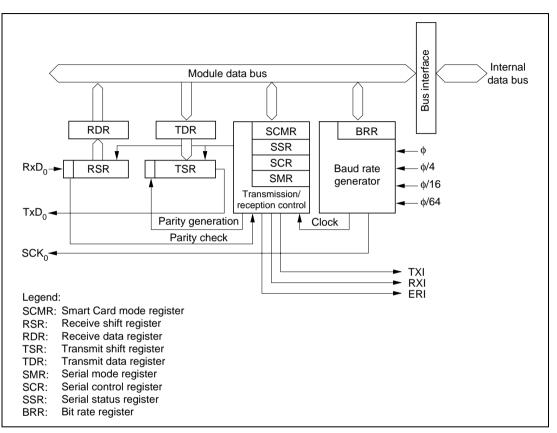

# 12.1.2 Block Diagram

Figure 12.1 shows a block diagram of the Smart Card interface.

Figure 12.1 Block Diagram of Smart Card Interface

See section 4.2.2, Reset Sequence and 15.9, Notes on Flash Memory Programming/Erasing. With the mask ROM version of the H8/3039, H8/3038, H8/3037, and H8/3036, the minimum reset period during operation is 10 system clocks. However, the flash memory versions of the H8/3039 requires a minimum of 20 system clocks.

# 15.4.2 User Program Mode

When set to the user program mode, this LSI can erase and program its flash memory by executing a user program. Therefore, on-chip flash memory on-board programming can be performed by providing a means of controlling FWE and supplying the write data on the board and providing a write program in a part of the program area.

To select this mode, set the LSI to on-chip ROM enable modes 5 and 7 and apply a high level to the FWE pin. In this mode, the peripheral functions, other than flash memory, are performed the same as in modes 5 and 7.

Since the flash memory cannot be read while it is being programmed/erased, place a programming program on external memory, or transfer the programming program to RAM area, and execute it in the RAM. In mode 6, do not program/erase the flash memory. When setting mode 6, always input low level to the FWE pin.

Figure 15.9 shows the procedure for executing when transferred to on-chip RAM. During reset start, starting from the user program mode is possible.

# **External Clock**

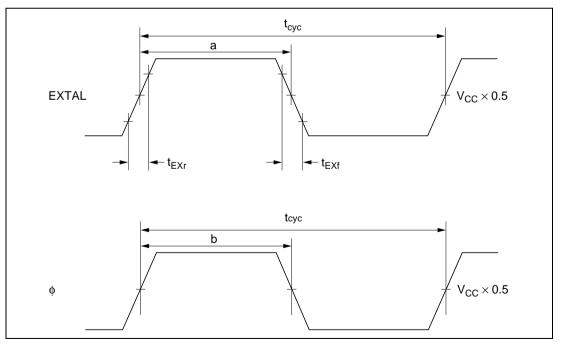

The external clock frequency should be equal to the system clock frequency ( $\phi$ ). Table 16.3 and figure 16.6 indicate the clock timing.

# Table 16.3 Clock Timing

|                                               |                                |     | V <sub>cc</sub> =<br>/ to 5.5 V |     | V <sub>cc</sub> =<br>V ±10% |      |                                 |

|-----------------------------------------------|--------------------------------|-----|---------------------------------|-----|-----------------------------|------|---------------------------------|

| ltem                                          | Symbol                         | Min | Max                             | Min | Max                         | Unit | Test Conditions                 |

| External clock rise time                      | $\mathbf{t}_{_{\mathrm{EXr}}}$ | _   | 10                              | _   | 5                           | ns   | Figure 16.6                     |

| External clock fall time                      | t <sub>exf</sub>               | —   | 10                              | —   | 5                           | ns   | _                               |

| External clock                                | _                              | 30  | 70                              | 30  | 70                          | %    | $\phi \ge 5 \text{ MHz}$ Figure |

| input duty (a/t <sub>cyc</sub> )              |                                | 40  | 60                              | 40  | 60                          | %    | φ < 5 MHz <sup>16.6</sup>       |

| $\phi$ clock width duty (b/t <sub>cyc</sub> ) | _                              | 40  | 60                              | 40  | 60                          | %    |                                 |

**Bit 7—Software Standby (SSBY):** Enables transition to software standby mode. When software standby mode is exited by an external interrupt, this bit remains set to 1 after the return to normal operation. To clear this bit, write 0.

| Bit 7 |                                                              |                 |

|-------|--------------------------------------------------------------|-----------------|

| SSBY  | Description                                                  |                 |

| 0     | SLEEP instruction causes transition to sleep mode            | (Initial value) |

| 1     | SLEEP instruction causes transition to software standby mode |                 |

**Bits 6 to 4—Standby Timer Select (STS2 to STS0):** These bits select the length of time the CPU and on-chip supporting modules wait for the clock to settle when software standby mode is exited by an external interrupt. If the clock is generated by a crystal resonator, set these bits according to the clock frequency so that the waiting time (for the clock to stabilize) will be at least 7 ms. See table 17.3. If an external clock is used, any setting is permitted.

| Bit 6<br>STS2 | Bit 5<br>STS1 | Bit 4<br>STS0 | Description                  |                 |

|---------------|---------------|---------------|------------------------------|-----------------|

| 0             | 0             | 0             | Waiting time = 8192 states   | (Initial value) |

|               |               | 1             | Waiting time = 16384 states  |                 |

|               | 1             | 0             | Waiting time = 32768 states  |                 |

|               |               | 1             | Waiting time = 65536 states  |                 |

| 1             | 0             | 0             | Waiting time = 131072 states |                 |

|               | 0             | 1             | Waiting time = 1024 states   |                 |

|               | 1             | —             | Illegal setting              |                 |

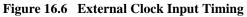

# 17.2.2 Module Standby Control Register (MSTCR)

MSTCR is an 8-bit readable/writable register that controls output of the system clock ( $\phi$ ). It also controls the module standby function, which places individual on-chip supporting modules in the standby state. Module standby can be designated for the ITU, SCI0, SCI1, and A/D converter modules.

MSTCR is initialized to H'40 by a reset and in hardware standby mode. It is not initialized in software standby mode.

**Bit 7—φ Clock Stop (PSTOP):** Enables or disables output of the system clock (φ).

| Bit 7<br>PSTOP | Description                     |                 |

|----------------|---------------------------------|-----------------|

| 0              | System clock output is enabled  | (Initial value) |

| 1              | System clock output is disabled |                 |

Bit 6—Reserved: This bit cannot be modified and is always read as 1.

Bit 5—Module Standby 5 (MSTOP5): Selects whether to place the ITU in standby.

| Bit 5<br>MSTOP5 | Description             |                 |

|-----------------|-------------------------|-----------------|

| 0               | ITU operates normally   | (Initial value) |

| 1               | ITU is in standby state |                 |

| 1           |                     | Instruction<br>Fetch | Addr. Read | • |   | Word Data<br>Access | Operation |

|-------------|---------------------|----------------------|------------|---|---|---------------------|-----------|

| Instruction | Mnemonic            | 1                    | J          | К | L | М                   | N         |

| Bcc         | BRA d:16 (BT d:16)  | 2                    |            |   |   |                     | 2         |

|             | BRN d:16 (BF d:16)  | 2                    |            |   |   |                     | 2         |

|             | BHI d:16            | 2                    |            |   |   |                     | 2         |

|             | BLS d:16            | 2                    |            |   |   |                     | 2         |

|             | BCC d:16 (BHS d:16) | 2                    |            |   |   |                     | 2         |

|             | BCS d:16 (BLO d:16) | 2                    |            |   |   |                     | 2         |

|             | BNE d:16            | 2                    |            |   |   |                     | 2         |

|             | BEQ d:16            | 2                    |            |   |   |                     | 2         |

|             | BVC d:16            | 2                    |            |   |   |                     | 2         |

|             | BVS d:16            | 2                    |            |   |   |                     | 2         |

|             | BPL d:16            | 2                    |            |   |   |                     | 2         |

|             | BMI d:16            | 2                    |            |   |   |                     | 2         |

|             | BGE d:16            | 2                    |            |   |   |                     | 2         |

|             | BLT d:16            | 2                    |            |   |   |                     | 2         |

|             | BGT d:16            | 2                    |            |   |   |                     | 2         |

|             | BLE d:16            | 2                    |            |   |   |                     | 2         |

| BCLR        | BCLR #xx:3, Rd      | 1                    |            |   |   |                     |           |

|             | BCLR #xx:3, @ERd    | 2                    |            |   | 2 |                     |           |

|             | BCLR #xx:3, @aa:8   | 2                    |            |   | 2 |                     |           |

|             | BCLR Rn, Rd         | 1                    |            |   |   |                     |           |

|             | BCLR Rn, @ERd       | 2                    |            |   | 2 |                     |           |

|             | BCLR Rn, @aa:8      | 2                    |            |   | 2 |                     |           |

| BIAND       | BIAND #xx:3, Rd     | 1                    |            |   |   |                     |           |

|             | BIAND #xx:3, @ERd   | 2                    |            |   | 1 |                     |           |

|             | BIAND #xx:3, @aa:8  | 2                    |            |   | 1 |                     |           |

| BILD        | BILD #xx:3, Rd      | 1                    |            |   |   |                     |           |

|             | BILD #xx:3, @ERd    | 2                    |            |   | 1 |                     |           |

|             | BILD #xx:3, @aa:8   | 2                    |            |   | 1 |                     |           |

| BIOR        | BIOR #xx:8, Rd      | 1                    |            |   |   |                     |           |

|             | BIOR #xx:8, @ERd    | 2                    |            |   | 1 |                     |           |

|             | BIOR #xx:8, @aa:8   | 2                    |            |   | 1 |                     |           |

| BIST        | BIST #xx:3, Rd      | 1                    |            |   |   |                     |           |

|             | BIST #xx:3, @ERd    | 2                    |            |   | 2 |                     |           |

|             | BIST #xx:3, @aa:8   | 2                    |            |   | 2 |                     |           |

| BIXOR       | BIXOR #xx:3, Rd     | 1                    |            |   |   |                     |           |

|             | BIXOR #xx:3, @ERd   | 2                    |            |   | 1 |                     |           |

|             | BIXOR #xx:3, @aa:8  | 2                    |            |   | 1 |                     |           |

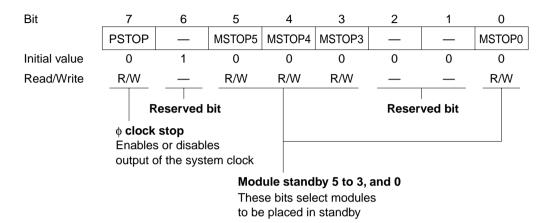

Note: \* Determined by pins P7<sub>7</sub> to P7<sub>0</sub>.

| P8DR—Port 8 Data Register |   |   |   | H'CF |     |     |      | Port 8          |   |

|---------------------------|---|---|---|------|-----|-----|------|-----------------|---|

| Bit                       | 7 | 6 | 5 | 4    | 3   | 2   | 1    | 0               | _ |

|                           |   | _ | _ | _    | _   | _   | P8 1 | P8 <sub>0</sub> |   |

| Initial value             | 1 | 1 | 1 | 0    | 0   | 0   | 0    | 0               | _ |

| Read/Write                | — | — | — | R/W  | R/W | R/W | R/W  | R/W             |   |

Data for port 8 pins

# Renesas

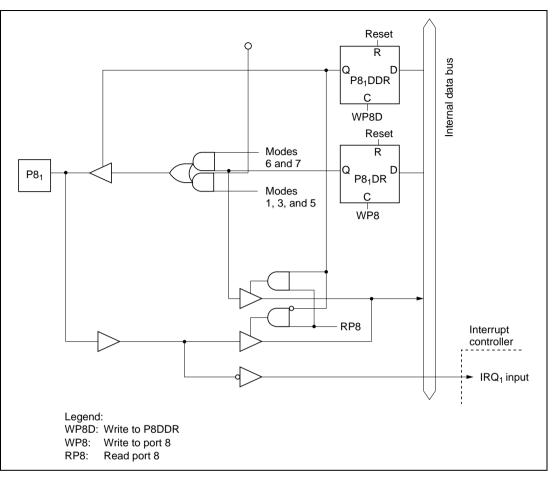

Figure C.7 (b) Port 8 Block Diagram (Pin P8<sub>1</sub>)

# C.9 Port A Block Diagram

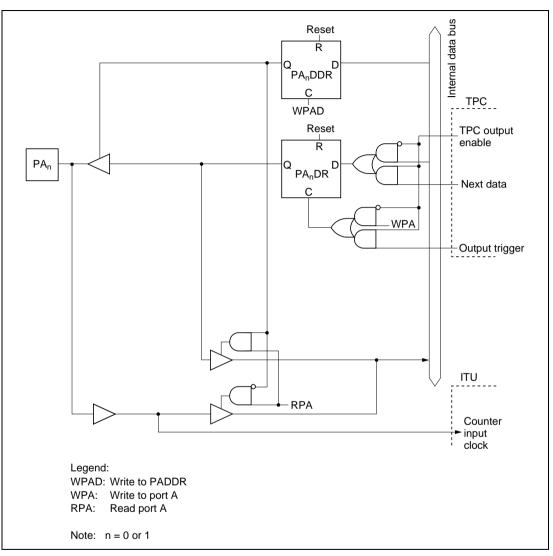

Figure C.9 (a) Port A Block Diagram (Pins PA<sub>0</sub>, PA<sub>1</sub>)

# Appendix F Product Lineup

# Table F.1 H8/3039 Group Product Lineup

| Product Type |                         |                | Part Number  | Mark Code         | Package<br>(Package Code) |  |  |

|--------------|-------------------------|----------------|--------------|-------------------|---------------------------|--|--|

| H8/3039      | Flash memory<br>version | 5 V<br>version | HD64F3039F   | HD64F3039F        | 80-pin QFP (FP-80A)       |  |  |

|              |                         |                | HD64F3039TE  | HD64F3039TE       | 80-pin TQFP (TFP-80C)     |  |  |

|              |                         | 3 V<br>version | HD64F3039VF  | HD64F3039VF       | 80-pin QFP (FP-80A)       |  |  |

|              |                         |                | HD64F3039VTE | HD64F3039VTE      | 80-pin TQFP (TFP-80C)     |  |  |

|              | Mask ROM                | 5 V<br>version | HD6433039F   | HD6433039(***)F   | 80-pin QFP (FP-80A)       |  |  |

|              | version                 |                | HD6433039TE  | HD6433039(***)TE  | 80-pin TQFP (TFP-80C)     |  |  |

|              |                         | 3 V            | HD6433039VF  | HD6433039(***)VF  | 80-pin QFP (FP-80A)       |  |  |

|              |                         | version        | HD6433039VTE | HD6433039(***)VTE | 80-pin TQFP (TFP-80C)     |  |  |

| H8/3038      | Mask ROM<br>version     | 5 V<br>version | HD6433038F   | HD6433038(***)F   | 80-pin QFP (FP-80A)       |  |  |

|              |                         |                | HD6433038TE  | HD6433038(***)TE  | 80-pin TQFP (TFP-80C)     |  |  |

|              |                         | 3 V            | HD6433038VF  | HD6433038(***)VF  | 80-pin QFP (FP-80A)       |  |  |

|              |                         | version        | HD6433038VTE | HD6433038(***)VTE | 80-pin TQFP (TFP-80C)     |  |  |

| H8/3037      | Mask ROM<br>version     | 5 V<br>version | HD6433037F   | HD6433037(***)F   | 80-pin QFP (FP-80A)       |  |  |

|              |                         |                | HD6433037TE  | HD6433037(***)TE  | 80-pin TQFP (TFP-80C)     |  |  |

|              |                         | 3 V            | HD6433037VF  | HD6433037(***)VF  | 80-pin QFP (FP-80A)       |  |  |

|              |                         | version        | HD6433037VTE | HD6433037(***)VTE | 80-pin TQFP (TFP-80C)     |  |  |

| H8/3036      | Mask ROM<br>version     | 5 V<br>version | HD6433036F   | HD6433036(***)F   | 80-pin QFP (FP-80A)       |  |  |

|              |                         |                | HD6433036TE  | HD6433036(***)TE  | 80-pin TQFP (TFP-80C)     |  |  |

|              |                         | 3 V<br>version | HD6433036VF  | HD6433036(***)VF  | 80-pin QFP (FP-80A)       |  |  |

|              |                         |                | HD6433036VTE | HD6433036(***)VTE | 80-pin TQFP (TFP-80C)     |  |  |

Note: (\*\*\*) in mask ROM versions is the ROM code.

RenesasTechnology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

#### RENESAS SALES OFFICES

http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

Renesas Technology America, Inc. 450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited Dukes Meadow, Miliboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <85- (21) 5877-1818, Fax: <85> (21) 6887-7898

# Renesas Technology Hong Kong Ltd. 7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852- 2265-6688, Fax: <852- 2730-6071

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

Renesas Technology Singapore Pte. Ltd. 1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bléd., 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603- 7955-9309, Fax: <603- 7955-9510