Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                      |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z4d                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 120MHz                                                                   |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 147                                                                      |

| Program Memory Size        | 1.5MB (1.5M × 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 128K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                |

| Data Converters            | A/D 27x10b, 5x12b                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 176-LQFP                                                                 |

| Supplier Device Package    | 176-LQFP (24x24)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc564b64l7c8e0x |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| <b>Revision history</b> | у | 118 |

|-------------------------|---|-----|

|-------------------------|---|-----|

# 1 Introduction

### 1.1 Document Overview

This document describes the features of the family and options available within the family members, and highlights important electrical and physical characteristics of the SPC564Bxx and SPC56ECxx device. To ensure a complete understanding of the device functionality, refer also to the SPC564Bxx and SPC56ECxx Reference Manual.

## 1.2 Description

The SPC564Bxx and SPC56ECxx is a new family of next generation microcontrollers built on the Power Architecture embedded category. This document describes the features of the family and options available within the family members, and highlights important electrical and physical characteristics of the device.

The SPC564Bxx and SPC56ECxx family expands the range of the SPC560B microcontroller family. It provides the scalability needed to implement platform approaches and delivers the performance required by increasingly sophisticated software architectures. The advanced and cost-efficient host processor core of the SPC564Bxx and SPC56ECxx automotive controller family complies with the Power Architecture embedded category, which is 100 percent user-mode compatible with the original Power Architecture user instruction set architecture (UISA). It operates at speeds of up to 120 MHz and offers high performance processing optimized for low power consumption. It also capitalizes on the available development infrastructure of current Power Architecture devices and is supported with software drivers, operating systems and configuration code to assist with users implementations.

# 2.3 Functional ports

The functional port pins are listed in *Table 5*.

|             |        |                                      |                                                                            |                                                                 |                                    |          |                  | Pir      | n numbe  | ər      |

|-------------|--------|--------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------|----------|------------------|----------|----------|---------|

| Port<br>pin | PCR    | Alternate<br>function <sup>(1)</sup> | Function                                                                   | Peripheral                                                      | VO<br>direction <sup>(2)</sup>     | Pad type | RESET<br>config. | LQFP 176 | LQFP 208 | LBGA256 |

| PA[0]       | PCR[0] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[0]<br>E0UC[0]<br>CLKOUT<br>E0UC[13]<br>WKPU[19]<br>CAN1RX             | SIUL<br>eMIOS_0<br>MC_CGM<br>eMIOS_0<br>WKPU<br>FlexCAN_1       | /O<br> /O<br>0<br> /O<br> <br>     | M/S      | Tristate         | 24       | 24       | G4      |

| PA[1]       | PCR[1] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—   | GPIO[1]<br>E0UC[1]<br>—<br>WKPU[2]<br>CAN3RX<br>NMI[0] <sup>(3)</sup>      | SIUL<br>eMIOS_0<br>—<br>WKPU<br>FlexCAN_3<br>WKPU               | /O<br> /O<br> -<br> <br> <br> <br> | S        | Tristate         | 19       | 19       | F3      |

| PA[2]       | PCR[2] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[2]<br>E0UC[2]<br>—<br>MA[2]<br>WKPU[3]<br>NMI[1] <sup>(3)</sup>       | SIUL<br>eMIOS_0<br>—<br>ADC_0<br>WKPU<br>WKPU                   | I/O<br>I/O<br>—<br>0<br>I<br>I     | S        | Tristate         | 17       | 17       | F1      |

| PA[3]       | PCR[3] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—   | GPIO[3]<br>E0UC[3]<br>LIN5TX<br>CS4_1<br>RX_ER_CLK<br>EIRQ[0]<br>ADC1_S[0] | SIUL<br>eMIOS_0<br>LINFlexD_5<br>DSPI_1<br>FEC<br>SIUL<br>ADC_1 | I/O<br>I/O<br>O<br>I<br>I<br>I     | M/S      | Tristate         | 114      | 138      | G16     |

| PA[4]       | PCR[4] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[4]<br>E0UC[4]<br>—<br>CS0_1<br>LIN5RX<br>WKPU[9]                      | SIUL<br>eMIOS_0<br>—<br>DSPI_1<br>LINFlexD_5<br>WKPU            | /O<br> /O<br> /O<br> <br>          | S        | Tristate         | 51       | 61       | T2      |

DocID17478 Rev 9

-

|             |         |                                      |                                                                   |                                                                  |                                     |          |                  | Pin number |          |         |  |

|-------------|---------|--------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------|----------|------------------|------------|----------|---------|--|

| Port<br>pin | PCR     | Alternate<br>function <sup>(1)</sup> | Function                                                          | Peripheral                                                       | I/O<br>direction <sup>(2)</sup>     | Pad type | RESET<br>config. | LQFP 176   | LQFP 208 | LBGA256 |  |

| PF[8]       | PCR[88] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[88]<br>CAN3TX<br>CS4_0<br>CAN2TX                             | SIUL<br>FlexCAN_3<br>DSPI_0<br>FlexCAN_2                         | I/O<br>O<br>O<br>O                  | M/S      | Tristate         | 42         | 50       | N2      |  |

| PF[9]       | PCR[89] | AF0<br>AF1<br>AF2<br>AF3<br>—<br>—   | GPIO[89]<br>E1UC[1]<br>CS5_0<br>—<br>CAN2RX<br>CAN3RX<br>WKPU[22] | SIUL<br>eMIOS_1<br>DSPI_0<br>—<br>FlexCAN_2<br>FlexCAN_3<br>WKPU | I/O<br>I/O<br>O<br>I<br>I<br>I<br>I | S        | Tristate         | 41         | 49       | M4      |  |

| PF[10]      | PCR[90] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[90]<br>CS1_0<br>LIN4TX<br>E1UC[2]                            | SIUL<br>DSPI_0<br>LINFlexD_4<br>eMIOS_1                          | I/O<br>O<br>O<br>I/O                | M/S      | Tristate         | 46         | 54       | P2      |  |

| PF[11]      | PCR[91] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[91]<br>CS2_0<br>E1UC[3]<br>—<br>LIN4RX<br>WKPU[15]           | SIUL<br>DSPI_0<br>eMIOS_1<br>—<br>LINFlexD_4<br>WKPU             | I/O<br>O<br>I/O<br>I<br>I           | S        | Tristate         | 47         | 55       | R1      |  |

| PF[12]      | PCR[92] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[92]<br>E1UC[25]<br>LIN5TX<br>—                               | SIUL<br>eMIOS_1<br>LINFlexD_5<br>—                               | I/O<br>I/O<br>O                     | M/S      | Tristate         | 43         | 51       | P1      |  |

| PF[13]      | PCR[93] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[93]<br>E1UC[26]<br>—<br>LIN5RX<br>WKPU[16]                   | SIUL<br>eMIOS_1<br>—<br>LINFlexD_5<br>WKPU                       | I/O<br>I/O<br>—<br>I<br>I           | S        | Tristate         | 49         | 57       | P3      |  |

Table 5. Functional port pin descriptions (continued)

|             |          |                                       |                                                 |                                              |                                 |          |                  | Pir      | n numbe  | ər      |

|-------------|----------|---------------------------------------|-------------------------------------------------|----------------------------------------------|---------------------------------|----------|------------------|----------|----------|---------|

| Port<br>pin | PCR      | Alternate<br>function <sup>(1)</sup>  | Function                                        | Peripheral                                   | I/O<br>direction <sup>(2)</sup> | Pad type | RESET<br>config. | LQFP 176 | LQFP 208 | LBGA256 |

| PG[10]      | PCR[106] | AF0<br>AF1<br>AF2<br>AF3<br>—         | GPIO[106]<br>E0UC[24]<br>E1UC[31]<br>—<br>SIN_4 | SIUL<br>eMIOS_0<br>eMIOS_1<br>—<br>DSPI_4    | /O<br> /O<br> /O<br>            | S        | Tristate         | 138      | 162      | B13     |

| PG[11]      | PCR[107] | AF0<br>AF1<br>AF2<br>AF3              | GPIO[107]<br>E0UC[25]<br>CS0_4<br>CS0_6         | SIUL<br>eMIOS_0<br>DSPI_4<br>DSPI_6          | I/O<br>I/O<br>I/O<br>I/O        | M/S      | Tristate         | 139      | 163      | A16     |

| PG[12]      | PCR[108] | AF0<br>AF1<br>AF2<br>AF3<br>ALT4      | GPIO[108]<br>E0UC[26]<br>SOUT_4<br>—<br>TXD[2]  | SIUL<br>eMIOS_0<br>DSPI_4<br>—<br>FEC        | I/O<br>I/O<br>O<br>O            | M/S      | Tristate         | 116      | 140      | F15     |

| PG[13]      | PCR[109] | AF0<br>AF1<br>AF2<br>AF3<br>ALT4      | GPIO[109]<br>E0UC[27]<br>SCK_4<br>—<br>TXD[3]   | SIUL<br>eMIOS_0<br>DSPI_4<br>—<br>FEC        | /O<br> /O<br> /O<br>            | M/S      | Tristate         | 115      | 139      | F16     |

| PG[14]      | PCR[110] | AF0<br>AF1<br>AF2<br>AF3<br>—         | GPIO[110]<br>E1UC[0]<br>LIN8TX<br>—<br>SIN_6    | SIUL<br>eMIOS_1<br>LINFlexD_8<br>—<br>DSPI_6 | I/O<br>I/O<br>O<br>I            | S        | Tristate         | 134      | 158      | C13     |

| PG[15]      | PCR[111] | AF0<br>AF1<br>AF2<br>AF3<br>—         | GPIO[111]<br>E1UC[1]<br>SOUT_6<br>—<br>LIN8RX   | SIUL<br>eMIOS_1<br>DSPI_6<br>—<br>LINFlexD_8 | I/O<br>I/O<br>O<br>I            | M/S      | Tristate         | 135      | 159      | D13     |

| PH[0]       | PCR[112] | AF0<br>AF1<br>AF2<br>AF3<br>ALT4<br>— | GPIO[112]<br>E1UC[2]<br>—<br>TXD[1]<br>SIN_1    | SIUL<br>eMIOS_1<br>—<br>FEC<br>DSPI_1        | I/O<br>I/O<br>  0<br>I          | M/S      | Tristate         | 117      | 141      | E15     |

Table 5. Functional port pin descriptions (continued)

| Table 5. Functional port pin descriptions (continued) |          |                                      |                                                       |                                                 |                                 |          |                  |          |          |         |

|-------------------------------------------------------|----------|--------------------------------------|-------------------------------------------------------|-------------------------------------------------|---------------------------------|----------|------------------|----------|----------|---------|

|                                                       |          |                                      |                                                       |                                                 |                                 |          |                  | Pir      | n numbe  | er      |

| Port<br>pin                                           | PCR      | Alternate<br>function <sup>(1)</sup> | Function                                              | Peripheral                                      | I/O<br>direction <sup>(2)</sup> | Pad type | RESET<br>config. | LQFP 176 | LQFP 208 | LBGA256 |

| PI[0]                                                 | PCR[128] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[128]<br>E0UC[28]<br>LIN8TX<br>—                  | SIUL<br>eMIOS_0<br>LINFlexD_8<br>—              | I/O<br>I/O<br>O                 | S        | Tristate         | 172      | 196      | C5      |

| PI[1]                                                 | PCR[129] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[129]<br>E0UC[29]<br>—<br>—<br>WKPU[24]<br>LIN8RX | SIUL<br>eMIOS_0<br>—<br>—<br>WKPU<br>LINFlexD_8 | I/O<br>I/O<br>—<br>I<br>I       | S        | Tristate         | 171      | 195      | A4      |

| PI[2]                                                 | PCR[130] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[130]<br>E0UC[30]<br>LIN9TX<br>—                  | SIUL<br>eMIOS_0<br>LINFlexD_9<br>—              | I/O<br>I/O<br>O                 | S        | Tristate         | 170      | 194      | D6      |

| PI[3]                                                 | PCR[131] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[131]<br>E0UC[31]<br>—<br>—<br>WKPU[23]<br>LIN9RX | SIUL<br>eMIOS_0<br>—<br>—<br>WKPU<br>LINFlexD_9 | /O<br> /O<br><br> <br> <br>     | S        | Tristate         | 169      | 193      | B5      |

| PI[4]                                                 | PCR[132] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[132]<br>E1UC[28]<br>SOUT_4<br>—                  | SIUL<br>eMIOS_1<br>DSPI_4<br>—                  | I/O<br>I/O<br>O                 | M/S      | Tristate         | 143      | 167      | A12     |

| PI[5]                                                 | PCR[133] | AF0<br>AF1<br>AF2<br>AF3<br>ALT4     | GPIO[133]<br>E1UC[29]<br>SCK_4<br>CS2_5<br>CS2_6      | SIUL<br>eMIOS_1<br>DSPI_4<br>DSPI_5<br>DSPI_6   | I/O<br>I/O<br>I/O<br>O          | M/S      | Tristate         | 142      | 166      | D12     |

| PI[6]                                                 | PCR[134] | AF0<br>AF1<br>AF2<br>AF3<br>ALT4     | GPIO[134]<br>E1UC[30]<br>CS0_4<br>CS0_5<br>CS0_6      | SIUL<br>eMIOS_1<br>DSPI_4<br>DSPI_5<br>DSPI_6   | I/O<br>I/O<br>I/O<br>I/O        | S        | Tristate         | 11       | 11       | D2      |

| Tabl | e 5. Functional | port pin descri | ptions | (con | tinued) |  |

|------|-----------------|-----------------|--------|------|---------|--|

|      |                 |                 |        |      |         |  |

|             |          |                                      |                                                    |                                             |                                 |          |                  | Pir      | n numbe  | er      |

|-------------|----------|--------------------------------------|----------------------------------------------------|---------------------------------------------|---------------------------------|----------|------------------|----------|----------|---------|

| Port<br>pin | PCR      | Alternate<br>function <sup>(1)</sup> | Function                                           | Peripheral                                  | I/O<br>direction <sup>(2)</sup> | Pad type | RESET<br>config. | LQFP 176 | LQFP 208 | LBGA256 |

| PI[13]      | PCR[141] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[141]<br>CS1_3<br>CS1_2<br>—<br>ADC0_S[21]     | SIUL<br>DSPI_3<br>DSPI_2<br>—<br>ADC_0      | I/O<br>O<br>O<br>I              | S        | Tristate         | 113      | 137      | G14     |

| PI[14]      | PCR[142] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[142]<br>—<br>—<br>ADC0_S[22]<br>SIN_4         | SIUL<br>—<br>—<br>ADC_0<br>DSPI_4           | I/O<br>—<br>—<br>—<br>I<br>I    | S        | Tristate         | 76       | 92       | T12     |

| PI[15]      | PCR[143] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[143]<br>CS0_4<br>CS2_2<br>—<br>ADC0_S[23]     | SIUL<br>DSPI_4<br>DSPI_2<br>—<br>ADC_0      | I/O<br>I/O<br>O<br>I            | S        | Tristate         | 75       | 91       | P11     |

| PJ[0]       | PCR[144] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[144]<br>CS1_4<br>CS3_2<br>—<br>ADC0_S[24]     | SIUL<br>DSPI_4<br>DSPI_2<br>—<br>ADC_0      | I/O<br>O<br>—<br>I              | S        | Tristate         | 74       | 90       | R11     |

| PJ[1]       | PCR[145] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[145]<br>—<br>—<br>—<br>ADC0_S[25]<br>SIN_5    | SIUL<br>—<br>—<br>ADC_0<br>DSPI_5           | I/O<br>—<br>—<br>—<br>I<br>I    | S        | Tristate         | 73       | 89       | N10     |

| PJ[2]       | PCR[146] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[146]<br>CS0_5<br>CS0_6<br>CS0_7<br>ADC0_S[26] | SIUL<br>DSPI_5<br>DSPI_6<br>DSPI_7<br>ADC_0 | /O<br> /O<br> /O<br> /O<br>     | S        | Tristate         | 72       | 88       | R10     |

Table 5. Functional port pin descriptions (continued)

|             |          |                                      |                                  |                              |                                 |          |                  | Pir      | n numbe  | ər      |

|-------------|----------|--------------------------------------|----------------------------------|------------------------------|---------------------------------|----------|------------------|----------|----------|---------|

| Port<br>pin | PCR      | Alternate<br>function <sup>(1)</sup> | Function                         | Peripheral                   | I/O<br>direction <sup>(2)</sup> | Pad type | RESET<br>config. | LQFP 176 | LQFP 208 | LBGA256 |

| PL[6]       | PCR[182] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[182]<br>—<br>MDO4<br>—      | SIUL<br>—<br>Nexus<br>—      | I/O<br>—<br>O<br>—              | M/S      | Tristate         | _        | _        | K5      |

| PL[7]       | PCR[183] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[183]<br>—<br>MDO5<br>—      | SIUL<br>—<br>Nexus<br>—      | I/O<br>—<br>O<br>—              | M/S      | Tristate         | _        | _        | L5      |

| PL[8]       | PCR[184] | AF0<br>AF1<br>AF2<br>AF3<br>—        | GPIO[184]<br>—<br>—<br>—<br>EVTI | SIUL<br>—<br>—<br>—<br>Nexus | I/O<br>—<br>—<br>—<br>I         | S        | Pull-up          |          |          | M9      |

| PL[9]       | PCR[185] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[185]<br>—<br>MSEO<br>—      | SIUL<br>—<br>Nexus<br>—      | I/O<br>—<br>O<br>—              | M/S      | Tristate         |          | _        | M10     |

| PL[10]      | PCR[186] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[186]<br>—<br>MCKO<br>—      | SIUL<br>—<br>Nexus<br>—      | I/O<br>—<br>O<br>—              | F/S      | Tristate         | _        | _        | M11     |

| PL[11]      | PCR[187] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[187]<br>—<br>—<br>—         | SIUL<br>—<br>—<br>—          | I/O<br>—<br>—                   | M/S      | Tristate         | _        | _        | M12     |

| PL[12]      | PCR[188] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[188]<br>—<br>EVTO<br>—      | SIUL<br>—<br>Nexus<br>—      | I/O<br>—<br>O<br>—              | M/S      | Tristate         | _        | _        | F11     |

| PL[13]      | PCR[189] | AF0<br>AF1<br>AF2<br>AF3             | GPIO[189]<br>—<br>MDO6<br>—      | SIUL<br>—<br>Nexus<br>—      | I/O<br>—<br>O<br>—              | M/S      | Tristate         | _        | _        | F10     |

Table 5. Functional port pin descriptions (continued)

| Cumhal                       |        | Devenuetor                                                                    | Conditions                                         | Val                        | ue                                 | 11        |

|------------------------------|--------|-------------------------------------------------------------------------------|----------------------------------------------------|----------------------------|------------------------------------|-----------|

| Symbol                       |        | Parameter                                                                     | Conditions                                         | Min                        | Max                                | Unit      |

|                              |        |                                                                               | —                                                  | 4.5                        | 5.5                                |           |

| V <sub>DD_HV_ADC0</sub>      | S      | Voltage on VDD_HV_ADC0 with                                                   | Voltage drop <sup>(2)</sup>                        | 3.0                        | 5.5                                | v         |

| (3)                          | R      | respect to ground (V <sub>SS_HV</sub> )                                       | Relative to<br>V <sub>DD_HV_A</sub> <sup>(6)</sup> | V <sub>DD_HV_A</sub> - 0.1 | V <sub>DD_HV_A</sub> + 0.1         |           |

|                              |        |                                                                               | _                                                  | 4.5                        | 5.5                                |           |

| V <sub>DD_HV_ADC1</sub>      | S      | Voltage on VDD_HV_ADC1 with                                                   | Voltage drop <sup>(2)</sup>                        | 3.0                        | 5.5                                | v         |

|                              | R      | respect to ground (V <sub>SS_HV</sub> )                                       | Relative to $V_{DD_HV_A}^{(6)}$                    | V <sub>DD_HV_A</sub> - 0.1 | V <sub>DD_HV_A</sub> + 0.1         |           |

|                              | s      | Voltage on any GPIO pin with                                                  |                                                    | V <sub>SS_HV</sub> -0.1    |                                    |           |

| V <sub>IN</sub>              | R      | respect to ground (V <sub>SS_HV</sub> )                                       | Relative to<br>V <sub>DD_HV_A/HV_B</sub>           | _                          | V <sub>DD_HV_A/HV_B</sub><br>+ 0.1 | V         |

| I <sub>INJPAD</sub>          | S<br>R | Injected input current on any pin<br>during overload condition                | _                                                  | -5                         | 5                                  |           |

| I <sub>INJSUM</sub>          | S<br>R | Absolute sum of all injected input<br>currents during overload —<br>condition |                                                    | -50                        | 50                                 | mA        |

| TV <sub>DD</sub>             | s      | V <sub>DD_HV_A</sub> slope to ensure correct                                  | —                                                  | —                          | 0.5                                | V/µs      |

| I V DD                       | R      | power up <sup>(8)</sup>                                                       | —                                                  | 0.5                        | —                                  | V/min     |

| T <sub>A C-Grade</sub> Part  | S<br>R | Ambient temperature under bias                                                | _                                                  | -40                        | 85                                 |           |

| T <sub>J C-Grade</sub> Part  | S<br>R | Junction temperature under bias                                               | _                                                  | -40                        | 110                                |           |

| T <sub>A V-Grade</sub> Part  | S<br>R | Ambient temperature under bias                                                | _                                                  | -40                        | 105                                | <b>0°</b> |

| T <sub>J V-Grade Part</sub>  | S<br>R | Junction temperature under bias                                               | —                                                  | -40                        | 130                                |           |

| T <sub>A M-Grade Part</sub>  | S<br>R | Ambient temperature under bias                                                | _                                                  | -40                        | 125                                |           |

| T <sub>J M</sub> -Grade Part | S<br>R | Junction temperature under bias                                               | —                                                  | -40                        | 150                                |           |

| Table 11. Recommended of | perating conditions | (5 0 V) | (continued) |

|--------------------------|---------------------|---------|-------------|

|                          | peraling conditions | (J.U V) | (continueu) |

1. 100 nF EMI capacitance need to be provided between each VDD/VSS\_HV pair.

Full device operation is guaranteed by design from 3.0 V–5.5 V. OSC functionality is guaranteed from the entire range 3.0V–5.5 V, the parametrics measured are at 3.0V and 5.5V (extreme voltage ranges to cover the range of operation). The parametrics might have some variation in the intermediate voltage range, but there is no impact to functionality.

100 nF EMI capacitance needs to be provided between each VDD\_LV/VSS\_LV supply pair. 10 µF bulk capacitance needs to be provided as CREG on each VDD\_LV pin.

4. This voltage is internally generated by the device and no external voltage should be supplied.

5. 100 nF capacitance needs to be provided between  $V_{DD\_HV\_(ADC0/ADC1)}/V_{SS\_HV\_(ADC0/ADC1)}$  pair.

6. Both the relative and the fixed conditions must be met. For instance: If  $V_{DD\_HV\_A}$  is 5.9 V,  $V_{DD\_HV\_ADC0}$  maximum value is 6.0 V then, despite the relative condition, the max value is  $V_{DD\_HV\_A} + 0.3 = 6.2$  V.

PA3, PA7, PA10, PA11 and PE12 ADC\_1 channels are coming from V<sub>DD\_HV\_B</sub> domain hence VDD\_HV\_ADC1 should be within ±100 mV of V<sub>DD\_HV\_B</sub> when these channels are used for ADC\_1.

The internal voltage regulator requires external bulk capacitance ( $C_{REGn}$ ) to be connected to the device to provide a stable low voltage digital supply to the device. Also required for stability is the  $C_{DEC2}$  capacitor at ballast collector. This is needed to minimize sharp injection current when ballast is turning ON. Apart from the bulk capacitance, user should connect EMI/decoupling cap ( $C_{REGP}$ ) at each  $V_{DD_LV}/V_{SS_LV}$  pin pair.

#### 3.8.1.1 Recommendations

- The external NPN driver must be BCP68 type.

- V<sub>DD\_LV</sub> should be implemented as a power plane from the emitter of the ballast transistor.

- 10 μF capacitors should be connected to the 4 pins closest to the outside of the package and should be evenly distributed around the package. For BGA packages, the balls should be used are D8, H14, R9, J3–one cap on each side of package.

- There should be a track direct from the capacitor to this pin (pin also connects to  $V_{DD LV}$  plane). The tracks ESR should be less than 100 m $\Omega$ .

- The remaining  $V_{DD_{LV}}$  pins (exact number will vary with package) should be decoupled with 0.1  $\mu$ F caps, connected to the pin as per 10  $\mu$ F.

(see Section 3.4: Recommended operating conditions).

## 3.8.2 V<sub>DD BV</sub> options

Option 1: V<sub>DD\_BV</sub> shared with V<sub>DD\_HV\_A</sub>

$V_{DD\_BV}$  must be star routed from  $V_{DD\_HV\_A}$  from the common source. This is to eliminate ballast noise injection on the MCU.

• Option 2: V<sub>DD BV</sub> independent of the MCU supply

$V_{DD_BV}$  > 2.6 V for correct functionality. The device is not monitoring this supply hence the external component must meet the 2.6 V criteria through external monitoring if required.

| Symbol C          |        | c            | Parameter                                                                     | Conditions <sup>(1)</sup>                             |      | Value <sup>(2)</sup> |                         | Unit |

|-------------------|--------|--------------|-------------------------------------------------------------------------------|-------------------------------------------------------|------|----------------------|-------------------------|------|

|                   |        | r ai ainetei | Conditions                                                                    | Min                                                   | Тур  | Мах                  | - Unit<br>μF<br>W<br>nF |      |

| C <sub>REGn</sub> | S<br>R | _            | External ballast stability capacitance                                        | _                                                     | 40   | _                    | 60                      | μF   |

| R <sub>REG</sub>  | S<br>R |              | Stability capacitor equivalent serial resistance                              | _                                                     |      |                      | 0.2                     | W    |

| C <sub>REGP</sub> | S<br>R |              | Decoupling capacitance (Close to the pin)                                     | V <sub>DD_HV_A/HV_B</sub> /V <sub>SS_HV</sub><br>pair |      | 100                  | _                       | nF   |

|                   |        |              |                                                                               | V <sub>DD_LV</sub> /V <sub>SS_LV</sub> pair           |      | 100                  | —                       | nF   |

| C <sub>DEC2</sub> | S<br>R |              | Stability capacitance regulator<br>supply (Close to the ballast<br>collector) | V <sub>DD_BV</sub> /V <sub>SS_HV</sub>                | 10   |                      | 40                      | μF   |

| V <sub>MREG</sub> | C<br>C | Ρ            | Main regulator output voltage                                                 | After trimming<br>T <sub>A</sub> = 25 °C              | 1.20 | 1.28                 | 1.32                    | V    |

#### Table 23. Voltage regulator electrical characteristics

| Cumhal                   |        | ~ | Devenuetor                                                                              | Conditions <sup>(1)</sup>                             |      | Value <sup>(2)</sup> |            | 11   |

|--------------------------|--------|---|-----------------------------------------------------------------------------------------|-------------------------------------------------------|------|----------------------|------------|------|

| Symbol C                 |        | С | Parameter                                                                               | Conditions                                            | Min  | Тур                  | Max        | Unit |

| I <sub>MREG</sub>        | S<br>R |   | Main regulator current provided to $V_{DD_LV}$ domain                                   | —                                                     | _    | _                    | 350        | mA   |

| I <sub>MREGINT</sub> C D |        | П | Main regulator module current                                                           | I <sub>MREG</sub> = 200 mA                            | _    |                      | 2          | mA   |

|                          |        |   | consumption                                                                             | I <sub>MREG</sub> = 0 mA                              | _    |                      | 1          |      |

| V <sub>LPREG</sub>       | C<br>C | Ρ | Low power regulator output voltage                                                      | After trimming<br>T <sub>A</sub> = 25 °C              | 1.17 | 1.27                 | 1.32       | V    |

| I <sub>LPREG</sub>       | S<br>R |   | Low power regulator current provided to V <sub>DD_LV</sub> domain                       | _                                                     | _    | _                    | 50         | mA   |

| L                        | С      | D | Low power regulator module                                                              | I <sub>LPREG</sub> = 15 mA;<br>T <sub>A</sub> = 55 °C | _    | _                    | 600        |      |

| I <sub>LPREGINT</sub>    | С      | — | current consumption                                                                     | I <sub>LPREG</sub> = 0 mA;<br>T <sub>A</sub> = 55 °C  | _    | 20                   | _          | μA   |

| I <sub>VREGREF</sub>     | с<br>с | D | Main LVDs and reference current consumption (low power and main regulator switched off) | T <sub>A</sub> = 55 °C                                | _    | 2                    | _          | μΑ   |

| I <sub>VREDLVD12</sub>   | C<br>C | D | Main LVD current consumption (switch-off during standby)                                | T <sub>A</sub> = 55 °C                                | _    | 1                    | _          | μA   |

| I <sub>DD_HV_A</sub>     | C<br>C | D | In-rush current on V <sub>DD_BV</sub> during power-up                                   | _                                                     | _    | _                    | 600<br>(3) | mA   |

Table 23. Voltage regulator electrical characteristics (continued)

1.  $V_{DD_HV_A} = 3.3 \text{ V} \pm 10 \% / 5.0 \text{ V} \pm 10 \%$ ,  $T_A = -40$  to 125 °C, unless otherwise specified.

2. All values need to be confirmed during device validation.

3. Inrush current is seen more like steps of 600 mA peak. The startup of the regulator happens in steps of 50 mV in ~25 steps to reach ~1.2 V  $V_{DD_LV}$ . Each step peak current is within 600 mA

## 3.8.3 Voltage monitor electrical characteristics

The device implements a Power-on Reset module to ensure correct power-up initialization, as well as four low voltage detectors to monitor the  $V_{DD_HV_A}$  and the  $V_{DD_LV}$  voltage while device is supplied:

- POR monitors V<sub>DD\_HV\_A</sub> during the power-up phase to ensure device is maintained in a safe reset state

- LVDHV3 monitors V<sub>DD\_HV\_A</sub> to ensure device is reset below minimum functional supply

- LVDHV5 monitors  $V_{DD_HV_A}$  when application uses device in the 5.0 V±10 % range

- LVDLVCOR monitors power domain No. 1 (PD1)

- LVDLVBKP monitors power domain No. 0 (PD0). VDD\_LV is same as PD0 supply.

Note: When enabled, PD2 (RAM retention) is monitored through LVD\_DIGBKP.

- 9. Subject to change, Configuration: 1 × e200z4d + 4 kbit/s Cache, 1 × e200z0h (1/2 system frequency), CSE, 1 × eDMA (10 ch.), 6 × FlexCAN (4 × 500 kbit/s, 2 × 125 kbit/s), 4 × LINFlexD (20 kbit/s), 6 × DSPI (2 × 2 Mbit/s, 3 × 4 Mbit/s, 1 × 10 Mbit/s), 16 × Timed I/O, 16 × ADC Input, 1 × FlexRay (2 ch., 10 Mbit/s), 1 × FEC (100 Mbit/s), 1 × RTC, 4 PIT channels, 1 × SWT, 1 × STM. For lower pin count packages reduce the amount of timed I/O's and ADC channels. RUN current measured with typical application with accesses on both code flash and RAM.

- 10. This value is obtained from limited sample set.

- 11. Data Flash Power Down. Code Flash in Low Power. SIRC 128 kHz and FIRC 16 MHz ON. 16 MHz XTAL clock. FlexCAN: instances: 0, 1, 2 ON (clocked but no reception or transmission), instances: 4, 5, 6 clocks gated. LINFlex: instances: 0, 1, 2 ON (clocked but no reception or transmission), instance: 3-9 clocks gated. eMIOS: instance: 0 ON (16 channels on PA[0]-PA[11] and PC[12]-PC[15]) with PWM 20 kHz, instance: 1 clock gated. DSPI: instance: 0 (clocked but no communication, instance: 1-7 clocks gated). RTC/API ON. PIT ON. STM ON. ADC ON but no conversion except 2 analog watchdogs.

- 12. Only for the "P" classification: No clock, FIRC 16 MHz OFF, SIRC128 kHz ON, PLL OFF, HPvreg OFF, LPVreg ON. All possible peripherals off and clock gated. Flash in power down mode.

- Only for the "P" classification: LPreg ON, HPVreg OFF, 96 KB RAM ON, device configured for minimum consumption, all

possible modules switched-off. Measurement condition assumes T<sub>i</sub> = Ta.

- LPreg ON, HPVreg OFF, 64 KB RAM ON, device configured for minimum consumption, all possible modules switched-off. Measurement condition assumes T<sub>i</sub> = Ta.

- LPreg ON, HPVreg OFF, 8 KB RAM ON, device configured for minimum consumption, all possible modules switched OFF. Measurement condition assumes T<sub>i</sub> = Ta.

# 3.10 Flash memory electrical characteristics

#### 3.10.1 Program/Erase characteristics

Table 26 shows the code flash memory program and erase characteristics.

|                                  |                    |   |                                                   |                    | Valu                          | ue                 |      |    |

|----------------------------------|--------------------|---|---------------------------------------------------|--------------------|-------------------------------|--------------------|------|----|

| Symbol                           | Symbol C Parameter |   | Min                                               | Typ <sup>(1)</sup> | Initial<br>max <sup>(2)</sup> | Max <sup>(3)</sup> | Unit |    |

| T <sub>dwprogram</sub>           |                    |   | Double word (64 bits) program time <sup>(4)</sup> | _                  | 18                            | 50                 | 500  | μs |

| T <sub>16Kpperase</sub>          |                    | с | 16 KB block pre-program and erase time            | _                  | 200                           | 500                | 5000 | ms |

| T <sub>32Kpperase</sub>          |                    | C | 32 KB block pre-program and erase time            | —                  | 300                           | 600                | 5000 | ms |

| T <sub>128Kpperase</sub>         | с                  |   | 128 KB block pre-program and erase time           | _                  | 600                           | 1300               | 5000 | ms |

| T <sub>eslat</sub>               | С                  | D | Erase Suspend Latency                             | _                  |                               | 30                 | 30   | μs |

| t <sub>ESRT</sub> <sup>(5)</sup> |                    | С | Erase Suspend Request Rate                        | 20                 | _                             |                    | _    | ms |

| t <sub>PABT</sub>                |                    | D | Program Abort Latency                             | _                  | _                             | 10                 | 10   | μs |

| t <sub>EAPT</sub>                |                    | D | Erase Abort Latency                               | _                  | _                             | 30                 | 30   | μs |

#### Table 26. Code flash memory—Program and erase specifications

1. Typical program and erase times assume nominal supply values and operation at 25 °C. All times are subject to change pending device characterization.

2. Initial factory condition: < 100 program/erase cycles, 25 °C, typical supply voltage.

3. The maximum program and erase times occur after the specified number of program/erase cycles. These maximum values are characterized but not guaranteed.

4. Actual hardware programming times. This does not include software overhead.

5. It is Time between erase suspend resume and the next erase suspend request.

Table 27 shows the data flash memory program and erase characteristics.

## 3.11.2 Electromagnetic interference (EMI)

The product is monitored in terms of emission based on a typical application. This emission test conforms to the IEC61967-1 standard, which specifies the general conditions for EMI measurements.

| Symb               | Symbol C Para |   | Parameter              | Condition                                                                                   | •                                   |       | Value |                   | Unit     |  |

|--------------------|---------------|---|------------------------|---------------------------------------------------------------------------------------------|-------------------------------------|-------|-------|-------------------|----------|--|

| Synib              | UI            | C | Farameter              | Conditions                                                                                  |                                     | Min   | Тур   | Max               | Unit     |  |

| _                  | S<br>R        | _ | Scan range             | —                                                                                           |                                     | 0.150 |       | 1000              | MHz      |  |

| f <sub>CPU</sub>   | S<br>R        | _ | Operating<br>frequency | —                                                                                           |                                     | _     | 120   | _                 | MHz      |  |

| V <sub>DD_LV</sub> | S<br>R        | _ | LV operating voltages  | _                                                                                           |                                     | _     | 1.28  |                   | V        |  |

| 6                  | С             | т | Peak level             | V <sub>DD</sub> = 5 V, T <sub>A</sub> = 25 °C,<br>LQFP176 package<br>Test conforming to IEC | No PLL<br>frequency<br>modulation   | _     | _     | 18                | dBµV     |  |

| S <sub>EMI</sub> C | С             | 1 | ר כמג ופעפו            | 61967-2,<br>f <sub>OSC</sub> = 40 MHz/f <sub>CPU</sub> = 120<br>MHz                         | ± 2% PLL<br>frequency<br>modulation | _     | _     | 14 <sup>(3)</sup> | MHz<br>V |  |

| Table 32. EMI radiated emission measurement | 32. EMI radiated emission measureme | nt <sup>(1)(2</sup> | 2) |

|---------------------------------------------|-------------------------------------|---------------------|----|

|---------------------------------------------|-------------------------------------|---------------------|----|

1. EMI testing and I/O port waveforms per IEC 61967-1, -2, -4.

2. For information on conducted emission and susceptibility measurement (norm IEC 61967-4), please contact your local marketing representative.

3. All values need to be confirmed during device validation.

## 3.11.3 Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity.

#### 3.11.3.1 Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pin). This test conforms to the AEC-Q100-002/-003/-011 standard. For more details, refer to the application note *Electrostatic Discharge Sensitivity Measurement* (AN1181).

| Symbol                | Ratings Conditions                                    |                                                      | Class | Max value <sup>(3)</sup> | Unit |  |  |  |  |  |

|-----------------------|-------------------------------------------------------|------------------------------------------------------|-------|--------------------------|------|--|--|--|--|--|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage<br>(Human Body Model) | T <sub>A</sub> = 25 °C<br>conforming to AEC-Q100-002 | H1C   | 2000                     |      |  |  |  |  |  |

| V <sub>ESD(MM)</sub>  | Electrostatic discharge voltage (Machine Model)       | T <sub>A</sub> = 25 °C<br>conforming to AEC-Q100-003 | M2    | 200                      | V    |  |  |  |  |  |

|                       | Electrostatic discharge voltage                       | T <sub>A</sub> = 25 °C                               |       | 500                      |      |  |  |  |  |  |

| V <sub>ESD(CDM)</sub> | (Charged Device Model)                                | conforming to AEC-Q100-011                           | C3A   | 750<br>(corners)         |      |  |  |  |  |  |

| Table 33. ESI | ) absolute | maximum | $ratings^{(1)(2)}$ |

|---------------|------------|---------|--------------------|

|---------------|------------|---------|--------------------|

| Symbol          | 1                                         | с | Paramotor                                     | Conditions <sup>(1)</sup> |                              | Value | e <sup>(2)</sup>           | Unit |

|-----------------|-------------------------------------------|---|-----------------------------------------------|---------------------------|------------------------------|-------|----------------------------|------|

| Symbol          | bol C Parameter Conditions <sup>(1)</sup> |   | Min                                           | Тур                       | Мах                          | Onit  |                            |      |

| V <sub>IH</sub> | SR                                        | Ρ | Input high level<br>CMOS<br>(Schmitt Trigger) | Oscillator bypass mode    | 0.65V <sub>DD_</sub><br>HV_A | _     | V <sub>DD_HV_A</sub> + 0.4 | V    |

| V <sub>IL</sub> | SR                                        | Ρ | Input low level<br>CMOS<br>(Schmitt Trigger)  | Oscillator bypass mode    | -0.3                         | _     | 0.35V <sub>DD_HV_A</sub>   | V    |

#### Table 36. Fast external crystal oscillator (4 to 40 MHz) electrical characteristics (continued)

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified.

2. All values need to be confirmed during device validation.

3. Based on ATE Cz

4. Stated values take into account only analog module consumption but not the digital contributor (clock tree and enabled peripherals).

# 3.13 Slow external crystal oscillator (32 kHz) electrical characteristics

The device provides a low power oscillator/resonator driver.

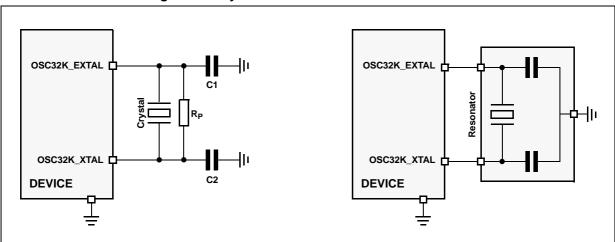

#### Figure 12. Crystal oscillator and resonator connection scheme

Note:

OSC32K\_XTAL/OSC32K\_EXTAL must not be directly used to drive external circuits.

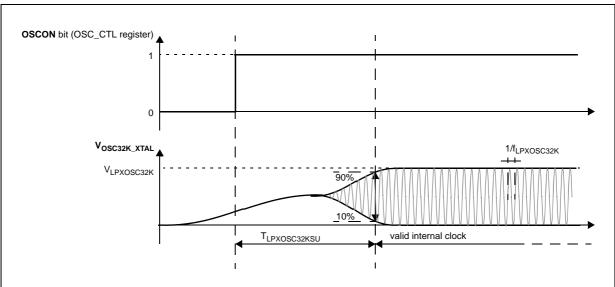

Figure 14. Slow external crystal oscillator (32 kHz) electrical characteristics

| Symbol                           |        | с | Perometer                                      | Conditions <sup>(1)</sup>         |                   | Value <sup>(2)</sup> |                   | Unit |

|----------------------------------|--------|---|------------------------------------------------|-----------------------------------|-------------------|----------------------|-------------------|------|

|                                  |        | C | Parameter                                      | Conditions                        | Min               | Тур                  | Max               | Unit |

| f <sub>sxosc</sub>               | S<br>R |   | Slow external crystal oscillator<br>frequency  | -                                 | 32                | 32.76<br>8           | 40                | kHz  |

|                                  | С      |   | Slow external crystal oscillator               | $V_{DD} = 3.3 V \pm 10\%,$        | 13 <sup>(3)</sup> | —                    | 33 <sup>(3)</sup> |      |

| <sup>g</sup> <sub>mSXOSC</sub> C |        |   | transconductance                               | $V_{DD} = 5.0 \text{ V} \pm 10\%$ | 15 <sup>(3)</sup> | —                    | 35 <sup>(3)</sup> | μΑ/V |

| V <sub>SXOSC</sub>               | C<br>C | т | Oscillation amplitude                          | _                                 | 1.2               | 1.4                  | 1.7               | V    |

| I <sub>SXOSCBIAS</sub>           | C<br>C | т | Oscillation bias current                       | _                                 | 1.2               | _                    | 4.4               | μA   |

| I <sub>sxosc</sub>               | C<br>C | т | Slow external crystal oscillator consumption   | _                                 | _                 | _                    | 7                 | μA   |

| T <sub>SXOSCSU</sub>             | C<br>C | т | Slow external crystal oscillator start-up time | _                                 |                   |                      | 2 <sup>(4)</sup>  | S    |

Table 38. Slow external crystal oscillator (32 kHz) electrical characteristics

1. V\_{DD} = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified.

2. All values need to be confirmed during device validation.

3. Based on ATE CZ

4. Start-up time has been measured with EPSON TOYOCOM MC306 crystal. Variation may be seen with other crystal.

# 3.14 **FMPLL** electrical characteristics

The device provides a frequency-modulated phase-locked loop (FMPLL) module to generate a fast system clock from the main oscillator driver.

| Symbol              |        | с | Parameter                                       | Conditions <sup>(1)</sup>                                                              |    | Val | ue <sup>(2)</sup>       | Unit |

|---------------------|--------|---|-------------------------------------------------|----------------------------------------------------------------------------------------|----|-----|-------------------------|------|

| Symbo               | וכ     | J | Falameter                                       | Conditions                                                                             |    | Тур | Мах                     | Unit |

| f <sub>PLLIN</sub>  | S<br>R | _ | FMPLL reference clock <sup>(3)</sup>            | _                                                                                      | 4  | _   | 64                      | MHz  |

| $\Delta_{PLLIN}$    | S<br>R | _ | FMPLL reference clock duty cycle <sup>(3)</sup> | _                                                                                      | 40 | _   | 60                      | %    |

| f <sub>PLLOUT</sub> | C<br>C | Ρ | FMPLL output clock<br>frequency                 | _                                                                                      | 16 | _   | 120                     | MHz  |

| f <sub>CPU</sub>    | S<br>R | _ | System clock frequency                          | _                                                                                      | _  | _   | 120 + 2% <sup>(4)</sup> | MHz  |

| f <sub>FREE</sub>   | C<br>C | Ρ | Free-running frequency                          | _                                                                                      | 20 | _   | 150                     | MHz  |

| t <sub>LOCK</sub>   | C<br>C | Ρ | FMPLL lock time                                 | Stable oscillator (f <sub>PLLIN</sub> = 16 MHz)                                        |    | 40  | 100                     | μs   |

| $\Delta t_{LTJIT}$  | C<br>C | _ | FMPLL long term jitter                          | f <sub>PLLIN</sub> = 40 MHz (resonator),<br>f <sub>PLLCLK</sub> @ 120 MHz, 4000 cycles | _  | _   | 6<br>(for < 1ppm)       | ns   |

| I <sub>PLL</sub>    | C<br>C | С | FMPLL consumption                               | T <sub>A</sub> = 25 °C                                                                 | _  | _   | 3                       | mA   |

| Table 39. FMPLL | electrical | characteristics |

|-----------------|------------|-----------------|

|-----------------|------------|-----------------|

1.  $V_{DD}$  = 3.3 V  $\pm$  10% / 5.0 V  $\pm$  10%,  $T_A$  = –40 to 125 °C, unless otherwise specified.

2. All values need to be confirmed during device validation.

PLLIN clock retrieved directly from 4-40 MHz XOSC or 16 MIRC. Input characteristics are granted when oscillator is used in functional mode. When bypass mode is used, oscillator input clock should verify f<sub>PLLIN</sub> and Δ<sub>PLLIN</sub>.

4.  $f_{CPU}$  120 + 2% MHz can be achieved at 125 °C.

# 3.15 Fast internal RC oscillator (16 MHz) electrical characteristics

The device provides a 16 MHz main internal RC oscillator. This is used as the default clock at the power-up of the device and can also be used as input to PLL.

| Table 40. Fast internal RC oscillator | (16 MHz) electrical characteristics |

|---------------------------------------|-------------------------------------|

|                                       |                                     |

| Symbol            |        | С | Parameter                                  | Conditions <sup>(1)</sup>       | Value <sup>(2)</sup> |     |     | Unit |

|-------------------|--------|---|--------------------------------------------|---------------------------------|----------------------|-----|-----|------|

|                   |        |   |                                            | Conditions                      | Min                  | Тур | Max | Unit |

| f <sub>FIRC</sub> | C<br>C | Ρ | Fast internal RC oscillator high frequency | $T_A = 25 \text{ °C}$ , trimmed | _                    | 16  | _   | MHz  |

|                   | S<br>R |   |                                            | _                               | 12                   |     | 20  |      |

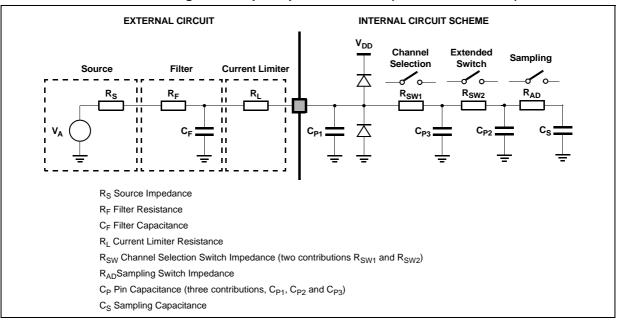

Figure 17. Input equivalent circuit (extended channels)

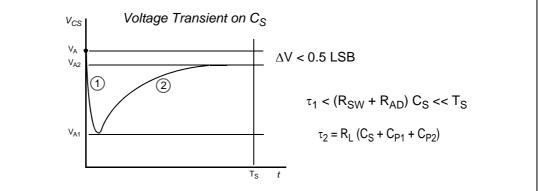

A second aspect involving the capacitance network shall be considered. Assuming the three capacitances  $C_F$ ,  $C_{P1}$  and  $C_{P2}$  initially charged at the source voltage  $V_A$  (refer to the equivalent circuit reported in *Figure 16*): when the sampling phase is started (A/D switch close), a charge sharing phenomena is installed.

In particular two different transient periods can be distinguished:

• A first and quick charge transfer from the internal capacitance  $C_{P1}$  and  $C_{P2}$  to the sampling capacitance  $C_S$  occurs ( $C_S$  is supposed initially completely discharged): considering a worst case (since the time constant in reality would be faster) in which  $C_{P2}$  is reported in parallel to  $C_{P1}$  (call  $C_P = C_{P1} + C_{P2}$ ), the two capacitances  $C_P$  and  $C_S$  are in series, and the time constant is

#### **Equation 5**

$$\tau_1 = (\mathbf{R}_{SW} + \mathbf{R}_{AD}) \bullet \frac{\mathbf{C}_{\mathbf{P}} \bullet \mathbf{C}_{S}}{\mathbf{C}_{\mathbf{P}} + \mathbf{C}_{S}}$$

| _           |              | Table 57. Revision history (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date        | Revision     | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 04-Mar-2013 | 5<br>(cont.) | <ul> <li>Updated the min, max and typical values of V<sub>LVDLVCORL</sub> and V<sub>LVDLVBKPL</sub> in <i>Table 24: Low voltage monitor electrical characteristics</i></li> <li>Updated values of gmFXOSC in <i>Table 36: Fast external crystal oscillator (4 to 40 MHz) electrical characteristics</i></li> <li>Updated values of gmSXOSC in <i>Table 38: Slow external crystal oscillator (32 kHz) electrical characteristics</i></li> <li>Updated the footnote 5 for T<sub>ADC0_C</sub> in <i>Table 43: ADC conversion characteristics (10-bit ADC_0)</i></li> <li>Updated the footnotes of <i>Table 25: Low voltage power domain electrical characteristics</i></li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 17-Sep-2013 | 6            | - Updated Disclaimer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 28-Nov-2014 | 7            | <ul> <li>Removed occurrences of 208BGA from Table 2: SPC564Bxx and SPC56ECxx family comparison.</li> <li>Added PM[3] and PM[4] in the figure note 1 of <i>Figure 4</i>: 256-pin BGA configuration.</li> <li>Added a table note in <i>Table 20: I/O supplies</i>.</li> <li>Updated <i>Figure 8: Voltage regulator capacitance connection</i> and added a note in this figure.</li> <li>Removed before trimming value for V<sub>MREG</sub> updated after trimming min value of V<sub>LPREG</sub> from 1.24 V to 1.20 V, updated after trimming min value of V<sub>LPREG</sub> from 1.25 V to 1.17 V, updated after trimming typical value of V<sub>LPREG</sub> from 1.25 V to 1.27 V and updated after trimming max value of V<sub>LPREG</sub> from 1.25 V to 1.32 V in <i>Table 23: Voltage regulator electrical characteristics</i>.</li> <li>Changed min value of V<sub>LVDLVCORL</sub> and V<sub>LVDLVBKPL</sub> from 1.12 V to 1.08 V, and removed typical value of V<sub>LVDLVCORL</sub> and V<sub>LVDLVBKPL</sub> in <i>Table 24: Low voltage monitor electrical characteristics</i></li> <li>Updated max values at 120 MHz for IDDRUN from 200 mA to 208 mA and from 270 mA to 280 mA; updated max value at T<sub>A</sub> = 125 °C for IDDHALT from 80 mA to 100 mA; updated max value at T<sub>A</sub> = 25 °C for IDDSTDP from 1.2 mA to 5 mA and at T<sub>A</sub> = 125 °C from 1100 µA to 2000 µA; updated max value at T<sub>A</sub> = 25 °C for IDDSTDP1 fom 1.2 mA to 3 mA and at T<sub>A</sub> = 125 °C from 100 µA to 2400 µA; updated max value at T<sub>A</sub> = 25 °C for IDDSTDP1 fom 1.2 MA to 3 mA and at T<sub>A</sub> = 125 °C from 100 µA to 2400 µA; updated max value at T<sub>A</sub> = 25 °C for IDDSTDP1 fom 1.2 MA to 3 mA and at T<sub>A</sub> = 125 °C from 65 µA to 96 µA and at T<sub>A</sub> = 125 °C from 650 µA to 1100 µA; updated max value at T<sub>A</sub> = 25 °C for IDDSTDP1 fom 1.2 MA to 3 mA and at T<sub>A</sub> = 125 °C from 65 µA to 85 µA and at T<sub>A</sub> = 125 °C from 650 µA to 1100 µA; updated max value at T<sub>A</sub> = 25 °C for IDDSTDP1 form 1.2 MA to 5 mA/X and from 100 µA to 2000 µA; updated max value at T<sub>A</sub> = 25 °C for IDDSTDP1 form 1.2 MA to 500 µA to 1100 µA; updated the formula in Eq. 11 in Section 3.17.1.1: Input impedance and ADC accuracy.</li> <li>Updated legend in <i>Figu</i></li></ul> |

#### Table 57. Revision history (continued)

| Date        | Revision     | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28-Nov-2014 | 7<br>(cont.) | <ul> <li>Added Category column in <i>Table 44: Conversion characteristics (12-bit ADC_1)</i>.</li> <li>Added the IDD_HV_ADC0 values in <i>Table 49: On-chip peripherals current consumption</i>.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16-Jun-2015 | 8            | Updated Figure 37: LQFP176 package mechanical drawing and Figure 40:<br>Ordering information scheme.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11-Mar-2016 | 9            | <ul> <li>Added package silhouette on the cover page</li> <li>Removed <i>Figure 4: LBGA208 configuration</i></li> <li>Removed LBGA208 column in <i>Table 4: System pin descriptions</i> and in <i>Table 5: Functional port pin descriptions</i></li> <li><i>Table 12: LQFP thermal characteristics</i>: for "R<sub>θJA</sub>" row, changed Max value relating to conditions "Single-layer board—1s" and "Four-layer board—2s2p" from "TBD" to "43" and "33.9", respectively</li> <li>Removed <i>Table 13: LBGA208 thermal characteristics</i>: for "R<sub>θJA</sub>" row, changed Max value relating to conditions "Single-layer board—1s" and "Four-layer board—2s2p" from "TBD" to "44.3" and "31.9", respectively</li> <li>Removed <i>Table 13: LBGA256 thermal characteristics</i>: for "R<sub>θJA</sub>" row, changed Max value relating to conditions "Single-layer board—1s" and "Four-layer board—2s2p" from "TBD" to "44.3" and "31", respectively</li> <li>Removed LBGA208 row in <i>Table 20: I/O supplies</i></li> <li>Removed <i>Section 4.2.3: LBGA208 package mechanical drawing</i></li> <li>In <i>Table 25: Low voltage power domain electrical characteristics</i>, updated notes "Only for the "P" classification: LPreg ON, HPVreg OFF, 96 KB RAM ON, device configured for", and "LPreg ON, HPVreg OFF, 8 KB RAM ON, device configured for"</li> <li>In <i>Table 49: On-chip peripherals current consumption</i>, changed IDD_HV_ADC1 value from "300 × f<sub>periph</sub>" to "300"</li> </ul> |

Table 57. Revision history (continued)