Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 37                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 6K x 8                                                                |

| RAM Size                   | 20K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l073cbt6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of figures

| Figure 1.  | STM32L073xx block diagram                                                                    | . 12 |

|------------|----------------------------------------------------------------------------------------------|------|

| Figure 2.  | Clock tree                                                                                   | . 24 |

| Figure 3.  | STM32L073xx LQFP100 pinout - 14 x 14 mm                                                      | . 37 |

| Figure 4.  | STM32L073xx UFBGA100 ballout - 7x 7 mm                                                       | . 38 |

| Figure 5.  | STM32L073xx LQFP64 pinout - 10 x 10 mm                                                       | . 39 |

| Figure 6.  | STM32L073xx TFBGA64 ballout - 5x 5 mm                                                        | . 40 |

| Figure 7.  | STM32L073xx LQFP48 pinout - 7 x 7 mm                                                         | . 41 |

| Figure 8.  | Memory map                                                                                   | . 56 |

| Figure 9.  | Pin loading conditions.                                                                      | . 57 |

| Figure 10. | Pin input voltage                                                                            | . 57 |

| Figure 11. | Power supply scheme                                                                          | . 58 |

| Figure 12. | Optional LCD power supply scheme                                                             | . 59 |

| Figure 13. | Current consumption measurement scheme                                                       |      |

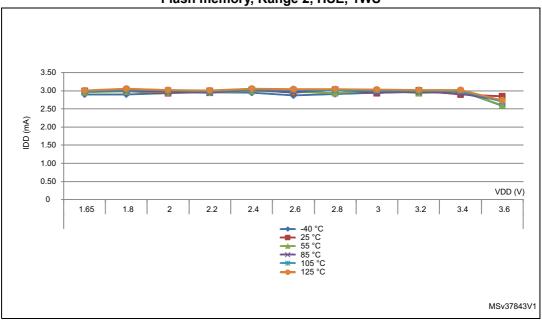

| Figure 14. | IDD vs VDD, at TA= 25/55/85/105 °C, Run mode, code running from                              |      |

| 0          | Flash memory, Range 2, HSE, 1WS                                                              | . 68 |

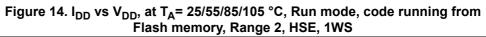

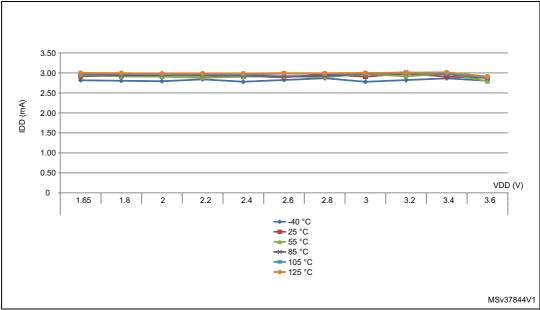

| Figure 15. | IDD vs VDD, at TA= 25/55/85/105 °C, Run mode, code running from                              |      |

| 0          | Flash memory, Range 2, HSI16, 1WS                                                            | . 68 |

| Figure 16. | IDD vs VDD, at TA= 25 °C, Low-power run mode, code running                                   |      |

| 0          | from RAM, Range 3, MSI (Range 0) at 64 KHz, 0 WS                                             | . 72 |

| Figure 17. | IDD vs VDD, at TA= 25/55/ 85/105/125 °C, Stop mode with RTC enabled                          |      |

| 0          | and running on LSE Low drive                                                                 | . 73 |

| Figure 18. | IDD vs VDD, at TA= 25/55/85/105/125 °C, Stop mode with RTC disabled,                         |      |

| 0          | all clocks off                                                                               | . 74 |

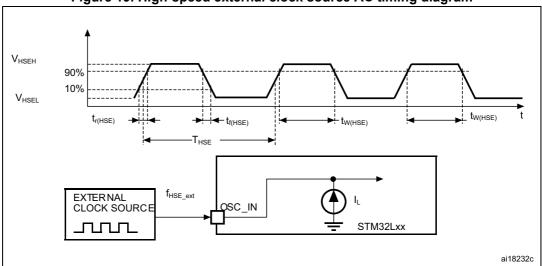

| Figure 19. | High-speed external clock source AC timing diagram                                           |      |

| Figure 20. | Low-speed external clock source AC timing diagram                                            |      |

| Figure 21. | HSE oscillator circuit diagram                                                               |      |

| Figure 22. | Typical application with a 32.768 kHz crystal                                                |      |

| Figure 23. | HSI16 minimum and maximum value versus temperature                                           |      |

| Figure 24. | VIH/VIL versus VDD (CMOS I/Os)                                                               |      |

| Figure 25. | VIH/VIL versus VDD (TTL I/Os)                                                                |      |

| Figure 26. | I/O AC characteristics definition                                                            |      |

| Figure 27. | Recommended NRST pin protection                                                              |      |

| Figure 28. | ADC accuracy characteristics                                                                 |      |

| Figure 29. | Typical connection diagram using the ADC                                                     |      |

| Figure 30. | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> ) |      |

| Figure 31. | Power supply and reference decoupling ( $V_{REF+}$ connected to $V_{DDA}$ )                  |      |

| Figure 32. | 12-bit buffered/non-buffered DAC.                                                            |      |

| Figure 33. | SPI timing diagram - slave mode and CPHA = 0                                                 | 112  |

| Figure 34. | SPI timing diagram - slave mode and CPHA = $1^{(1)}$                                         | 113  |

| Figure 35. | SPI timing diagram - master mode <sup>(1)</sup>                                              | 113  |

| Figure 36. | I <sup>2</sup> S slave timing diagram (Philips protocol) <sup>(1)</sup>                      | 115  |

| Figure 37. | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup>                     | 115  |

| Figure 38. | USB timings: definition of data signal rise and fall time                                    |      |

| Figure 39. | LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline                          | 119  |

| Figure 40. | LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat                                          | . •  |

|            | recommended footprint.                                                                       | 121  |

| Figure 41. | LQFP100 marking example (package top view)                                                   | 121  |

| Figure 42. | UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball                           | _ ·  |

|            |                                                                                              |      |

# 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of core and features, from 8-bit proprietary core up to ARM<sup>®</sup> Cortex<sup>®</sup>-M4, including ARM<sup>®</sup> Cortex<sup>®</sup>-M3 and ARM<sup>®</sup> Cortex<sup>®</sup>-M0+. The STM32Lx series are the best choice to answer your needs in terms of ultra-low-power features. The STM32 ultra-low-power series are the best solution for applications such as gaz/water meter, keyboard/mouse or fitness and healthcare application. Several built-in features like LCD drivers, dual-bank memory, low-power run mode, operational amplifiers, 128-bit AES, DAC, crystal-less USB and many other definitely help you building a highly cost optimized application by reducing BOM cost. STMicroelectronics, as a reliable and long-term manufacturer, ensures as much as possible pin-to-pin compatibility between all STM8Lx and STM32Lx on one hand, and between all STM32Lx and STM32Fx on the other hand. Thanks to this unprecedented scalability, your legacy application can be upgraded to respond to the latest market feature and efficiency requirements.

|                                                | Functionalities depending on the operating power supply range                                                   |                                |                            |                           |  |  |  |  |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------|---------------------------|--|--|--|--|

| Operating power<br>supply range                | DAC and ADC<br>operation Dynamic<br>voltage scaling<br>range                                                    |                                | I/O operation              | USB                       |  |  |  |  |

| V <sub>DD</sub> = 1.65 to 1.71 V               | 35 to 1.71 V ADC only,<br>conversion time<br>up to 570 ksps Range 2 or<br>range 3 Degraded speed<br>performance |                                | ÷ .                        | Not functional            |  |  |  |  |

| V <sub>DD</sub> = 1.71 to 1.8 V <sup>(1)</sup> | ADC only,<br>conversion time<br>up to 1.14 Msps                                                                 | Range 1, range 2<br>or range 3 | Degraded speed performance | Functional <sup>(2)</sup> |  |  |  |  |

| $V_{DD}$ = 1.8 to 2.0 V <sup>(1)</sup>         | Conversion time<br>up to 1.14 Msps                                                                              | Range1, range 2<br>or range 3  | Degraded speed performance | Functional <sup>(2)</sup> |  |  |  |  |

| V <sub>DD</sub> = 2.0 to 2.4 V                 | Conversion time<br>up to<br>1.14 Msps                                                                           | Range 1, range 2<br>or range 3 | Full speed operation       | Functional <sup>(2)</sup> |  |  |  |  |

| V <sub>DD</sub> = 2.4 to 3.6 V                 | Conversion time<br>up to<br>1.14 Msps                                                                           | Range 1, range 2<br>or range 3 | Full speed operation       | Functional <sup>(2)</sup> |  |  |  |  |

CPU frequency changes from initial to final must respect "fcpu initial <4\*fcpu final". It must also respect 5

µs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, you can switch from 4.2

MHz to 16 MHz, wait 5 µs, then switch from 16 MHz to 32 MHz.</li>

2. To be USB compliant from the I/O voltage standpoint, the minimum  $V_{\text{DD\_USB}}$  is 3.0 V.

#### Table 4. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                              | Dynamic voltage scaling range |

|--------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws) | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)   | Range 2                       |

| 32 kHz to 4.2 MHz (0ws)                          | Range 3                       |

### 3.4.3 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32 KHz oscillator, RCC\_CSR).

# 3.5 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

Clock prescaler

To get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

#### • Safe clock switching

Clock sources can be changed safely on the fly in Run mode through a configuration register.

#### Clock management

To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

#### System clock source

Three different clock sources can be used to drive the master clock SYSCLK:

- 1-25 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLLMultispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz). When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

#### • Auxiliary clock source

Two ultra-low-power clock sources that can be used to drive the LCD controller and the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

#### • RTC and LCD clock source

The LSI, LSE or HSE sources can be chosen to clock the RTC and the LCD, whatever the system clock.

#### USB clock source

A 48 MHz clock trimmed through the USB SOF or LSE supplies the USB interface.

# 3.8 Memories

The STM32L073xx devices have the following features:

- 20 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 64, 128 or 192 Kbytes of embedded Flash program memory

- 6 Kbytes of data EEPROM

- Information block containing 32 user and factory options bytes plus 8 Kbytes of system memory

Flash program and data EEPROM are divided into two banks. This allows writing in one bank while running code or reading data from the other bank.

The user options bytes are used to write-protect or read-out protect the memory (with 4 Kbyte granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no protection

- Level 1: memory readout protected.

The Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

• Level 2: chip readout protected, debug features (Cortex-M0+ serial wire) and boot in RAM selection disabled (debugline fuse)

The firewall protects parts of code/data from access by the rest of the code that is executed outside of the protected area. The granularity of the protected code segment or the non-volatile data segment is 256 bytes (Flash memory or EEPROM) against 64 bytes for the volatile data segment (RAM).

The whole non-volatile memory embeds the error correction code (ECC) feature.

# 3.9 Boot modes

At startup, BOOT0 pin and nBOOT1 option bit are used to select one of three boot options:

- Boot from Flash memory

- Boot from System memory

- Boot from embedded RAM

The boot loader is located in System memory. It is used to reprogram the Flash memory by using USB (PA11, PA12), USART1(PA9, PA10) or USART2(PA2, PA3). See STM32<sup>™</sup> microcontroller system memory boot mode AN2606 for details.

# 3.16 Touch sensing controller (TSC)

The STM32L073xx provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 24 capacitive sensing channels distributed over 8 analog I/O groups.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (such as glass, plastic). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists of charging the sensor capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. To limit the CPU bandwidth usage, this acquisition is directly managed by the hardware touch sensing controller and only requires few external components to operate.

The touch sensing controller is fully supported by the STMTouch touch sensing firmware library, which is free to use and allows touch sensing functionality to be implemented reliably in the end application.

| Group | Capacitive sensing signal name | Pin<br>name | Group | Capacitive sensing<br>signal name | Pin<br>name |

|-------|--------------------------------|-------------|-------|-----------------------------------|-------------|

|       | TSC_G1_IO1                     | PA0         |       | TSC_G5_IO1                        | PB3         |

| 1     | TSC_G1_IO2                     | PA1         | 5     | TSC_G5_IO2                        | PB4         |

|       | TSC_G1_IO3                     | PA2         | 5     | TSC_G5_IO3                        | PB6         |

|       | TSC_G1_IO4                     | PA3         |       | TSC_G5_IO4                        | PB7         |

|       | TSC_G2_IO1                     | PA4         |       | TSC_G6_IO1                        | PB11        |

| 2     | TSC_G2_IO2                     | PA5         | 6     | TSC_G6_IO2                        | PB12        |

|       | TSC_G2_IO3                     | PA6         | 0     | TSC_G6_IO3                        | PB13        |

|       | TSC_G2_IO4                     | PA7         |       | TSC_G6_IO4                        | PB14        |

|       | TSC_G3_IO1                     | PC5         |       | TSC_G7_IO1                        | PC0         |

| 3     | TSC_G3_IO2                     | PB0         | 7     | TSC_G7_IO2                        | PC1         |

| 5     | TSC_G3_IO3                     | PB1         | 1     | TSC_G7_IO3                        | PC2         |

|       | TSC_G3_IO4                     | PB2         |       | TSC_G7_IO4                        | PC3         |

|       | TSC_G4_IO1                     | PA9         |       | TSC_G8_IO1                        | PC6         |

| 4     | TSC_G4_IO2                     | PA10        | 8     | TSC_G8_IO2                        | PC7         |

|       | TSC_G4_IO3                     | PA11        | 0     | TSC_G8_IO3                        | PC8         |

|       | TSC_G4_IO4                     | PA12        |       | TSC_G8_IO4                        | PC9         |

Table 9. Capacitive sensing GPIOs available on STM32L073xx devices

# 3.18 Communication interfaces

# 3.18.1 I<sup>2</sup>C bus

Up to three I<sup>2</sup>C interfaces (I2C1 and I2C3) can operate in multimaster or slave modes.

Each I<sup>2</sup>C interface can support Standard mode (Sm, up to 100 kbit/s), Fast mode (Fm, up to 400 kbit/s) and Fast Mode Plus (Fm+, up to 1 Mbit/s) with 20 mA output drive on some I/Os.

7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask) are also supported as well as programmable analog and digital noise filters.

|                                     | Analog filter                                         | Digital filter                                                                                       |  |  |

|-------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2C peripheral clocks                                            |  |  |

| Benefits                            | Available in Stop mode                                | <ol> <li>Extra filtering capability vs.<br/>standard requirements.</li> <li>Stable length</li> </ol> |  |  |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.             |  |  |

Table 11. Comparison of I2C analog and digital filters

In addition, I2C1 and I2C3 provide hardware support for SMBus 2.0 and PMBus 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1/I2C3 also have a clock domain independent from the CPU clock, allowing the I2C1/I2C3 to wake up the MCU from Stop mode on address match.

Each I2C interface can be served by the DMA controller.

Refer to Table 12 for an overview of I2C interface features.

| Table 12. | STM32L | .073xx l <sup>2</sup> C | implementation |

|-----------|--------|-------------------------|----------------|

|-----------|--------|-------------------------|----------------|

| I2C features <sup>(1)</sup>                                     | I2C1 | I2C2             | I2C3 |

|-----------------------------------------------------------------|------|------------------|------|

| 7-bit addressing mode                                           | Х    | Х                | Х    |

| 10-bit addressing mode                                          | Х    | Х                | Х    |

| Standard mode (up to 100 kbit/s)                                | Х    | Х                | Х    |

| Fast mode (up to 400 kbit/s)                                    | Х    | Х                | Х    |

| Fast Mode Plus with 20 mA output drive I/Os (up to 1<br>Mbit/s) | х    | X <sup>(2)</sup> | х    |

| Independent clock                                               | Х    | -                | Х    |

| SMBus                                                           | Х    | -                | Х    |

| Wakeup from STOP                                                | Х    | -                | Х    |

1. X = supported.

2. See Table 16: STM32L073xx pin definition on page 42 for the list of I/Os that feature Fast Mode Plus capability

| Table 16. | STM32L | .073xx | pin | definition | (continued) |

|-----------|--------|--------|-----|------------|-------------|

|-----------|--------|--------|-----|------------|-------------|

|        | Pi     | n num   | ber     |          |                                       |          | -             |      |                                                                                      |                      |

|--------|--------|---------|---------|----------|---------------------------------------|----------|---------------|------|--------------------------------------------------------------------------------------|----------------------|

| LQFP48 | LQFP64 | TFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Note | Alternate functions                                                                  | Additional functions |

| 33     | 45     | B8      | 71      | A12      | PA12                                  | I/O      | FT            | (2)  | SPI1_MOSI, EVENTOUT,<br>TSC_G4_IO4,<br>USART1_RTS_DE,<br>COMP2_OUT                   | USB_DP               |

| 34     | 46     | A8      | 72      | A11      | PA13                                  | I/O      | FT            | -    | SWDIO, USB_OE,<br>LPUART1_RX                                                         | -                    |

| -      | -      | -       | 73      | C11      | VDD                                   | S        |               | -    | -                                                                                    | -                    |

| 35     | 47     | D5      | 74      | F11      | VSS                                   | S        |               | -    | -                                                                                    | -                    |

| 36     | 48     | E6      | 75      | G11      | VDD_USB                               | S        |               | -    | -                                                                                    | -                    |

| 37     | 49     | A7      | 76      | A10      | PA14                                  | I/O      | FT            | -    | SWCLK, USART2_TX,<br>LPUART1_TX                                                      | -                    |

| 38     | 50     | A6      | 77      | A9       | PA15                                  | I/O      | FT            | -    | SPI1_NSS, LCD_SEG17,<br>TIM2_ETR, EVENTOUT,<br>USART2_RX, TIM2_CH1,<br>USART4_RTS_DE | -                    |

| -      | 51     | B7      | 78      | B11      | PC10                                  | I/O      | FT            | -    | LPUART1_TX,<br>LCD_COM4/LCD_SEG28/<br>LCD_SEG48, USART4_TX                           | -                    |

| -      | 52     | B6      | 79      | C10      | PC11                                  | I/O      | FT            | -    | LPUART1_RX,<br>LCD_COM5/LCD_SEG29/<br>LCD_SEG49,<br>USART4_RX                        | -                    |

| -      | 53     | C5      | 80      | B10      | PC12                                  | I/O      | FT            | -    | LCD_COM6/LCD_SEG30/<br>LCD_SEG50,<br>USART5_TX,<br>USART4_CK                         | -                    |

| -      | -      | -       | 81      | C9       | PD0                                   | I/O      | FT            | -    | TIM21_CH1,<br>SPI2_NSS/I2S2_WS                                                       | -                    |

| -      | -      | -       | 82      | B9       | PD1                                   | I/O      | FT            | I    | SPI2_SCK/I2S2_CK                                                                     | -                    |

| -      | 54     | В5      | 83      | C8       | PD2                                   | I/O      | FT            | -    | LPUART1_RTS_DE,<br>LCD_COM7/LCD_SEG31/<br>LCD_SEG51, TIM3_ETR,<br>USART5_RX          | -                    |

| -      | -      | -       | 84      | B8       | PD3                                   | I/O      | FT            | -    | USART2_CTS,<br>LCD_SEG44,<br>SPI2_MISO/I2S2_MCK                                      | -                    |

DocID027096 Rev 3

| Symbol            | Parameter          | Conditions                                | Min  | Тур  | Max  | Unit |  |  |  |  |  |

|-------------------|--------------------|-------------------------------------------|------|------|------|------|--|--|--|--|--|

| V                 | PVD threshold 6    | Falling edge                              | 2.97 | 3.05 | 3.09 | v    |  |  |  |  |  |

| V <sub>PVD6</sub> |                    | Rising edge                               | 3.08 | 3.15 | 3.20 | v    |  |  |  |  |  |

|                   |                    | BOR0 threshold                            | -    | 40   | -    |      |  |  |  |  |  |

| V <sub>hyst</sub> | Hysteresis voltage | All BOR and PVD thresholds excepting BOR0 | -    | 100  | -    | mV   |  |  |  |  |  |

Table 27. Embedded reset and power control block characteristics (continued)

1. Guaranteed by characterization results.

2. Valid for device version without BOR at power up. Please see option "D" in Ordering information scheme for more details.

### 6.3.3 Embedded internal reference voltage

The parameters given in *Table 29* are based on characterization results, unless otherwise specified.

| Table 28. Embedde | ed internal reference volta | ge calibration values |

|-------------------|-----------------------------|-----------------------|

|                   |                             |                       |

| Calibration value name | Description                                                            | Memory address            |

|------------------------|------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at<br>temperature of 25 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

| Symbol                                   | Parameter                                                            | Conditions                                                                              | Min   | Тур   | Max   | Unit   |

|------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|--------|

| V <sub>REFINT out</sub> <sup>(2)</sup>   | Internal reference voltage                                           | – 40 °C < T <sub>J</sub> < +125 °C                                                      | 1.202 | 1.224 | 1.242 | V      |

| T <sub>VREFINT</sub>                     | Internal reference startup time                                      | -                                                                                       | -     | 2     | 3     | ms     |

| V <sub>VREF_MEAS</sub>                   | $V_{DDA}$ and $V_{REF+}$ voltage during $V_{REFINT}$ factory measure | -                                                                                       | 2.99  | 3     | 3.01  | V      |

| A <sub>VREF_MEAS</sub>                   | Accuracy of factory-measured $V_{REFINT}$ value <sup>(3)</sup>       | Including uncertainties<br>due to ADC and<br>V <sub>DDA</sub> /V <sub>REF+</sub> values | -     | -     | ±5    | mV     |

| T <sub>Coeff</sub> <sup>(4)</sup>        | Temperature coefficient                                              | –40 °C < T <sub>J</sub> < +125 °C                                                       | -     | 25    | 100   | ppm/°C |

| A <sub>Coeff</sub> <sup>(4)</sup>        | Long-term stability                                                  | 1000 hours, T= 25 °C                                                                    | -     | -     | 1000  | ppm    |

| V <sub>DDCoeff</sub> <sup>(4)</sup>      | Voltage coefficient                                                  | 3.0 V < V <sub>DDA</sub> < 3.6 V                                                        | -     | -     | 2000  | ppm/V  |

| T <sub>S_vrefint</sub> <sup>(4)(5)</sup> | ADC sampling time when<br>reading the internal reference<br>voltage  | -                                                                                       | 5     | 10    | -     | μs     |

| T <sub>ADC_BUF</sub> <sup>(4)</sup>      | Startup time of reference voltage buffer for ADC                     | -                                                                                       | -     | -     | 10    | μs     |

| I <sub>BUF_ADC</sub> <sup>(4)</sup>      | Consumption of reference voltage buffer for ADC                      | -                                                                                       | -     | 13.5  | 25    | μA     |

| I <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output current <sup>(6)</sup>                               | -                                                                                       | -     | -     | 1     | μA     |

| C <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output load                                                 | -                                                                                       | -     | -     | 50    | pF     |

### Table 29. Embedded internal reference voltage<sup>(1)</sup>

| Symbol                                   | parameter                                   | System frequency     | Current<br>consumption<br>during wakeup | Unit |

|------------------------------------------|---------------------------------------------|----------------------|-----------------------------------------|------|

|                                          |                                             | HSI                  | 1                                       |      |

|                                          |                                             | HSI/4                | 0,7                                     |      |

| I <sub>DD</sub> (Wakeup from<br>Stop)    | Supply current during Wakeup from Stop mode | MSI clock = 4,2 MHz  | 0,7                                     |      |

|                                          |                                             | MSI clock = 1,05 MHz | 0,4                                     | mA   |

|                                          |                                             | MSI clock = 65 KHz   | 0,1                                     |      |

| I <sub>DD</sub> (Reset)                  | Reset pin pulled down                       | -                    | 0,21                                    |      |

| I <sub>DD</sub> (Power-up)               | BOR on                                      | -                    | 0,23                                    |      |

| I <sub>DD</sub> (Wakeup from<br>StandBy) | With Fast wakeup set                        | MSI clock = 2,1 MHz  | 0,5                                     |      |

|                                          | With Fast wakeup disabled                   | MSI clock = 2,1 MHz  | 0,12                                    |      |

Table 39. Average current consumption during Wakeup

| Symbol                     | Derinheral                   | Typical consum         | nption, T <sub>A</sub> = 25 °C | Unit   |

|----------------------------|------------------------------|------------------------|--------------------------------|--------|

| Symbol                     | Peripheral —                 | V <sub>DD</sub> =1.8 V | V <sub>DD</sub> =3.0 V         | – Unit |

| I <sub>DD(PVD / BOR)</sub> | -                            | 0.7                    | 1.2                            |        |

| IREFINT                    | -                            | -                      | 1.7                            |        |

| -                          | LSE Low drive <sup>(2)</sup> | 0.11                   | 0,13                           |        |

| -                          | LSI                          | 0.27                   | 0.31                           |        |

| -                          | IWDG                         | 0.2                    | 0.3                            |        |

| -                          | LPTIM1, Input 100 Hz         | 0.01                   | 0,01                           | μA     |

| -                          | LPTIM1, Input 1 MHz 11 12    |                        |                                |        |

| -                          | - LPUART1                    |                        | 0,5                            |        |

| -                          | RTC                          | 0.16                   | 0,3                            |        |

| -                          | LCD1 (static duty)           | 0.15                   | 0.15                           |        |

| -                          | LCD1 (1/8 duty)              | 1.6                    | 2.6                            | μA     |

| Table 41 Peri | pheral current consun | notion in Sto | on and Standh | w mode <sup>(1)</sup> |

|---------------|-----------------------|---------------|---------------|-----------------------|

|               | pheral current consul |               | p and otands  | y mouc                |

1. LCD, LPTIM, LPUART peripherals can operate in Stop mode but not in Standby mode.

2. LSE Low drive consumption is the difference between an external clock on OSC32\_IN and a quartz between OSC32\_IN and OSC32\_OUT.-

### 6.3.5 Wakeup time from low-power mode

The wakeup times given in the following table are measured with the MSI or HSI16 RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is either the MSI oscillator in the range configured before entering Stop mode, the HSI16 or HSI16/4.

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 26*.

## 6.3.6 External clock source characteristics

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.The external clock signal has to respect the I/O characteristics in *Section 6.3.12*. However, the recommended clock input waveform is shown in *Figure 19*.

| Symbol                                     | Parameter                           | Conditions                       | Min          | Тур | Мах                | Unit |

|--------------------------------------------|-------------------------------------|----------------------------------|--------------|-----|--------------------|------|

| f                                          | User external clock source          | CSS is on or<br>PLL is used      | 1            | 8   | 32                 | MHz  |

| <sup>f</sup> HSE_ext                       | frequency                           | CSS is off, PLL<br>not used      | 0            | 8   | 32                 | MHz  |

| V <sub>HSEH</sub>                          | OSC_IN input pin high level voltage |                                  | $0.7 V_{DD}$ | -   | V <sub>DD</sub>    | V    |

| V <sub>HSEL</sub>                          | OSC_IN input pin low level voltage  |                                  | $V_{SS}$     | -   | $0.3V_{\text{DD}}$ | v    |

| t <sub>w(HSE)</sub><br>t <sub>w(HSE)</sub> | OSC_IN high or low time             |                                  | 12           | -   | -                  | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub> | OSC_IN rise or fall time            | -                                | -            | -   | 20                 | 115  |

| C <sub>in(HSE)</sub>                       | OSC_IN input capacitance            |                                  | -            | 2.6 | -                  | pF   |

| DuCy <sub>(HSE)</sub>                      | Duty cycle                          |                                  | 45           | -   | 55                 | %    |

| ١ <sub>L</sub>                             | OSC_IN Input leakage current        | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -            | -   | ±1                 | μA   |

Table 43. High-speed external user clock characteristics<sup>(1)</sup>

1. Guaranteed by design.

| Symbol                                                                        | Parameter                                                                         | Conditions                 | Value              | Unit  |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------|--------------------|-------|

| Symbol                                                                        | Farameter                                                                         | Conditions                 | Min <sup>(1)</sup> | Unit  |

| Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 85 °C |                                                                                   | T <sub>RFT</sub> = +85 °C  | 30                 |       |

| after 100<br>Data rete                                                        | Data retention (EEPROM data memory) after 100 kcycles at $T_A = 85 \text{ °C}$    | 1 <sub>RET</sub> - +65 C   | 30                 |       |

|                                                                               | Data retention (program memory) after 10 kcycles at $T_A$ = 105 °C                | T <sub>RFT</sub> = +105 °C | 10                 | years |

| 'RET`                                                                         | Data retention (EEPROM data memory) after 100 kcycles at $T_A = 105$ °C           | TRET - FIUS C              |                    |       |

|                                                                               | Data retention (program memory) after<br>200 cycles at T <sub>A</sub> = 125 °C    | T - +125 °C                |                    |       |

|                                                                               | Data retention (EEPROM data memory)<br>after 2 kcycles at T <sub>A</sub> = 125 °C | T <sub>RET</sub> = +125 °C |                    |       |

Table 54. Flash memory and data EEPROM endurance and retention (continued)

1. Guaranteed by characterization results.

2. Characterization is done according to JEDEC JESD22-A117.

### 6.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- **Electrostatic discharge (ESD)** (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 55*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                                   | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD} = 3.3 \text{ V}, \text{ LQFP100}, \text{ T}_{\text{A}} = +25 \text{ °C},$<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-2 | 3B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3$ V, LQFP100, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-4                               | 4A              |

#### Table 55. EMS characteristics

### 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu A/+0 \mu A$  range), or other functional failure (for example reset occurrence oscillator frequency deviation).

The test results are given in the Table 59.

|                  |                                                      | Functional s       |                    |      |  |

|------------------|------------------------------------------------------|--------------------|--------------------|------|--|

| Symbol           | Description                                          | Negative injection | Positive injection | Unit |  |

| I <sub>INJ</sub> | Injected current on BOOT0                            | -0                 | NA                 |      |  |

|                  | Injected current on PA0, PA4, PA5, PC15, PH0 and PH1 | -5                 | 0                  | mA   |  |

|                  | Injected current on any other FT, FTf pins           | -5 <sup>(1)</sup>  | NA                 |      |  |

|                  | Injected current on any other pins                   | -5 <sup>(1)</sup>  | +5                 |      |  |

#### Table 59. I/O current injection susceptibility

1. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

# 6.3.16 DAC electrical specifications

Data guaranteed by design, not tested in production, unless otherwise specified.

| Symbol                              | Parameter                                 | Conditions                                                                 | Min | Тур              | Мах                         | Unit |

|-------------------------------------|-------------------------------------------|----------------------------------------------------------------------------|-----|------------------|-----------------------------|------|

| V <sub>DDA</sub>                    | Analog supply voltage                     | -                                                                          | 1.8 | -                | 3.6                         | V    |

| V <sub>REF+</sub>                   | Reference supply voltage                  | V <sub>REF+</sub> must always be<br>below V <sub>DDA</sub>                 | 1.8 | -                | 3.6                         | V    |

| V <sub>REF-</sub>                   | Lower reference voltage                   | -                                                                          |     | V <sub>SSA</sub> |                             | V    |

| . (1)                               | Current consumption on V <sub>REF+</sub>  | No load, middle code<br>(0x800)                                            | -   | 130              | 220                         |      |

| I <sub>DDVREF+</sub> <sup>(1)</sup> | supply<br>V <sub>REF+</sub> = 3.3 V       | No load, worst code<br>(0x000)                                             | -   | 220              | 350                         | μA   |

| ı (2)                               | Current consumption on V <sub>DDA</sub>   | No load, middle code<br>(0x800)                                            | -   | 210              | 320                         |      |

| I <sub>DDA</sub> <sup>(2)</sup>     | supply,<br>V <sub>DDA</sub> = 3.3 V       | No load, worst code<br>(0xF1C)                                             | -   | 320              | 520                         | μA   |

| $R_L^{(3)}$                         | Resistive load                            | DAC output buffer on                                                       | 5   | -                | -                           | kΩ   |

| C <sub>L</sub> <sup>(3)</sup>       | Capacitive load                           |                                                                            | -   | -                | 50                          | pF   |

| R <sub>O</sub>                      | Output impedance                          | DAC output buffer off                                                      | 12  | 16               | 20                          | kΩ   |

| V <sub>DAC_OUT</sub>                | Voltage on DAC_OUT output                 | DAC output buffer ON                                                       | 0.2 | -                | V <sub>DDA</sub> – 0.2      | V    |

|                                     |                                           | DAC output buffer OFF                                                      | 0.5 | -                | V <sub>REF+</sub> –<br>1LSB | mV   |

| DNL <sup>(2)</sup>                  | Differential non linearity <sup>(4)</sup> | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer on | -   | 1.5              | 3                           |      |

|                                     |                                           | No $R_{LOAD}$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer off           | -   | 1.5              | 3                           |      |

| INL <sup>(2)</sup>                  | Integral non linearity <sup>(5)</sup>     | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer on | -   | 2                | 4                           |      |

|                                     |                                           | No $R_{LOAD}$ , $C_L \le 50 \text{ pF}$ DAC output buffer off              | -   | 2                | 4                           | LSB  |

| Offset <sup>(2)</sup>               | Offset error at code 0x800 <sup>(6)</sup> | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer on | -   | ±10              | ±25                         |      |

|                                     |                                           | No $R_{LOAD}$ , $C_L \le 50 \text{ pF}$ DAC output buffer off              | -   | ±5               | ±8                          |      |

| Offset1 <sup>(2)</sup>              | Offset error at code 0x001 <sup>(7)</sup> | No $R_{LOAD}$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer off           | -   | ±1.5             | ±5                          |      |

| Table | 67.         | DAC | characteristics |

|-------|-------------|-----|-----------------|

| Table | <b>U</b> 1. | DAO | characteristics |

| Symbol                    | Parameter                                                                                                                                                 | Conditions                                                                            | Min | Тур          | Max          | Unit  |  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----|--------------|--------------|-------|--|

| dOffset/dT <sup>(2)</sup> | Offset error temperature coefficient (code 0x800)                                                                                                         | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0 V$<br>$T_A = 0$ to 50 °C<br>DAC output buffer off | -20 | -10          | 0            | μV/°C |  |

|                           |                                                                                                                                                           | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0 V$<br>$T_A = 0$ to 50 °C<br>DAC output buffer on  | 0   | 20           | 50           |       |  |

| Gain <sup>(2)</sup>       | Gain error <sup>(8)</sup>                                                                                                                                 | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer on            | -   | +0.1 / -0.2% | +0.2 / -0.5% | %     |  |

|                           |                                                                                                                                                           | No $R_{LOAD}$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer off                      | -   | +0 / -0.2%   | +0 / -0.4%   | 70    |  |

| dGain/dT <sup>(2)</sup>   | Gain error temperature<br>coefficient                                                                                                                     | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0 V$<br>$T_A = 0$ to 50 °C<br>DAC output buffer off | -10 | -2           | 0            | µV/°C |  |

|                           |                                                                                                                                                           | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0 V$<br>$T_A = 0$ to 50 °C<br>DAC output buffer on  | -40 | -8           | 0            |       |  |

| TUE <sup>(2)</sup>        | Total unadjusted error                                                                                                                                    | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer on            | -   | 12           | 30           | - LSB |  |

|                           |                                                                                                                                                           | No $R_{LOAD}$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer off                      | -   | 8            | 12           |       |  |

| t <sub>SETTLING</sub>     | Settling time (full scale: for a<br>12-bit code transition between<br>the lowest and the highest<br>input codes till DAC_OUT<br>reaches final value ±1LSB | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                    | -   | 7            | 12           | μs    |  |

| Update rate               | Max frequency for a correct<br>DAC_OUT change (95% of<br>final value) with 1 LSB<br>variation in the input code                                           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                    | -   | -            | 1            | Msps  |  |

| t <sub>WAKEUP</sub>       | Wakeup time from off state<br>(setting the ENx bit in the DAC<br>Control register) <sup>(9)</sup>                                                         | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                    | -   | 9            | 15           | μs    |  |

| PSRR+                     | V <sub>DDA</sub> supply rejection ratio<br>(static DC measurement)                                                                                        | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                    | -   | -60          | -35          | dB    |  |

### Table 67. DAC characteristics (continued)

1. Guaranteed by characterization results.

2. Guaranteed by design, not tested in production.

3. Connected between DAC\_OUT and  $V_{SSA}$ .

4. Difference between two consecutive codes - 1 LSB.

5. Difference between measured value at Code i and the value at Code i on a line drawn between Code 0 and last Code 4095.

DocID027096 Rev 3

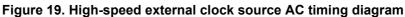

### **Device marking for UFBGA100**

The following figure gives an example of topside marking versus ball A 1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 8 Part numbering

| Table 91. STM32L073xx orc                                   | lering i | nforr | nati | on s | chei | ne |   |   |      |

|-------------------------------------------------------------|----------|-------|------|------|------|----|---|---|------|

| Example:                                                    | STM      | 32 L  | 0    | 73   | R    | 8  | Т | 6 | D TR |

| Device family                                               |          |       |      |      |      |    |   |   |      |

| STM32 = ARM-based 32-bit microcontroller                    |          |       |      |      |      |    |   |   |      |

| Product type                                                |          |       |      |      |      |    |   |   |      |

| L = Low power                                               |          |       |      |      |      |    |   |   |      |

| Device subfamily                                            |          |       |      |      |      |    |   |   |      |

| 073 = USB + LCD                                             |          |       |      |      |      |    |   |   |      |

| Pin count                                                   |          |       |      |      |      |    |   |   |      |

| C = 48/49 pins                                              |          |       |      |      |      |    |   |   |      |

| R = 64 pins                                                 |          |       |      |      |      |    |   |   |      |

| V = 100 pins                                                |          |       |      |      |      |    |   |   |      |

| Flash memory size                                           |          |       |      |      |      |    |   |   |      |

| 8 = 64 Kbytes                                               |          |       |      |      |      |    |   |   |      |

| B = 128 Kbytes                                              |          |       |      |      |      |    |   |   |      |

| Z = 192 Kbytes                                              |          |       |      |      |      |    |   |   |      |

| Package                                                     |          |       |      |      |      |    |   |   |      |

| T = LQFP                                                    |          |       |      |      |      |    |   |   |      |

| H = TFBGA                                                   |          |       |      |      |      |    |   |   |      |

| I = UFBGA                                                   |          |       |      |      |      |    |   |   |      |

| Temperature range                                           |          |       |      |      |      |    |   |   |      |

| 6 = Industrial temperature range, -40 to 85 °C              |          |       |      |      |      |    |   |   |      |

| 7 = Industrial temperature range, -40 to 105 °C             |          |       |      |      |      |    |   |   |      |

| 3 = Industrial temperature range, –40 to 125 $^\circ$ C     |          |       |      |      |      |    |   |   |      |

| Options                                                     |          |       |      |      |      |    |   |   |      |

| No character = $V_{DD}$ range: 1.8 to 3.6 V and BOR enabled |          |       |      |      |      |    |   |   | -    |

| D = $V_{DD}$ range: 1.65 to 3.6 V and BOR disabled          |          |       |      |      |      |    |   |   |      |

| Packing                                                     |          |       |      |      |      |    |   |   |      |

|                                                             |          |       |      |      |      |    |   |   |      |

TR = tape and reel

No character = tray or tube

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID027096 Rev 3