Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Core ProcessorARM® Cortex®-M0+Core Size32-Bit Single-CoreSpeed32MHzConnectivityI*C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, I*S, LCD, POR, PWM, WDTNumber of I/O37Program Memory Size192KB (192K x 8)Program Memory TypeFLASHEEPROM Size6K x 8RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case49-UFBGA, WLCSP |                            |                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed32MHzConnectivityPC, IrDA, LINbus, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, I*S, LCD, POR, PWM, WDTNumber of I/O37Program Memory Size192KB (192K x 8)Program Memory TypeFLASHEEPROM Size6K x 8RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case49-UFBGA, WLCSP                                | Product Status             | Active                                                                  |

| Speed32MHzConnectivityI*C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, I*S, LCD, POR, PWM, WDTNumber of I/O37Program Memory Size192KB (192K x 8)Program Memory TypeFLASHEEPROM Size6K x 8RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case49-UFBGA, WLCSP                                                                                 | Core Processor             | ARM® Cortex®-M0+                                                        |

| Connectivityi²C, IrDA, LINbus, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, I²S, LCD, POR, PWM, WDTNumber of I/O37Program Memory Size192KB (192K x 8)Program Memory TypeFLASHEEPROM Size6K x 8RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case49-UFBGA, WLCSP                                                                    | Core Size                  | 32-Bit Single-Core                                                      |

| PeripheralsBrown-out Detect/Reset, DMA, I2S, LCD, POR, PWM, WDTNumber of I/O37Program Memory Size192KB (192K x 8)Program Memory TypeFLASHEEPROM Size6K x 8RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case49-UFBGA, WLCSP                                                                                                                       | Speed                      | 32MHz                                                                   |

| Number of I/O37Program Memory Size192KB (192K x 8)Program Memory TypeFLASHEEPROM Size6K x 8RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case49-UFBGA, WLCSPSuppler Device Package9-WLCSP                                                                                                                                                         | Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Program Memory Size192KB (192K x 8)Program Memory TypeFLASHEEPROM Size6K x 8RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case49-UFBGA, WLCSP                                                                                                                                                                                                     | Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT       |

| Program Memory TypeFLASHEEPROM Size6K x 8RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case49-UFBGA, WLCSPSupplier Device Package49-WLCSP                                                                                                                                                                                                         | Number of I/O              | 37                                                                      |

| EEPROM Size6K x 8RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case49-UFBGA, WLCSPSupplier Device Package49-WLCSP                                                                                                                                                                                                                                 | Program Memory Size        | 192KB (192K x 8)                                                        |

| RAM Size20K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case49-UFBGA, WLCSPSupplier Device Package49-WLCSP                                                                                                                                                                                                                                                  | Program Memory Type        | FLASH                                                                   |

| Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case49-UFBGA, WLCSPSupplier Device Package49-WLCSP                                                                                                                                                                                                                                                                 | EEPROM Size                | 6K x 8                                                                  |

| Data ConvertersA/D 10x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case49-UFBGA, WLCSPSupplier Device Package49-WLCSP                                                                                                                                                                                                                                                                                                      | RAM Size                   | 20K x 8                                                                 |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case49-UFBGA, WLCSPSupplier Device Package49-WLCSP                                                                                                                                                                                                                                                                                                                                          | Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Operating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case49-UFBGA, WLCSPSupplier Device Package49-WLCSP                                                                                                                                                                                                                                                                                                                                                                 | Data Converters            | A/D 10x12b; D/A 2x12b                                                   |

| Mounting TypeSurface MountPackage / Case49-UFBGA, WLCSPSupplier Device Package49-WLCSP                                                                                                                                                                                                                                                                                                                                                                                                       | Oscillator Type            | Internal                                                                |

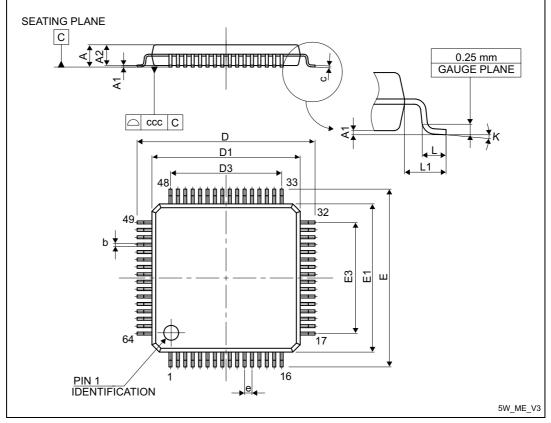

| Package / Case     49-UFBGA, WLCSP       Supplier Device Package     49-WLCSP                                                                                                                                                                                                                                                                                                                                                                                                                | Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Supplier Device Package 49-WLCSP                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Mounting Type              | Surface Mount                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Package / Case             | 49-UFBGA, WLCSP                                                         |

| Purchase URL https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l073czy6tr                                                                                                                                                                                                                                                                                                                                                                                                         | Supplier Device Package    | 49-WLCSP                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l073czy6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3 Functional overview

### 3.1 Low-power modes

The ultra-low-power STM32L073xx support dynamic voltage scaling to optimize its power consumption in Run mode. The voltage from the internal low-drop regulator that supplies the logic can be adjusted according to the system's maximum operating frequency and the external voltage supply.

There are three power consumption ranges:

- Range 1 (V<sub>DD</sub> range limited to 1.71-3.6 V), with the CPU running at up to 32 MHz

- Range 2 (full V<sub>DD</sub> range), with a maximum CPU frequency of 16 MHz

- Range 3 (full V<sub>DD</sub> range), with a maximum CPU frequency limited to 4.2 MHz

Seven low-power modes are provided to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs. Sleep mode power consumption at 16 MHz is about 1 mA with all peripherals off.

#### Low-power run mode

This mode is achieved with the multispeed internal (MSI) RC oscillator set to the lowspeed clock (max 131 kHz), execution from SRAM or Flash memory, and internal regulator in low-power mode to minimize the regulator's operating current. In Lowpower run mode, the clock frequency and the number of enabled peripherals are both limited.

Low-power sleep mode

This mode is achieved by entering Sleep mode with the internal voltage regulator in low-power mode to minimize the regulator's operating current. In Low-power sleep mode, both the clock frequency and the number of enabled peripherals are limited; a typical example would be to have a timer running at 32 kHz.

When wakeup is triggered by an event or an interrupt, the system reverts to the Run mode with the regulator on.

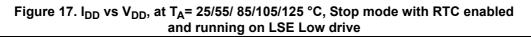

#### Stop mode with RTC

The Stop mode achieves the lowest power consumption while retaining the RAM and register contents and real time clock. All clocks in the  $V_{CORE}$  domain are stopped, the PLL, MSI RC, HSE crystal and HSI RC oscillators are disabled. The LSE or LSI is still running. The voltage regulator is in the low-power mode.

Some peripherals featuring wakeup capability can enable the HSI RC during Stop mode to detect their wakeup condition.

The device can be woken up from Stop mode by any of the EXTI line, in 3.5 µs, the processor can serve the interrupt or resume the code. The EXTI line source can be any GPIO. It can be the PVD output, the comparator 1 event or comparator 2 event (if internal reference voltage is on), it can be the RTC alarm/tamper/timestamp/wakeup events, the USB/USART/I2C/LPUART/LPTIMER wakeup events.

### 3.4.3 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32 KHz oscillator, RCC\_CSR).

### 3.5 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

Clock prescaler

To get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

#### • Safe clock switching

Clock sources can be changed safely on the fly in Run mode through a configuration register.

#### Clock management

To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

### System clock source

Three different clock sources can be used to drive the master clock SYSCLK:

- 1-25 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLLMultispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz). When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

#### • Auxiliary clock source

Two ultra-low-power clock sources that can be used to drive the LCD controller and the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

### • RTC and LCD clock source

The LSI, LSE or HSE sources can be chosen to clock the RTC and the LCD, whatever the system clock.

### USB clock source

A 48 MHz clock trimmed through the USB SOF or LSE supplies the USB interface.

### 3.19 Clock recovery system (CRS)

The STM32L073xx embeds a special block which allows automatic trimming of the internal 48 MHz oscillator to guarantee its optimal accuracy over the whole device operational range. This automatic trimming is based on the external synchronization signal, which could be either derived from USB SOF signalization, from LSE oscillator, from an external signal on CRS\_SYNC pin or generated by user software. For faster lock-in during startup it is also possible to combine automatic trimming with manual trimming action.

### 3.20 Cyclic redundancy check (CRC) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at linktime and stored at a given memory location.

### 3.21 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

|     |      |      |                                                                                                   |                                         | Table 19. Alter                                                                 | mate functior         | ns port C                                          |                                              |                                                             |                                   |

|-----|------|------|---------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------|-----------------------|----------------------------------------------------|----------------------------------------------|-------------------------------------------------------------|-----------------------------------|

|     |      |      | AF0                                                                                               | AF1                                     | AF2                                                                             | AF3                   | AF4                                                | AF5                                          | AF6                                                         | AF7                               |

| •   | F    | Port | SPI1/SPI2/I2S2/<br>USART1/2/<br>LPUART1/USB/<br>LPTIM1/TSC/<br>TIM2/21/22/<br>EVENTOUT/<br>SYS_AF | SPI1/SPI2/I2S2/I2C1/<br>LCD/<br>TIM2/21 | SPI1/SPI2/I2S2/<br>LPUART1/<br>USART5/USB/<br>LPTIM1/TIM2/3<br>/EVENTOUT/SYS_AF | I2C1/TSC/<br>EVENTOUT | I2C1/USART1/2/<br>LPUART1/<br>TIM3/22/<br>EVENTOUT | SPI2/I2S2<br>/I2C2/<br>USART1/<br>TIM2/21/22 | I2C1/2/<br>LPUART1/<br>USART4/<br>UASRT5/TIM21/E<br>VENTOUT | I2C3/LPUART1/<br>COMP1/2/<br>TIM3 |

|     |      | PC0  | LPTIM1_IN1                                                                                        | LCD_SEG18                               | EVENTOUT                                                                        | TSC_G7_IO1            |                                                    |                                              | LPUART1_RX                                                  | I2C3_SCL                          |

|     |      | PC1  | LPTIM1_OUT                                                                                        | LCD_SEG19                               | EVENTOUT                                                                        | TSC_G7_IO2            |                                                    |                                              | LPUART1_TX                                                  | I2C3_SDA                          |

|     |      | PC2  | LPTIM1_IN2                                                                                        | LCD_SEG20                               | SPI2_MISO/<br>I2S2_MCK                                                          | TSC_G7_103            |                                                    |                                              |                                                             |                                   |

| כ   |      | PC3  | LPTIM1_ETR                                                                                        | LCD_SEG21                               | SPI2_MOSI/<br>I2S2_SD                                                           | TSC_G7_104            |                                                    |                                              |                                                             |                                   |

|     |      | PC4  | EVENTOUT                                                                                          | LCD_SEG22                               | LPUART1_TX                                                                      |                       |                                                    |                                              |                                                             |                                   |

| 5   |      | PC5  |                                                                                                   | LCD_SEG23                               | LPUART1_RX                                                                      | TSC_G3_IO1            |                                                    |                                              |                                                             |                                   |

| 000 |      | PC6  | TIM22_CH1                                                                                         | LCD_SEG24                               | TIM3_CH1                                                                        | TSC_G8_IO1            |                                                    |                                              |                                                             |                                   |

| 0   | U    | PC7  | TIM22_CH2                                                                                         | LCD_SEG25                               | TIM3_CH2                                                                        | TSC_G8_IO2            |                                                    |                                              |                                                             |                                   |

| 5   | Port | PC8  | TIM22_ETR                                                                                         | LCD_SEG26                               | TIM3_CH3                                                                        | TSC_G8_IO3            |                                                    |                                              |                                                             |                                   |

|     |      | PC9  | TIM21_ETR                                                                                         | LCD_SEG27                               | USB_OE/TIM3_CH4                                                                 | TSC_G8_IO4            |                                                    |                                              |                                                             | I2C3_SDA                          |

|     |      | PC10 | LPUART1_TX                                                                                        | LCD_COM4/LCD_SEG<br>28/LCD_SEG48        |                                                                                 |                       |                                                    |                                              | USART4_TX                                                   |                                   |

|     |      | PC11 | LPUART1_RX                                                                                        | LCD_COM5/LCD_SEG<br>29/LCD_SEG49        |                                                                                 |                       |                                                    |                                              | USART4_RX                                                   |                                   |

|     |      | PC12 |                                                                                                   | LCD_COM6/LCD_SEG<br>30/LCD_SEG50        | USART5_TX                                                                       |                       |                                                    |                                              | USART4_CK                                                   |                                   |

|     |      | PC13 |                                                                                                   |                                         |                                                                                 |                       |                                                    |                                              |                                                             |                                   |

|     |      | PC14 |                                                                                                   |                                         |                                                                                 |                       |                                                    |                                              |                                                             |                                   |

|     |      | PC15 |                                                                                                   |                                         |                                                                                 |                       |                                                    |                                              |                                                             |                                   |

52/139

STM32L073xx

Pin descriptions

| 53/         |        |      |                                                                                                   |                                      | Table 20. A                                                                         | lternate func         | tions port D                                       |                                              |                                                             |                               |

|-------------|--------|------|---------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------|----------------------------------------------|-------------------------------------------------------------|-------------------------------|

| 53/139      |        |      | AF0                                                                                               | AF1                                  | AF2                                                                                 | AF3                   | AF4                                                | AF5                                          | AF6                                                         | AF7                           |

|             | Port   |      | SPI1/SPI2/I2S2/<br>USART1/2/<br>LPUART1/USB/<br>LPTIM1/TSC/<br>TIM2/21/22/<br>EVENTOUT/<br>SYS_AF | SPI1/SPI2/I2S2/I2C1/<br>LCD/TIM2/21  | SPI1/SPI2/I2S2/<br>LPUART1/<br>USART5/USB/<br>LPTIM1/TIM2/3<br>/EVENTOUT/<br>SYS_AF | I2C1/TSC/<br>EVENTOUT | I2C1/USART1/2/<br>LPUART1/<br>TIM3/22/<br>EVENTOUT | SPI2/I2S2<br>/I2C2/<br>USART1/<br>TIM2/21/22 | I2C1/2/<br>LPUART1/<br>USART4/<br>UASRT5/TIM21/E<br>VENTOUT | I2C3/LPUART1/<br>COMP1/2/TIM3 |

|             |        | PD0  | TIM21_CH1                                                                                         | SPI2_NSS/I2S2_WS                     | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|             |        | PD1  | -                                                                                                 | SPI2_SCK/I2S2_CK                     | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|             |        | PD2  | LPUART1_RTS_<br>DE                                                                                | LCD_COM7/<br>LCD_SEG31/<br>LCD_SEG51 | TIM3_ETR                                                                            | -                     | -                                                  | -                                            | USART5_RX                                                   | -                             |

| Doc         |        | PD3  | USART2_CTS                                                                                        | LCD_SEG44                            | SPI2_MISO/<br>I2S2_MCK                                                              | -                     | -                                                  | -                                            | -                                                           | -                             |

| DocID027096 |        | PD4  | USART2_RTS_D<br>E                                                                                 | SPI2_MOSI/I2S2_SD                    | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

| 096         |        | PD5  | USART2_TX                                                                                         | -                                    | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

| Rev         | D      | PD6  | USART2_RX                                                                                         | -                                    | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

| ώ           | Port D | PD7  | USART2_CK                                                                                         | TIM21_CH2                            | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|             |        | PD8  | LPUART1_TX                                                                                        | LCD_SEG28                            | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|             |        | PD9  | LPUART1_RX                                                                                        | LCD_SEG29                            | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|             |        | PD10 | -                                                                                                 | LCD_SEG30                            | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|             |        | PD11 | LPUART1_CTS                                                                                       | LCD_SEG31                            | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|             |        | PD12 | LPUART1_RTS_<br>DE                                                                                | LCD_SEG32                            | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|             |        | PD13 | -                                                                                                 | LCD_SEG33                            | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|             |        | PD14 | -                                                                                                 | LCD_SEG34                            | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

|             |        | PD15 | USB_CRS_SYNC                                                                                      | LCD_SEG35                            | -                                                                                   | -                     | -                                                  | -                                            | -                                                           | -                             |

5

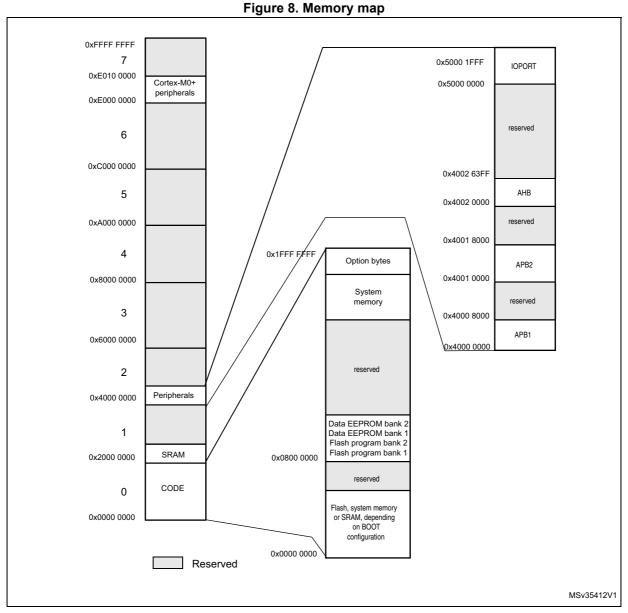

## 5 Memory mapping

1. Refer to the STM32L073xx reference manual for details on the Flash memory organization for each memory size.

### 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 23: Voltage characteristics*, *Table 24: Current characteristics*, and *Table 25: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                                                   | Definition                                                                                                           | Min                  | Мах                  | Unit |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>                                         | External main supply voltage<br>(including V <sub>DDA</sub> , V <sub>DD_USB</sub> , V <sub>DD</sub> ) <sup>(1)</sup> | -0.3                 | 4.0                  |      |

|                                                                          | Input voltage on FT and FTf pins                                                                                     | $V_{SS} - 0.3$       | V <sub>DD</sub> +4.0 |      |

| V <sub>IN</sub> <sup>(2)</sup>                                           | Input voltage on TC pins                                                                                             | V <sub>SS</sub> -0.3 | 4.0                  | V    |

| VIN Y                                                                    | Input voltage on BOOT0                                                                                               | V <sub>SS</sub>      | $V_{DD} + 4.0$       |      |

|                                                                          | Input voltage on any other pin                                                                                       | $V_{SS} - 0.3$       | 4.0                  |      |

| $ \Delta V_{DD} $                                                        | Variations between different $V_{DDx}$ power pins                                                                    | -                    | 50                   |      |

| V <sub>DDA</sub> -V <sub>DDx</sub>                                       | Variations between any $V_{DDx}$ and $V_{DDA}$ power $pins^{(3)}$                                                    | -                    | 300                  | mV   |

| ΔV <sub>SS</sub>                                                         | Variations between all different ground pins including $V_{\text{REF}\text{-}}$ pin                                  | -                    | 50                   |      |

| $V_{REF+} - V_{DDA}$ Allowed voltage difference for $V_{REF+} > V_{DDA}$ |                                                                                                                      | -                    | 0.4                  | V    |

| V <sub>ESD(HBM)</sub>                                                    | Electrostatic discharge voltage (human body model)                                                                   | see Secti            | ion 6.3.11           |      |

| Table 23. | Voltage | characteristics |

|-----------|---------|-----------------|

|-----------|---------|-----------------|

1. All main power ( $V_{DD}, V_{DD}, U_{SB}, V_{DDA}$ ) and ground ( $V_{SS}, V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 24* for maximum allowed injected current values.

It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and device operation. V<sub>DD\_USB</sub> is independent from V<sub>DD</sub> and V<sub>DDA</sub>: its value does not need to respect this rule.

| Symbol            | Parameter          | Conditions                                | Min  | Тур  | Max  | Unit |  |

|-------------------|--------------------|-------------------------------------------|------|------|------|------|--|

| V                 | PVD threshold 6    | Falling edge                              | 2.97 | 3.05 | 3.09 | V    |  |

| V <sub>PVD6</sub> |                    | Rising edge                               | 3.08 | 3.15 | 3.20 | v    |  |

|                   |                    | BOR0 threshold                            | -    | 40   | -    |      |  |

| V <sub>hyst</sub> | Hysteresis voltage | All BOR and PVD thresholds excepting BOR0 | -    | 100  | -    | mV   |  |

Table 27. Embedded reset and power control block characteristics (continued)

1. Guaranteed by characterization results.

2. Valid for device version without BOR at power up. Please see option "D" in Ordering information scheme for more details.

### 6.3.3 Embedded internal reference voltage

The parameters given in *Table 29* are based on characterization results, unless otherwise specified.

| Table 28. Embedde | ed internal reference volta | ge calibration values |

|-------------------|-----------------------------|-----------------------|

|                   |                             |                       |

| Calibration value name | Description                                                            | Memory address            |

|------------------------|------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at<br>temperature of 25 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

| Symbol                                                                              | Parameter                                                            | Conditions                                                                              | Min   | Тур   | Max   | Unit   |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|--------|

| V <sub>REFINT out</sub> <sup>(2)</sup>                                              | Internal reference voltage                                           | – 40 °C < T <sub>J</sub> < +125 °C                                                      | 1.202 | 1.224 | 1.242 | V      |

| T <sub>VREFINT</sub>                                                                | Internal reference startup time                                      | -                                                                                       | -     | 2     | 3     | ms     |

| V <sub>VREF_MEAS</sub>                                                              | $V_{DDA}$ and $V_{REF+}$ voltage during $V_{REFINT}$ factory measure | -                                                                                       | 2.99  | 3     | 3.01  | V      |

| A <sub>VREF_MEAS</sub>                                                              | Accuracy of factory-measured $V_{REFINT}$ value <sup>(3)</sup>       | Including uncertainties<br>due to ADC and<br>V <sub>DDA</sub> /V <sub>REF+</sub> values | -     | -     | ±5    | mV     |

| T <sub>Coeff</sub> <sup>(4)</sup>                                                   | Temperature coefficient                                              | –40 °C < T <sub>J</sub> < +125 °C                                                       | -     | 25    | 100   | ppm/°C |

| A <sub>Coeff</sub> <sup>(4)</sup>                                                   | Long-term stability                                                  | 1000 hours, T= 25 °C                                                                    | -     | -     | 1000  | ppm    |

| V <sub>DDCoeff</sub> <sup>(4)</sup>                                                 | Voltage coefficient                                                  | 3.0 V < V <sub>DDA</sub> < 3.6 V                                                        | -     | -     | 2000  | ppm/V  |

| T <sub>S_vrefint</sub> <sup>(4)(5)</sup>                                            | ADC sampling time when<br>reading the internal reference<br>voltage  | -                                                                                       | 5     | 10    | -     | μs     |

| T <sub>ADC_BUF</sub> <sup>(4)</sup>                                                 | Startup time of reference voltage buffer for ADC                     | -                                                                                       | -     | -     | 10    | μs     |

| I <sub>BUF_ADC</sub> <sup>(4)</sup> Consumption of reference voltage buffer for ADC |                                                                      | -                                                                                       | -     | 13.5  | 25    | μA     |

| I <sub>VREF_OUT</sub> <sup>(4)</sup>                                                | VREF_OUT output current <sup>(6)</sup>                               | -                                                                                       | -     | -     | 1     | μA     |

| C <sub>VREF_OUT</sub> <sup>(4)</sup>                                                | VREF_OUT output load                                                 | -                                                                                       | -     | -     | 50    | pF     |

### Table 29. Embedded internal reference voltage<sup>(1)</sup>

| Symbol               | Parameter                                                      | Conditio                                                          | f <sub>HCLK</sub><br>(MHz)            | Тур   | Max <sup>(1)</sup> | Unit |      |

|----------------------|----------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------|-------|--------------------|------|------|

|                      |                                                                |                                                                   | Range3,                               | 1     | 175                | 230  |      |

|                      |                                                                |                                                                   | Vcore=1.2 V                           | 2     | 315                | 360  | μA   |

|                      |                                                                |                                                                   | VOS[1:0]=11                           | 4     | 570                | 630  |      |

|                      |                                                                | f <sub>HSE</sub> = f <sub>HCLK</sub> up to                        | Range2,                               | 4     | 0,71               | 0,78 |      |

|                      |                                                                | 16 MHz included,<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above | Vcore=1.5 V                           | 8     | 1,35               | 1,6  |      |

|                      | Supply current in Run<br>mode code executed<br>from RAM, Flash | 16 MHz (PLL ON) <sup>(2)</sup>                                    | VOS[1:0]=10                           | 16    | 2,7                | 3    | mA   |

|                      |                                                                |                                                                   | Range1,<br>Vcore=1.8 V                | 8     | 1,7                | 1,9  |      |

| I <sub>DD</sub> (Run |                                                                |                                                                   |                                       | 16    | 3,2                | 3,7  |      |

| from RAM)            |                                                                |                                                                   | VOS[1:0]=01                           | 32    | 6,65               | 7,1  |      |

|                      | memory switched off                                            |                                                                   | Range3,<br>Vcore=1.2 V                | 0,065 | 38                 | 98   |      |

|                      |                                                                | MSI clock                                                         |                                       | 0,524 | 105                | 160  | μA   |

|                      |                                                                |                                                                   | VOS[1:0]=11                           | 4,2   | 615                | 710  |      |

|                      |                                                                | HSI clock source                                                  | Range2,<br>Vcore=1.5 V<br>VOS[1:0]=10 | 16    | 2,85               | 3    | mA   |

|                      |                                                                | (16 MHz)                                                          | Range1,<br>Vcore=1.8 V<br>VOS[1:0]=01 | 32    | 6,85               | 7,3  | IIIA |

#### Table 32. Current consumption in Run mode, code with data processing running from RAM

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

# Table 33. Current consumption in Run mode vs code type,code with data processing running from RAM<sup>(1)</sup>

| Symbol                       | Parameter                       |                                                                                 | f <sub>HCLK</sub>                        | Тур       | Unit   |      |    |

|------------------------------|---------------------------------|---------------------------------------------------------------------------------|------------------------------------------|-----------|--------|------|----|

|                              |                                 |                                                                                 |                                          | Dhrystone |        | 570  |    |

| Supply current in            |                                 |                                                                                 | Range 3,                                 | CoreMark  | 4 MHz  | 670  |    |

|                              | f f unto                        | V <sub>CORE</sub> =1.2 V,<br>VOS[1:0]=11                                        | Fibonacci                                |           | 410    | μA   |    |

| I <sub>DD</sub> (Run<br>from | Run mode, code<br>executed from | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included,                  |                                          | while(1)  |        | 375  |    |

| RAM)                         | RAM, Flash<br>memory switched   | f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above<br>16 MHz (PLL on) <sup>(2)</sup> |                                          | Dhrystone |        | 6,65 |    |

|                              | off                             |                                                                                 | Range 1,                                 | CoreMark  | 32 MHz | 6,95 | mA |

|                              |                                 |                                                                                 | V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01 | Fibonacci |        | 5,9  |    |

|                              |                                 |                                                                                 |                                          | while(1)  |        | 5,2  |    |

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Symbol                 | Parameter                   | Conditions                                   | Тур   | Max <sup>(1)</sup> | Unit |  |

|------------------------|-----------------------------|----------------------------------------------|-------|--------------------|------|--|

|                        |                             | $T_{A} = -40 \text{ to } 25^{\circ}\text{C}$ | 0,43  | 1,00               |      |  |

|                        | Supply current in Stop mode | T <sub>A</sub> = 55°C                        | 0,735 | 2,50               |      |  |

| I <sub>DD</sub> (Stop) |                             | T <sub>A</sub> = 85°C                        | 2,25  | 4,90               | μA   |  |

|                        |                             | T <sub>A</sub> = 105°C                       | 5,3   | 13,00              |      |  |

|                        |                             | T <sub>A</sub> = 125°C                       | 12,5  | 28,00              |      |  |

Table 37. Typical and maximum current consumptions in Stop mode

1. Guaranteed by characterization results at 125  $^\circ\text{C},$  unless otherwise specified.

### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in the following tables. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

### Table 40. Peripheral current consumption in Run or Sleep mode<sup>(1)</sup>

| Peripheral |         | Typical                                               | consumption, V                                        | / <sub>DD</sub> = 3.0 V, T <sub>A</sub> =             | 25 °C                         |                      |

|------------|---------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------|----------------------|

|            |         | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | Low-power<br>sleep and<br>run | Unit                 |

|            | CRS     | 2.5                                                   | 2                                                     | 2                                                     | 2                             |                      |

|            | DAC1/2  | 4                                                     | 3.5                                                   | 3                                                     | 2.5                           |                      |

|            | I2C1    | 11                                                    | 9.5                                                   | 7.5                                                   | 9                             |                      |

|            | I2C3    | 11                                                    | 9                                                     | 7                                                     | 9                             |                      |

|            | LCD1    | 4                                                     | 3.5                                                   | 3                                                     | 2.5                           |                      |

|            | LPTIM1  | 10                                                    | 8.5                                                   | 6.5                                                   | 8                             |                      |

|            | LPUART1 | 8                                                     | 6.5                                                   | 5.5                                                   | 6                             |                      |

|            | SPI2    | 9                                                     | 4.5                                                   | 3.5                                                   | 4                             | µA/MHz               |

| APB1       | USB     | 8.5                                                   | 4.5                                                   | 4                                                     | 4.5                           | (f <sub>HCLK</sub> ) |

|            | USART2  | 14.5                                                  | 12                                                    | 9.5                                                   | 11                            |                      |

|            | USART4  | 5                                                     | 4                                                     | 3                                                     | 5                             |                      |

|            | USART5  | 5                                                     | 4                                                     | 3                                                     | 5                             |                      |

|            | TIM2    | 10.5                                                  | 8.5                                                   | 7                                                     | 9                             |                      |

|            | TIM3    | 12                                                    | 10                                                    | 8                                                     | 11                            |                      |

|            | TIM6    | 3.5                                                   | 3                                                     | 2.5                                                   | 2                             |                      |

|            | TIM7    | 3.5                                                   | 3                                                     | 2.5                                                   | 2                             |                      |

|            | WWDG    | 3                                                     | 2                                                     | 2                                                     | 2                             |                      |

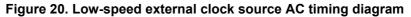

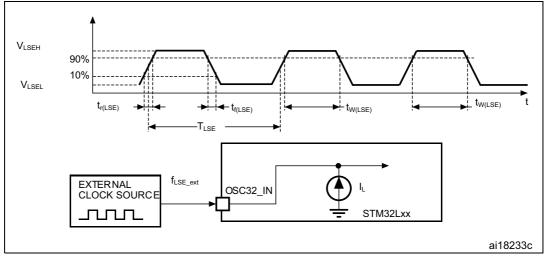

### Low-speed external user clock generated from an external source

The characteristics given in the following table result from tests performed using a lowspeed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 26*.

| Symbol                                     | Parameter                               | Conditions                       | Min                | Тур    | Max                | Unit |

|--------------------------------------------|-----------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User external clock source<br>frequency |                                  | 1                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage   |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | v    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage    | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSE)</sub><br>t <sub>w(LSE)</sub> | OSC32_IN high or low time               |                                  | 465                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time              |                                  | -                  | -      | 10                 | 115  |

| C <sub>IN(LSE)</sub>                       | OSC32_IN input capacitance              | -                                | -                  | 0.6    | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                              | -                                | 45                 | -      | 55                 | %    |

| ١L                                         | OSC32_IN Input leakage current          | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |

Table 44. Low-speed external user clock characteristics<sup>(1)</sup>

1. Guaranteed by design, not tested in production

| Symbol                                | Parameter                          | Condition                                | Тур                | Max                                                 | Unit |  |

|---------------------------------------|------------------------------------|------------------------------------------|--------------------|-----------------------------------------------------|------|--|

|                                       |                                    | MSI range 0                              | -                  | 40                                                  |      |  |

|                                       |                                    | MSI range 1 - 20                         |                    |                                                     |      |  |

|                                       |                                    | MSI range 2                              | -                  | 40<br>20<br>10<br>4<br>2.5<br>2<br>2<br>2<br>3<br>4 |      |  |

|                                       |                                    | MSI range 3 - 4                          |                    |                                                     |      |  |

| + (2)                                 | MSI oscillator stabilization time  | MSI range 4                              | VISI range 4 - 2.5 |                                                     | μs   |  |

| t <sub>STAB(MSI)</sub> <sup>(2)</sup> |                                    | MSI range 5                              | -                  | 2                                                   | μο   |  |

|                                       |                                    | MSI range 6,<br>Voltage range 1<br>and 2 | - 2                |                                                     |      |  |

|                                       |                                    | MSI range 3,<br>Voltage range 3          | -                  | 3                                                   |      |  |

| f <sub>over(MSI)</sub>                | MSI oscillator frequency overshoot | Any range to range 5                     |                    | 4                                                   | MHz  |  |

|                                       |                                    | Any range to<br>range 6                  | -                  | 6                                                   |      |  |

Table 50. MSI oscillator characteristics (continued)

1. This is a deviation for an individual part, once the initial frequency has been measured.

2. Guaranteed by characterization results.

### 6.3.8 PLL characteristics

The parameters given in *Table 51* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 26*.

| Table 51. PLL characteristics |

|-------------------------------|

|-------------------------------|

| Symbol                 | Parameter                               |     | Value |                    | Unit |

|------------------------|-----------------------------------------|-----|-------|--------------------|------|

| Symbol                 | Farameter                               | Min | Тур   | Max <sup>(1)</sup> | Unit |

| £                      | PLL input clock <sup>(2)</sup>          | 2   | -     | 24                 | MHz  |

| f <sub>PLL_IN</sub>    | PLL input clock duty cycle              | 45  | -     | 55                 | %    |

| f <sub>PLL_OUT</sub>   | PLL output clock                        | 2   | -     | 32                 | MHz  |

| t <sub>LOCK</sub>      | PLL input = 16 MHz<br>PLL VCO = 96 MHz  | -   | 115   | 160                | μs   |

| Jitter                 | Cycle-to-cycle jitter                   | -   |       | $\pm600$           | ps   |

| I <sub>DDA</sub> (PLL) | Current consumption on V <sub>DDA</sub> | -   | 220   | 450                | μA   |

| I <sub>DD</sub> (PLL)  | Current consumption on V <sub>DD</sub>  | -   | 120   | 150                | μΑ   |

1. Guaranteed by characterization results.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{PLL_OUT}$ .

### 6.3.9 Memory characteristics

### **RAM** memory

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

Table 52. RAM and hardware registers

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

### Flash memory and data EEPROM

| Symbol               | Parameter                                                                      | Conditions                                      | Min  | Тур  | Max <sup>(1)</sup> | Unit |

|----------------------|--------------------------------------------------------------------------------|-------------------------------------------------|------|------|--------------------|------|

| V <sub>DD</sub>      | Operating voltage<br>Read / Write / Erase                                      | -                                               | 1.65 | -    | 3.6                | V    |

| Programming time for |                                                                                | Erasing                                         | -    | 3.28 | 3.94               | me   |

| τ <sub>prog</sub>    | word or half-page                                                              | Programming                                     | -    | 3.28 | 3.94               | ms   |

|                      | Average current during<br>the whole programming /<br>erase operation           |                                                 | -    | 500  | 700                | μA   |

| I <sub>DD</sub>      | Maximum current (peak)<br>during the whole<br>programming / erase<br>operation | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 1.5  | 2.5                | mA   |

### Table 53. Flash memory and data EEPROM characteristics

1. Guaranteed by design.

| Table 54. Flash memory | and data EEPROM endurance and retention |  |

|------------------------|-----------------------------------------|--|

|                        |                                         |  |

| Symbol                          | Parameter                                     | Conditions                       | Value              | Unit    |  |

|---------------------------------|-----------------------------------------------|----------------------------------|--------------------|---------|--|

| Symbol                          | Falameter                                     | Conditions                       | Min <sup>(1)</sup> | Unit    |  |

|                                 | Cycling (erase / write)<br>Program memory     | T 40°C to 105 °C                 | 10                 | kcycles |  |

| N. (2)                          | Cycling (erase / write)<br>EEPROM data memory | T <sub>A</sub> = -40°C to 105 °C | 100                |         |  |

| N <sub>CYC</sub> <sup>(2)</sup> | Cycling (erase / write)<br>Program memory     | T 40°C to 125 °C                 | 0.2                | KUYUUUS |  |

|                                 | Cycling (erase / write)<br>EEPROM data memory | T <sub>A</sub> = -40°C to 125 °C | 2                  |         |  |

| Symbol                                | Parameter                          | Conditions                                      | Min                                                                           | Тур   | Max                                               | Unit                       |

|---------------------------------------|------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------------|-------|---------------------------------------------------|----------------------------|

| C <sub>ADC</sub> <sup>(3)</sup>       | Internal sample and hold capacitor | -                                               | -                                                                             | -     | 8                                                 | pF                         |

| <b>↓</b> (3)(5)                       | Calibration time                   | f <sub>ADC</sub> = 16 MHz                       |                                                                               | 5.2   |                                                   | μs                         |

| t <sub>CAL</sub> <sup>(3)(5)</sup>    | Calibration time                   | -                                               |                                                                               | 83    |                                                   | 1/f <sub>ADC</sub>         |

|                                       |                                    | ADC clock = HSI16                               | 1.5 ADC<br>cycles + 2<br>f <sub>PCLK</sub> cycles                             | -     | 1.5 ADC<br>cycles + 3<br>f <sub>PCLK</sub> cycles | -                          |

| W <sub>LATENCY</sub> <sup>(6)</sup>   | ADC_DR register write<br>latency   | ADC clock = PCLK/2                              | -                                                                             | 4.5   | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                       |                                    | ADC clock = PCLK/4                              | -                                                                             | 8.5   | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                       |                                    | $f_{ADC} = f_{PCLK}/2 = 16 \text{ MHz}$         |                                                                               | 0.266 |                                                   |                            |

|                                       |                                    | $f_{ADC} = f_{PCLK}/2$                          | 8.5                                                                           |       | 1/f <sub>PCLK</sub>                               |                            |

| t <sub>latr</sub> (3)                 | Trigger conversion latency         | $f_{ADC} = f_{PCLK}/4 = 8 \text{ MHz}$          | 0.516                                                                         |       | μs                                                |                            |

|                                       |                                    | $f_{ADC} = f_{PCLK}/4$                          | 16.5                                                                          |       | 1/f <sub>PCLK</sub>                               |                            |

|                                       |                                    | f <sub>ADC</sub> = f <sub>HSI16</sub> = 16 MHz  | 0.252                                                                         | -     | 0.260                                             | μs                         |

| Jitter <sub>ADC</sub>                 | ADC jitter on trigger conversion   | f <sub>ADC</sub> = f <sub>HSI16</sub>           | -                                                                             | 1     | -                                                 | 1/f <sub>HSI16</sub>       |

| ts <sup>(3)</sup>                     | Sampling time                      | f <sub>ADC</sub> = 16 MHz                       | 0.093                                                                         | -     | 10.03                                             | μs                         |

| LS (*)                                |                                    | -                                               | 1.5                                                                           | -     | 160.5                                             | 1/f <sub>ADC</sub>         |

| t <sub>UP_LDO</sub> <sup>(3)(5)</sup> | Internal LDO power-up time         | -                                               | -                                                                             | -     | 10                                                | μs                         |

| t <sub>STAB</sub> <sup>(3)(5)</sup>   | ADC stabilization time             | -                                               | 14                                                                            |       | 1/f <sub>ADC</sub>                                |                            |

| t <sub>ConV</sub> <sup>(3)</sup>      | Total conversion time              | f <sub>ADC</sub> = 16 MHz,<br>12-bit resolution | 0.875                                                                         | -     | 10.81                                             | μs                         |

|                                       | (including sampling time)          | 12-bit resolution                               | 14 to 173 (t <sub>S</sub> for sampling +12.5<br>for successive approximation) |       |                                                   | 1/f <sub>ADC</sub>         |

1. V<sub>DDA</sub> minimum value can be decreased in specific temperature conditions. Refer to Table 65: RAIN max for fADC = 16 MHz.

2. A current consumption proportional to the APB clock frequency has to be added (see *Table 40: Peripheral current consumption in Run or Sleep mode*).

3. Guaranteed by design.

Standard channels have an extra protection resistance which depends on supply voltage. Refer to Table 65: RAIN max for fADC = 16 MHz.

5. This parameter only includes the ADC timing. It does not take into account register access latency.

6. This parameter specifies the latency to transfer the conversion result into the ADC\_DR register. EOC bit is set to indicate the conversion is complete and has the same latency.

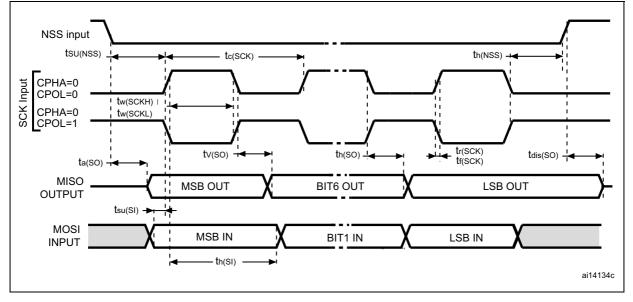

### **SPI characteristics**