# E·XFL

#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 50                                                                    |

| Program Memory Size        | 192KB (192K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 6K x 8                                                                |

| RAM Size                   | 20K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 15x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-UFBGA                                                              |

| Supplier Device Package    | 64-UFBGA (5x5)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l073rzh6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 43. | grid array package outline                                                  |

|------------|-----------------------------------------------------------------------------|

| Ū          | grid array package recommended footprint                                    |

| Figure 44. | UFBGA100 marking example (package top view) 124                             |

| Figure 45. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline           |

| Figure 46. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint 126 |

| Figure 47. | LQFP64 marking example (package top view) 127                               |

| Figure 48. | TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch thin profile fine pitch ball      |

|            | grid array package outline                                                  |

| Figure 49. | TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball     |

|            | ,grid array recommended footprint                                           |

| Figure 50. | TFBGA64 marking example (package top view)                                  |

| Figure 51. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline             |

| Figure 52. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint       |

| Figure 53. | LQFP48 marking example (package top view)                                   |

| Figure 54. | Thermal resistance                                                          |

## 1 Introduction

The ultra-low-power STM32L073xx are offered in 5 different package types from 48 to 100 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the ultra-low-power STM32L073xx microcontrollers suitable for a wide range of applications:

- Gas/water meters and industrial sensors

- Healthcare and fitness equipment

- Remote control and user interface

- PC peripherals, gaming, GPS equipment

- Alarm system, wired and wireless sensors, video intercom

This STM32L073xx datasheet should be read in conjunction with the STM32L0x3xx reference manual (RM0367).

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ core please refer to the Cortex<sup>®</sup>-M0+ Technical Reference Manual, available from the www.arm.com website.

*Figure 1* shows the general block diagram of the device family.

### 3.4.3 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32 KHz oscillator, RCC\_CSR).

### 3.5 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

Clock prescaler

To get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

### • Safe clock switching

Clock sources can be changed safely on the fly in Run mode through a configuration register.

### Clock management

To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

### System clock source

Three different clock sources can be used to drive the master clock SYSCLK:

- 1-25 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLLMultispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz). When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

### • Auxiliary clock source

Two ultra-low-power clock sources that can be used to drive the LCD controller and the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog. The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

### • RTC and LCD clock source

The LSI, LSE or HSE sources can be chosen to clock the RTC and the LCD, whatever the system clock.

### USB clock source

A 48 MHz clock trimmed through the USB SOF or LSE supplies the USB interface.

## 3.16 Touch sensing controller (TSC)

The STM32L073xx provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 24 capacitive sensing channels distributed over 8 analog I/O groups.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (such as glass, plastic). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists of charging the sensor capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. To limit the CPU bandwidth usage, this acquisition is directly managed by the hardware touch sensing controller and only requires few external components to operate.

The touch sensing controller is fully supported by the STMTouch touch sensing firmware library, which is free to use and allows touch sensing functionality to be implemented reliably in the end application.

| Group | Capacitive sensing signal name | Pin<br>name | Group | Capacitive sensing<br>signal name | Pin<br>name |

|-------|--------------------------------|-------------|-------|-----------------------------------|-------------|

|       | TSC_G1_IO1                     | PA0         |       | TSC_G5_IO1                        | PB3         |

| 1     | TSC_G1_IO2                     | PA1         | 5     | TSC_G5_IO2                        | PB4         |

| 1     | TSC_G1_IO3                     | PA2         | 5     | TSC_G5_IO3                        | PB6         |

|       | TSC_G1_IO4                     | PA3         |       | TSC_G5_IO4                        | PB7         |

|       | TSC_G2_IO1                     | PA4         |       | TSC_G6_IO1                        | PB11        |

| 2     | TSC_G2_IO2                     | PA5         | 6     | TSC_G6_IO2                        | PB12        |

| 2     | TSC_G2_IO3                     | PA6         | 0     | TSC_G6_IO3                        | PB13        |

|       | TSC_G2_IO4                     | PA7         |       | TSC_G6_IO4                        | PB14        |

|       | TSC_G3_IO1                     | PC5         |       | TSC_G7_IO1                        | PC0         |

| 3     | TSC_G3_IO2                     | PB0         | 7     | TSC_G7_IO2                        | PC1         |

| 5     | TSC_G3_IO3                     | PB1         | 1     | TSC_G7_IO3                        | PC2         |

|       | TSC_G3_IO4                     | PB2         |       | TSC_G7_IO4                        | PC3         |

|       | TSC_G4_IO1                     | PA9         |       | TSC_G8_IO1                        | PC6         |

| 4     | TSC_G4_IO2                     | PA10        | 8     | TSC_G8_IO2                        | PC7         |

| -     | TSC_G4_IO3                     | PA11        | 0     | TSC_G8_IO3                        | PC8         |

|       | TSC_G4_IO4                     | PA12        |       | TSC_G8_IO4                        | PC9         |

Table 9. Capacitive sensing GPIOs available on STM32L073xx devices

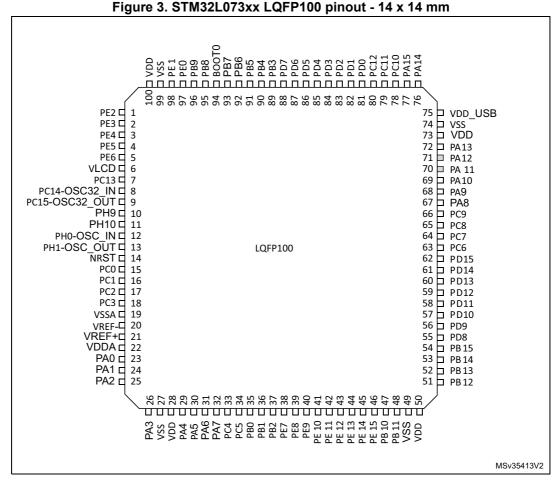

## 4 Pin descriptions

1. The above figure shows the package top view.

2. I/O pin supplied by VDD\_USB.

|   | i igule c                  |        |       |       |        | Danou  | l - JX J |        |

|---|----------------------------|--------|-------|-------|--------|--------|----------|--------|

|   | 1                          | 2      | 3     | 4     | 5      | 6      | 7        | 8      |

| A | ₽°C14-<br>OSC32<br>`_41¥   | (PC13) | (PB9) | (PB4) | (PB3)  | (PA15) | (PA14)   | (PA13) |

| В | アCT5-<br>OSC32<br>OUオ      | (VLCD) | (PB8) |       | (PD2)  | (PC11) | (PC10)   | (PA12) |

| С | (PHO-)<br>osc_IN           | (vss)  | (PB7) | (PB5) | (PC12) | (PA10) | (PA9)    | (PA11) |

| D | ( 0SC )<br>( 0SC )<br>\QUT |        | (PB6) | (vss) | (vss)  | (vss)  | (PA8)    | (PC9)  |

| E |                            | (PC1)  | (PC0) | (VDD) | (VDD)  |        | (PC7)    | (PC8)  |

| F | (VSSA)                     | (PC2)  | (PA2) | (PA5) | (PB0)  | (PC6)  | (PB15)   | (PB14) |

| G |                            | (PA0)  | (PA3) | (PA6) | (PB1)  | (PB2)  | (PB10)   | (PB13) |

| Н | (VDDA)                     | (PA1)  | (PA4) | (PA7) | (PC4)  | (PC5)  | (PB11)   | (PB12) |

|   | L                          |        |       |       |        |        |          |        |

Figure 6. STM32L073xx TFBGA64 ballout - 5x 5 mm

1. The above figure shows the package top view.

2. I/O pin supplied by VDD\_USB.

| Name          |                        | Abbreviation                                   | Definition                              |  |  |  |  |

|---------------|------------------------|------------------------------------------------|-----------------------------------------|--|--|--|--|

| Pin functions | Alternate<br>functions | Functions selected through GPIOx_AFR registers |                                         |  |  |  |  |

|               | Additional functions   | Functions directly selecte                     | ed/enabled through peripheral registers |  |  |  |  |

Table 15. Legend/abbreviations used in the pinout table (continued)

|        | Pi     | n num   | ber     |          |                                       |          |               |      |                                   |                                    |

|--------|--------|---------|---------|----------|---------------------------------------|----------|---------------|------|-----------------------------------|------------------------------------|

| LQFP48 | LQFP64 | TFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Note | Alternate functions               | Additional functions               |

| -      | -      | -       | 1       | B2       | PE2                                   | I/O      | FT            | -    | LCD_SEG38, TIM3_ETR               | -                                  |

| -      | -      | -       | 2       | A1       | PE3                                   | I/O      | FT            | -    | TIM22_CH1, LCD_SEG39,<br>TIM3_CH1 | -                                  |

| -      | -      | -       | 3       | B1       | PE4                                   | I/O      | FT            | -    | TIM22_CH2, TIM3_CH2               | -                                  |

| -      | -      | -       | 4       | C2       | PE5                                   | I/O      | FT            | -    | TIM21_CH1, TIM3_CH3               | -                                  |

| -      | -      | -       | 5       | D2       | PE6                                   | I/O      | FT            | -    | TIM21_CH2, TIM3_CH4               | RTC_TAMP3/WKUP3                    |

| 1      | 1      | B2      | 6       | E2       | VLCD                                  | S        |               | -    | -                                 |                                    |

| 2      | 2      | A2      | 7       | C1       | PC13                                  | I/O      | FT            | -    | -                                 | RTC_TAMP1/RTC_TS/<br>RTC_OUT/WKUP2 |

| 3      | 3      | A1      | 8       | D1       | PC14-<br>OSC32_IN<br>(PC14)           | I/O      | FT            | -    | -                                 | OSC32_IN                           |

| 4      | 4      | B1      | 9       | E1       | PC15-<br>OSC32_OUT<br>(PC15)          | I/O      | тс            | -    | -                                 | OSC32_OUT                          |

| -      | -      | -       | 10      | F2       | PH9                                   | I/O      | FT            | -    | -                                 | -                                  |

| -      | -      | -       | 11      | G2       | PH10                                  | I/O      | FT            | -    | -                                 | -                                  |

| 5      | 5      | C1      | 12      | F1       | PH0-OSC_IN<br>(PH0)                   | I/O      | тс            | -    | USB_CRS_SYNC                      | OSC_IN                             |

| 6      | 6      | D1      | 13      | G1       | PH1-<br>OSC_OUT<br>(PH1)              | I/O      | тс            | -    | -                                 | OSC_OUT                            |

| 7      | 7      | E1      | 14      | H2       | NRST                                  | I/O      | -             | -    | -                                 | -                                  |

### Table 16. STM32L073xx pin definition

| C | Ŋ |

|---|---|

|   | S |

|   | ŝ |

| Ś | Ş |

| Š | 2 |

|   |   |

DocID027096 Rev 3

5

|        |      |                                                                                                   |                                         | Table 17.                                                                           | Alternate fund        | tions port A                                       | -                                        |                                                             |                                   |

|--------|------|---------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------|------------------------------------------|-------------------------------------------------------------|-----------------------------------|

|        |      | AF0                                                                                               | AF1                                     | AF2                                                                                 | AF3                   | AF4                                                | AF5                                      | AF6                                                         | AF7                               |

| F      | Port | SPI1/SPI2/I2S2/U<br>SART1/2/<br>LPUART1/USB/L<br>PTIM1/TSC/<br>TIM2/21/22/<br>EVENTOUT/<br>SYS_AF | SPI1/SPI2/I2S2/I2<br>C1/LCD/<br>TIM2/21 | SPI1/SPI2/I2S2/L<br>PUART1/<br>USART5/USB/LP<br>TIM1/TIM2/3/EVE<br>NTOUT/<br>SYS_AF | I2C1/TSC/<br>EVENTOUT | I2C1/USART1/2/<br>LPUART1/<br>TIM3/22/<br>EVENTOUT | SPI2/I2S2/I2C2/U<br>SART1/<br>TIM2/21/22 | I2C1/2/<br>LPUART1/<br>USART4/<br>UASRT5/TIM21/E<br>VENTOUT | I2C3/LPUART1/C<br>OMP1/2/<br>TIM3 |

|        | PA0  | -                                                                                                 | -                                       | TIM2_CH1                                                                            | TSC_G1_IO1            | USART2_CTS                                         | TIM2_ETR                                 | USART4_TX                                                   | COMP1_OUT                         |

|        | PA1  | EVENTOUT                                                                                          | LCD_SEG0                                | TIM2_CH2                                                                            | TSC_G1_IO2            | USART2_RTS_D<br>E                                  | TIM21_ETR                                | USART4_RX                                                   | -                                 |

|        | PA2  | TIM21_CH1                                                                                         | LCD_SEG1                                | TIM2_CH3                                                                            | TSC_G1_IO3            | USART2_TX                                          | -                                        | LPUART1_TX                                                  | COMP2_OUT                         |

|        | PA3  | TIM21_CH2                                                                                         | LCD_SEG2                                | TIM2_CH4                                                                            | TSC_G1_IO4            | USART2_RX                                          | -                                        | LPUART1_RX                                                  | -                                 |

|        | PA4  | SPI1_NSS                                                                                          | -                                       | -                                                                                   | TSC_G2_IO1            | USART2_CK                                          | TIM22_ETR                                | -                                                           | -                                 |

|        | PA5  | SPI1_SCK                                                                                          | -                                       | TIM2_ETR                                                                            | TSC_G2_IO2            |                                                    | TIM2_CH1                                 | -                                                           | -                                 |

|        | PA6  | SPI1_MISO                                                                                         | LCD_SEG3                                | TIM3_CH1                                                                            | TSC_G2_IO3            | LPUART1_CTS                                        | TIM22_CH1                                | EVENTOUT                                                    | COMP1_OUT                         |

|        | PA7  | SPI1_MOSI                                                                                         | LCD_SEG4                                | TIM3_CH2                                                                            | TSC_G2_IO4            | -                                                  | TIM22_CH2                                | EVENTOUT                                                    | COMP2_OUT                         |

| Port A | PA8  | МСО                                                                                               | LCD_COM0                                | USB_CRS_<br>SYNC                                                                    | EVENTOUT              | USART1_CK                                          | -                                        | -                                                           | I2C3_SCL                          |

|        | PA9  | MCO                                                                                               | LCD_COM1                                | -                                                                                   | TSC_G4_IO1            | USART1_TX                                          | -                                        | I2C1_SCL                                                    | I2C3_SMBA                         |

|        | PA10 | -                                                                                                 | LCD_COM2                                | -                                                                                   | TSC_G4_IO2            | USART1_RX                                          | -                                        | I2C1_SDA                                                    | -                                 |

|        | PA11 | SPI1_MISO                                                                                         | -                                       | EVENTOUT                                                                            | TSC_G4_IO3            | USART1_CTS                                         | -                                        | -                                                           | COMP1_OUT                         |

|        | PA12 | SPI1_MOSI                                                                                         | -                                       | EVENTOUT                                                                            | TSC_G4_IO4            | USART1_RTS_<br>DE                                  | -                                        | -                                                           | COMP2_OUT                         |

|        | PA13 | SWDIO                                                                                             | -                                       | USB_OE                                                                              | -                     | -                                                  | -                                        | LPUART1_RX                                                  | -                                 |

|        | PA14 | SWCLK                                                                                             | -                                       | -                                                                                   | -                     | USART2_TX                                          | -                                        | LPUART1_TX                                                  | -                                 |

|        | PA15 | SPI1_NSS                                                                                          | LCD_SEG17                               | TIM2_ETR                                                                            | EVENTOUT              | USART2_RX                                          | TIM2_CH1                                 | USART4_RTS_D<br>E                                           | -                                 |

Pin descriptions

50/139

51/139

DocID027096 Rev 3

5

|        |      | 4.50                                                                                              | 454                                     |                                                                                     |                       | functions port B                                   | 455                                      | 450                                                         | 457                               |  |

|--------|------|---------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------|------------------------------------------|-------------------------------------------------------------|-----------------------------------|--|

|        |      | AF0                                                                                               | AF1                                     | AF2                                                                                 | AF3                   | AF4                                                | AF5                                      | AF6                                                         | AF7                               |  |

|        | Port | SPI1/SPI2/I2S2/<br>USART1/2/<br>LPUART1/USB/<br>LPTIM1/TSC/<br>TIM2/21/22/<br>EVENTOUT/<br>SYS_AF | SPI1/SPI2/I2S2/I<br>2C1/LCD/<br>TIM2/21 | SPI1/SPI2/I2S2/<br>LPUART1/<br>USART5/USB/L<br>PTIM1/TIM2/3/E<br>VENTOUT/<br>SYS_AF | I2C1/TSC/<br>EVENTOUT | I2C1/USART1/2/<br>LPUART1/<br>TIM3/22/<br>EVENTOUT | SPI2/I2S2/I2C2/<br>USART1/<br>TIM2/21/22 | I2C1/2/<br>LPUART1/<br>USART4/<br>UASRT5/TIM21/<br>EVENTOUT | I2C3/LPUART1/<br>COMP1/2/<br>TIM3 |  |

|        | PB0  | EVENTOUT                                                                                          | LCD_SEG5                                | TIM3_CH3                                                                            | TSC_G3_IO2            | -                                                  | -                                        | -                                                           | -                                 |  |

|        | PB1  | -                                                                                                 | LCD_SEG6                                | TIM3_CH4                                                                            | TSC_G3_IO3            | LPUART1_RTS_DE                                     | -                                        | -                                                           | -                                 |  |

|        | PB2  | -                                                                                                 | -                                       | LPTIM1_OUT                                                                          | TSC_G3_IO4            | -                                                  | -                                        | -                                                           | I2C3_SMBA                         |  |

|        | PB3  | SPI1_SCK                                                                                          | LCD_SEG7                                | TIM2_CH2                                                                            | TSC_G5_IO1            | EVENTOUT                                           | USART1_RTS_DE                            | USART5_TX                                                   | -                                 |  |

|        | PB4  | SPI1_MISO                                                                                         | LCD_SEG8                                | TIM3_CH1                                                                            | TSC_G5_IO2            | TIM22_CH1                                          | USART1_CTS                               | USART5_RX                                                   | I2C3_SDA                          |  |

|        | PB5  | SPI1_MOSI                                                                                         | LCD_SEG9                                | LPTIM1_IN1                                                                          | I2C1_SMBA             | TIM3_CH2/<br>TIM22_CH2                             | USART1_CK                                | USART5_CK/<br>USART5_RTS_D<br>E                             | -                                 |  |

|        | PB6  | USART1_TX                                                                                         | I2C1_SCL                                | LPTIM1_ETR                                                                          | TSC_G5_IO3            | -                                                  | -                                        | -                                                           | -                                 |  |

|        | PB7  | USART1_RX                                                                                         | I2C1_SDA                                | LPTIM1_IN2                                                                          | TSC_G5_IO4            | -                                                  | -                                        | USART4_CTS                                                  | -                                 |  |

| Port B | PB8  | -                                                                                                 | LCD_SEG16                               | -                                                                                   | TSC_SYNC              | I2C1_SCL                                           | -                                        | -                                                           | -                                 |  |

| đ      | PB9  | -                                                                                                 | LCD_COM3                                | EVENTOUT                                                                            | -                     | I2C1_SDA                                           | SPI2_NSS/<br>I2S2_WS                     | -                                                           | -                                 |  |

|        | PB10 | -                                                                                                 | LCD_SEG10                               | TIM2_CH3                                                                            | TSC_SYNC              | LPUART1_TX                                         | SPI2_SCK                                 | I2C2_SCL                                                    | LPUART1_RX                        |  |

|        | PB11 | EVENTOUT                                                                                          | LCD_SEG11                               | TIM2_CH4                                                                            | TSC_G6_IO1            | LPUART1_RX                                         | -                                        | I2C2_SDA                                                    | LPUART1_TX                        |  |

|        | PB12 | SPI2_NSS/I2S2_WS                                                                                  | LCD_SEG12                               | LPUART1_RTS_<br>DE                                                                  | TSC_G6_IO2            |                                                    | I2C2_SMBA                                | EVENTOUT                                                    | -                                 |  |

|        | PB13 | SPI2_SCK/I2S2_CK                                                                                  | LCD_SEG13                               | MCO                                                                                 | TSC_G6_IO3            | LPUART1_CTS                                        | I2C2_SCL                                 | TIM21_CH1                                                   | -                                 |  |

|        | PB14 | SPI2_MISO/<br>I2S2_MCK                                                                            | LCD_SEG14                               | RTC_OUT                                                                             | TSC_G6_IO4            | LPUART1_RTS_DE                                     | I2C2_SDA                                 | TIM21_CH2                                                   | -                                 |  |

|        | PB15 | SPI2_MOSI/<br>I2S2_SD                                                                             | LCD_SEG15                               | RTC_REFIN                                                                           | -                     | -                                                  | -                                        | -                                                           | -                                 |  |

# Pin descriptions

STM32L073xx

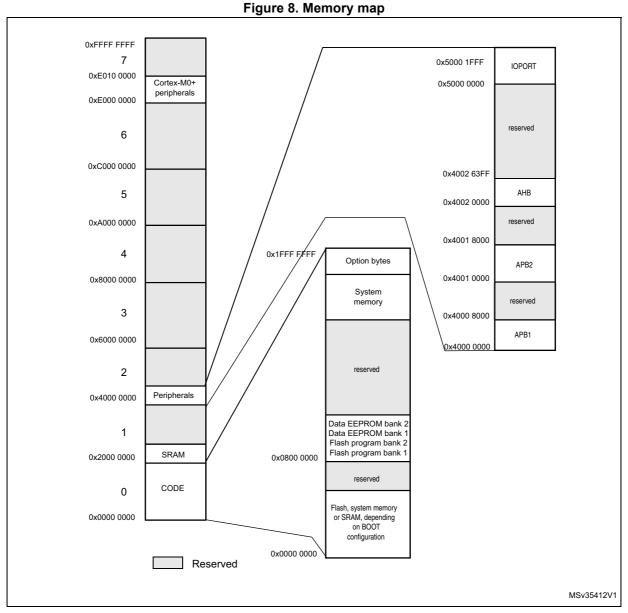

## 5 Memory mapping

1. Refer to the STM32L073xx reference manual for details on the Flash memory organization for each memory size.

### 6.3.2 Embedded reset and power control block characteristics

The parameters given in the following table are derived from the tests performed under the ambient temperature condition summarized in *Table 26*.

| Symbol                          | Parameter                      | Conditions                                          | Min  | Тур  | Мах      | Unit |

|---------------------------------|--------------------------------|-----------------------------------------------------|------|------|----------|------|

|                                 |                                | BOR detector enabled                                | 0    | -    | $\infty$ |      |

| + (1)                           | V <sub>DD</sub> rise time rate | BOR detector disabled                               | 0    | -    | 1000     | μs/V |

| t <sub>VDD</sub> <sup>(1)</sup> | ) ( foll time rate             | BOR detector enabled                                | 20   | -    | x        | μs/v |

|                                 | V <sub>DD</sub> fall time rate | BOR detector disabled                               | 0    | -    | 1000     |      |

| т (1)                           | Reset temporization            | V <sub>DD</sub> rising, BOR enabled                 | -    | 2    | 3.3      | ma   |

| RSTTEMPO <sup>(1)</sup>         | Reset temponzation             | V <sub>DD</sub> rising, BOR disabled <sup>(2)</sup> | 0.4  | 0.7  | 1.6      | ms   |

| M                               | Power on/power down reset      | Falling edge                                        | 1    | 1.5  | 1.65     |      |

| V <sub>POR/PDR</sub>            | threshold                      | Rising edge                                         | 1.3  | 1.5  | 1.65     |      |

|                                 |                                | Falling edge                                        | 1.67 | 1.7  | 1.74     |      |

| V <sub>BOR0</sub>               | Brown-out reset threshold 0    | Rising edge                                         | 1.69 | 1.76 | 1.8      |      |

|                                 | Drewe out react threaded 4     | Falling edge                                        | 1.87 | 1.93 | 1.97     |      |

| V <sub>BOR1</sub>               | Brown-out reset threshold 1    | Rising edge                                         | 1.96 | 2.03 | 2.07     |      |

|                                 | Drewe out react threaded 2     | Falling edge                                        | 2.22 | 2.30 | 2.35     |      |

| V <sub>BOR2</sub>               | Brown-out reset threshold 2    | Rising edge                                         | 2.31 | 2.41 | 2.44     |      |

|                                 |                                | Falling edge                                        | 2.45 | 2.55 | 2.6      |      |

| V <sub>BOR3</sub>               | Brown-out reset threshold 3    | Rising edge                                         | 2.54 | 2.66 | 2.7      |      |

|                                 |                                | Falling edge                                        | 2.68 | 2.8  | 2.85     |      |

| V <sub>BOR4</sub>               | Brown-out reset threshold 4    | Rising edge                                         | 2.78 | 2.9  | 2.95     |      |

|                                 | Programmable voltage detector  | Falling edge                                        | 1.8  | 1.85 | 1.88     | V    |

| V <sub>PVD0</sub>               | threshold 0                    | Rising edge                                         | 1.88 | 1.94 | 1.99     |      |

| M                               | D) (D) there are a lot 4       | Falling edge                                        | 1.98 | 2.04 | 2.09     |      |

| V <sub>PVD1</sub>               | PVD threshold 1                | Rising edge                                         | 2.08 | 2.14 | 2.18     |      |

|                                 | D) (D three held 2             | Falling edge                                        | 2.20 | 2.24 | 2.28     | 1    |

| V <sub>PVD2</sub>               | PVD threshold 2                | Rising edge                                         | 2.28 | 2.34 | 2.38     | 1    |

| N/                              | DVD threehold 2                | Falling edge                                        | 2.39 | 2.44 | 2.48     |      |

| V <sub>PVD3</sub>               | PVD threshold 3                | Rising edge                                         | 2.47 | 2.54 | 2.58     |      |

|                                 | D) (D three held 4             | Falling edge                                        | 2.57 | 2.64 | 2.69     |      |

| V <sub>PVD4</sub>               | PVD threshold 4                | Rising edge                                         | 2.68 | 2.74 | 2.79     |      |

|                                 |                                | Falling edge                                        | 2.77 | 2.83 | 2.88     |      |

| V <sub>PVD5</sub>               | PVD threshold 5                | Rising edge                                         | 2.87 | 2.94 | 2.99     |      |

| Table 27. Embedded reset and power control block characteristics |

|------------------------------------------------------------------|

|------------------------------------------------------------------|

| Symbol                             | parameter                                   | System frequency     | Current<br>consumption<br>during wakeup | Unit |  |

|------------------------------------|---------------------------------------------|----------------------|-----------------------------------------|------|--|

|                                    |                                             | HSI                  | 1                                       |      |  |

|                                    |                                             | HSI/4                | 0,7                                     |      |  |

| I <sub>DD</sub> (Wakeup from Stop) | Supply current during Wakeup from Stop mode | MSI clock = 4,2 MHz  | 0,7                                     |      |  |

| etep)                              |                                             | MSI clock = 1,05 MHz | 0,4                                     |      |  |

|                                    |                                             | MSI clock = 65 KHz   | 0,1                                     | mA   |  |

| I <sub>DD</sub> (Reset)            | Reset pin pulled down                       | -                    | 0,21                                    |      |  |

| I <sub>DD</sub> (Power-up)         | BOR on                                      | -                    | 0,23                                    |      |  |

| I <sub>DD</sub> (Wakeup from       | With Fast wakeup set                        | MSI clock = 2,1 MHz  | 0,5                                     |      |  |

| StandBy)                           | With Fast wakeup disabled                   | MSI clock = 2,1 MHz  | 0,12                                    |      |  |

Table 39. Average current consumption during Wakeup

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                            | Monitored<br>frequency band | Max vs.<br>frequency<br>range at<br>32 MHz | Unit |

|------------------|------------|-------------------------------------------------------|-----------------------------|--------------------------------------------|------|

|                  |            | V                                                     | 0.1 to 30 MHz               | -7                                         |      |

| 6                | Peak level | $V_{DD} = 3.6 \text{ V},$<br>$T_{A} = 25 \text{ °C},$ | 30 to 130 MHz               | 14                                         | dBµV |

| S <sub>EMI</sub> | reak level | LQFP100 package 130 MHz to 1 GHz 9                    | 9                           |                                            |      |

|                  |            | compliant with IEC 61967-2                            | EMI Level                   | 2                                          | -    |

### Table 56. EMI characteristics

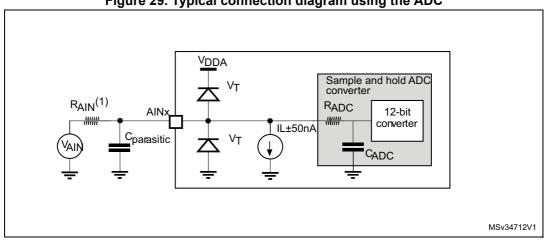

- 1. Refer to Table 64: ADC characteristics for the values of RAIN, RADC and CADC.

- $C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high  $C_{parasitic}$  value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced. 2.

### **General PCB design guidelines**

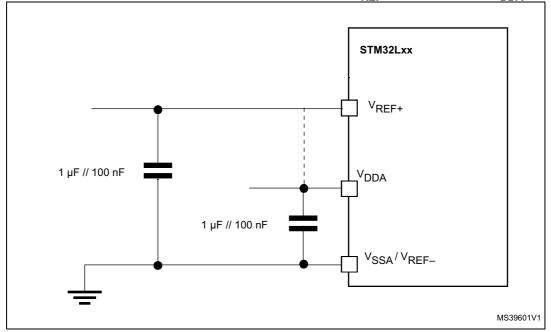

Power supply decoupling should be performed as shown in Figure 30 or Figure 31, depending on whether  $V_{\text{REF+}}$  is connected to  $V_{\text{DDA}}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed as close as possible to the chip.

Figure 30. Power supply and reference decoupling (V<sub>REF+</sub> not connected to V<sub>DDA</sub>)

### **SPI characteristics**

Unless otherwise specified, the parameters given in the following tables are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 26*.

Refer to *Section 6.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                       | Parameter Conditions Min                                            |                                                             | Min     | Тур   | Max               | Unit |  |

|----------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------|---------|-------|-------------------|------|--|

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    |                                                                     | Master mode                                                 |         |       | 16                |      |  |

|                                              |                                                                     | Slave mode<br>receiver                                      | -       | -     | 16                |      |  |

|                                              | SPI clock frequency                                                 | Slave mode<br>Transmitter<br>1.71 <v<sub>DD&lt;3.6V</v<sub> | -       | -     | 12 <sup>(2)</sup> | MHz  |  |

|                                              |                                                                     | Slave mode<br>Transmitter<br>2.7 <v<sub>DD&lt;3.6V</v<sub>  | -       | -     | 16 <sup>(2)</sup> |      |  |

| Duty <sub>(SCK)</sub>                        | Duty cycle of SPI clock<br>frequency                                | Slave mode                                                  | 30      | 50    | 70                | %    |  |

| t <sub>su(NSS)</sub>                         | NSS setup time         Slave mode, SPI<br>presc = 2         4*Tpclk |                                                             | -       | -     |                   |      |  |

| t <sub>h(NSS)</sub>                          | NSS hold time                                                       | Slave mode, SPI<br>presc = 2                                | 2*Tpclk | -     | -                 |      |  |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                                               | Master mode                                                 | Tpclk-2 | Tpclk | Tpclk+<br>2       |      |  |

| t <sub>su(MI)</sub>                          | Data input setup time                                               | Master mode                                                 | 0       | -     | -                 |      |  |

| t <sub>su(SI)</sub>                          |                                                                     | Slave mode                                                  | 3       | -     | -                 |      |  |

| t <sub>h(MI)</sub>                           | Data input hold time                                                | Master mode                                                 | 7       | -     | -                 |      |  |

| t <sub>h(SI)</sub>                           |                                                                     | Slave mode                                                  | 3.5     | -     | -                 | ns   |  |

| t <sub>a(SO</sub>                            | Data output access time                                             | Slave mode                                                  | 15      | -     | 36                |      |  |

| t <sub>dis(SO)</sub>                         | Data output disable time                                            | Slave mode                                                  | 10      | -     | 30                |      |  |

| t <sub>v(SO)</sub>                           |                                                                     | Slave mode<br>1.65 V <v<sub>DD&lt;3.6 V</v<sub>             | -       | 18    | 41                |      |  |

|                                              | Data output valid time                                              | Slave mode<br>2.7 V <v<sub>DD&lt;3.6 V</v<sub>              | -       | 18    | 25                |      |  |

| t <sub>v(MO)</sub>                           |                                                                     | Master mode                                                 | -       | 4     | 7                 |      |  |

| t <sub>h(SO)</sub>                           | Data output hold time                                               | Slave mode                                                  | 10      | -     | -                 |      |  |

| t <sub>h(MO)</sub>                           |                                                                     | Master mode                                                 | 0       | -     | -                 |      |  |

| Table 75. SPI characteristics in | voltage Range 1 <sup>(1)</sup> |

|----------------------------------|--------------------------------|

|----------------------------------|--------------------------------|

1. Guaranteed by characterization results.

2. The maximum SPI clock frequency in slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty<sub>(SCK)</sub> = 50%.

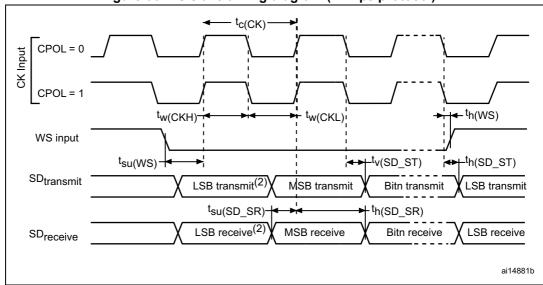

Figure 36. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at CMOS levels:  $0.3 \times V_{DD}$  and  $0.7 \times V_{DD}$ .

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

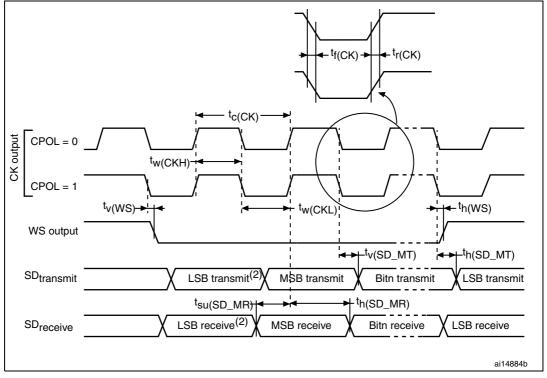

### Figure 37. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Guaranteed by characterization results.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

STM32L073xx

| Symbol                           | Parameter                                                           |      | Тур                  | Max              | Unit |  |

|----------------------------------|---------------------------------------------------------------------|------|----------------------|------------------|------|--|

| I <sub>LCD</sub> <sup>(1)</sup>  | Supply current at $V_{DD}$ = 2.2 V                                  |      | 3.3                  | -                |      |  |

| LCD` ′                           | Supply current at V <sub>DD</sub> = 3.0 V                           | -    | 3.1                  | -                | μA   |  |

| R <sub>Htot</sub> <sup>(2)</sup> | Low drive resistive network overall value                           | 5.28 | 6.6                  | 7.92             | MΩ   |  |

| R <sub>L</sub> <sup>(2)</sup>    | High drive resistive network total value                            | 192  | 240                  | 288              | kΩ   |  |

| V <sub>44</sub>                  | Segment/Common highest level voltage                                | -    | -                    | V <sub>LCD</sub> | V    |  |

| V <sub>34</sub>                  | Segment/Common 3/4 level voltage                                    | -    | 3/4 V <sub>LCD</sub> | -                |      |  |

| V <sub>23</sub>                  | Segment/Common 2/3 level voltage                                    | -    | 2/3 V <sub>LCD</sub> | -                |      |  |

| V <sub>12</sub>                  | Segment/Common 1/2 level voltage                                    | -    | 1/2 V <sub>LCD</sub> | -                | v    |  |

| V <sub>13</sub>                  | Segment/Common 1/3 level voltage                                    | -    | 1/3 V <sub>LCD</sub> | -                | v    |  |

| V <sub>14</sub>                  | Segment/Common 1/4 level voltage                                    | -    | 1/4 V <sub>LCD</sub> | -                |      |  |

| V <sub>0</sub>                   | Segment/Common lowest level voltage                                 | 0    | -                    | -                |      |  |

| $\Delta Vxx^{(3)}$               | Segment/Common level voltage error<br>T <sub>A</sub> = -40 to 85 °C |      | -                    | ± 50             | mV   |  |

| Table 82. LCD controller characteristics (continu | ed) |

|---------------------------------------------------|-----|

|---------------------------------------------------|-----|

LCD enabled with 3 V internal step-up active, 1/8 duty, 1/4 bias, division ratio= 64, all pixels active, no LCD connected.

2. Guaranteed by design.

3. Guaranteed by characterization results.

## 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status *are available at www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

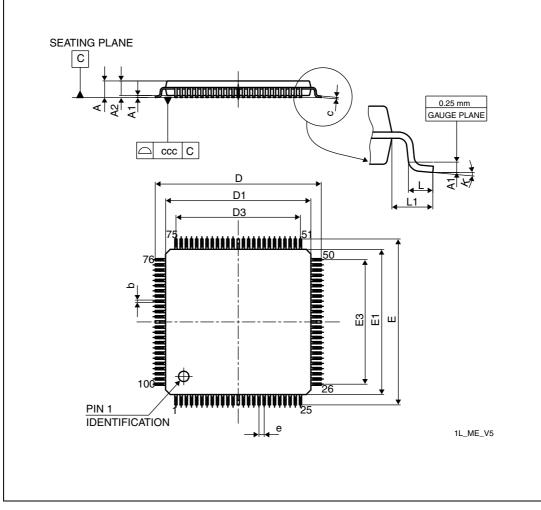

## 7.1 LQFP100 package information

Figure 39. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale. Dimensions are in millimeters.

## Table 84. UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid arraypackage mechanical data (continued)

| Symbol | millimeters |      |       | inches <sup>(1)</sup> |      |        |  |  |  |

|--------|-------------|------|-------|-----------------------|------|--------|--|--|--|

| Symbol | Min.        | Тур. | Max.  | Min.                  | Тур. | Max.   |  |  |  |

| ddd    | -           | -    | 0.080 | -                     | -    | 0.0031 |  |  |  |

| eee    | -           | -    | 0.150 | -                     | -    | 0.0059 |  |  |  |

| fff    | -           | -    | 0.050 | -                     | -    | 0.0020 |  |  |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

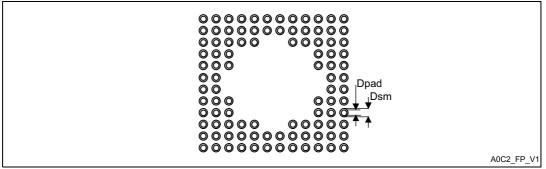

# Figure 43. UFBGA100 - 100-pin, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package recommended footprint

### Table 85. UFBGA100 recommended PCB design rules (0.5 mm pitch BGA)

| Dimension         | Recommended values                                               |  |  |  |  |  |

|-------------------|------------------------------------------------------------------|--|--|--|--|--|

| Pitch             | 0.5                                                              |  |  |  |  |  |

| Dpad              | 0.280 mm                                                         |  |  |  |  |  |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |  |  |  |  |  |

| Stencil opening   | 0.280 mm                                                         |  |  |  |  |  |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |  |  |  |  |  |

## 8 Part numbering

| Table 91. STM32L073xx ord                                   | lering ir | nforn | natio | n sc | her | ne |   |   |      |

|-------------------------------------------------------------|-----------|-------|-------|------|-----|----|---|---|------|

| Example:                                                    | STM3      | 2 L   | 07    | 3    | R   | 8  | т | 6 | D TR |

| Device family                                               |           |       |       |      |     |    |   |   |      |

| STM32 = ARM-based 32-bit microcontroller                    |           |       |       |      |     |    |   |   |      |

| Product type                                                |           |       |       |      |     |    |   |   |      |

| L = Low power                                               |           |       |       |      |     |    |   |   |      |

| Device subfamily                                            |           |       |       |      |     |    |   |   |      |

| 073 = USB + LCD                                             |           |       |       |      |     |    |   |   |      |

| Pin count                                                   |           |       |       |      |     |    |   |   |      |

| C = 48/49 pins                                              |           |       |       |      | 1   |    |   |   |      |

| R = 64 pins                                                 |           |       |       |      |     |    |   |   |      |

| V = 100 pins                                                |           |       |       |      |     |    |   |   |      |

| Flash memory size                                           |           |       |       |      |     |    |   |   |      |

| 8 = 64 Kbytes                                               |           |       |       |      |     |    |   |   |      |

| B = 128 Kbytes                                              |           |       |       |      |     |    |   |   |      |

| Z = 192 Kbytes                                              |           |       |       |      |     |    |   |   |      |

| Package                                                     |           |       |       |      |     |    |   |   |      |

| T = LQFP                                                    |           |       |       |      |     |    |   |   |      |

| H = TFBGA                                                   |           |       |       |      |     |    |   |   |      |

| I = UFBGA                                                   |           |       |       |      |     |    |   |   |      |

| Temperature range                                           |           |       |       |      |     |    |   |   |      |

| 6 = Industrial temperature range, -40 to 85 °C              |           |       |       |      |     |    |   |   |      |

| 7 = Industrial temperature range, -40 to 105 °C             |           |       |       |      |     |    |   |   |      |

| 3 = Industrial temperature range, –40 to 125 $^\circ$ C     |           |       |       |      |     |    |   |   |      |

| Options                                                     |           |       |       |      |     |    |   |   |      |

| No character = $V_{DD}$ range: 1.8 to 3.6 V and BOR enabled |           |       |       |      |     |    |   |   | -    |

| D = $V_{DD}$ range: 1.65 to 3.6 V and BOR disabled          |           |       |       |      |     |    |   |   |      |

| Packing                                                     |           |       |       |      |     |    |   |   |      |

|                                                             |           |       |       |      |     |    |   |   |      |

TR = tape and reel

No character = tray or tube

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.