Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 84                                                                    |

| Program Memory Size        | 192KB (192K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 6K x 8                                                                |

| RAM Size                   | 20K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-UFBGA                                                             |

| Supplier Device Package    | 100-UFBGA (7x7)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l073vzi6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

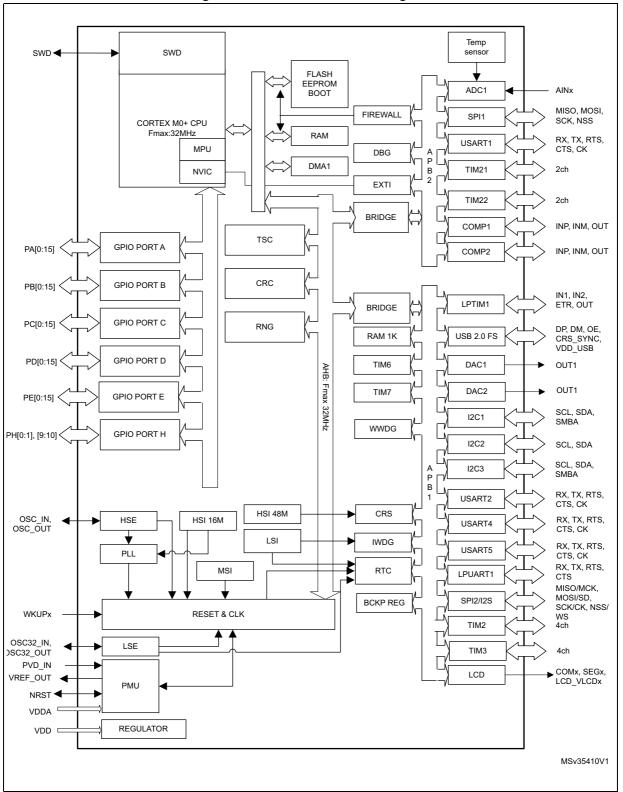

Figure 1. STM32L073xx block diagram

DocID027096 Rev 3

# 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of core and features, from 8-bit proprietary core up to ARM<sup>®</sup> Cortex<sup>®</sup>-M4, including ARM<sup>®</sup> Cortex<sup>®</sup>-M3 and ARM<sup>®</sup> Cortex<sup>®</sup>-M0+. The STM32Lx series are the best choice to answer your needs in terms of ultra-low-power features. The STM32 ultra-low-power series are the best solution for applications such as gaz/water meter, keyboard/mouse or fitness and healthcare application. Several built-in features like LCD drivers, dual-bank memory, low-power run mode, operational amplifiers, 128-bit AES, DAC, crystal-less USB and many other definitely help you building a highly cost optimized application by reducing BOM cost. STMicroelectronics, as a reliable and long-term manufacturer, ensures as much as possible pin-to-pin compatibility between all STM8Lx and STM32Lx on one hand, and between all STM32Lx and STM32Fx on the other hand. Thanks to this unprecedented scalability, your legacy application can be upgraded to respond to the latest market feature and efficiency requirements.

#### • Startup clock

After reset, the microcontroller restarts by default with an internal 2.1 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

### • Clock security system (CSS)

This feature can be enabled by software. If an HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled.

Another clock security system can be enabled, in case of failure of the LSE it provides an interrupt or wakeup event which is generated if enabled.

### • Clock-out capability (MCO: microcontroller clock output)

It outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, each APB (APB1 and APB2) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

# 3.13.2 V<sub>LCD</sub> voltage monitoring

This embedded hardware feature allows the application to measure the V<sub>LCD</sub> supply voltage using the internal ADC channel ADC\_IN16. As the V<sub>LCD</sub> voltage may be higher than V<sub>DDA</sub>, and thus outside the ADC input range, the ADC input is connected to LCD\_VLCD2 (which provides 1/3V<sub>LCD</sub> when the LCD is configured 1/3Bias and 1/4V<sub>LCD</sub> when the LCD is configured 1/4Bias or 1/2Bias).

# 3.14 Digital-to-analog converter (DAC)

Two 12-bit buffered DACs can be used to convert digital signal into analog voltage signal output. An optional amplifier can be used to reduce the output signal impedance.

This digital Interface supports the following features:

- One data holding register (for each channel)

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

- Triangular-wave generation

- Dual DAC channels with independent or simultaneous conversions

- DMA capability (including the underrun interrupt)

- External triggers for conversion

- Input reference voltage V<sub>REF+</sub>

Six DAC trigger inputs are used in the STM32L073xx. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

# 3.15 Ultra-low-power comparators and reference voltage

The STM32L073xx embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- One comparator with ultra low consumption

- One comparator with rail-to-rail inputs, fast or slow mode.

- The threshold can be one of the following:

- DAC output

- External I/O pins

- Internal reference voltage (V<sub>REFINT</sub>)

- submultiple of Internal reference voltage(1/4, 1/2, 3/4) for the rail to rail comparator.

Both comparators can wake up the devices from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low-power / low-current output buffer (driving current capability of 1  $\mu$ A typical).

# 3.16 Touch sensing controller (TSC)

The STM32L073xx provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 24 capacitive sensing channels distributed over 8 analog I/O groups.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (such as glass, plastic). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists of charging the sensor capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. To limit the CPU bandwidth usage, this acquisition is directly managed by the hardware touch sensing controller and only requires few external components to operate.

The touch sensing controller is fully supported by the STMTouch touch sensing firmware library, which is free to use and allows touch sensing functionality to be implemented reliably in the end application.

| Group | Capacitive sensing signal name | Pin<br>name | Group | Capacitive sensing<br>signal name | Pin<br>name |

|-------|--------------------------------|-------------|-------|-----------------------------------|-------------|

|       | TSC_G1_IO1                     | PA0         |       | TSC_G5_IO1                        | PB3         |

| 1     | TSC_G1_IO2                     | PA1         | 5     | TSC_G5_IO2                        | PB4         |

| 1     | TSC_G1_IO3                     | PA2         | 5     | TSC_G5_IO3                        | PB6         |

|       | TSC_G1_IO4                     | PA3         |       | TSC_G5_IO4                        | PB7         |

|       | TSC_G2_IO1                     | PA4         |       | TSC_G6_IO1                        | PB11        |

| 2     | TSC_G2_IO2                     | PA5         | 6     | TSC_G6_IO2                        | PB12        |

| 2     | TSC_G2_IO3                     | PA6         | 0     | TSC_G6_IO3                        | PB13        |

|       | TSC_G2_IO4                     | PA7         |       | TSC_G6_IO4                        | PB14        |

|       | TSC_G3_IO1                     | PC5         |       | TSC_G7_IO1                        | PC0         |

| 3     | TSC_G3_IO2                     | PB0         | 7     | TSC_G7_IO2                        | PC1         |

| 5     | TSC_G3_IO3                     | PB1         | 1     | TSC_G7_IO3                        | PC2         |

|       | TSC_G3_IO4                     | PB2         |       | TSC_G7_IO4                        | PC3         |

|       | TSC_G4_IO1                     | PA9         |       | TSC_G8_IO1                        | PC6         |

| 4     | TSC_G4_IO2                     | PA10        | 8     | TSC_G8_IO2                        | PC7         |

| 4     | TSC_G4_IO3                     | PA11        | 0     | TSC_G8_IO3                        | PC8         |

|       | TSC_G4_IO4                     | PA12        |       | TSC_G8_IO4                        | PC9         |

Table 9. Capacitive sensing GPIOs available on STM32L073xx devices

# 3.18.2 Universal synchronous/asynchronous receiver transmitter (USART)

The four USART interfaces (USART1, USART2, USART4 and USART5) are able to communicate at speeds of up to 4 Mbit/s.

They provide hardware management of the CTS, RTS and RS485 driver enable (DE) signals, multiprocessor communication mode, master synchronous communication and single-wire half-duplex communication mode. USART1 and USART2 also support SmartCard communication (ISO 7816), IrDA SIR ENDEC, LIN Master/Slave capability, auto baud rate feature and has a clock domain independent from the CPU clock, allowing to wake up the MCU from Stop mode using baudrates up to 42 Kbaud.

All USART interfaces can be served by the DMA controller.

Table 13 for the supported modes and features of USART interfaces.

| USART modes/features <sup>(1)</sup>         | USART1 and USART2 | USART4 and USART5 |

|---------------------------------------------|-------------------|-------------------|

| Hardware flow control for modem             | Х                 | Х                 |

| Continuous communication using DMA          | Х                 | Х                 |

| Multiprocessor communication                | Х                 | Х                 |

| Synchronous mode <sup>(2)</sup>             | Х                 | Х                 |

| Smartcard mode                              | Х                 | -                 |

| Single-wire half-duplex communication       | Х                 | Х                 |

| IrDA SIR ENDEC block                        | Х                 | -                 |

| LIN mode                                    | Х                 | -                 |

| Dual clock domain and wakeup from Stop mode | Х                 | -                 |

| Receiver timeout interrupt                  | Х                 | -                 |

| Modbus communication                        | Х                 | -                 |

| Auto baud rate detection (4 modes)          | Х                 | -                 |

| Driver Enable                               | Х                 | Х                 |

Table 13. USART implementation

1. X = supported.

2. This mode allows using the USART as an SPI master.

# 3.18.3 Low-power universal asynchronous receiver transmitter (LPUART)

The devices embed one Low-power UART. The LPUART supports asynchronous serial communication with minimum power consumption. It supports half duplex single wire communication and modem operations (CTS/RTS). It allows multiprocessor communication.

The LPUART has a clock domain independent from the CPU clock. It can wake up the system from Stop mode using baudrates up to 46 Kbaud. The Wakeup events from Stop mode are programmable and can be:

- Start bit detection

- Or any received data frame

- Or a specific programmed data frame

|   | i igule c                  |        |       |       |        | Danou  | l - JX J |        |

|---|----------------------------|--------|-------|-------|--------|--------|----------|--------|

|   | 1                          | 2      | 3     | 4     | 5      | 6      | 7        | 8      |

| A | ₽°C14-<br>OSC32<br>`_41¥   | (PC13) | (PB9) | (PB4) | (PB3)  | (PA15) | (PA14)   | (PA13) |

| В | アCT5-<br>OSC32<br>OUオ      | (VLCD) | (PB8) |       | (PD2)  | (PC11) | (PC10)   | (PA12) |

| С | (PHO-)<br>osc_IN           | (vss)  | (PB7) | (PB5) | (PC12) | (PA10) | (PA9)    | (PA11) |

| D | ( 0SC )<br>( 0SC )<br>\QUT |        | (PB6) | (vss) | (vss)  | (vss)  | (PA8)    | (PC9)  |

| E |                            | (PC1)  | (PC0) | (VDD) | (VDD)  |        | (PC7)    | (PC8)  |

| F | (VSSA)                     | (PC2)  | (PA2) | (PA5) | (PB0)  | (PC6)  | (PB15)   | (PB14) |

| G |                            | (PA0)  | (PA3) | (PA6) | (PB1)  | (PB2)  | (PB10)   | (PB13) |

| Н | (VDDA)                     | (PA1)  | (PA4) | (PA7) | (PC4)  | (PC5)  | (PB11)   | (PB12) |

|   | L                          |        |       |       |        |        |          |        |

Figure 6. STM32L073xx TFBGA64 ballout - 5x 5 mm

1. The above figure shows the package top view.

2. I/O pin supplied by VDD\_USB.

|        |      |                                                                                                   |                                     | Table 21.                                                                           | Alternate fur         | nctions port E                                     |                                              |                                                             |                               |

|--------|------|---------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------|----------------------------------------------|-------------------------------------------------------------|-------------------------------|

|        |      | AF0                                                                                               | AF1                                 | AF2                                                                                 | AF3                   | AF4                                                | AF5                                          | AF6                                                         | AF7                           |

| Port   |      | SPI1/SPI2/I2S2/<br>USART1/2/<br>LPUART1/USB/<br>LPTIM1/TSC/<br>TIM2/21/22/<br>EVENTOUT/<br>SYS_AF | SPI1/SPI2/I2S2/I2C1<br>/LCD/TIM2/21 | SPI1/SPI2/I2S2/<br>LPUART1/<br>USART5/USB/<br>LPTIM1/TIM2/3<br>/EVENTOUT/<br>SYS_AF | I2C1/TSC/<br>EVENTOUT | I2C1/USART1/2/<br>LPUART1/<br>TIM3/22/<br>EVENTOUT | SPI2/I2S2<br>/I2C2/<br>USART1/<br>TIM2/21/22 | I2C1/2/<br>LPUART1/<br>USART4/<br>UASRT5/TIM21/<br>EVENTOUT | I2C3/LPUART1/<br>COMP1/2/TIM3 |

|        | PE0  | -                                                                                                 | LCD_SEG36                           | EVENTOUT                                                                            | -                     | -                                                  | -                                            | -                                                           | -                             |

|        | PE1  | -                                                                                                 | LCD_SEG37                           | EVENTOUT                                                                            | -                     | -                                                  | -                                            | -                                                           | -                             |

|        | PE2  | -                                                                                                 | LCD_SEG38                           | TIM3_ETR                                                                            | -                     | -                                                  | -                                            | -                                                           | -                             |

|        | PE3  | TIM22_CH1                                                                                         | LCD_SEG39                           | TIM3_CH1                                                                            | -                     | -                                                  | -                                            | -                                                           | -                             |

|        | PE4  | TIM22_CH2                                                                                         | -                                   | TIM3_CH2                                                                            | -                     | -                                                  | -                                            | -                                                           | -                             |

|        | PE5  | TIM21_CH1                                                                                         | -                                   | TIM3_CH3                                                                            | -                     | -                                                  | -                                            | -                                                           | -                             |

|        | PE6  | TIM21_CH2                                                                                         | -                                   | TIM3_CH4                                                                            | -                     | -                                                  | -                                            | -                                                           | -                             |

| Port E | PE7  | -                                                                                                 | LCD_SEG45                           | -                                                                                   | -                     | -                                                  | -                                            | USART5_CK/U<br>SART5_RTS_D<br>E                             | -                             |

| ш      | PE8  | -                                                                                                 | LCD_SEG46                           | -                                                                                   | -                     | -                                                  | -                                            | USART4_TX                                                   | -                             |

|        | PE9  | TIM2_CH1                                                                                          | LCD_SEG47                           | TIM2_ETR                                                                            | -                     | -                                                  | -                                            | USART4_RX                                                   | -                             |

|        | PE10 | TIM2_CH2                                                                                          | LCD_SEG40                           | -                                                                                   | -                     | -                                                  | -                                            | USART5_TX                                                   | -                             |

|        | PE11 | TIM2_CH3                                                                                          | -                                   | -                                                                                   | -                     | -                                                  | -                                            | USART5_RX                                                   | -                             |

|        | PE12 | TIM2_CH4                                                                                          | -                                   | SPI1_NSS                                                                            | -                     | -                                                  | -                                            | -                                                           | -                             |

|        | PE13 | -                                                                                                 | LCD_SEG41                           | SPI1_SCK                                                                            | -                     | -                                                  | -                                            | -                                                           | -                             |

|        | PE14 | -                                                                                                 | LCD_SEG42                           | SPI1_MISO                                                                           | -                     | -                                                  | -                                            | -                                                           | -                             |

|        | PE15 | -                                                                                                 | LCD_SEG43                           | SPI1_MOSI                                                                           | -                     | -                                                  | -                                            | -                                                           | -                             |

# DocID027096 Rev 3

54/139

STM32L073xx

Pin descriptions

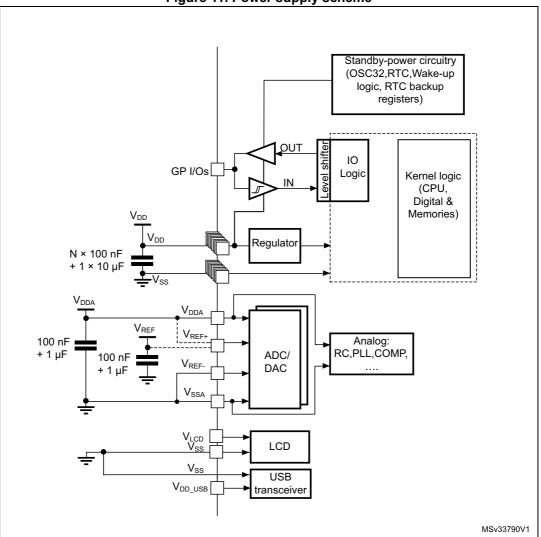

# 6.1.6 Power supply scheme

#### Figure 11. Power supply scheme

# 6.3 **Operating conditions**

# 6.3.1 General operating conditions

# Table 26. General operating conditions

| Symbol             | Parameter                                                                                                | Conditions                                 | Min  | Max                  | Unit  |  |

|--------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------|------|----------------------|-------|--|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                                                                             | -                                          | 0    | 32                   |       |  |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                                                                            | -                                          | 0    | 32                   | MHz   |  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency                                                                            | -                                          | 0    | 32                   |       |  |

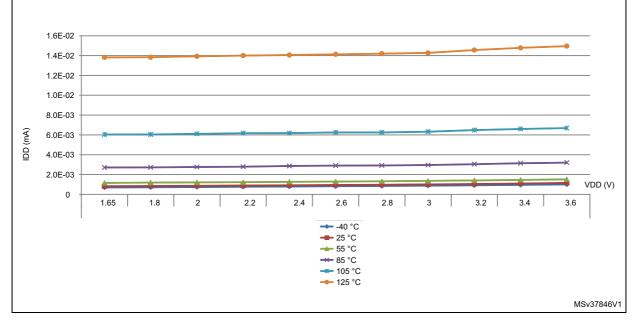

|                    |                                                                                                          | BOR detector disabled                      | 1.65 | 3.6                  |       |  |

| V <sub>DD</sub>    | Standard operating voltage                                                                               | BOR detector enabled, at power on          | 1.8  | 3.6                  | v     |  |

|                    |                                                                                                          | BOR detector disabled, after power on      | 1.65 | 3.6                  |       |  |

| V <sub>DDA</sub>   | Analog operating voltage (DAC not used)                                                                  | Must be the same voltage as $V_{DD}^{(1)}$ | 1.65 | 3.6                  | V     |  |

| V <sub>DDA</sub>   | Analog operating voltage (all features)                                                                  | Must be the same voltage as $V_{DD}^{(1)}$ | 1.8  | 3.6                  | V     |  |

| V <sub>DD_US</sub> | Standard operating voltage, USB                                                                          | USB peripheral used                        | 3.0  | 3.6                  | - V   |  |

| В                  | domain <sup>(2)</sup>                                                                                    | USB peripheral not used                    | 1.65 | 3.6                  |       |  |

|                    | Input voltage on FT, FTf and RST pins <sup>(3)</sup>                                                     | $2.0~V \leq V_{DD} \leq 3.6~V$             | -0.3 | 5.5                  |       |  |

| V                  |                                                                                                          | $1.65~V \leq V_{DD} \leq 2.0~V$            | -0.3 | 5.2                  | v     |  |

| V <sub>IN</sub>    | Input voltage on BOOT0 pin                                                                               | -                                          | 0    | 5.5                  | v     |  |

|                    | Input voltage on TC pin                                                                                  | -                                          | -0.3 | V <sub>DD</sub> +0.3 |       |  |

|                    |                                                                                                          | UFBGA100 package                           | -    | 351                  |       |  |

|                    |                                                                                                          | LQFP100 package                            | -    | 488                  |       |  |

|                    | Power dissipation at $T_A = 85 \degree C$ (range 6)<br>or $T_A = 105 \degree C$ (range 7) <sup>(4)</sup> | TFBGA64 package                            | -    | 313                  |       |  |

|                    |                                                                                                          | LQFP64 package                             | -    | 435                  |       |  |

| PD                 |                                                                                                          | LQFP48 package                             | -    | 370                  | mW    |  |

| ГD                 |                                                                                                          | UFBGA100 package                           | -    | 88                   | 11100 |  |

|                    |                                                                                                          | LQFP100 package                            | -    | 122                  |       |  |

|                    | Power dissipation at $T_A = 125 \degree C$ (range 3) <sup>(4)</sup>                                      | TFBGA64 package                            | -    | 78                   |       |  |

|                    |                                                                                                          | LQFP64 package                             | -    | 109                  |       |  |

|                    |                                                                                                          | LQFP48 package                             | -    | 93                   |       |  |

| Symbol                 | Parameter                   | Conditions                                   | Тур   | Max <sup>(1)</sup> | Unit |  |  |  |

|------------------------|-----------------------------|----------------------------------------------|-------|--------------------|------|--|--|--|

|                        | Supply current in Stop mode | $T_{A} = -40 \text{ to } 25^{\circ}\text{C}$ | 0,43  | 1,00               |      |  |  |  |

|                        |                             | T <sub>A</sub> = 55°C                        | 0,735 | 2,50               | μA   |  |  |  |

| I <sub>DD</sub> (Stop) |                             | T <sub>A</sub> = 85°C                        | 2,25  | 4,90               |      |  |  |  |

|                        |                             | T <sub>A</sub> = 105°C                       | 5,3   | 13,00              |      |  |  |  |

|                        |                             | T <sub>A</sub> = 125°C                       | 12,5  | 28,00              |      |  |  |  |

Table 37. Typical and maximum current consumptions in Stop mode

1. Guaranteed by characterization results at 125  $^\circ\text{C},$  unless otherwise specified.

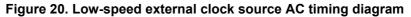

## Low-speed external user clock generated from an external source

The characteristics given in the following table result from tests performed using a lowspeed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 26*.

| Symbol                                     | Parameter                               | Conditions                       | Min                | Тур    | Max                | Unit |

|--------------------------------------------|-----------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User external clock source<br>frequency |                                  | 1                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage   |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | v    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage    | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSE)</sub><br>t <sub>w(LSE)</sub> | OSC32_IN high or low time               |                                  | 465                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time              |                                  | -                  | -      | 10                 | 115  |

| C <sub>IN(LSE)</sub>                       | OSC32_IN input capacitance              | -                                | -                  | 0.6    | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                              | -                                | 45                 | -      | 55                 | %    |

| ١L                                         | OSC32_IN Input leakage current          | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |

Table 44. Low-speed external user clock characteristics<sup>(1)</sup>

1. Guaranteed by design, not tested in production

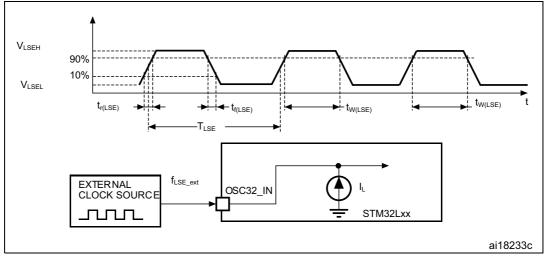

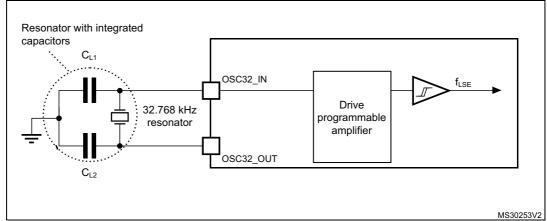

### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 46*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                                 | Conditions <sup>(2)</sup>                                         | Min <sup>(2)</sup> | Тур    | Max  | Unit |

|-------------------------------------|-------------------------------------------|-------------------------------------------------------------------|--------------------|--------|------|------|

| f <sub>LSE</sub>                    | LSE oscillator frequency                  |                                                                   | -                  | 32.768 | -    | kHz  |

| G <sub>m</sub>                      |                                           | LSEDRV[1:0]=00<br>lower driving capability                        | -                  | -      | 0.5  |      |

|                                     | Maximum critical crystal transconductance | LSEDRV[1:0]= 01<br>critical crystal medium low driving capability |                    | -      | 0.75 | uA/V |

|                                     |                                           | LSEDRV[1:0] = 10<br>medium high driving capability                | -                  | -      | 1.7  | μΑνν |

|                                     |                                           | LSEDRV[1:0]=11<br>higher driving capability                       | -                  | -      | 2.7  |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time                              | V <sub>DD</sub> is stabilized                                     | -                  | 2      | -    | S    |

| Table 46. LSE oscillator cha | racteristics <sup>(1)</sup> |

|------------------------------|-----------------------------|

|------------------------------|-----------------------------|

1. Guaranteed by design.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

3. Guaranteed by characterization results. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer. To increase speed, address a lower-drive quartz with a high- driver mode.

# *Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Note:

An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

| Symbol                          | Parameter                                                                         | Conditions                 | Value              | Unit  |

|---------------------------------|-----------------------------------------------------------------------------------|----------------------------|--------------------|-------|

| Symbol                          | Farameter                                                                         | Conditions                 | Min <sup>(1)</sup> | Unit  |

|                                 | Data retention (program memory) after<br>10 kcycles at T <sub>A</sub> = 85 °C     | T <sub>RFT</sub> = +85 °C  | 30                 |       |

|                                 | Data retention (EEPROM data memory) after 100 kcycles at $T_A = 85 \text{ °C}$    | 1 <sub>RET</sub> - +65 C   | 30                 |       |

| t <sub>RET</sub> <sup>(2)</sup> | Data retention (program memory) after 10 kcycles at $T_A$ = 105 °C                | T <sub>RFT</sub> = +105 °C | 10                 |       |

| 'RET`                           | Data retention (EEPROM data memory) after 100 kcycles at $T_A = 105$ °C           | TRET - FIUS C              |                    | years |

|                                 | Data retention (program memory) after<br>200 cycles at T <sub>A</sub> = 125 °C    | T - +125 °C                | 10                 |       |

|                                 | Data retention (EEPROM data memory)<br>after 2 kcycles at T <sub>A</sub> = 125 °C | T <sub>RET</sub> = +125 °C |                    |       |

Table 54. Flash memory and data EEPROM endurance and retention (continued)

1. Guaranteed by characterization results.

2. Characterization is done according to JEDEC JESD22-A117.

# 6.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

## Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- **Electrostatic discharge (ESD)** (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 55*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                                                   | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD} = 3.3 \text{ V}, \text{ LQFP100}, \text{ T}_{\text{A}} = +25 \text{ °C},$<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-2 | 3B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3$ V, LQFP100, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-4                               | 4A              |

#### Table 55. EMS characteristics

| Symbol                                       | Parameter                            | Parameter Conditions                                     |         | Тур   | Max              | Unit |

|----------------------------------------------|--------------------------------------|----------------------------------------------------------|---------|-------|------------------|------|

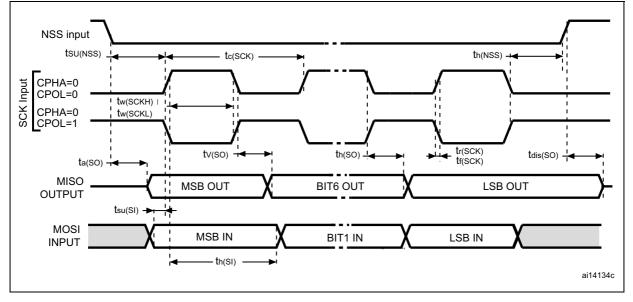

|                                              |                                      | Master mode                                              |         |       | 8                |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency                  | Slave mode Transmitter<br>1.65 <v<sub>DD&lt;3.6V</v<sub> | -       | -     | 8                | MHz  |

| -C(SCR)                                      |                                      | Slave mode Transmitter<br>2.7 <v<sub>DD&lt;3.6V</v<sub>  |         |       | 8 <sup>(2)</sup> |      |

| Duty <sub>(SCK)</sub>                        | Duty cycle of SPI clock<br>frequency | Slave mode                                               | 30      | 50    | 70               | %    |

| t <sub>su(NSS)</sub>                         | NSS setup time                       | Slave mode, SPI presc = 2                                | 4*Tpclk | -     | -                |      |

| t <sub>h(NSS)</sub>                          | NSS hold time                        | Slave mode, SPI presc = 2                                | 2*Tpclk | -     | -                |      |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                | Master mode                                              | Tpclk-2 | Tpclk | Tpclk+2          |      |

| t <sub>su(MI)</sub>                          | Data input setup time                | Master mode                                              | 0       | -     | -                |      |

| t <sub>su(SI)</sub>                          | Data input setup time                | Slave mode                                               | 3       | -     | -                |      |

| t <sub>h(MI)</sub>                           | Data input hold time                 | Master mode                                              | 11      | -     | -                |      |

| t <sub>h(SI)</sub>                           |                                      | Slave mode                                               | 4.5     | -     | -                | ns   |

| t <sub>a(SO</sub>                            | Data output access time              | Slave mode                                               | 18      | -     | 52               |      |

| t <sub>dis(SO)</sub>                         | Data output disable time             | Slave mode                                               | 12      | -     | 42               |      |

| t <sub>v(SO)</sub>                           | Data output valid time               | Slave mode                                               | -       | 20    | 56.5             |      |

| t <sub>v(MO)</sub>                           |                                      | Master mode                                              | -       | 5     | 9                |      |

| t <sub>h(SO)</sub>                           | Data output hold time                | Slave mode                                               | 13      | -     | -                |      |

| t <sub>h(MO)</sub>                           |                                      | Master mode                                              | 3       | -     | -                |      |

| Table 76. SPI characteristics in | n voltage | Range 2 <sup>(1)</sup> |

|----------------------------------|-----------|------------------------|

|----------------------------------|-----------|------------------------|

1. Guaranteed by characterization results.

2. The maximum SPI clock frequency in slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty<sub>(SCK)</sub> = 50%.

| Symbol                                       | Parameter                            | Conditions                | Min     | Тур   | Max              | Unit  |

|----------------------------------------------|--------------------------------------|---------------------------|---------|-------|------------------|-------|

| f <sub>SCK</sub>                             | SDI alaak fraguanay                  | Master mode               |         |       | 2                | MHz   |

| 1/t <sub>c(SCK)</sub>                        | SPI clock frequency                  | Slave mode                | -       | -     | 2 <sup>(2)</sup> | IVILL |

| Duty <sub>(SCK)</sub>                        | Duty cycle of SPI clock<br>frequency | Slave mode                | 30      | 50    | 70               | %     |

| t <sub>su(NSS)</sub>                         | NSS setup time                       | Slave mode, SPI presc = 2 | 4*Tpclk | -     | -                |       |

| t <sub>h(NSS)</sub>                          | NSS hold time                        | Slave mode, SPI presc = 2 | 2*Tpclk | -     | -                |       |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                | Master mode               | Tpclk-2 | Tpclk | Tpclk+2          |       |

| t <sub>su(MI)</sub>                          | Data input setup time                | Master mode               | 1.5     | -     | -                |       |

| t <sub>su(SI)</sub>                          | Data input setup time                | Slave mode                | 6       | -     | -                |       |

| t <sub>h(MI)</sub>                           | Data input hold time                 | Master mode               | 13.5    | -     | -                |       |

| t <sub>h(SI)</sub>                           |                                      | Slave mode                | 16      | -     | -                | ns    |

| t <sub>a(SO</sub>                            | Data output access time              | Slave mode                | 30      | -     | 70               |       |

| t <sub>dis(SO)</sub>                         | Data output disable time             | Slave mode                | 40      | -     | 80               |       |

| t <sub>v(SO)</sub>                           | Data output valid time               | Slave mode                | -       | 30    | 70               |       |

| t <sub>v(MO)</sub>                           |                                      | Master mode               | -       | 7     | 9                |       |

| t <sub>h(SO)</sub>                           | Data output hold time                | Slave mode                | 25      | -     | -                |       |

| t <sub>h(MO)</sub>                           | Data output hold time                | Master mode               | 8       | -     | -                |       |

| Table 77. SPI characteristics in voltage F | Range 3 <sup>(1)</sup> |

|--------------------------------------------|------------------------|

|--------------------------------------------|------------------------|

1. Guaranteed by characterization results.

2. The maximum SPI clock frequency in slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty<sub>(SCK)</sub> = 50%.

Figure 33. SPI timing diagram - slave mode and CPHA = 0

DocID027096 Rev 3

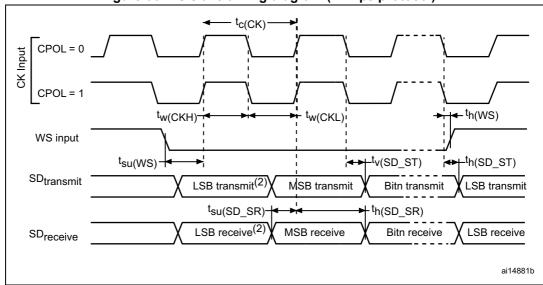

Figure 36. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at CMOS levels:  $0.3 \times V_{DD}$  and  $0.7 \times V_{DD}$ .

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

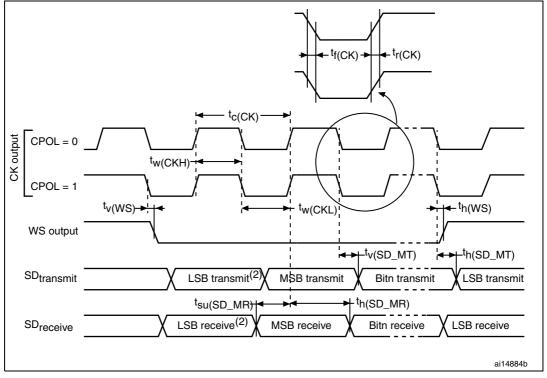

## Figure 37. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Guaranteed by characterization results.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

STM32L073xx

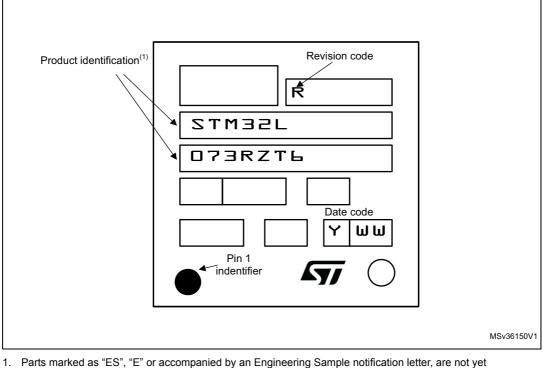

## **Device marking for LQFP64**

The following figure gives an example of topside marking versus pin 1 position identifier location.

I. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

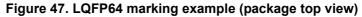

# 7.4 **TFBGA64** package information

Figure 48. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch thin profile fine pitch ball grid array package outline

1. Drawing is not to scale.

| Table 87. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball |

|-----------------------------------------------------------------------------------|

| grid array package mechanical data                                                |

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min   | Тур         | Мах   | Min    | Тур                   | Max    |

| А      | -     | -           | 1.200 | -      | -                     | 0.0472 |

| A1     | 0.150 | -           | -     | 0.0059 | -                     | -      |

| A2     | -     | 0.200       | -     | -      | 0.0079                | -      |

| A4     | -     | -           | 0.600 | -      | -                     | 0.0236 |

| b      | 0.250 | 0.300       | 0.350 | 0.0098 | 0.0118                | 0.0138 |

| D      | 4.850 | 5.000       | 5.150 | 0.1909 | 0.1969                | 0.2028 |

| D1     | -     | 3.500       | -     | -      | 0.1378                | -      |

| E      | 4.850 | 5.000       | 5.150 | 0.1909 | 0.1969                | 0.2028 |

| E1     | -     | 3.500       | -     | -      | 0.1378                | -      |

# Table 87. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ballgrid array package mechanical data (continued)

| Symbol |     | millimeters |       |     | inches <sup>(1)</sup> |        |

|--------|-----|-------------|-------|-----|-----------------------|--------|

| Symbol | Min | Тур         | Мах   | Min | Тур                   | Мах    |

| е      | -   | 0.500       | -     | -   | 0.0197                | -      |

| F      | -   | 0.750       | -     | -   | 0.0295                | -      |

| ddd    | -   | -           | 0.080 | -   | -                     | 0.0031 |

| eee    | -   | -           | 0.150 | -   | -                     | 0.0059 |

| fff    | -   | -           | 0.050 | -   | -                     | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

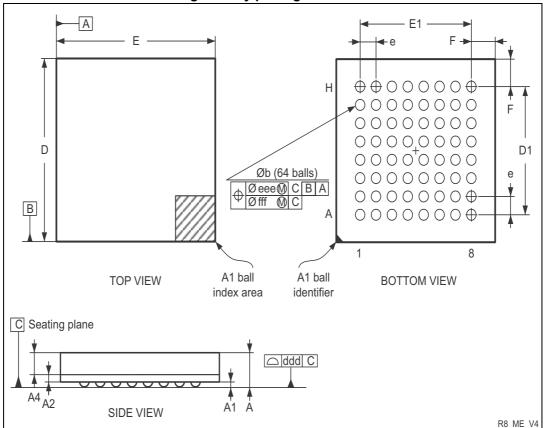

# Figure 49. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball ,grid array recommended footprint

### Table 88. TFBGA64 recommended PCB design rules (0.5 mm pitch BGA)

| Dimension    | Recommended values                                              |

|--------------|-----------------------------------------------------------------|

| Pitch        | 0.5                                                             |

| Dpad         | 0.27 mm                                                         |

| Dsm          | 0.35 mm typ. (depends on the soldermask registration tolerance) |

| Solder paste | 0.27 mm aperture diameter.                                      |

Note:Non solder mask defined (NSMD) pads are recommended.4 to 6 mils solder paste screen printing process.