Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                        |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT       |

| Number of I/O              | 84                                                                      |

| Program Memory Size        | 192KB (192K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 6K x 8                                                                  |

| RAM Size                   | 20K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-UFBGA                                                               |

| Supplier Device Package    | 100-UFBGA (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l073vzi6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Intro | duction                                                     |

|---|-------|-------------------------------------------------------------|

| 2 | Desc  | ription                                                     |

|   | 2.1   | Device overview                                             |

|   | 2.2   | Ultra-low-power device continuum                            |

| 3 | Func  | tional overview                                             |

|   | 3.1   | Low-power modes                                             |

|   | 3.2   | Interconnect matrix                                         |

|   | 3.3   | ARM® Cortex®-M0+ core with MPU 20                           |

|   | 3.4   | Reset and supply management                                 |

|   |       | 3.4.1 Power supply schemes                                  |

|   |       | 3.4.2 Power supply supervisor                               |

|   |       | 3.4.3 Voltage regulator                                     |

|   | 3.5   | Clock management                                            |

|   | 3.6   | Low-power real-time clock and backup registers              |

|   | 3.7   | General-purpose inputs/outputs (GPIOs) 25                   |

|   | 3.8   | Memories                                                    |

|   | 3.9   | Boot modes                                                  |

|   | 3.10  | Direct memory access (DMA) 27                               |

|   | 3.11  | Liquid crystal display (LCD) 27                             |

|   | 3.12  | Analog-to-digital converter (ADC) 27                        |

|   | 3.13  | Temperature sensor                                          |

|   |       | 3.13.1 Internal voltage reference (V <sub>REFINT</sub> )    |

|   |       | 3.13.2 V <sub>LCD</sub> voltage monitoring                  |

|   | 3.14  | Digital-to-analog converter (DAC) 29                        |

|   | 3.15  | Ultra-low-power comparators and reference voltage           |

|   | 3.16  | Touch sensing controller (TSC)                              |

|   | 3.17  | Timers and watchdogs                                        |

|   |       | 3.17.1 General-purpose timers (TIM2, TIM3, TIM21 and TIM22) |

|   |       | 3.17.2 Low-power Timer (LPTIM)                              |

|   |       | 3.17.3 Basic timer (TIM6, TIM7)                             |

DocID027096 Rev 3

## 3.4 Reset and supply management

#### 3.4.1 **Power supply schemes**

- V<sub>DD</sub> = 1.65 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.65 to 3.6 V: external analog power supplies for ADC reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>DD\_USB</sub> = 1.65 to 3.6V: external power supply for USB transceiver, USB\_DM (PA11) and USB\_DP (PA12). To guarantee a correct voltage level for USB communication V<sub>DD\_USB</sub> must be above 3.0V. If USB is not used this pin must be tied to V<sub>DD</sub>.

#### 3.4.2 Power supply supervisor

The devices have an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR) that can be coupled with a brownout reset (BOR) circuitry.

Two versions are available:

- The version with BOR activated at power-on operates between 1.8 V and 3.6 V.

- The other version without BOR operates between 1.65 V and 3.6 V.

After the  $V_{DD}$  threshold is reached (1.65 V or 1.8 V depending on the BOR which is active or not at power-on), the option byte loading process starts, either to confirm or modify default thresholds, or to disable the BOR permanently: in this case, the VDD min value becomes 1.65 V (whatever the version, BOR active or not, at power-on).

When BOR is active at power-on, it ensures proper operation starting from 1.8 V whatever the power ramp-up phase before it reaches 1.8 V. When BOR is not active at power-up, the power ramp-up should guarantee that 1.65 V is reached on  $V_{DD}$  at least 1 ms after it exits the POR area.

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

Note: The start-up time at power-on is typically 3.3 ms when BOR is active at power-up, the startup time at power-on can be decreased down to 1 ms typically for devices with BOR inactive at power-up.

The devices feature an embedded programmable voltage detector (PVD) that monitors the  $V_{DD/VDDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD/VDDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD/VDDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

## 3.13.2 V<sub>LCD</sub> voltage monitoring

This embedded hardware feature allows the application to measure the V<sub>LCD</sub> supply voltage using the internal ADC channel ADC\_IN16. As the V<sub>LCD</sub> voltage may be higher than V<sub>DDA</sub>, and thus outside the ADC input range, the ADC input is connected to LCD\_VLCD2 (which provides 1/3V<sub>LCD</sub> when the LCD is configured 1/3Bias and 1/4V<sub>LCD</sub> when the LCD is configured 1/4Bias or 1/2Bias).

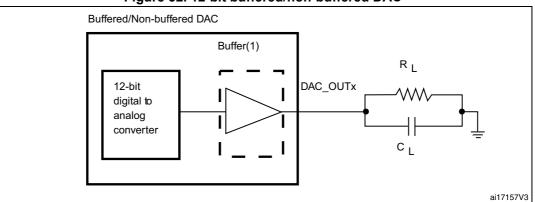

## 3.14 Digital-to-analog converter (DAC)

Two 12-bit buffered DACs can be used to convert digital signal into analog voltage signal output. An optional amplifier can be used to reduce the output signal impedance.

This digital Interface supports the following features:

- One data holding register (for each channel)

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

- Triangular-wave generation

- Dual DAC channels with independent or simultaneous conversions

- DMA capability (including the underrun interrupt)

- External triggers for conversion

- Input reference voltage V<sub>REF+</sub>

Six DAC trigger inputs are used in the STM32L073xx. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

## 3.15 Ultra-low-power comparators and reference voltage

The STM32L073xx embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- One comparator with ultra low consumption

- One comparator with rail-to-rail inputs, fast or slow mode.

- The threshold can be one of the following:

- DAC output

- External I/O pins

- Internal reference voltage (V<sub>REFINT</sub>)

- submultiple of Internal reference voltage(1/4, 1/2, 3/4) for the rail to rail comparator.

Both comparators can wake up the devices from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low-power / low-current output buffer (driving current capability of 1  $\mu$ A typical).

Only a 32.768 kHz clock (LSE) is needed to allow LPUART communication up to 9600 baud. Therefore, even in Stop mode, the LPUART can wait for an incoming frame while having an extremely low energy consumption. Higher speed clock can be used to reach higher baudrates.

LPUART interface can be served by the DMA controller.

#### 3.18.4 Serial peripheral interface (SPI)/Inter-integrated sound (I2S)

Up to two SPIs are able to communicate at up to 16 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

The USARTs with synchronous capability can also be used as SPI master.

One standard I2S interfaces (multiplexed with SPI2) is available. It can operate in master or slave mode, and can be configured to operate with a 16-/32-bit resolution as input or output channels. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When the I2S interfaces is configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

The SPIs can be served by the DMA controller.

Refer to *Table 14* for the differences between SPI1 and SPI2.

| SPI features <sup>(1)</sup> | SPI1 | SPI2 |

|-----------------------------|------|------|

| Hardware CRC calculation    | Х    | Х    |

| I2S mode                    | -    | Х    |

| TI mode                     | Х    | Х    |

Table 14. SPI/I2S implementation

1. X = supported.

#### 3.18.5 Universal serial bus (USB)

The STM32L073xx embeds a full-speed USB device peripheral compliant with the USB specification version 2.0. The internal USB PHY supports USB FS signaling, embedded DP pull-up and also battery charging detection according to Battery Charging Specification Revision 1.2. The USB interface implements a full-speed (12 Mbit/s) function interface with added support for USB 2.0 Link Power Management. It has software-configurable endpoint setting with packet memory up to 1 KB and suspend/resume support. It requires a precise 48 MHz clock which can be generated from the internal main PLL (the clock source must use a HSE crystal oscillator) or by the internal 48 MHz oscillator in automatic trimming mode. The synchronization for this oscillator can be taken from the USB data stream itself (SOF signalization) which allows crystal-less operation.

| _    | 1                                  | 2 3                      | 4          | 5      | 6      | 7      | 8      | 9      | 10           | 11          | 12               |

|------|------------------------------------|--------------------------|------------|--------|--------|--------|--------|--------|--------------|-------------|------------------|

|      |                                    | 옷을                       | 8) BOOT    |        | 1      | )=('   | 2      | )=(    | $\geq$       |             | (PA12)<br>(PA11) |

| c F  | C13) I F                           | $\leq$                   | (VDD)      |        |        | \_/'   | 2      | X      | (PC11)       | X           | (PA10)           |

| □ Q: | SC32   F                           | PE6) (VS                 | <          |        |        |        |        |        | (PA9)<br>=() | (PA8)       | (PC9)            |

|      | <u>_</u> סט <i>ד</i> י<br>הווּה: י | 2()<br>2()<br>2()<br>2() | ~          |        |        |        |        |        | \/           | (VSS)       | (VSS)            |

| G C  | ₽Ħ1、 ァ<br>DSC_) IPI                | =(<br>+10)<br>=(         |            |        |        |        |        |        | (T)          | VDD<br>USB  |                  |

| Н    | PC0) IN                            | ミン                       | /          |        |        |        |        |        | 2            | (PD14)      | (PD13)           |

| к    |                                    | C3) ( PA                 | 2) ( PA5 ) | (PC4)  | 5.     | -      | (PD9)  | (PD8)  | iPB15)       | IPB14)      | (PB13)           |

|      |                                    | ミン                       | 3) ( PA6 ) | $\geq$ | $\geq$ | $\geq$ | $\geq$ | $\geq$ | $\geq$       | $\geq$      | PB12)            |

| M    |                                    | /A1) ( PA<br>_ ∕ ` ` _   | 4)   PA7)  | >_/    | 1 PB1) |        | (PE9)  | IPE11) | PE13)        | IPE14)<br>^ | (PE15)           |

|      |                                    |                          |            |        |        |        |        |        |              |             |                  |

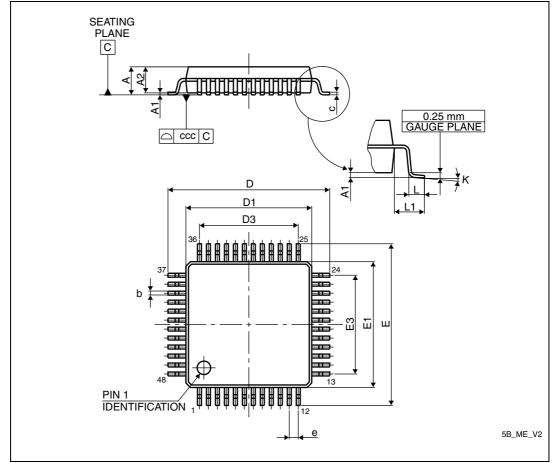

Figure 4. STM32L073xx UFBGA100 ballout - 7x 7 mm

1. The above figure shows the package top view.

2. I/O pin supplied by VDD\_USB.

| Table 16. | STM32L | .073xx | pin | definition | (continued) |

|-----------|--------|--------|-----|------------|-------------|

|-----------|--------|--------|-----|------------|-------------|

|        | Pi     | n num   | ber     |          |                                       |          | -             |      |                                                                                      |                      |

|--------|--------|---------|---------|----------|---------------------------------------|----------|---------------|------|--------------------------------------------------------------------------------------|----------------------|

| LQFP48 | LQFP64 | TFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Note | Alternate functions                                                                  | Additional functions |

| 33     | 45     | B8      | 71      | A12      | PA12                                  | I/O      | FT            | (2)  | SPI1_MOSI, EVENTOUT,<br>TSC_G4_IO4,<br>USART1_RTS_DE,<br>COMP2_OUT                   | USB_DP               |

| 34     | 46     | A8      | 72      | A11      | PA13                                  | I/O      | FT            | -    | SWDIO, USB_OE,<br>LPUART1_RX                                                         | -                    |

| -      | -      | -       | 73      | C11      | VDD                                   | S        |               | -    | -                                                                                    | -                    |

| 35     | 47     | D5      | 74      | F11      | VSS                                   | S        |               | -    | -                                                                                    | -                    |

| 36     | 48     | E6      | 75      | G11      | VDD_USB                               | S        |               | -    | -                                                                                    | -                    |

| 37     | 49     | A7      | 76      | A10      | PA14                                  | I/O      | FT            | -    | SWCLK, USART2_TX,<br>LPUART1_TX                                                      | -                    |

| 38     | 50     | A6      | 77      | A9       | PA15                                  | I/O      | FT            | -    | SPI1_NSS, LCD_SEG17,<br>TIM2_ETR, EVENTOUT,<br>USART2_RX, TIM2_CH1,<br>USART4_RTS_DE | -                    |

| -      | 51     | B7      | 78      | B11      | PC10                                  | I/O      | FT            | -    | LPUART1_TX,<br>LCD_COM4/LCD_SEG28/<br>LCD_SEG48, USART4_TX                           | -                    |

| -      | 52     | B6      | 79      | C10      | PC11                                  | I/O      | FT            | -    | LPUART1_RX,<br>LCD_COM5/LCD_SEG29/<br>LCD_SEG49,<br>USART4_RX                        | -                    |

| -      | 53     | C5      | 80      | B10      | PC12                                  | I/O      | FT            | -    | LCD_COM6/LCD_SEG30/<br>LCD_SEG50,<br>USART5_TX,<br>USART4_CK                         | -                    |

| -      | -      | -       | 81      | C9       | PD0                                   | I/O      | FT            | -    | TIM21_CH1,<br>SPI2_NSS/I2S2_WS                                                       | -                    |

| -      | -      | -       | 82      | B9       | PD1                                   | I/O      | FT            | I    | SPI2_SCK/I2S2_CK                                                                     | -                    |

| -      | 54     | В5      | 83      | C8       | PD2                                   | I/O      | FT            | -    | LPUART1_RTS_DE,<br>LCD_COM7/LCD_SEG31/<br>LCD_SEG51, TIM3_ETR,<br>USART5_RX          | -                    |

| -      | -      | -       | 84      | B8       | PD3                                   | I/O      | FT            | -    | USART2_CTS,<br>LCD_SEG44,<br>SPI2_MISO/I2S2_MCK                                      | -                    |

DocID027096 Rev 3

| C | Ŋ |

|---|---|

|   | S |

|   | ŝ |

| Ś | Ş |

| Š | 2 |

|   |   |

DocID027096 Rev 3

5

|        | Table 17. Alternate functions port A |                                                                                                   |                                         |                                                                                     |                       |                                                    |                                          |                                                             |                                   |  |

|--------|--------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------|------------------------------------------|-------------------------------------------------------------|-----------------------------------|--|

|        |                                      | AF0                                                                                               | AF1                                     | AF2                                                                                 | AF3                   | AF4                                                | AF5                                      | AF6                                                         | AF7                               |  |

| F      | Port                                 | SPI1/SPI2/I2S2/U<br>SART1/2/<br>LPUART1/USB/L<br>PTIM1/TSC/<br>TIM2/21/22/<br>EVENTOUT/<br>SYS_AF | SPI1/SPI2/I2S2/I2<br>C1/LCD/<br>TIM2/21 | SPI1/SPI2/I2S2/L<br>PUART1/<br>USART5/USB/LP<br>TIM1/TIM2/3/EVE<br>NTOUT/<br>SYS_AF | I2C1/TSC/<br>EVENTOUT | I2C1/USART1/2/<br>LPUART1/<br>TIM3/22/<br>EVENTOUT | SPI2/I2S2/I2C2/U<br>SART1/<br>TIM2/21/22 | I2C1/2/<br>LPUART1/<br>USART4/<br>UASRT5/TIM21/E<br>VENTOUT | I2C3/LPUART1/C<br>OMP1/2/<br>TIM3 |  |

|        | PA0                                  | -                                                                                                 | -                                       | TIM2_CH1                                                                            | TSC_G1_IO1            | USART2_CTS                                         | TIM2_ETR                                 | USART4_TX                                                   | COMP1_OUT                         |  |

|        | PA1                                  | EVENTOUT                                                                                          | LCD_SEG0                                | TIM2_CH2                                                                            | TSC_G1_IO2            | USART2_RTS_D<br>E                                  | TIM21_ETR                                | USART4_RX                                                   | -                                 |  |

|        | PA2                                  | TIM21_CH1                                                                                         | LCD_SEG1                                | TIM2_CH3                                                                            | TSC_G1_IO3            | USART2_TX                                          | -                                        | LPUART1_TX                                                  | COMP2_OUT                         |  |

|        | PA3                                  | TIM21_CH2                                                                                         | LCD_SEG2                                | TIM2_CH4                                                                            | TSC_G1_IO4            | USART2_RX                                          | -                                        | LPUART1_RX                                                  | -                                 |  |

|        | PA4                                  | SPI1_NSS                                                                                          | -                                       | -                                                                                   | TSC_G2_IO1            | USART2_CK                                          | TIM22_ETR                                | -                                                           | -                                 |  |

|        | PA5                                  | SPI1_SCK                                                                                          | -                                       | TIM2_ETR                                                                            | TSC_G2_IO2            |                                                    | TIM2_CH1                                 | -                                                           | -                                 |  |

|        | PA6                                  | SPI1_MISO                                                                                         | LCD_SEG3                                | TIM3_CH1                                                                            | TSC_G2_IO3            | LPUART1_CTS                                        | TIM22_CH1                                | EVENTOUT                                                    | COMP1_OUT                         |  |

|        | PA7                                  | SPI1_MOSI                                                                                         | LCD_SEG4                                | TIM3_CH2                                                                            | TSC_G2_IO4            | -                                                  | TIM22_CH2                                | EVENTOUT                                                    | COMP2_OUT                         |  |

| Port A | PA8                                  | МСО                                                                                               | LCD_COM0                                | USB_CRS_<br>SYNC                                                                    | EVENTOUT              | USART1_CK                                          | -                                        | -                                                           | I2C3_SCL                          |  |

|        | PA9                                  | MCO                                                                                               | LCD_COM1                                | -                                                                                   | TSC_G4_IO1            | USART1_TX                                          | -                                        | I2C1_SCL                                                    | I2C3_SMBA                         |  |

|        | PA10                                 | -                                                                                                 | LCD_COM2                                | -                                                                                   | TSC_G4_IO2            | USART1_RX                                          | -                                        | I2C1_SDA                                                    | -                                 |  |

|        | PA11                                 | SPI1_MISO                                                                                         | -                                       | EVENTOUT                                                                            | TSC_G4_IO3            | USART1_CTS                                         | -                                        | -                                                           | COMP1_OUT                         |  |

|        | PA12                                 | SPI1_MOSI                                                                                         | -                                       | EVENTOUT                                                                            | TSC_G4_IO4            | USART1_RTS_<br>DE                                  | -                                        | -                                                           | COMP2_OUT                         |  |

|        | PA13                                 | SWDIO                                                                                             | -                                       | USB_OE                                                                              | -                     | -                                                  | -                                        | LPUART1_RX                                                  | -                                 |  |

|        | PA14                                 | SWCLK                                                                                             | -                                       | -                                                                                   | -                     | USART2_TX                                          | -                                        | LPUART1_TX                                                  | -                                 |  |

|        | PA15                                 | SPI1_NSS                                                                                          | LCD_SEG17                               | TIM2_ETR                                                                            | EVENTOUT              | USART2_RX                                          | TIM2_CH1                                 | USART4_RTS_D<br>E                                           | -                                 |  |

Pin descriptions

50/139

### High-speed internal 48 MHz (HSI48) RC oscillator

| Symbol                  | Parameter                                                                          | Conditions             | Min                 | Тур  | Мах                | Unit |  |  |  |  |

|-------------------------|------------------------------------------------------------------------------------|------------------------|---------------------|------|--------------------|------|--|--|--|--|

| f <sub>HSI48</sub>      | Frequency                                                                          |                        | -                   | 48   | -                  | MHz  |  |  |  |  |

| TRIM                    | HSI48 user-trimming step                                                           |                        | 0.09 <sup>(2)</sup> | 0.14 | 0.2 <sup>(2)</sup> | %    |  |  |  |  |

| DuCy <sub>(HSI48)</sub> | Duty cycle                                                                         |                        | 45 <sup>(2)</sup>   | -    | 55 <sup>(2)</sup>  | %    |  |  |  |  |

| ACC <sub>HSI48</sub>    | Accuracy of the HSI48<br>oscillator (factory calibrated<br>before CRS calibration) | T <sub>A</sub> = 25 °C | -4 <sup>(3)</sup>   | -    | 4 <sup>(3)</sup>   | %    |  |  |  |  |

| t <sub>su(HSI48)</sub>  | HSI48 oscillator startup time                                                      |                        | -                   | -    | 6 <sup>(2)</sup>   | μs   |  |  |  |  |

| I <sub>DDA(HSI48)</sub> | HSI48 oscillator power<br>consumption                                              |                        | -                   | 330  | 380 <sup>(2)</sup> | μA   |  |  |  |  |

1.  $V_{DDA}$  = 3.3 V,  $T_A$  = -40 to 125 °C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization results.

### Low-speed internal (LSI) RC oscillator

#### Table 49. LSI oscillator characteristics

| Symbol                              | Parameter                                                           | Min | Тур | Max | Unit |

|-------------------------------------|---------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(1)</sup>     | LSI frequency                                                       | 26  | 38  | 56  | kHz  |

| D <sub>LSI</sub> <sup>(2)</sup>     | LSI oscillator frequency drift $0^{\circ}C \le T_A \le 85^{\circ}C$ | -10 | -   | 4   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                                         | -   | -   | 200 | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                                    | -   | 400 | 510 | nA   |

1. Guaranteed by test in production.

2. This is a deviation for an individual part, once the initial frequency has been measured.

3. Guaranteed by design.

## Multi-speed internal (MSI) RC oscillator

#### Table 50. MSI oscillator characteristics

| Symbol           | Parameter                                                                                                 | Condition   | Тур  | Max | Unit |

|------------------|-----------------------------------------------------------------------------------------------------------|-------------|------|-----|------|

|                  |                                                                                                           | MSI range 0 | 65.5 | -   |      |

|                  |                                                                                                           | MSI range 1 | 131  | -   | kHz  |

|                  | Frequency after factory calibration, done at V <sub>DD</sub> = 3.3 V and T <sub>A</sub> = 25 $^{\circ}$ C | MSI range 2 | 262  | -   | KLIZ |

| f <sub>MSI</sub> |                                                                                                           | MSI range 3 | 524  | -   |      |

|                  |                                                                                                           | MSI range 4 | 1.05 | -   |      |

|                  |                                                                                                           | MSI range 5 | 2.1  | -   | MHz  |

|                  |                                                                                                           | MSI range 6 | 4.2  | -   |      |

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC 61967-2 standard which specifies the test board and the pin loading.

| Symbol | Parameter                   | Conditions                                            | Monitored<br>frequency band | Max vs.<br>frequency<br>range at<br>32 MHz | Unit |

|--------|-----------------------------|-------------------------------------------------------|-----------------------------|--------------------------------------------|------|

|        | S <sub>EMI</sub> Peak level | V                                                     | 0.1 to 30 MHz               | -7                                         |      |

| 6      |                             | $V_{DD} = 3.6 \text{ V},$<br>$T_{A} = 25 \text{ °C},$ | 30 to 130 MHz               | 14                                         | dBµV |

| SEMI   |                             | LQFP100 package                                       | 130 MHz to 1 GHz            | 9                                          |      |

|        |                             | compliant with IEC 61967-2                            | EMI Level                   | 2                                          | -    |

#### Table 56. EMI characteristics

#### **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 61* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 26*. All I/Os are CMOS and TTL compliant.

| Symbol                            | Parameter                                | Conditions                                                                                                                                                                     | Min                   | Max  | Unit |

|-----------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|------|

| V <sub>OL</sub> <sup>(1)</sup>    | Output low level voltage for an I/O pin  | CMOS port <sup>(2)</sup> ,<br>I <sub>IO</sub> = +8 mA                                                                                                                          | -                     | 0.4  |      |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin | $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$                                                                                                                     | V <sub>DD</sub> -0.4  | -    |      |

| V <sub>OL</sub> <sup>(1)</sup>    | Output low level voltage for an I/O pin  | $\begin{array}{c} {\sf TTL} \; {\sf port}^{(2)}, \\ {\sf I}_{IO} \; \mbox{=} + \; 8 \; \mbox{mA} \\ {\sf 2.7} \; {\sf V} \leq {\sf V}_{DD} \leq \; 3.6 \; {\sf V} \end{array}$ | -                     | 0.4  |      |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | $\begin{array}{c} {\sf TTL} \ {\sf port}^{(2)}, \\ {\sf I}_{IO} = \ {\sf -6} \ {\sf mA} \\ {\sf 2.7} \ {\sf V} \leq {\sf V}_{DD} \leq \ {\sf 3.6} \ {\sf V} \end{array}$       | 2.4                   | -    |      |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin  | $\begin{array}{l} \text{I}_{IO} = +15 \text{ mA} \\ \text{2.7 V} \leq \text{V}_{DD} \leq \ \text{3.6 V} \end{array}$                                                           | -                     | 1.3  | V    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | $\begin{array}{l} \text{I}_{\text{IO}} \text{ = -15 mA} \\ \text{2.7 V} \leq \text{V}_{\text{DD}} \leq \ \text{3.6 V} \end{array}$                                             | V <sub>DD</sub> -1.3  | -    |      |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin  | $I_{IO}$ = +4 mA<br>1.65 V $\leq$ V <sub>DD</sub> < 3.6 V                                                                                                                      | -                     | 0.45 |      |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | $\begin{array}{l} \text{I}_{IO} = \text{-4 mA} \\ 1.65 \text{ V} \leq \text{V}_{DD} \leq \ 3.6 \text{ V} \end{array}$                                                          | V <sub>DD</sub> -0.45 | -    |      |

| V <sub>OLFM+</sub> (1)(4)         | Output low level voltage for an FTf      | $\begin{array}{l} \text{I}_{\text{IO}} = 20 \text{ mA} \\ 2.7 \text{ V} \leq \text{V}_{DD} \leq \ 3.6 \text{ V} \end{array}$                                                   | -                     | 0.4  |      |

| VOLFM+                            | I/O pin in Fm+ mode                      | $\begin{array}{l} {\sf I}_{IO} \mbox{=} \ 10 \ mA \\ 1.65 \ V \le V_{DD} \le \ 3.6 \ V \end{array}$                                                                            | -                     | 0.4  |      |

| Table 61. | Output voltage characteristics |

|-----------|--------------------------------|

|-----------|--------------------------------|

The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 24*. The sum of the currents sunk by all the I/Os (I/O ports and control pins) must always be respected and must not exceed ΣI<sub>IO(PIN)</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 24. The sum of the currents sourced by all the I/Os (I/O ports and control pins) must always be respected and must not exceed  $\Sigma I_{IO(PIN)}$ .

4. Guaranteed by characterization results.

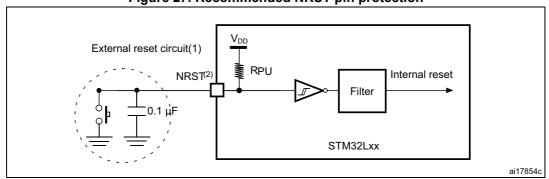

Figure 27. Recommended NRST pin protection

1. The reset network protects the device against parasitic resets.

2. The user must ensure that the level on the NRST pin can go below the  $V_{IL(NRST)}$  max level specified in *Table 63*. Otherwise the reset will not be taken into account by the device.

#### 6.3.15 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 64* are derived from tests performed under ambient temperature, f<sub>PCLK</sub> frequency and V<sub>DDA</sub> supply voltage conditions summarized in *Table 26: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

| Symbol                             | Parameter                                     | Conditions                                            | Min                 | Тур | Мах               | Unit               |  |

|------------------------------------|-----------------------------------------------|-------------------------------------------------------|---------------------|-----|-------------------|--------------------|--|

| M                                  | Analog supply voltage for                     | Fast channel                                          | 1.65                | -   | 3.6               | V                  |  |

| V <sub>DDA</sub>                   | ADC on                                        | Standard channel                                      | 1.75 <sup>(1)</sup> | -   | 3.6               |                    |  |

| V <sub>REF+</sub>                  | Positive reference voltage                    | -                                                     | 1.65                |     | V <sub>DDA</sub>  | V                  |  |

| V <sub>REF-</sub>                  | Negative reference voltage                    | -                                                     | -                   | 0   | -                 |                    |  |

|                                    | Current consumption of the                    | 1.14 Msps                                             | -                   | 200 | -                 |                    |  |

|                                    | ADC on $V_{\mbox{DDA}}$ and $V_{\mbox{REF}+}$ | 10 ksps                                               | -                   | 40  | -                 |                    |  |

| I <sub>DDA</sub> (ADC)             | Current consumption of the                    | 1.14 Msps                                             | -                   | 70  | -                 | μA                 |  |

|                                    | ADC on V <sub>DD</sub> <sup>(2)</sup>         | 10 ksps                                               | -                   | 1   | -                 | 1                  |  |

|                                    |                                               | Voltage scaling Range 1                               | 0.14                | -   | 16                |                    |  |

| f <sub>ADC</sub>                   | ADC clock frequency                           | Voltage scaling Range 2                               | 0.14                | -   | 8                 | MHz                |  |

|                                    |                                               | Voltage scaling Range 3                               | 0.14                | -   | 4                 | 1                  |  |

| $f_S^{(3)}$                        | Sampling rate                                 | 12-bit resolution                                     | 0.01                | -   | 1.14              | MHz                |  |

| f <sub>TRIG</sub> <sup>(3)</sup>   | External trigger frequency                    | f <sub>ADC</sub> = 16 MHz,<br>12-bit resolution       | -                   | -   | 941               | kHz                |  |

| inio                               |                                               | -                                                     | -                   | -   | 17                | 1/f <sub>ADC</sub> |  |

| V <sub>AIN</sub>                   | Conversion voltage range                      | -                                                     | 0                   | -   | V <sub>REF+</sub> | V                  |  |

| R <sub>AIN</sub> <sup>(3)</sup>    | External input impedance                      | See <i>Equation 1</i> and <i>Table 65</i> for details | -                   | -   | 50                | kΩ                 |  |

| R <sub>ADC</sub> <sup>(3)(4)</sup> | Sampling switch resistance                    | -                                                     | -                   | -   | 1                 | kΩ                 |  |

Table 64. ADC characteristics

- 6. Difference between the value measured at Code (0x800) and the ideal value =  $V_{REF+}/2$ .

- 7. Difference between the value measured at Code (0x001) and the ideal value.

- 8. Difference between ideal slope of the transfer function and measured slope computed from code 0x000 and 0xFFF when buffer is off, and from code giving 0.2 V and ( $V_{DDA} 0.2$ ) V when buffer is on.

- 9. In buffered mode, the output can overshoot above the final value for low input code (starting from min value).

#### Figure 32. 12-bit buffered/non-buffered DAC

#### 6.3.17 Temperature sensor characteristics

#### Table 68. Temperature sensor calibration values

| Calibration value name | Description                                                               | Memory address            |  |

|------------------------|---------------------------------------------------------------------------|---------------------------|--|

| TS_CAL1                | TS ADC raw data acquired at temperature of 30 °C, V <sub>DDA</sub> = 3 V  | 0x1FF8 007A - 0x1FF8 007B |  |

| TS_CAL2                | TS ADC raw data acquired at temperature of 130 °C, V <sub>DDA</sub> = 3 V | 0x1FF8 007E - 0x1FF8 007F |  |

#### Table 69. Temperature sensor characteristics

| Symbol                                | Parameter                                      | Min  | Тур  | Max  | Unit  |

|---------------------------------------|------------------------------------------------|------|------|------|-------|

| T <sub>L</sub> <sup>(1)</sup>         | V <sub>SENSE</sub> linearity with temperature  |      | ±1   | ±2   | °C    |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 1.48 | 1.61 | 1.75 | mV/°C |

| V <sub>130</sub>                      | Voltage at 130°C ±5°C <sup>(2)</sup>           |      | 670  | 700  | mV    |

| I <sub>DDA(TEMP)</sub> <sup>(3)</sup> | Current consumption                            |      | 3.4  | 6    | μA    |

| t <sub>START</sub> <sup>(3)</sup>     | Startup time                                   |      | -    | 10   |       |

| T <sub>S_temp</sub> <sup>(4)(3)</sup> | ADC sampling time when reading the temperature | 10   | -    | -    | μs    |

1. Guaranteed by characterization results.

2. Measured at  $V_{DD}$  = 3 V ±10 mV. V130 ADC conversion result is stored in the TS\_CAL2 byte.

- 3. Guaranteed by design.

- 4. Shortest sampling time can be determined in the application by multiple iterations.

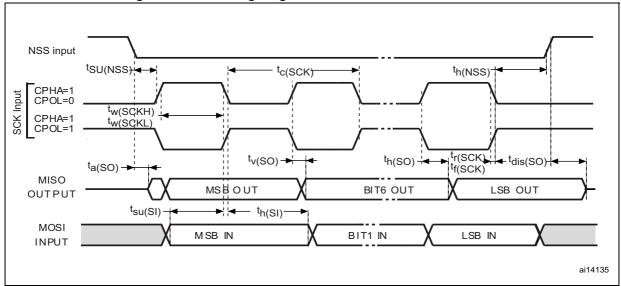

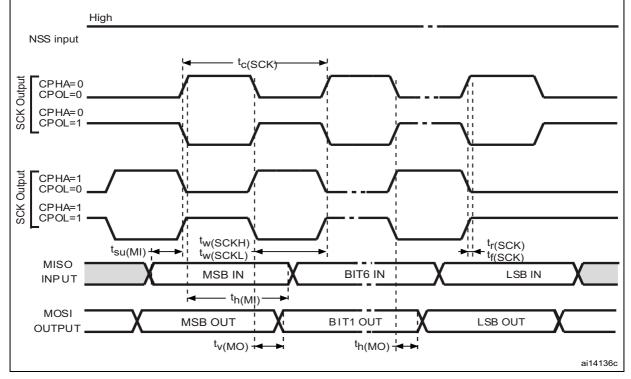

| Symbol                                       | Parameter                            | Conditions                                               | Min     | Тур   | Max              | Unit |

|----------------------------------------------|--------------------------------------|----------------------------------------------------------|---------|-------|------------------|------|

|                                              |                                      | Master mode                                              |         |       | 8                |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency                  | Slave mode Transmitter<br>1.65 <v<sub>DD&lt;3.6V</v<sub> | -       | -     | 8                | MHz  |

| -C(SCR)                                      |                                      | Slave mode Transmitter<br>2.7 <v<sub>DD&lt;3.6V</v<sub>  |         |       | 8 <sup>(2)</sup> |      |

| Duty <sub>(SCK)</sub>                        | Duty cycle of SPI clock<br>frequency | Slave mode                                               | 30      | 50    | 70               | %    |

| t <sub>su(NSS)</sub>                         | NSS setup time                       | Slave mode, SPI presc = 2                                | 4*Tpclk | -     | -                |      |

| t <sub>h(NSS)</sub>                          | NSS hold time                        | Slave mode, SPI presc = 2                                | 2*Tpclk | -     | -                |      |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                | Master mode                                              | Tpclk-2 | Tpclk | Tpclk+2          |      |

| t <sub>su(MI)</sub>                          | Data input setup time                | Master mode                                              | 0       | -     | -                |      |

| t <sub>su(SI)</sub>                          | Data input setup time                | Slave mode                                               | 3       | -     | -                |      |

| t <sub>h(MI)</sub>                           | Data input hold time                 | Master mode                                              | 11      | -     | -                |      |

| t <sub>h(SI)</sub>                           |                                      | Slave mode                                               | 4.5     | -     | -                | ns   |

| t <sub>a(SO</sub>                            | Data output access time              | Slave mode                                               | 18      | -     | 52               |      |

| t <sub>dis(SO)</sub>                         | Data output disable time             | Slave mode                                               | 12      | -     | 42               |      |

| t <sub>v(SO)</sub>                           | Data output valid time               | Slave mode                                               | -       | 20    | 56.5             |      |

| t <sub>v(MO)</sub>                           |                                      | Master mode                                              | -       | 5     | 9                |      |

| t <sub>h(SO)</sub>                           | Data output hold time                | Slave mode                                               | 13      | -     | -                |      |

| t <sub>h(MO)</sub>                           |                                      | Master mode                                              | 3       | -     | -                |      |

| Table 76. SPI characteristics in | n voltage | Range 2 <sup>(1)</sup> |

|----------------------------------|-----------|------------------------|

|----------------------------------|-----------|------------------------|

1. Guaranteed by characterization results.

2. The maximum SPI clock frequency in slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty<sub>(SCK)</sub> = 50%.

Figure 34. SPI timing diagram - slave mode and CPHA =  $1^{(1)}$

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

Figure 35. SPI timing diagram - master mode<sup>(1)</sup>

<sup>1.</sup> Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

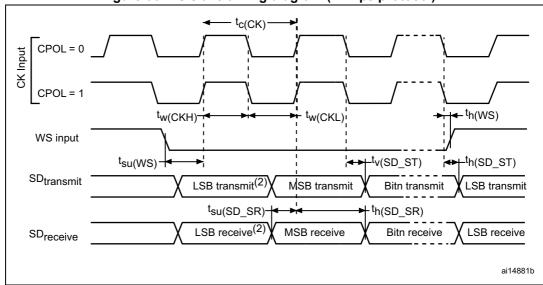

Figure 36. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at CMOS levels:  $0.3 \times V_{DD}$  and  $0.7 \times V_{DD}$ .

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

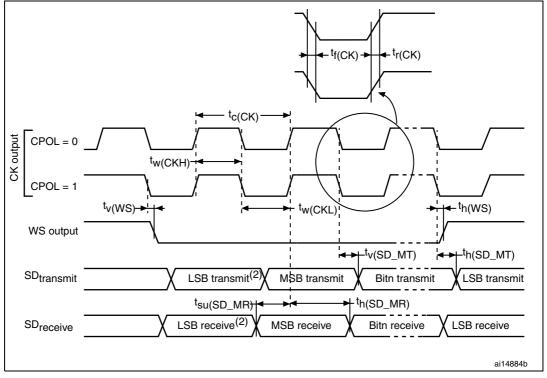

#### Figure 37. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Guaranteed by characterization results.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

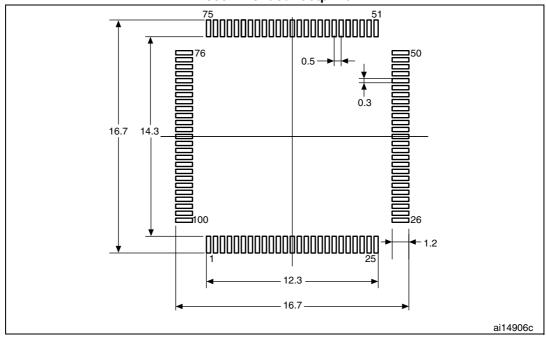

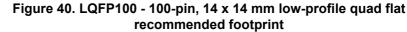

STM32L073xx

1. Dimensions are expressed in millimeters.

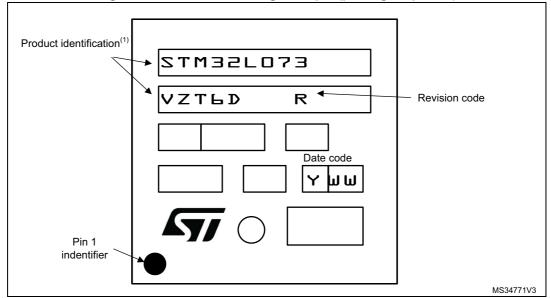

#### **Device marking for LQFP100**

The following figure gives an example of topside marking versus pin 1 position identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

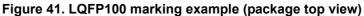

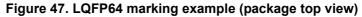

#### **Device marking for LQFP64**

The following figure gives an example of topside marking versus pin 1 position identifier location.

I. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

## 7.4 **TFBGA64** package information

Figure 48. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch thin profile fine pitch ball grid array package outline

1. Drawing is not to scale.

| Table 87. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball |

|-----------------------------------------------------------------------------------|

| grid array package mechanical data                                                |

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |

|--------|-------|-------------|-------|--------|-----------------------|--------|--|

| Symbol | Min   | Тур         | Мах   | Min    | Тур                   | Max    |  |

| А      | -     | -           | 1.200 | -      | -                     | 0.0472 |  |

| A1     | 0.150 | -           | -     | 0.0059 | -                     | -      |  |

| A2     | -     | 0.200       | -     | -      | 0.0079                | -      |  |

| A4     | -     | -           | 0.600 | -      | -                     | 0.0236 |  |

| b      | 0.250 | 0.300       | 0.350 | 0.0098 | 0.0118                | 0.0138 |  |

| D      | 4.850 | 5.000       | 5.150 | 0.1909 | 0.1969                | 0.2028 |  |

| D1     | -     | 3.500       | -     | -      | 0.1378                | -      |  |

| E      | 4.850 | 5.000       | 5.150 | 0.1909 | 0.1969                | 0.2028 |  |

| E1     | -     | 3.500       | -     | -      | 0.1378                | -      |  |

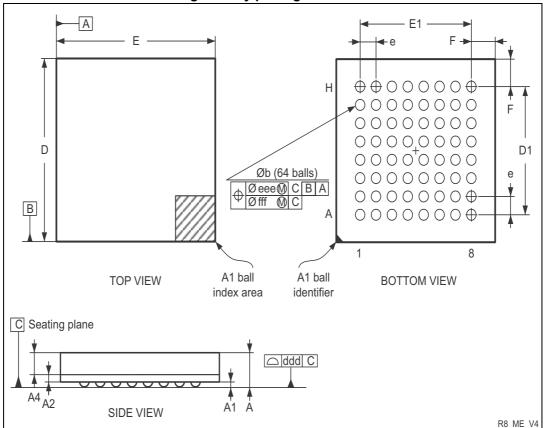

## 7.5 LQFP48 package information

Figure 51. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.

# 9 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03-Aug-2015 | 1        | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 26-Oct-2015 | 2        | Changed confidentiality level to public.<br>Updated datasheet status to "production data".<br>Modified ultra-low-power platform features on cover page.<br>Changed number of GPIOs for LQFP48 for 37 in <i>Table 2: Ultra-low-power STM32L073xxx device features and peripheral counts</i> .<br>Changed LCD_VLCD1 into LCD_VLCD2 in <i>Section 3.13.2: VLCD voltage monitoring</i> .<br>In <i>Section 6: Electrical characteristics</i> , updated notes related to values guaranteed by characterization.<br>Updated $ \Delta V_{SS} $ definition to include $V_{REF-}$ in <i>Table 23: Voltage characteristics</i> .<br>Added $\Sigma V_{DD_USB}$ and updated $\Sigma I_{IO(PIN)}$ in <i>Figure 24: Current characteristics</i> .<br>Updated <i>Table 56: EMI characteristics</i> .<br>Updated <i>Table 56: EMI characteristics</i> .<br>Updated <i>Section 7.2: UFBGA100 package information</i> . Updated <i>Figure 53: LQFP48 marking example (package top view)</i> . |

#### Table 92. Document revision history