#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 109                                                                   |

| Program Memory Size        | 256KB (256K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 8K x 8                                                                |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 40x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 132-UFBGA                                                             |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l162qch6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of cores and features. From proprietary 8bit to up to Cortex-M3, including the Cortex-M0+, the STM32Lx series are the best choice to answer the user needs, in terms of ultra-low-power features. The STM32 ultra-low-power series are the best fit, for instance, for gas/water meter, keyboard/mouse or fitness and healthcare, wearable applications. Several built-in features like LCD drivers, dual-bank memory, Low-power run mode, op-amp, AES 128-bit, DAC, USB crystal-less and many others will clearly allow to build very cost-optimized applications by reducing BOM.

Note: STMicroelectronics as a reliable and long-term manufacturer ensures as much as possible the pin-to-pin compatibility between any STM8Lxxxxx and STM32Lxxxxx devices and between any of the STM32Lx and STM32Fx series. Thanks to this unprecedented scalability, the old applications can be upgraded to respond to the latest market features and efficiency demand.

#### 2.2.1 **Performance**

All the families incorporate highly energy-efficient cores with both Harvard architecture and pipelined execution: advanced STM8 core for STM8L families and ARM Cortex-M3 core for STM32L family. In addition specific care for the design architecture has been taken to optimize the mA/DMIPS and mA/MHz ratios.

This allows the ultra-low-power performance to range from 5 up to 33.3 DMIPs.

#### 2.2.2 Shared peripherals

STM8L15xxx, STM32L15xxx and STM32L162xx share identical peripherals which ensure a very easy migration from one family to another:

- Analog peripherals: ADC, DAC and comparators

- Digital peripherals: RTC and some communication interfaces

#### 2.2.3 Common system strategy.

To offer flexibility and optimize performance, the STM8L15xxx, STM32L15xxx and STM32L162xx family uses a common architecture:

- Same power supply range from 1.65 V to 3.6 V

- Architecture optimized to reach ultra-low consumption both in low-power modes and Run mode

- Fast startup strategy from low-power modes

- Flexible system clock

- Ultrasafe reset: same reset strategy including power-on reset, power-down reset, brownout reset and programmable voltage detector

#### 2.2.4 Features

ST ultra-low-power continuum also lies in feature compatibility:

- More than 15 packages with pin count from 20 to 144 pins and size down to 3 x 3 mm

- Memory density ranging from 2 to 512 Kbytes

|                                   | Functionalities depending on the operating power supply range |                           |                                  |                      |  |  |  |  |  |

|-----------------------------------|---------------------------------------------------------------|---------------------------|----------------------------------|----------------------|--|--|--|--|--|

| Operating power supply range      | DAC and ADC operation                                         | USB                       | Dynamic voltage<br>scaling range | I/O operation        |  |  |  |  |  |

| $V_{DD}=V_{DDA}=2.0$ to 2.4 V     | Conversion time up<br>to 500 Ksps                             | Functional <sup>(2)</sup> | Range 1, Range 2<br>or Range 3   | Full speed operation |  |  |  |  |  |

| $V_{DD} = V_{DDA} = 2.4$ to 3.6 V | Conversion time up<br>to 1 Msps                               | Functional <sup>(2)</sup> | Range 1, Range 2<br>or Range 3   | Full speed operation |  |  |  |  |  |

#### Table 3. Functionalities depending on the operating power supply range (continued)

CPU frequency changes from initial to final must respect "F<sub>CPU</sub> initial < 4\*F<sub>CPU</sub> final" to limit V<sub>CORE</sub> drop due to current consumption peak when frequency increases. It must also respect 5 μs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, the user can switch from 4.2 MHz to 16 MHz, wait 5 μs, then switch from 16 MHz to 32 MHz.

2. Should be USB compliant from I/O voltage standpoint, the minimum  $\rm V_{DD}$  is 3.0 V.

#### Table 4. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                                | Dynamic voltage scaling range |

|----------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws)   | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)     | Range 2                       |

| 2.1MHz to 4.2 MHz (1ws)<br>32 kHz to 2.1 MHz (0ws) | Range 3                       |

| Table 5. Functionalities depending on the working mode (from Run/active down to |

|---------------------------------------------------------------------------------|

| standby)                                                                        |

|                                           |            | Sta   | andby)       |                |   |                      |         |                      |  |

|-------------------------------------------|------------|-------|--------------|----------------|---|----------------------|---------|----------------------|--|

|                                           |            |       | Low-         | Low-           |   | Stop                 | Standby |                      |  |

| lps                                       | Run/Active | Sleep | power<br>Run | power<br>Sleep |   | Wakeup<br>capability |         | Wakeup<br>capability |  |

| CPU                                       | Y          |       | Y            |                |   |                      |         |                      |  |

| Flash                                     | Y          | Y     | Y            | Y              |   |                      |         |                      |  |

| RAM                                       | Y          | Y     | Y            | Y              | Y |                      |         |                      |  |

| Backup Registers                          | Y          | Y     | Y            | Y              | Y |                      | Y       |                      |  |

| EEPROM                                    | Y          | Y     | Y            | Y              | Y |                      |         |                      |  |

| Brown-out rest<br>(BOR)                   | Y          | Y     | Y            | Y              | Y | Y                    | Y       |                      |  |

| DMA                                       | Y          | Y     | Y            | Y              |   |                      |         |                      |  |

| Programmable<br>Voltage Detector<br>(PVD) | Y          | Y     | Y            | Y              | Y | Y                    | Y       |                      |  |

| Power On Reset<br>(POR)                   | Y          | Y     | Y            | Y              | Y | Y                    | Y       |                      |  |

| Power Down Rest<br>(PDR)                  | Y          | Y     | Y            | Y              | Y |                      | Y       |                      |  |

| High Speed<br>Internal (HSI)              | Y          | Y     |              |                |   |                      |         |                      |  |

| High Speed<br>External (HSE)              | Y          | Y     |              |                |   |                      |         |                      |  |

| Low Speed Internal<br>(LSI)               | Y          | Y     | Y            | Y              | Y |                      | Y       |                      |  |

| Low Speed<br>External (LSE)               | Y          | Y     | Y            | Y              | Y |                      | Y       |                      |  |

| Multi-Speed<br>Internal (MSI)             | Y          | Y     | Y            | Y              |   |                      |         |                      |  |

| Inter-Connect<br>Controller               | Y          | Y     | Y            | Y              |   |                      |         |                      |  |

| RTC                                       | Y          | Y     | Y            | Y              | Y | Y                    | Y       |                      |  |

| RTC Tamper                                | Y          | Y     | Y            | Y              | Y | Y                    | Y       | Y                    |  |

| Auto WakeUp<br>(AWU)                      | Y          | Y     | Y            | Y              | Y | Y                    | Y       | Y                    |  |

| LCD                                       | Y          | Y     | Y            | Y              | Y |                      |         |                      |  |

| USB                                       | Y          | Y     |              |                |   | Y                    |         |                      |  |

| USART                                     | Y          | Y     | Y            | Y              | Y | (1)                  |         |                      |  |

| SPI                                       | Y          | Y     | Y            | Y              |   |                      |         |                      |  |

| I2C                                       | Y          | Y     | Y            | Y              |   | (1)                  |         |                      |  |

# 3.7 Memories

The STM32L162xC/C-A devices have the following features:

- 32 Kbytes of embedded RAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 256 Kbytes of embedded Flash program memory

- 8 Kbytes of data EEPROM

- Options bytes

The options bytes are used to write-protect or read-out protect the memory (with 4 Kbytes granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no readout protection

- Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protection, debug features (ARM Cortex-M3 JTAG and serial wire) and boot in RAM selection disabled (JTAG fuse)

The whole non-volatile memory embeds the error correction code (ECC) feature.

# 3.8 DMA (direct memory access)

The flexible 12-channel, general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. The DMA controller supports circular buffer management, avoiding the generation of interrupts when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with software trigger support for each channel. Configuration is done by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals: AES, SPI, I<sup>2</sup>C, USART, general-purpose timers, DAC and ADC.

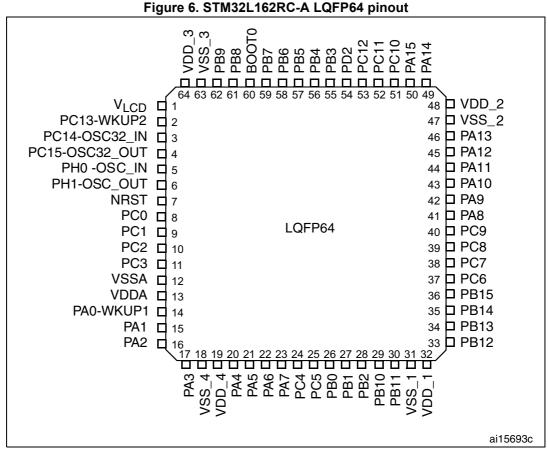

1. This figure shows the package top view.

| Na               | me                   | Abbreviation                       | Definition                                                                                            |  |  |  |  |

|------------------|----------------------|------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin r            | name                 |                                    | e specified in brackets below the pin name, the pin function reset is the same as the actual pin name |  |  |  |  |

|                  |                      | S                                  | Supply pin                                                                                            |  |  |  |  |

| Pin              | type                 | I                                  | Input only pin                                                                                        |  |  |  |  |

|                  |                      | I/O                                | Input / output pin                                                                                    |  |  |  |  |

|                  |                      | FT                                 | 5 V tolerant I/O                                                                                      |  |  |  |  |

| I/O etr          | ucture               | TC Standard 3.3 V I/O              |                                                                                                       |  |  |  |  |

| 1/O Sti          | ucluie               | В                                  | B Dedicated BOOT0 pin                                                                                 |  |  |  |  |

|                  |                      | RST                                | Bidirectional reset pin with embedded weak pull-up resistor                                           |  |  |  |  |

| No               | tes                  | Unless otherwis<br>and after reset | e specified by a note, all I/Os are set as floating inputs during                                     |  |  |  |  |

|                  | Alternate functions  | Functions select                   | Functions selected through GPIOx_AFR registers                                                        |  |  |  |  |

| Pin<br>functions | Additional functions | Functions direct                   | ly selected/enabled through peripheral registers                                                      |  |  |  |  |

| Table 7. Legend/abbreviations | used in the pinout table |

|-------------------------------|--------------------------|

|                               |                          |

## Table 8. STM32L162xC/C-A pin definitions

|         | F        | Pins    |        |         |                 |                         |                 |                                                  | Pin functions                   |                         |  |

|---------|----------|---------|--------|---------|-----------------|-------------------------|-----------------|--------------------------------------------------|---------------------------------|-------------------------|--|

| LQFP144 | UFBGA132 | LQFP100 | LQFP64 | WLCSP64 | Pin name        | Pin Type <sup>(1)</sup> | I / O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions             | Additional<br>functions |  |

| 1       | B2       | 1       | -      | -       | PE2             | I/O                     | FT              | PE2                                              | TIM3_ETR/LCD_SEG38/<br>TRACECLK | -                       |  |

| 2       | A1       | 2       | -      | -       | PE3             | I/O                     | FT              | PE3                                              | TIM3_CH1/LCD_SEG39/<br>TRACED0  | -                       |  |

| 3       | B1       | 3       | -      | -       | PE4             | I/O                     | FT              | PE4                                              | TIM3_CH2/TRACED1                | -                       |  |

| 4       | C2       | 4       | -      | -       | PE5             | I/O                     | FT              | PE5                                              | TIM9_CH1/TRACED2                | -                       |  |

| 5       | D2       | 5       | -      | -       | PE6-<br>WKUP3   | I/O                     | FT              | PE6                                              | TIM9_CH2/TRACED3                | WKUP3/<br>RTC_TAMP3     |  |

| 6       | E2       | 6       | 1      | C6      | $V_{LCD}^{(3)}$ | S                       | -               | V <sub>LCD</sub>                                 | -                               | -                       |  |

|         | F        | Pins    |        |         |                   |                         | _               | •                                                | Pin functions                                                      |                         |  |  |

|---------|----------|---------|--------|---------|-------------------|-------------------------|-----------------|--------------------------------------------------|--------------------------------------------------------------------|-------------------------|--|--|

| LQFP144 | UFBGA132 | LQFP100 | LQFP64 | WLCSP64 | Pin name          | Pin Type <sup>(1)</sup> | I / O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                                                | Additional<br>functions |  |  |

| 53      | K7       | -       | -      | -       | PF13              | I/O                     | FT              | PF13                                             | -                                                                  | ADC_IN3b                |  |  |

| 54      | J8       | -       | -      | -       | PF14              | I/O                     | FT              | PF14                                             | -                                                                  | ADC_IN6b                |  |  |

| 55      | J9       | -       | -      | -       | PF15              | I/O                     | FT              | PF15                                             | -                                                                  | ADC_IN7b                |  |  |

| 56      | H9       | -       | -      | -       | PG0               | I/O                     | FT              | PG0                                              | -                                                                  | ADC_IN8b                |  |  |

| 57      | G9       | -       | -      | -       | PG1               | I/O                     | FT              | PG1                                              | -                                                                  | ADC_IN9b                |  |  |

| 58      | M7       | 38      | -      | -       | PE7               | I/O                     | тс              | PE7                                              | -                                                                  | ADC_IN22/<br>COMP1_INP  |  |  |

| 59      | L7       | 39      | -      | -       | PE8               | I/O                     | тс              | PE8                                              | -                                                                  | ADC_IN23/<br>COMP1_INP  |  |  |

| 60      | M8       | 40      | -      | -       | PE9               | I/O                     | тс              | PE9                                              | TIM2_CH1_ETR                                                       | ADC_IN24/<br>COMP1_INP  |  |  |

| 61      | -        | -       | -      | -       | V <sub>SS_7</sub> | S                       | -               | V <sub>SS_7</sub>                                | -                                                                  | -                       |  |  |

| 62      | -        | -       | -      | -       | V <sub>DD_7</sub> | S                       | -               | V <sub>DD_7</sub>                                | -                                                                  | -                       |  |  |

| 63      | L8       | 41      | -      | -       | PE10              | I/O                     | тс              | PE10                                             | TIM2_CH2                                                           | ADC_IN25/<br>COMP1_INP  |  |  |

| 64      | M9       | 42      | -      | -       | PE11              | I/O                     | FT              | PE11                                             | TIM2_CH3                                                           | -                       |  |  |

| 65      | L9       | 43      | -      | -       | PE12              | I/O                     | FT              | PE12                                             | TIM2_CH4/SPI1_NSS                                                  | -                       |  |  |

| 66      | M10      | 44      | -      | -       | PE13              | I/O                     | FT              | PE13                                             | SPI1_SCK                                                           | -                       |  |  |

| 67      | M11      | 45      | -      | -       | PE14              | I/O                     | FT              | PE14                                             | SPI1_MISO                                                          | -                       |  |  |

| 68      | M12      | 46      | -      | -       | PE15              | I/O                     | FT              | PE15                                             | SPI1_MOSI                                                          | -                       |  |  |

| 69      | L10      | 47      | 29     | G3      | PB10              | I/O                     | FT              | PB10                                             | TIM2_CH3/I2C2_SCL/<br>USART3_TX/<br>LCD_SEG10                      | -                       |  |  |

| 70      | L11      | 48      | 30     | F3      | PB11              | I/O                     | FT              | PB11                                             | TIM2_CH4/ I2C2_SDA/<br>USART3_RX/ LCD_SEG11                        | -                       |  |  |

| 71      | F12      | 49      | 31     | H2      | V <sub>SS_1</sub> | S                       | -               | V <sub>SS_1</sub>                                | -                                                                  | -                       |  |  |

| 72      | G12      | 50      | 32     | H1      | V <sub>DD_1</sub> | S                       | -               | V <sub>DD_1</sub>                                | -                                                                  | -                       |  |  |

| 73      | L12      | 51      | 33     | G2      | PB12              | I/O                     | FT              | PB12                                             | TIM10_CH1/I2C2_SMBA/<br>SPI2_NSS/ I2S2_WS/<br>USART3_CK/ LCD_SEG12 | ADC_IN18/<br>COMP1_INP  |  |  |

# Table 8. STM32L162xC/C-A pin definitions (continued)

|           |        |          |          |                | [         | Digital alte         | ernate fui | nction numbe | er    |        |        |          |              |

|-----------|--------|----------|----------|----------------|-----------|----------------------|------------|--------------|-------|--------|--------|----------|--------------|

|           | AFIO0  | AFIO1    | AFIO2    | AFIO3          | AFIO4     | AFIO5                | AFIO6      | AFIO7        | AFIO8 | AFIO11 | AFIO12 | AFIO14   | AFIO15       |

| Port name |        |          | -        | •              |           | Alt                  | ernate fu  | inction      |       | -      | I      |          |              |

|           | SYSTEM | TIM2     | TIM3/4/5 | TIM9/<br>10/11 | I2C1/2    | SPI1/2               | SPI3       | USART1/2/3   | -     | LCD    | -      | CPRI     | SYSTEM       |

| PB11      | -      | TIM2_CH4 | -        | -              | I2C2_SDA  | -                    | -          | USART3_RX    | -     | SEG11  | -      | -        | EVENT<br>OUT |

| PB12      | -      | -        | -        | TIM10_CH1      | I2C2_SMBA | SPI2_NSS<br>I2S2_WS  | -          | USART3_CK    | -     | SEG12  | -      | -        | EVENT<br>OUT |

| PB13      | -      | -        | -        | TIM9_CH1       | -         | SPI2_SCK<br>I2S2_CK  | -          | USART3_CTS   | -     | SEG13  | -      | -        | EVENT<br>OUT |

| PB14      | -      | -        | -        | TIM9_CH2       | -         | SPI2_MISO            | -          | USART3_RTS   | -     | SEG14  | -      | -        | EVENT<br>OUT |

| PB15      | -      | -        | -        | TIM11_CH1      | -         | SPI2_MOSI<br>I2S2_SD | -          | -            | -     | SEG15  | -      | -        | EVENT<br>OUT |

| PC0       | -      | -        | -        | -              | -         |                      | -          | -            | -     | SEG18  | -      | TIMx_IC1 | EVENT<br>OUT |

| PC1       | -      | -        | -        | -              | -         | -                    | -          | -            | -     | SEG19  | -      | TIMx_IC2 | EVENT<br>OUT |

| PC2       | -      | -        | -        | -              | -         | -                    | -          | -            | -     | SEG20  | -      | TIMx_IC3 | EVENT<br>OUT |

| PC3       | -      | -        | -        | -              | -         | -                    | -          | -            | -     | SEG21  | -      | TIMx_IC4 | EVENT<br>OUT |

| PC4       | -      | -        | -        | -              | -         | -                    | -          | -            | -     | SEG22  | -      | TIMx_IC1 | EVENT<br>OUT |

| PC5       | -      | -        | -        | -              | -         | -                    | -          | -            | -     | SEG23  | -      | TIMx_IC2 | EVENT<br>OUT |

| PC6       | -      | -        | TIM3_CH1 | -              | -         | I2S2_MCK             | -          | -            | -     | SEG24  |        | TIMx_IC3 | EVENT<br>OUT |

| PC7       | -      | -        | TIM3_CH2 | -              | -         | -                    | I2S3_MCK   | -            | -     | SEG25  |        | TIMx_IC4 | EVENT<br>OUT |

| PC8       | -      | -        | тімз_снз | -              | -         | -                    | -          | -            | -     | SEG26  |        | TIMx_IC1 | EVENT<br>OUT |

| PC9       | -      | -        | TIM3_CH4 | -              | -         | -                    | -          | -            | -     | SEG27  |        | TIMx_IC2 | EVENT<br>OUT |

Pin descriptions

STM32L162xC/C-A

# 6 Electrical characteristics

# 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

#### 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 3.6$  V (for the 1.65 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

#### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

#### 6.1.4 Loading capacitor

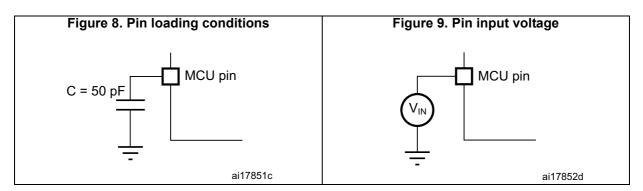

The loading conditions used for pin parameter measurement are shown in *Figure 8*.

#### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 9*.

| Symbol | Parameter                  | Conditions       | Min | Max | Unit |

|--------|----------------------------|------------------|-----|-----|------|

| т.     | Junction temperature range | 6 suffix version | -40 | 105 | °C   |

| TJ     |                            | 7 suffix version | -40 | 110 | C    |

#### Table 13. General operating conditions (continued)

1. When the ADC is used, refer to Table 55: ADC characteristics.

2. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up .

3. To sustain a voltage higher than VDD+0.3V, the internal pull-up/pull-down resistors must be disabled.

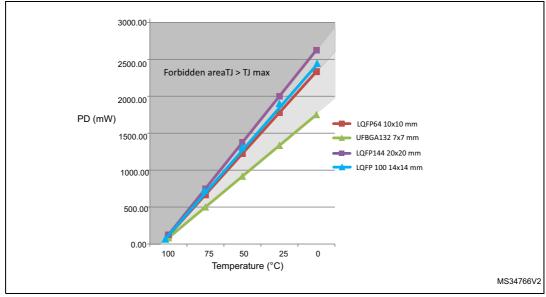

If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see Table 69: Thermal characteristics on page 124).

5. In low-power dissipation state,  $T_A$  can be extended to -40°C to 105°C temperature range as long as  $T_J$  does not exceed  $T_J$  max (see *Table 69: Thermal characteristics on page 124*).

## 6.3.2 Embedded reset and power control block characteristics

The parameters given in the following table are derived from the tests performed under the conditions summarized in *Table 13*.

| Symbol                               | Parameter                            | Conditions                          | Min  | Тур  | Мах  | Unit  |

|--------------------------------------|--------------------------------------|-------------------------------------|------|------|------|-------|

|                                      | V <sub>DD</sub> rise time rate       | BOR detector enabled                | 0    | -    | 8    |       |

| t <sub>VDD</sub> <sup>(1)</sup>      |                                      | BOR detector disabled               | 0    | -    | 1000 | μs/V  |

| ٩٥٩٠                                 | V <sub>DD</sub> fall time rate       | BOR detector enabled                | 20   | -    | ∞    | μ3/ ν |

|                                      |                                      | BOR detector disabled               | 0    | -    | 1000 |       |

| T <sub>RSTTEMPO</sub> <sup>(1)</sup> | Reset temporization                  | V <sub>DD</sub> rising, BOR enabled | -    | 2    | 3.3  | ms    |

| 'RSTTEMPO` '                         | V <sub>DD</sub> rising, BOR disabled |                                     | 0.4  | 0.7  | 1.6  | 1115  |

| N                                    | Power on/power down reset            | Falling edge                        | 1    | 1.5  | 1.65 |       |

| V <sub>POR/PDR</sub>                 | threshold                            | Rising edge                         | 1.3  | 1.5  | 1.65 |       |

| V                                    | Brown-out reset threshold 0          | Falling edge                        | 1.67 | 1.7  | 1.74 |       |

| V <sub>BOR0</sub>                    |                                      | Rising edge                         | 1.69 | 1.76 | 1.8  | v     |

| N/ -                                 | Brown-out reset threshold 1          | Falling edge                        | 1.87 | 1.93 | 1.97 | v     |

| V <sub>BOR1</sub>                    |                                      | Rising edge                         | 1.96 | 2.03 | 2.07 |       |

| N .                                  | Brown-out reset threshold 2          | Falling edge                        | 2.22 | 2.30 | 2.35 | 1     |

| V <sub>BOR2</sub>                    |                                      | Rising edge                         | 2.31 | 2.41 | 2.44 |       |

Table 14. Embedded reset and power control block characteristics

| Symbol                  | Parameter                                                                            | Conditions                                                              | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------|--------------------|------|

| t <sub>WUSLEEP</sub>    | Wakeup from Sleep mode                                                               | f <sub>HCLK</sub> = 32 MHz                                              | 0.4  | -                  |      |

| +                       | Wakeup from Low-power sleep                                                          | f <sub>HCLK</sub> = 262 kHz<br>Flash enabled                            | 46   | -                  |      |

| <sup>t</sup> wusleep_lp | mode, f <sub>HCLK</sub> = 262 kHz                                                    | f <sub>HCLK</sub> = 262 kHz<br>Flash switched OFF                       | 46   | -                  |      |

|                         | Wakeup from Stop mode,<br>regulator in Run mode<br>ULP bit = 1 and FWU bit = 1       | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz                          | 8.2  | -                  |      |

|                         |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 1 and 2 | 7.7  | 8.9                |      |

|                         | Wakeup from Stop mode,<br>regulator in low-power mode<br>ULP bit = 1 and FWU bit = 1 | f <sub>HCLK</sub> = f <sub>MSI</sub> = 4.2 MHz<br>Voltage range 3       | 8.2  | 13.1               | μs   |

| t <sub>WUSTOP</sub>     |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 2.1 MHz                          | 10.2 | 13.4               |      |

|                         |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 1.05 MHz                         | 16   | 20                 |      |

|                         |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 524 kHz                          | 31   | 37                 |      |

|                         |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 262 kHz                          | 57   | 66                 |      |

|                         |                                                                                      | f <sub>HCLK</sub> = f <sub>MSI</sub> = 131 kHz                          | 112  | 123                |      |

|                         |                                                                                      | f <sub>HCLK</sub> = MSI = 65 kHz                                        | 221  | 236                |      |

| tuniona                 | Wakeup from Standby mode<br>ULP bit = 1 and FWU bit = 1                              | f <sub>HCLK</sub> = MSI = 2.1 MHz                                       | 58   | 104                |      |

| twustdby                | Wakeup from Standby mode<br>FWU bit = 0                                              | f <sub>HCLK</sub> = MSI = 2.1 MHz                                       | 2.6  | 3.25               | ms   |

Table 25. Low-power mode wakeup timings

1. Guaranteed by characterization, unless otherwise specified

#### 6.3.6 External clock source characteristics

.

#### High-speed external user clock generated from an external source

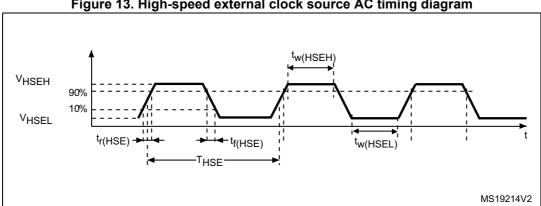

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO. The external clock signal has to respect the I/O characteristics in *Section 6.3.12*. However, the recommended clock input waveform is shown in *Figure 13*.

| Table 26 | High-speed | external | user clock | characteristics <sup>(1)</sup> |

|----------|------------|----------|------------|--------------------------------|

|          |            |          |            |                                |

| Symbol               | Parameter                               | Conditions                  | Min | Тур | Max | Unit |

|----------------------|-----------------------------------------|-----------------------------|-----|-----|-----|------|

| f <sub>HSE_ext</sub> | User external clock source<br>frequency | CSS is on or<br>PLL is used | 1   | 8   | 32  | MHz  |

|                      |                                         | CSS is off, PLL<br>not used | 0   | 8   | 32  | MHz  |

| Symbol                                       | Parameter                           | Conditions | Min         | Тур | Max                | Unit |

|----------------------------------------------|-------------------------------------|------------|-------------|-----|--------------------|------|

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage |            | $0.7V_{DD}$ | -   | $V_{DD}$           | V    |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage  |            | $V_{SS}$    | -   | $0.3V_{\text{DD}}$ |      |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time             |            | 12          | -   | -                  | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time            |            | -           | -   | 20                 | 115  |

| C <sub>in(HSE)</sub>                         | OSC_IN input capacitance            |            | -           | 2.6 | -                  | pF   |

Table 26. High-speed external user clock characteristics<sup>(1)</sup> (continued)

1. Guaranteed by design.

Figure 13. High-speed external clock source AC timing diagram

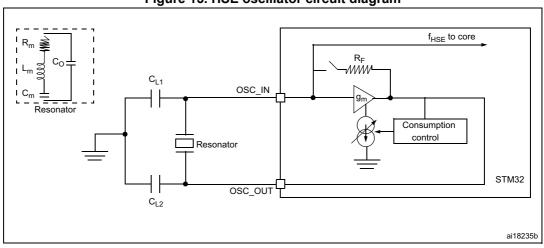

Figure 15. HSE oscillator circuit diagram

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 29*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                | Parameter                                                                                     | Conditions                            | Min | Тур    | Max | Unit |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------|---------------------------------------|-----|--------|-----|------|--|--|

| f <sub>LSE</sub>      | Low speed external oscillator<br>frequency                                                    | -                                     | -   | 32.768 | -   | kHz  |  |  |

| R <sub>F</sub>        | Feedback resistor                                                                             | -                                     | -   | 1.2    | -   | MΩ   |  |  |

| C <sup>(2)</sup>      | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(3)}$ | R <sub>S</sub> = 30 kΩ                | -   | 8      | -   | pF   |  |  |

| I <sub>LSE</sub>      | LSE driving current                                                                           | $V_{DD}$ = 3.3 V, $V_{IN}$ = $V_{SS}$ | -   | -      | 1.1 | μA   |  |  |

|                       |                                                                                               | V <sub>DD</sub> = 1.8 V               | -   | 450    | -   |      |  |  |

| I <sub>DD (LSE)</sub> | LSE oscillator current<br>consumption                                                         | V <sub>DD</sub> = 3.0 V               | -   | 600    | -   | nA   |  |  |

|                       |                                                                                               | V <sub>DD</sub> = 3.6V                | -   | 750    | -   |      |  |  |

| 9 <sub>m</sub>        | Oscillator transconductance                                                                   | -                                     | 3   | -      | -   | µA/V |  |  |

| $t_{SU(LSE)}^{(4)}$   | Startup time                                                                                  | $V_{\text{DD}}$ is stabilized         | -   | 1      | -   | S    |  |  |

| Table 29. L | SE oscillator | characteristics | (f <sub>LSE</sub> = 32.768 | kHz) <sup>(1)</sup> |

|-------------|---------------|-----------------|----------------------------|---------------------|

|-------------|---------------|-----------------|----------------------------|---------------------|

1. Guaranteed by characterization results.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value for example MSIV-TIN32.768kHz. Refer to crystal manufacturer for more details.

| Symbol                                | Parameter                          | Condition                                | Тур | Max | Unit |

|---------------------------------------|------------------------------------|------------------------------------------|-----|-----|------|

|                                       |                                    | MSI range 0                              | -   | 40  |      |

|                                       |                                    | MSI range 1                              | -   | 20  |      |

|                                       |                                    | MSI range 2                              | -   | 10  |      |

| t <sub>STAB(MSI)</sub> <sup>(2)</sup> |                                    | MSI range 3                              | -   | 4   |      |

|                                       | MSI oscillator stabilization time  | MSI range 4                              | -   | 2.5 | μs   |

|                                       |                                    | MSI range 5                              | -   | 2   |      |

|                                       |                                    | MSI range 6,<br>Voltage range 1<br>and 2 | -   | 2   |      |

|                                       |                                    | MSI range 3,<br>Voltage range 3          | -   | 3   |      |

| f <sub>OVER(MSI)</sub>                | MSI oscillator frequency overshoot | Any range to<br>range 5                  | -   | 4   | MHz  |

|                                       |                                    | Any range to range 6                     | -   | 6   |      |

Table 32. MSI oscillator characteristics (continued)

1. This is a deviation for an individual part, once the initial frequency has been measured.

2. Guaranteed by characterization results.

# 6.3.8 PLL characteristics

The parameters given in *Table 33* are derived from tests performed under the conditions summarized in *Table 13*.

| Cumhal                 | Devenueter                                              |     | Value |                    |        |  |

|------------------------|---------------------------------------------------------|-----|-------|--------------------|--------|--|

| Symbol                 | Parameter                                               | Min | Тур   | Max <sup>(1)</sup> | – Unit |  |

| £                      | PLL input clock <sup>(2)</sup>                          | 2   | -     | 24                 | MHz    |  |

| f <sub>PLL_IN</sub>    | PLL input clock duty cycle                              | 45  | -     | 55                 | %      |  |

| f <sub>PLL_OUT</sub>   | PLL output clock                                        | 2   | -     | 32                 | MHz    |  |

| t <sub>LOCK</sub>      | PLL lock time<br>PLL input = 16 MHz<br>PLL VCO = 96 MHz | -   | 115   | 160                | μs     |  |

| Jitter                 | Cycle-to-cycle jitter                                   | -   | -     | ±600               | ps     |  |

| I <sub>DDA</sub> (PLL) | Current consumption on V <sub>DDA</sub>                 | -   | 220   | 450                |        |  |

| I <sub>DD</sub> (PLL)  | Current consumption on V <sub>DD</sub>                  | -   | 120   | 150                | - μΑ   |  |

1. Guaranteed by characterization results.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{PLL_OUT}$ .

#### 6.3.9 Memory characteristics

The characteristics are given at  $T_A$  = -40 to 105 °C unless otherwise specified.

#### **RAM** memory

| Table 34. RAM and hardware regist | ers |

|-----------------------------------|-----|

|-----------------------------------|-----|

| Symbol | Parameter                          | Conditions           | Min  | Тур | Max | Unit |

|--------|------------------------------------|----------------------|------|-----|-----|------|

| VRM    | Data retention mode <sup>(1)</sup> | STOP mode (or RESET) | 1.65 | -   | -   | V    |

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

# 6.3.13 I/O port characteristics

#### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 48* are derived from tests performed under the conditions summarized in *Table 13*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                             | Conditions                                                                        | Min                                  | Тур                                                                                       | Max                | Unit |     |    |

|------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------|--------------------|------|-----|----|

| V <sub>IL</sub>  | Input low level voltage                               | -                                                                                 | _                                    | -                                                                                         | 0.3V <sub>DD</sub> |      |     |    |

|                  |                                                       | Standard I/O                                                                      | 0.7.\/                               | -                                                                                         | -                  | v    |     |    |

| $V_{\text{IH}}$  | Input high level voltage                              | FT I/O                                                                            | 0.7 V <sub>DD</sub>                  | -                                                                                         | -                  | v    |     |    |

|                  |                                                       | BOOT0 I/O                                                                         |                                      | -                                                                                         | -                  |      |     |    |

| V <sub>hys</sub> | I/O Schmitt trigger voltage hysteresis <sup>(2)</sup> | Standard I/O                                                                      | -                                    | 10%<br>V <sub>DD</sub> <sup>(3)</sup>                                                     | -                  |      |     |    |

|                  |                                                       | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with LCD                | -                                    | -                                                                                         | ±50                |      |     |    |

|                  |                                                       | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with analog<br>switches | -                                    | -                                                                                         | ±50                |      |     |    |

| l <sub>lkg</sub> | <sub>kg</sub> Input leakage current <sup>(4)</sup>    | Input leakage current <sup>(4)</sup>                                              | Input leakage current <sup>(4)</sup> | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with analog<br>switches and LCD | -                  | -    | ±50 | nA |

|                  |                                                       | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>I/Os with USB                | -                                    | -                                                                                         | ±250               |      |     |    |

|                  |                                                       | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>Standard I/Os                | -                                    | -                                                                                         | ±50                |      |     |    |

|                  |                                                       | FT I/O<br>V <sub>DD</sub> ≤ V <sub>IN</sub> ≤ 5V                                  | -                                    | -                                                                                         | ±10                | uA   |     |    |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(1)(5)</sup>    | $V_{IN} = V_{SS}$                                                                 | 30                                   | 45                                                                                        | 60                 | kΩ   |     |    |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(5)</sup>     | $V_{IN} = V_{DD}$                                                                 | 30                                   | 45                                                                                        | 60                 | kΩ   |     |    |

| C <sub>IO</sub>  | I/O pin capacitance                                   | -                                                                                 | -                                    | 5                                                                                         | -                  | pF   |     |    |

Table 42. I/O static characteristics

1. Guaranteed by test in production

2. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results.

3. With a minimum of 200 mV. Guaranteed by characterization results.

4. The max. value may be exceeded if negative current is injected on adjacent pins.

5. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS.

| Symbol                    | Parameter                                                                                                                                                       | Conditions                                                                                                    | Min | Тур          | Max          | Unit    |  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----|--------------|--------------|---------|--|

| dOffset/dT <sup>(1)</sup> | Offset error temperature coefficient (code 0x800)                                                                                                               | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0V$<br>$T_A = 0$ to 50 ° C<br>DAC output buffer OFF                         | -20 | -10          | 0            | - μV/°C |  |

|                           |                                                                                                                                                                 | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0V$<br>$T_A = 0 \text{ to } 50 ^{\circ}\text{C}$<br>DAC output buffer ON    | 0   | 20           | 50           |         |  |

| Gain <sup>(1)</sup>       | Gain error <sup>(7)</sup>                                                                                                                                       | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON                                    | -   | +0.1 / -0.2% | +0.2 / -0.5% | - %     |  |

|                           | Gain error                                                                                                                                                      | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                                                   | -   | +0 / -0.2%   | +0 / -0.4%   |         |  |

| dGain/dT <sup>(1)</sup>   | Gain error temperature                                                                                                                                          | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0V$<br>$T_A = 0 \text{ to } 50 \ ^{\circ}\text{C}$<br>DAC output buffer OFF | -10 | -2           | 0            | -μV/°C  |  |

|                           | coefficient                                                                                                                                                     | $V_{DDA} = 3.3V$<br>$V_{REF+} = 3.0V$<br>$T_A = 0 \text{ to } 50 ^{\circ}\text{C}$<br>DAC output buffer ON    | -40 | -8           | 0            |         |  |

| TUE <sup>(1)</sup>        | Total upadiusted error                                                                                                                                          | $C_{L} \le 50 \text{ pF}, R_{L} \ge 5 \text{ k}\Omega$<br>DAC output buffer ON                                | -   | 12           | 30           | - LSB   |  |

|                           | Total unadjusted error                                                                                                                                          | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                                                   | -   | 8            | 12           |         |  |

| tsettling                 | Settling time (full scale:<br>for a 12-bit code<br>transition between the<br>lowest and the highest<br>input codes till<br>DAC_OUT reaches final<br>value ±1LSB | $C_L ≤ 50 \text{ pF, } R_L ≥ 5 \text{ k}\Omega$                                                               | -   | 7            | 12           | μs      |  |

| Update rate               | Max frequency for a<br>correct DAC_OUT<br>change (95% of final<br>value) with 1 LSB<br>variation in the input<br>code                                           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                                            | -   | -            | 1            | Msps    |  |

| twakeup                   | Wakeup time from off<br>state (setting the ENx bit<br>in the DAC Control<br>register) <sup>(8)</sup>                                                            | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                                                            | -   | 9            | 15           | μs      |  |

| PSRR+                     | V <sub>DDA</sub> supply rejection<br>ratio (static DC<br>measurement)                                                                                           | $C_L \le 50 \text{ pF, } R_L \ge 5 \text{ k}\Omega$                                                           | -   | -60          | -35          | dB      |  |

Table 58. DAC characteristics (continued)

1. Data based on characterization results.

2. Connected between DAC\_OUT and  $\mathsf{V}_{\mathsf{SSA}}.$

3. Difference between two consecutive codes - 1 LSB.

| data   |             |        |        |                       |        |        |  |

|--------|-------------|--------|--------|-----------------------|--------|--------|--|

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |  |

|        | Min         | Тур    | Мах    | Min                   | Тур    | Max    |  |

| А      | -           | -      | 1.600  | -                     | -      | 0.0630 |  |

| A1     | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |  |

| D      | 21.800      | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.8740 |  |

| D1     | 19.800      | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |  |

| D3     | -           | 17.500 | -      | -                     | 0.6890 | -      |  |

| Е      | 21.800      | 22.000 | 22.200 | 0.8583                | 0.8661 | 0.8740 |  |

| E1     | 19.800      | 20.000 | 20.200 | 0.7795                | 0.7874 | 0.7953 |  |

| E3     | -           | 17.500 | -      | -                     | 0.6890 | -      |  |

| е      | -           | 0.500  | -      | -                     | 0.0197 | -      |  |

| L      | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -           | 1.000  | -      | -                     | 0.0394 | -      |  |

| k      | 0°          | 3.5°   | 7°     | 0°                    | 3.5°   | 7°     |  |

| CCC    | -           | -      | 0.080  | -                     | -      | 0.0031 |  |

# Table 65. LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

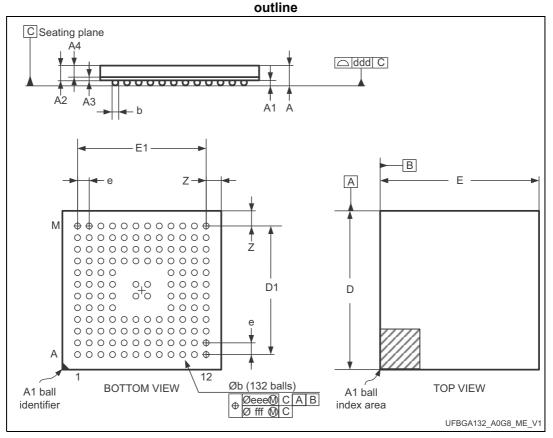

# 7.4 UFBGA132, 7 x 7 mm, 132-ball ultra thin, fine-pitch ball grid array package information

Figure 39. UFBGA132, 7 x 7 mm, 132-ball ultra thin, fine-pitch ball grid array package

1. Drawing is not to scale.

# Table 68. UFBGA132, 7 x 7 mm, 132-ball ultra thin, fine-pitch ball grid arraypackage mechanical data

| F      |             |       |       |                       |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|        | Min         | Тур   | Max   | Min                   | Тур    | Мах    |  |

| А      | 0.460       | 0.530 | 0.600 | 0.0181                | 0.0209 | 0.0236 |  |

| A1     | 0.050       | 0.080 | 0.110 | 0.0020                | 0.0031 | 0.0043 |  |

| A2     | 0.400       | 0.450 | 0.500 | 0.0157                | 0.0177 | 0.0197 |  |

| A3     | 0.270       | 0.320 | 0.370 | 0.0106                | 0.0126 | 0.0146 |  |

| b      | 0.170       | 0.280 | 0.330 | 0.0067                | 0.0110 | 0.0130 |  |

| D      | 6.950       | 7.000 | 7.050 | 0.2736                | 0.2756 | 0.2776 |  |

| Е      | 6.950       | 7.000 | 7.050 | 0.2736                | 0.2756 | 0.2776 |  |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |  |

| F      | 0.700       | 0.750 | 0.800 | 0.0276                | 0.0295 | 0.0315 |  |

DocID026175 Rev 4

# 7.5 Thermal characteristics

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max \times \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                                  | Value | Unit |  |

|-----------------|----------------------------------------------------------------------------|-------|------|--|

| Θ <sub>JA</sub> | Thermal resistance junction-ambient<br>LQFP144 - 20 x 20 mm / 0.5 mm pitch | 40    |      |  |

|                 | <b>Thermal resistance junction-ambient</b><br>UFBGA132 - 7 x 7 mm          | 60    | °C/W |  |

|                 | Thermal resistance junction-ambient<br>LQFP100 - 14 x 14 mm / 0.5 mm pitch | 43    | 0/11 |  |

|                 | Thermal resistance junction-ambient<br>LQFP64 - 10 x 10 mm / 0.5 mm pitch  | 46    |      |  |

Table 69. Thermal characteristics

Figure 42. Thermal resistance suffix 6