# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-VDFN Exposed Pad                                                       |

| Supplier Device Package    | 8-DFN-S (6x5)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f635-e-mf |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

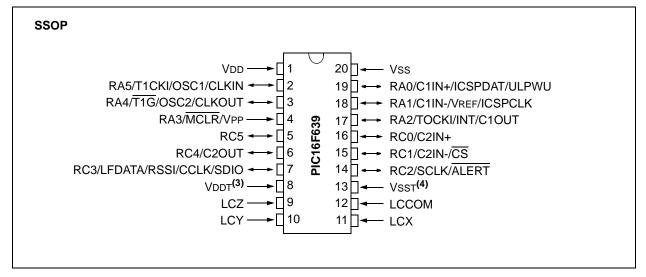

#### 20-Pin Diagram

| TABLE 4: 20-PIN SUMMARY |

|-------------------------|

|-------------------------|

| I/O                | Pin | Analog Front-End | Comparators | Timer | Interrupts | Pull-ups | Basic           |

|--------------------|-----|------------------|-------------|-------|------------|----------|-----------------|

| RA0                | 19  |                  | C1IN+       | _     | IOC        | Y        | ICSPDAT/ULPWU   |

| RA1                | 18  | —                | C1IN-       | _     | IOC        | Y        | VREF/ICSPCLK    |

| RA2                | 17  | —                | C1OUT       | T0CKI | INT/IOC    | Y        | —               |

| RA3 <sup>(1)</sup> | 4   | _                | _           | _     | IOC        | Y(2)     | MCLR/Vpp        |

| RA4                | 3   | —                | —           | T1G   | IOC        | Y        | OSC2/CLKOUT     |

| RA5                | 2   |                  | —           | T1CKI | IOC        | Y        | OSC1/CLKIN      |

| RC0                | 16  | —                | C2IN+       | —     | —          | -        | —               |

| RC1                | 15  | —                | C2IN-       | —     | —          | —        | CS              |

| RC2                | 14  | ALERT            | —           | —     | —          | _        | SCLK            |

| RC3                | 7   | LFDATA/RSSI      | —           | —     | _          |          | CCLK/SDIO       |

| RC4                | 6   |                  | C2OUT       | —     |            |          | —               |

| RC5                | 5   |                  | —           | —     | —          |          | —               |

| _                  | 8   | —                | —           | —     | —          | -        | Vddt(3)         |

| —                  | 13  |                  | —           | —     | —          |          | Vsst <b>(4)</b> |

|                    | 11  | LCX              | —           | —     | —          |          | —               |

| —                  | 10  | LCY              | —           | —     | _          |          | —               |

| —                  | 9   | LCZ              | —           |       | _          | _        | —               |

| —                  | 12  | LCCOM            |             | _     | _          | _        | _               |

|                    | 1   | _                | _           | _     | _          | _        | Vdd             |

|                    | 20  |                  |             | _     | _          | —        | Vss             |

Note 1: Input only.

2: Only when pin is configured for external MCLR.

**3:** VDDT is the supply voltage of the Analog Front-End section (PIC16F639 only). VDDT is treated as VDD in this document unless otherwise stated.

4: VSST is the ground reference voltage of the Analog Front-End section (PIC16F639 only). VSST is treated as VSS in this document unless otherwise stated.

#### TABLE 1-3: PIC16F639 PINOUT DESCRIPTIONS

| Name                                                                 | Function | Input<br>Type   | Output<br>Type | Description                                                                                                                                            |

|----------------------------------------------------------------------|----------|-----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCCOM                                                                | LCCOM    | AN              | -              | Common reference for analog inputs.                                                                                                                    |

| LCX                                                                  | LCX      | AN              | —              | 125 kHz analog X channel input.                                                                                                                        |

| LCY                                                                  | LCY      | AN              | _              | 125 kHz analog Y channel input.                                                                                                                        |

| LCZ                                                                  | LCZ      | AN              | _              | 125 kHz analog Z channel input.                                                                                                                        |

| RA0/C1IN+/ICSPDAT/ULPWU                                              | RA0      | TTL             | _              | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up/pull-down.<br>Selectable Ultra Low-Power Wake-up pin. |

|                                                                      | C1IN+    | AN              | —              | Comparator1 input – positive.                                                                                                                          |

|                                                                      | ICSPDAT  | TTL             | CMOS           | Serial Programming Data IO.                                                                                                                            |

|                                                                      | ULPWU    | AN              | —              | Ultra Low-Power Wake-up input.                                                                                                                         |

| RA1/C1IN-/VREF/ICSPCLK                                               | RA1      | TTL             | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up/pull-down.                                            |

|                                                                      | C1IN-    | AN              | —              | Comparator1 input – negative.                                                                                                                          |

|                                                                      | VREF     | AN              | _              | External voltage reference                                                                                                                             |

|                                                                      | ICSPCLK  | ST              | —              | Serial Programming Clock.                                                                                                                              |

| RA2/T0CKI/INT/C1OUT                                                  | RA2      | ST              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up/pull-down.                                            |

|                                                                      | TOCKI    | ST              | —              | External clock for Timer0.                                                                                                                             |

|                                                                      | INT      | ST              | —              | External Interrupt.                                                                                                                                    |

|                                                                      | C1OUT    | _               | CMOS           | Comparator1 output.                                                                                                                                    |

| RA3/MCLR/Vpp                                                         | RA3      | TTL             | —              | General purpose input. Individually controlled interrupt-on-change.                                                                                    |

|                                                                      | MCLR     | ST              | -              | Master Clear Reset. Pull-up enabled when configured as MCLF                                                                                            |

|                                                                      | Vpp      | HV              | —              | Programming voltage.                                                                                                                                   |

| RA4/T1G/OSC2/CLKOUT                                                  | RA4      | TTL             | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up/pull-down.                                            |

|                                                                      | T1G      | ST              | —              | Timer1 gate.                                                                                                                                           |

|                                                                      | OSC2     |                 | XTAL           | XTAL connection.                                                                                                                                       |

|                                                                      | CLKOUT   | _               | CMOS           | Tosc reference clock.                                                                                                                                  |

| RA5/T1CKI/OSC1/CLKIN                                                 | RA5      | TTL             | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up/pull-down.                                            |

|                                                                      | T1CKI    | ST              | _              | Timer1 clock.                                                                                                                                          |

|                                                                      | OSC1     | XTAL            | _              | XTAL connection.                                                                                                                                       |

|                                                                      | CLKIN    | ST              | _              | Tosc/4 reference clock.                                                                                                                                |

| RC0/C2IN+                                                            | RC0      | TTL             | CMOS           | General purpose I/O.                                                                                                                                   |

|                                                                      | C2IN+    | AN              | _              | Comparator1 input – positive.                                                                                                                          |

| RC1/C2IN-/CS                                                         | RC1      | TTL             | CMOS           | General purpose I/O.                                                                                                                                   |

|                                                                      | C2IN-    | AN              |                | Comparator1 input – negative.                                                                                                                          |

|                                                                      | CS       | TTL             | —              | Chip select input for SPI communication with internal pull-up resistor.                                                                                |

| RC2/SCLK/ALERT                                                       | RC2      | TTL             | CMOS           | General purpose I/O.                                                                                                                                   |

|                                                                      | SCLK     | TTL             | —              | Digital clock input for SPI communication.                                                                                                             |

|                                                                      | ALERT    |                 | OD             | Output with internal pull-up resistor for AFE error signal.                                                                                            |

| Legend: AN = Analog input<br>HV = High Voltage<br>TTL = TTL compatil |          | CM<br>ST<br>XTA | = Sch          | OS compatible input or output D = Direct<br>mitt Trigger input with CMOS levels OD = Open Drain<br>stal                                                |

| Name                                                                                  | Function | Input<br>Type | Output<br>Type                                                                                 | Description                                                                                                     |  |  |  |  |  |

|---------------------------------------------------------------------------------------|----------|---------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| RC3/LFDATA/RSSI/CCLK/SDO                                                              | RC3      | TTL           | CMOS                                                                                           | General purpose I/O.                                                                                            |  |  |  |  |  |

|                                                                                       | LFDATA   |               | CMOS                                                                                           | Digital output representation of analog input signal to LC pins.                                                |  |  |  |  |  |

|                                                                                       | RSSI     |               | Received signal strength indicator. Analog current that is<br>proportional to input amplitude. |                                                                                                                 |  |  |  |  |  |

|                                                                                       | CCLK     | _             | —                                                                                              | Carrier clock output.                                                                                           |  |  |  |  |  |

|                                                                                       | SDIO     | TTL           | CMOS                                                                                           | Input/Output for SPI communication.                                                                             |  |  |  |  |  |

| RC4/C2OUT                                                                             | RC4      | TTL           | CMOS                                                                                           | General purpose I/O.                                                                                            |  |  |  |  |  |

|                                                                                       | C2OUT    | _             | CMOS                                                                                           | Comparator2 output.                                                                                             |  |  |  |  |  |

| RC5                                                                                   | RC5      | TTL           | CMOS                                                                                           | General purpose I/O.                                                                                            |  |  |  |  |  |

| VDDT                                                                                  | Vddt     | D             | —                                                                                              | Power supply for Analog Front-End. In this document, VDDT is treated the same as VDD, unless otherwise stated.  |  |  |  |  |  |

| Vsst                                                                                  | VSST     | D             | —                                                                                              | Ground reference for Analog Front-End. In this document, VSST treated the same as VSS, unless otherwise stated. |  |  |  |  |  |

| Vdd                                                                                   | Vdd      | D             | —                                                                                              | Power supply for microcontroller.                                                                               |  |  |  |  |  |

| Vss                                                                                   | Vss      | D             | _                                                                                              | Ground reference for microcontroller.                                                                           |  |  |  |  |  |

| Legend: AN = Analog input or output CMOS = CMOS compatible input or output D = Direct |          |               |                                                                                                |                                                                                                                 |  |  |  |  |  |

#### PIC16F639 PINOUT DESCRIPTIONS (CONTINUED) **TABLE 1-3:**

HV = High Voltage TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

OD = Open Drain

XTAL = Crystal

| Addr   | Name   | Bit 7       | Bit 6          | Bit 5         | Bit 4          | Bit 3          | Bit 2         | Bit 1     | Bit 0               | Value on<br>POR/BOR/<br>WUR | Page    |

|--------|--------|-------------|----------------|---------------|----------------|----------------|---------------|-----------|---------------------|-----------------------------|---------|

| Bank ( | )      |             |                |               |                |                |               |           |                     |                             |         |

| 00h    | INDF   |             | this location  |               | XXXX XXXX      | 32,137         |               |           |                     |                             |         |

| 01h    | TMR0   | Timer0 Mod  | dule Registe   |               | xxxx xxxx      | 61,137         |               |           |                     |                             |         |

| 02h    | PCL    | Program C   | ounter's (PC   | c) Least Sigr | nificant Byte  |                |               |           |                     | 0000 0000                   | 32,137  |

| 03h    | STATUS | IRP         | RP1            | RP0           | TO             | PD             | Z             | DC        | С                   | 0001 1xxx                   | 26,137  |

| 04h    | FSR    | Indirect Da | ta Memory A    | Address Poir  | nter           | •              | •             | •         |                     | XXXX XXXX                   | 32,137  |

| 05h    | GPIO   | —           | _              | GP5           | GP4            | GP3            | GP2           | GP1       | GP0                 | xx xx00                     | 47,137  |

| 06h    | _      | Unimpleme   | ented          |               |                |                | •             | •         |                     | —                           | _       |

| 07h    | _      | Unimpleme   | ented          |               |                |                |               |           |                     | _                           | _       |

| 08h    | _      | Unimpleme   | ented          |               |                |                |               |           |                     | _                           | _       |

| 09h    | _      | Unimpleme   | ented          |               |                |                |               |           |                     | _                           | _       |

| 0Ah    | PCLATH | _           | _              | _             | Write Buffer   | for upper 5 b  | its of Progra | m Counter |                     | 0 0000                      | 32,137  |

| 0Bh    | INTCON | GIE         | PEIE           | TOIE          | INTE           | RAIE           | T0IF          | INTF      | RAIF <sup>(2)</sup> | 0000 000x                   | 28,137  |

| 0Ch    | PIR1   | EEIF        | LVDIF          | CRIF          | _              | C1IF           | OSFIF         | —         | TMR1IF              | 000- 00-0                   | 30,137  |

| 0Dh    |        | Unimpleme   | ented          |               |                | 1              |               |           |                     |                             |         |

| 0Eh    | TMR1L  | Holding Re  | gister for the | e Least Sign  | ificant Byte o | f the 16-bit T | MR1           |           |                     | xxxx xxxx                   | 64,137  |

| 0Fh    | TMR1H  | Holding Re  | gister for the | e Most Signi  | ficant Byte of | the 16-bit TM  | /IR1          |           |                     | xxxx xxxx                   | 64,137  |

| 10h    | T1CON  | T1GINV      | TMR1GE         | T1CKPS1       | T1CKPS0        | T1OSCEN        | T1SYNC        | TMR1CS    | TMR10N              | 0000 0000                   | 68,137  |

| 11h    | _      | Unimpleme   | ented          |               | 1              |                |               |           |                     | _                           | _       |

| 12h    | _      | Unimpleme   | ented          |               |                |                |               |           |                     | _                           | _       |

| 13h    | _      | Unimpleme   | ented          |               |                |                |               |           |                     | _                           | _       |

| 14h    | _      | Unimpleme   | ented          |               |                |                |               |           |                     | _                           | _       |

| 15h    | _      | Unimpleme   | ented          |               |                |                |               |           |                     | _                           | _       |

| 16h    | _      | Unimpleme   | ented          |               |                |                |               |           |                     | _                           | _       |

| 17h    | _      | Unimpleme   | ented          |               |                |                |               |           |                     | _                           | _       |

| 18h    | WDTCON | _           | _              | _             | WDTPS3         | WDTPS2         | WDTPS1        | WDTPS0    | SWDTEN              | 0 1000                      | 144,137 |

| 19h    | CMCON0 | _           | COUT           | -             | CINV           | CIS            | CM2           | CM1       | CM0                 | -0-0 0000                   | 79,137  |

| 1Ah    | CMCON1 | _           | _              | -             | _              | _              | _             | T1GSS     | CMSYNC              | 10                          | 82,137  |

| 1Bh    | _      | Unimpleme   | ented          |               |                |                |               |           |                     | _                           | _       |

| 1Ch    | _      | Unimpleme   | ented          |               |                |                |               |           |                     | _                           | _       |

| 1Dh    |        | Unimpleme   | ented          |               |                |                |               |           |                     | _                           | _       |

| 1Eh    | _      | Unimpleme   | ented          |               |                |                |               |           |                     | _                           | _       |

| 1Fh    | _      | Unimpleme   | ented          |               |                |                |               |           |                     | _                           | _       |

Legend: Note

1:

– = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

<u>Other (non Power-up)</u> Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

MCLR and WDT Reset do not affect the previous value data latch. The RAIF bit will be cleared upon Reset but will set again if the mismatch or units. 2: match exists.

#### 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains:

- the arithmetic status of the ALU

- the Reset status

- the bank select bits for data memory (GPR and SFR)

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS, will clear the upper three bits and set the Z bit. This leaves the STATUS register as '000u u1uu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits, see **Section 13.0 "Instruction Set Summary"**

| Note 1: | The C and DC bits operate as a Borrow      |

|---------|--------------------------------------------|

|         | and Digit Borrow out bit, respectively, in |

|         | subtraction.                               |

### REGISTER 2-1: STATUS: STATUS REGISTER

| R/W-0      | 0 R/W-0                                                         | R/W-0                                                                                  | R-1             | R-1              | R/W-x           | R/W-x             | R/W-x            |  |  |  |  |

|------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------|------------------|-----------------|-------------------|------------------|--|--|--|--|

| IRP        | RP1                                                             | RP0                                                                                    | TO              | PD               | Z               | DC <sup>(1)</sup> | C <sup>(1)</sup> |  |  |  |  |

| bit 7      |                                                                 |                                                                                        |                 |                  |                 |                   | bit C            |  |  |  |  |

| Legend:    |                                                                 |                                                                                        |                 |                  |                 |                   |                  |  |  |  |  |

| R = Read   | able bit                                                        | W = Writable I                                                                         | bit             | U = Unimple      | mented bit, rea | d as '0'          |                  |  |  |  |  |

| -n = Value | e at POR                                                        | '1' = Bit is set                                                                       |                 | '0' = Bit is cle | eared           | x = Bit is unkr   | nown             |  |  |  |  |

| bit 7      | IRP: Registe                                                    | r Bank Select bi                                                                       | t (used for inc | direct addressi  | ng)             |                   |                  |  |  |  |  |

|            | 1 = Bank 2, 3<br>0 = Bank 0, 7                                  | 3 (100h-1FFh)<br>1 (00h-FFh)                                                           |                 |                  |                 |                   |                  |  |  |  |  |

| bit 6-5    |                                                                 | egister Bank Sel                                                                       | ect bits (used  | for direct add   | ressing)        |                   |                  |  |  |  |  |

|            | 00 = Bank 0<br>01 = Bank 1                                      | · · · ·                                                                                |                 |                  |                 |                   |                  |  |  |  |  |

|            | 10 = Bank 2                                                     | • •                                                                                    |                 |                  |                 |                   |                  |  |  |  |  |

|            | 11 = Bank 3                                                     | ,                                                                                      |                 |                  |                 |                   |                  |  |  |  |  |

| bit 4      |                                                                 | <b>TO:</b> Time-out bit<br>1 = After power-up, CLRWDT instruction or SLEEP instruction |                 |                  |                 |                   |                  |  |  |  |  |

|            |                                                                 | ver-up, CLRWDT                                                                         |                 | SLEEP INStruc    | Ction           |                   |                  |  |  |  |  |

| bit 3      | PD: Power-d                                                     | own bit                                                                                | -               |                  |                 |                   |                  |  |  |  |  |

|            |                                                                 | ver-up or by the                                                                       |                 | uction           |                 |                   |                  |  |  |  |  |

|            | -                                                               | Ition of the SLEE                                                                      | EP instruction  |                  |                 |                   |                  |  |  |  |  |

| bit 2      | Z: Zero bit                                                     | It of an arithmat                                                                      | ia ar lagia any | ration in zora   |                 |                   |                  |  |  |  |  |

|            |                                                                 | It of an arithmet<br>It of an arithmet                                                 | • •             |                  | ero             |                   |                  |  |  |  |  |

| bit 1      |                                                                 | rry/Borrow bit (A                                                                      | •               |                  |                 | (1)               |                  |  |  |  |  |

|            |                                                                 | out from the 4th                                                                       |                 |                  | curred          |                   |                  |  |  |  |  |

|            | •                                                               | -out from the 4th                                                                      |                 |                  |                 | 0                 |                  |  |  |  |  |

| bit 0      | •                                                               | row bit <sup>(1)</sup> (ADDW                                                           |                 |                  |                 | ')                |                  |  |  |  |  |

|            |                                                                 | out from the Mos<br>-out from the Mo                                                   |                 |                  |                 |                   |                  |  |  |  |  |

| Note 1:    | For Borrow, the po<br>second operand. I<br>bit of the source re | For rotate (RRF, 1                                                                     |                 |                  |                 |                   |                  |  |  |  |  |

## 3.6 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bit of the OSCCON register.

#### 3.6.1 SYSTEM CLOCK SELECT (SCS) BIT

The System Clock Select (SCS) bit of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bit of the OSCCON register = 0, the system clock source is determined by configuration of the FOSC<2:0> bits in the Configuration Word register (CONFIG).

- When the SCS bit of the OSCCON register = 1, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<2:0> bits of the OSCCON register. After a Reset, the SCS bit of the OSCCON register is always cleared.

- Note: Any automatic clock switch, which may occur from Two-Speed Start-up or Fail-Safe Clock Monitor, does not update the SCS bit of the OSCCON register. The user can monitor the OSTS bit of the OSCCON register to determine the current system clock source.

## 3.6.2 OSCILLATOR START-UP TIME-OUT STATUS (OSTS) BIT

The Oscillator Start-up Time-out Status (OSTS) bit of the OSCCON register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word register (CONFIG), or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes.

#### 3.7 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device.

This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC as the clock source and go back to Sleep without waiting for the primary oscillator to become stable.

Note: Executing a SLEEP instruction will abort the oscillator start-up time and will cause the OSTS bit of the OSCCON register to remain clear. When the Oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) is enabled (see **Section 3.4.1 "Oscillator Start-up Timer (OST)"**). The OST will suspend program execution until 1024 oscillations are counted. Two-Speed Start-up mode minimizes the delay in code execution by operating from the internal oscillator as the OST is counting. When the OST count reaches 1024 and the OSTS bit of the OSCCON register is set, program execution switches to the external oscillator.

## 3.7.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Word register) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 0.

- FOSC<2:0> bits in the Configuration Word register (CONFIG) configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- Wake-up from Sleep.

If the external clock oscillator is configured to be anything other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

#### 3.7.2 TWO-SPEED START-UP SEQUENCE

- 1. Wake-up from Power-on Reset or Sleep.

- Instructions begin execution by the internal oscillator at the frequency set in the IRCF<2:0> bits of the OSCCON register.

- 3. OST enabled to count 1024 clock cycles.

- 4. OST timed out, wait for falling edge of the internal oscillator.

- 5. OSTS is set.

- 6. System clock held low until the next falling edge of new clock (LP, XT or HS mode).

- 7. System clock is switched to external clock source.

### 3.8 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM can detect oscillator failure any time after the Oscillator Start-up Timer (OST) has expired. The FSCM is enabled by setting the FCMEN bit in the Configuration Word register (CONFIG). The FSCM is applicable to all external oscillator modes (LP, XT, HS, EC, RC and RCIO).

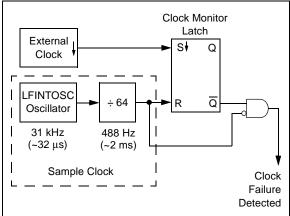

FIGURE 3-8: FSCM BLOCK DIAGRAM

#### 3.8.1 FAIL-SAFE DETECTION

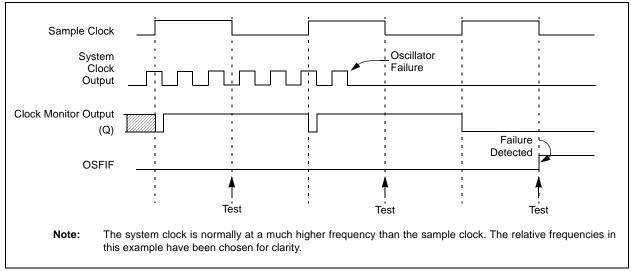

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 3-8. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the primary clock goes low.

#### 3.8.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM switches the device clock to an internal clock source and sets the bit flag OSFIF of the PIR1 register. Setting this flag will generate an interrupt if the OSFIE bit of the PIE1 register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation.

The internal clock source chosen by the FSCM is determined by the IRCF<2:0> bits of the OSCCON register. This allows the internal oscillator to be configured before a failure occurs.

#### 3.8.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or toggling the SCS bit of the OSCCON register. When the SCS bit is toggled, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON. When the OST times out, the Fail-Safe condition is cleared and the device will be operating from the external clock source. The Fail-Safe condition must be cleared before the OSFIF flag can be cleared.

#### 3.8.4 RESET OR WAKE-UP FROM SLEEP

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC or RC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed. When the FSCM is enabled, the Two-Speed Start-up is also enabled. Therefore, the device will always be executing code while the OST is operating.

| Note: | Due to the wide range of oscillator start-up<br>times, the Fail-Safe circuit is not active<br>during oscillator start-up (i.e., after exiting<br>Reset or Sleep). After an appropriate<br>amount of time, the user should check the<br>OSTS bit of the OSCCON register to verify |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | the oscillator start-up and that the system clock switchover has successfully completed.                                                                                                                                                                                         |

#### FIGURE 3-9: FSCM TIMING DIAGRAM

| Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4               | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets <sup>(1)</sup> |

|-----------------------|-------|-------|-------|---------------------|-------|-------|-------|--------|----------------------|------------------------------------------------|

| CONFIG <sup>(2)</sup> | CPD   | CP    | MCLRE | PWRTE               | WDTE  | FOSC2 | FOSC1 | FOSC0  | _                    | _                                              |

| INTCON                | GIE   | PEIE  | TOIE  | INTE                | RAIE  | T0IF  | INTF  | RAIF   | x000 000x            | 0000 000x                                      |

| OSCCON                | —     | IRCF2 | IRCF1 | IRCF0               | OSTS  | HTS   | LTS   | SCS    | -110 x000            | -110 x000                                      |

| OSCTUNE               | —     | —     | —     | TUN4                | TUN3  | TUN2  | TUN1  | TUN0   | 0 0000               | u uuuu                                         |

| PIE1                  | EEIE  | LVDIE | CRIE  | C2IE <sup>(3)</sup> | C1IE  | OSFIE | —     | TMR1IE | 000- 00-0            | 000- 00-0                                      |

| PIR1                  | EEIF  | LVDIF | CRIF  | C2IF <sup>(3)</sup> | C1IF  | OSFIF | —     | TMR1IF | 000- 00-0            | 000- 00-0                                      |

$\label{eq:local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_$

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: See Configuration Word register (CONFIG) for operation of all register bits.

3: PIC16F636/639 only.

## 7.4 Comparator Control

The CMCON0 register (Register 7-1) provides access to the following comparator features:

- Mode selection

- Output state

- Output polarity

- Input switch

#### 7.4.1 COMPARATOR OUTPUT STATE

Each comparator state can always be read internally via the CxOUT bit of the CMCON0 register. The comparator state may also be directed to the CxOUT pin in the following modes:

#### PIC12F635

- CM<2:0> = 001

- CM<2:0> = 011

- CM<2:0> = 101

#### PIC16F636/639

• CM<2:0> = 110

When one of the above modes is selected, the associated TRIS bit of the CxOUT pin must be cleared.

#### 7.4.2 COMPARATOR OUTPUT POLARITY

Inverting the output of a comparator is functionally equivalent to swapping the comparator inputs. The polarity of a comparator output can be inverted by setting the CXINV bit of the CMCON0 register. Clearing CXINV results in a non-inverted output. A complete table showing the output state versus input conditions and the polarity bit is shown in Table 7-1.

## TABLE 7-1: OUTPUT STATE VS. INPUT CONDITIONS

| Input Conditions | CxINV | CxOUT |

|------------------|-------|-------|

| VIN- > VIN+      | 0     | 0     |

| VIN- < VIN+      | 0     | 1     |

| VIN- > VIN+      | 1     | 1     |

| VIN- < VIN+      | 1     | 0     |

**Note:** CxOUT refers to both the register bit and output pin.

## 7.4.3 COMPARATOR INPUT SWITCH

The inverting input of the comparators may be switched between two analog pins in the following modes:

### PIC12F635

- CM<2:0> = 101

- CM<2:0> = 110

#### PIC16F636/639

- CM<2:0> = 001 (Comparator C1 only)

- CM<2:0> = 010 (Comparators C1 and C2)

In the above modes, both pins remain in Analog mode regardless of which pin is selected as the input. The CIS bit of the CMCON0 register controls the comparator input switch.

| R-0                                                                                                                | R-0                              | R/W-0                              | R/W-0          | R/W-0            | R/W-0           | R/W-0          | R/W-0 |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------------|----------------|------------------|-----------------|----------------|-------|

| C2OUT                                                                                                              | C1OUT                            | C2INV                              | C1INV          | CIS              | CM2             | CM1            | CM0   |

| bit 7                                                                                                              |                                  |                                    |                |                  |                 |                | bit 0 |

|                                                                                                                    |                                  |                                    |                |                  |                 |                |       |

| Legend:                                                                                                            |                                  |                                    |                |                  |                 |                |       |

| R = Readable                                                                                                       | e bit                            | W = Writable                       | bit            | U = Unimpler     | mented bit, rea | d as '0'       |       |

| -n = Value at                                                                                                      | POR                              | '1' = Bit is set                   |                | '0' = Bit is cle | eared           | x = Bit is unk | nown  |

|                                                                                                                    |                                  |                                    |                |                  |                 |                |       |

| bit 7                                                                                                              |                                  | parator 2 Outp                     | ut bit         |                  |                 |                |       |

|                                                                                                                    | When C2INV                       |                                    |                |                  |                 |                |       |

|                                                                                                                    | 1 = C2 VIN+ ><br>0 = C2 VIN+ <   |                                    |                |                  |                 |                |       |

|                                                                                                                    | When C2INV                       | -                                  |                |                  |                 |                |       |

|                                                                                                                    | 1 = C2 VIN+ <                    |                                    |                |                  |                 |                |       |

|                                                                                                                    | 0 = C2 VIN+ >                    |                                    |                |                  |                 |                |       |

| bit 6                                                                                                              | C1OUT: Com                       | parator 1 Outp                     | ut bit         |                  |                 |                |       |

|                                                                                                                    | When C1INV                       | = 0:                               |                |                  |                 |                |       |

|                                                                                                                    | 1 = C1 VIN+ >                    |                                    |                |                  |                 |                |       |

|                                                                                                                    | 0 = C1 VIN+ <                    |                                    |                |                  |                 |                |       |

|                                                                                                                    | When C1INV                       |                                    |                |                  |                 |                |       |

|                                                                                                                    | 1 = C1 VIN+ <<br>0 = C1 VIN+ >   |                                    |                |                  |                 |                |       |

| bit 5                                                                                                              |                                  | parator 2 Outpu                    | t Inversion bi | t                |                 |                |       |

| 2.1.0                                                                                                              | 1 = C2 output                    | =                                  |                | -                |                 |                |       |

|                                                                                                                    | 0 = C2 output                    |                                    |                |                  |                 |                |       |

| bit 4                                                                                                              | C1INV: Comp                      | parator 1 Outpu                    | t Inversion bi | t                |                 |                |       |

|                                                                                                                    | 1 = C1 Outpu                     |                                    |                |                  |                 |                |       |

|                                                                                                                    | 0 = C1 Outpu                     | it not inverted                    |                |                  |                 |                |       |

| bit 3                                                                                                              | CIS: Comparator Input Switch bit |                                    |                |                  |                 |                |       |

|                                                                                                                    | <u>When CM&lt;2:0&gt; = 010:</u> |                                    |                |                  |                 |                |       |

|                                                                                                                    |                                  | nnects to C1 V                     |                |                  |                 |                |       |

|                                                                                                                    |                                  | onnects to C2 V<br>nnects to C1 VI |                |                  |                 |                |       |

|                                                                                                                    |                                  | nnects to C2 V                     |                |                  |                 |                |       |

|                                                                                                                    | When CM<2:                       |                                    |                |                  |                 |                |       |

|                                                                                                                    |                                  | nnects to C1 V                     |                |                  |                 |                |       |

|                                                                                                                    |                                  | nnects to C1 VI                    |                | 7 5)             |                 |                |       |

| bit 2-0                                                                                                            |                                  | mparator Mode                      |                |                  | la a            |                |       |

|                                                                                                                    |                                  | inputs multiple                    |                | nfigured as anal | log             |                |       |

|                                                                                                                    |                                  | puts multiplexe                    |                | •                |                 |                |       |

|                                                                                                                    | 011 = Two co                     | ommon referen                      | ce comparato   |                  |                 |                |       |

|                                                                                                                    |                                  | dependent com                      | •              |                  |                 |                |       |

| <ul><li>101 = One independent comparator</li><li>110 = Two comparators with outputs and common reference</li></ul> |                                  |                                    |                |                  |                 |                |       |

|                                                                                                                    |                                  |                                    |                | figured as digit |                 |                |       |

|                                                                                                                    |                                  |                                    | 1              | <u>.</u>         |                 |                |       |

#### REGISTER 7-2: CMCON0: COMPARATOR CONFIGURATION REGISTER (PIC16F636/639)

NOTES:

#### 11.20 Soft Reset

The AFE issues a Soft Reset in the following events:

- a) After Power-on Reset (POR),

- b) After Inactivity timer time-out,

- c) If an "Abort" occurs,

- d) After receiving SPI Soft Reset command.

The "Abort" occurs if there is no positive signal detected at the end of the AGC stabilization period (TAGC). The Soft Reset initializes internal circuits and brings the AFE into a low current Standby mode operation. The internal circuits that are initialized by the Soft Reset include:

- Output Enable Filter

- AGC circuits

- Demodulator

- 32 kHz Internal Oscillator

The Soft Reset has no effect on the Configuration register setup, except for some of the AFE Status Register 7 bits. (Register 11-8).

The circuit initialization takes one internal clock cycle (1/32 kHz = 31.25  $\mu$ s). During the initialization, the modulation transistors between each input and LCCOM pins are turned-on to discharge any internal/external parasitic charges. The modulation transistors are turned-off immediately after the initialization time.

The Soft Reset is executed in Active mode only. It is not valid in Standby mode.

### 11.21 Minimum Modulation Depth Requirement for Input Signal

The AFE demodulates the modulated input signal if the modulation depth of the input signal is greater than the minimum requirement that is programmed in the AFE Configuration Register 5 (Register 11-6). Figure 11-7 shows the definition of the modulation depth and examples. MODMIN<6:5> of the Configuration Register 5 offer four options. They are 75%, 50%, 25% and 12%, with a default setting of 50%.

The purpose of this feature is to enhance the demodulation integrity of the input signal. The 12% setting is the best choice for the input signal with weak modulation depth, which is typically observed near the high-voltage base station antenna and also at far-distance from the base station antenna. It gives the best demodulation sensitivity, but is very susceptible to noise spikes that can result in a bit detection error. The 75% setting can reduce the bit errors caused by noise, but gives the least demodulation sensitivity. See Table 11-3 for minimum modulation depth requirement settings.

#### TABLE 11-3: SETTING FOR MINIMUM MODULATION DEPTH REQUIREMENT

|       | IIN Bits<br>Register 5) | Modulation Depth |

|-------|-------------------------|------------------|

| Bit 6 | Bit 5                   |                  |

| 0     | 0                       | 50% (default)    |

| 0     | 1                       | 75%              |

| 1     | 0                       | 25%              |

| 1     | 1                       | 12%              |

### REGISTER 11-2: CONFIGURATION REGISTER 1

| R/W-0                                                                                                                                       | R/W-0                                                                                                                  | R/W-0           | R/W-0   | R/W-0           | R/W-0         | R/W-0          | R/W-0   | R/W-0 |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------|---------|-----------------|---------------|----------------|---------|-------|

| DATOUT1                                                                                                                                     | DATOUT0                                                                                                                | LCXTUN5         | LCXTUN4 | LCXTUN3         | LCXTUN2       | LCXTUN1        | LCXTUN0 | R1PAR |

| bit 8 bit 0                                                                                                                                 |                                                                                                                        |                 |         |                 |               |                |         |       |

|                                                                                                                                             |                                                                                                                        |                 |         |                 |               |                |         |       |

| Legend:                                                                                                                                     |                                                                                                                        |                 |         |                 |               |                |         |       |

| R = Readab                                                                                                                                  | le bit                                                                                                                 | W = Writable    | e bit   | U = Unimple     | mented bit, r | ead as '0'     |         |       |

| -n = Value a                                                                                                                                | t POR                                                                                                                  | '1' = Bit is se | et      | '0' = Bit is cl | eared         | x = Bit is unl | known   |       |

| bit 8-7 DATOUT<1:0>: LFDATA Output type bit<br>00 = Demodulated output<br>01 = Carrier Clock output<br>10 = RSSI output<br>11 = RSSI output |                                                                                                                        |                 |         |                 |               |                |         |       |

| bit 6-1 LCXTUN<5:0>: LCX Tuning Capacitance bit<br>000000 = +0 pF (Default)<br>:<br>111111 = +63 pF                                         |                                                                                                                        |                 |         |                 |               |                |         |       |

| bit 0                                                                                                                                       | it 0 R1PAR: Register Parity Bit – set/cleared so the 9-bit register contains odd parity – an odd number of set<br>bits |                 |         |                 |               |                |         |       |

#### **REGISTER 11-3: CONFIGURATION REGISTER 2**

| R/W-0   | R/W-0  | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0 |

|---------|--------|---------|---------|---------|---------|---------|---------|-------|

| RSSIFET | CLKDIV | LCYTUN5 | LCYTUN4 | LCYTUN3 | LCYTUN2 | LCYTUN1 | LCYTUN0 | R2PAR |

| bit 8   |        |         |         |         |         |         |         | bit 0 |

| Legend:                                                                                             |                                                                                         |                                                                    |                             |                                    |           |  |

|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------|------------------------------------|-----------|--|

| R = Read                                                                                            | able bit                                                                                | W = Writable bit                                                   | U = Unimplemented b         | U = Unimplemented bit, read as '0' |           |  |

| -n = Value                                                                                          | e at POR                                                                                | '1' = Bit is set                                                   | '0' = Bit is cleared        | x = Bit is unknown                 |           |  |

| bit 8                                                                                               | 1 = Pull-                                                                               | Pull-down MOSFET on<br>down RSSI MOSFET on<br>down RSSI MOSFET off | LFDATA pad bit (controllab  | le by user in the RSSI mode only)  |           |  |

| bit 7                                                                                               | bit 7 CLKDIV: Carrier Clock Divide-by bit<br>1 = Carrier Clock/4<br>0 = Carrier Clock/1 |                                                                    |                             |                                    |           |  |

| bit 6-1 LCYTUN<5:0>: LCY Tuning Capacitance bit<br>000000 = +0 pF (Default)<br>:<br>111111 = +63 pF |                                                                                         |                                                                    |                             |                                    |           |  |

| bit 0                                                                                               |                                                                                         | l.                                                                 | eared so the 9-bit register | contains odd parity – an odd numbe | er of set |  |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ensuremath{\left[0,1\right]} \end{array}$                                                                                                                                                                                                                                                    |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                       |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', then a NOP is<br>executed instead, making it a<br>two-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                       |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                            |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a two-cycle<br>instruction. |  |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                          |