Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                        |

| Number of I/O              | 5                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 128 x 8                                                                 |

| RAM Size                   | 64 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 8-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f635-e-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

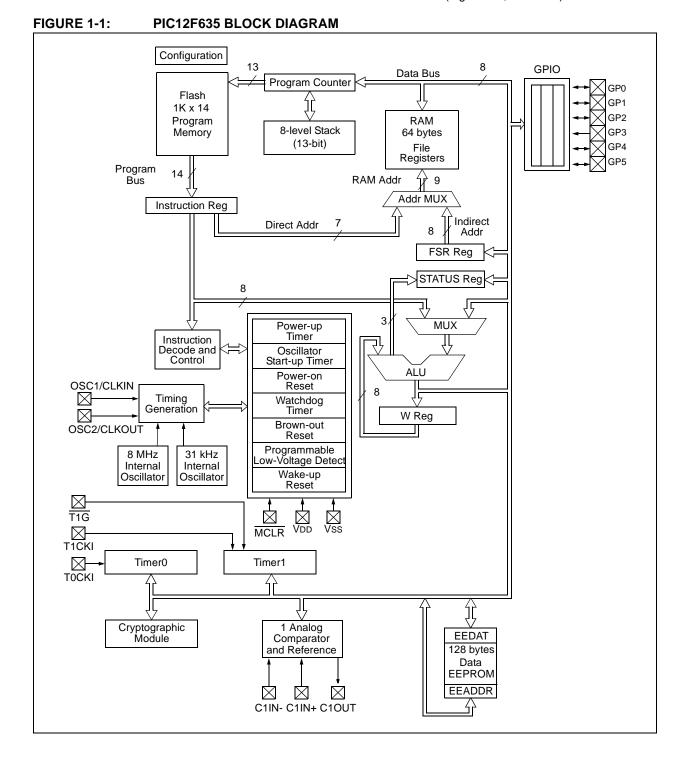

# 1.0 DEVICE OVERVIEW

This document contains device specific information for the PIC12F635/PIC16F636/639 devices.

Block Diagrams and pinout descriptions of the devices are as follows:

- PIC12F635 (Figure 1-1, Table 1-1)

- PIC16F636 (Figure 1-2, Table 1-2)

- PIC16F639 (Figure 1-3, Table 1-3)

NOTES:

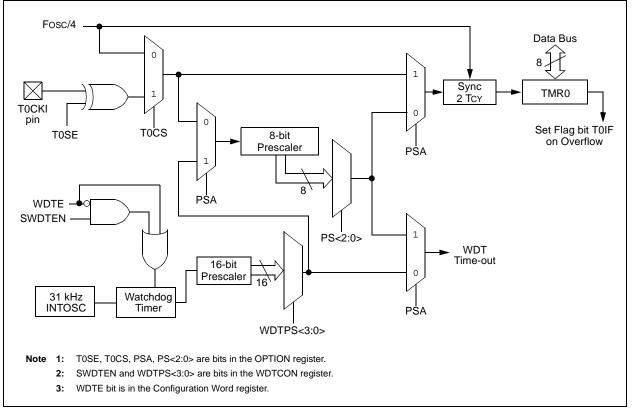

# 5.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (shared with Watchdog Timer)

- · Programmable internal or external clock source

- · Programmable external clock edge selection

- Interrupt on overflow

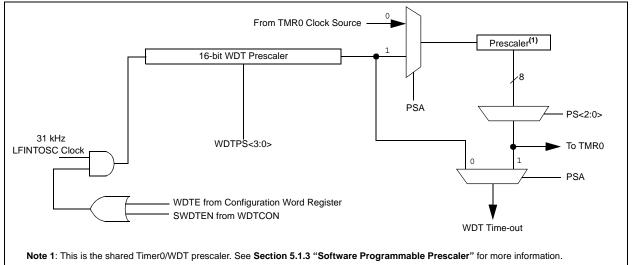

Figure 5-1 is a block diagram of the Timer0 module.

# 5.1 Timer0 Operation

When used as a timer, the Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

### 5.1.1 8-BIT TIMER MODE

When used as a timer, the Timer0 module will increment every instruction cycle (without prescaler). Timer mode is selected by clearing the T0CS bit of the OPTION register to '0'.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

Note: The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

### 5.1.2 8-BIT COUNTER MODE

When used as a counter, the Timer0 module will increment on every rising or falling edge of the T0CKI pin. The incrementing edge is determined by the T0SE bit of the OPTION register. Counter mode is selected by setting the T0CS bit of the OPTION register to '1'.

### FIGURE 5-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

| Name   | Bit 7                                                                         | Bit 6  | Bit 5   | Bit 4               | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------------------------------------------------------------------------------|--------|---------|---------------------|---------|--------|--------|--------|----------------------|---------------------------------|

| CMCON1 | —                                                                             | —      | —       | —                   | —       | _      | T1GSS  | CMSYNC | 10                   | 0010                            |

| INTCON | GIE                                                                           | PEIE   | T0IE    | INTE                | RAIE    | T0IF   | INTF   | RAIF   | 0000 000x            | 0000 000x                       |

| PIE1   | EEIE                                                                          | LVDIE  | CRIE    | C2IE <sup>(1)</sup> | C1IE    | OSFIE  | _      | TMR1IE | 000- 00-0            | 000-00-0                        |

| PIR1   | EEIF                                                                          | LVDIF  | CRIF    | C2IF <sup>(1)</sup> | C1IF    | OSFIF  | _      | TMR1IF | 000-00-0             | 000-00-0                        |

| TMR1H  | 1H Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |        |         |                     |         |        |        |        | XXXX XXXX            | uuuu uuuu                       |

| TMR1L  | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register   |        |         |                     |         |        |        |        | XXXX XXXX            | uuuu uuuu                       |

| T1CON  | T1GINV                                                                        | TMR1GE | T1CKPS1 | T1CKPS0             | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 0000 0000            | uuuu uuuu                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: PIC16F636/639 only.

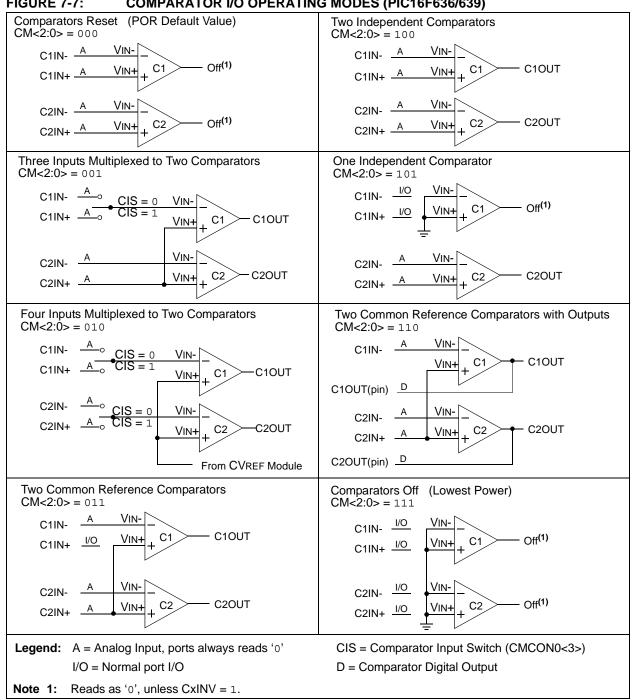

#### FIGURE 7-7: COMPARATOR I/O OPERATING MODES (PIC16F636/639)

# PIC12F635/PIC16F636/639

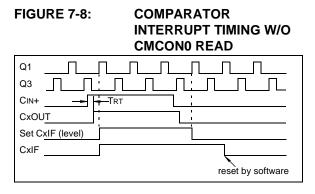

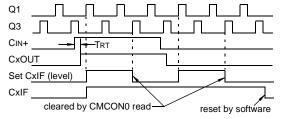

# FIGURE 7-9: COMPARATOR INTERRUPT TIMING WITH CMCON0 READ

- Note 1: If a change in the CMCON0 register (CxOUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CxIF of the PIR1 register interrupt flag may not get set.

- When either comparator is first enabled, bias circuitry in the Comparator module may cause an invalid output from the comparator until the bias circuitry is stable. Allow about 1 μs for bias settling then clear the mismatch condition and interrupt flags before enabling comparator interrupts.

| R-0           | R-0                            | R/W-0                              | R/W-0          | R/W-0            | R/W-0           | R/W-0          | R/W-0 |

|---------------|--------------------------------|------------------------------------|----------------|------------------|-----------------|----------------|-------|

| C2OUT         | C1OUT                          | C2INV                              | C1INV          | CIS              | CM2             | CM1            | CM0   |

| bit 7         |                                |                                    |                |                  |                 |                | bit 0 |

|               |                                |                                    |                |                  |                 |                |       |

| Legend:       |                                |                                    |                |                  |                 |                |       |

| R = Readable  | e bit                          | W = Writable                       | bit            | U = Unimpler     | mented bit, rea | d as '0'       |       |

| -n = Value at | POR                            | '1' = Bit is set                   |                | '0' = Bit is cle | eared           | x = Bit is unk | nown  |

|               |                                |                                    |                |                  |                 |                |       |

| bit 7         |                                | parator 2 Outp                     | ut bit         |                  |                 |                |       |

|               | When C2INV                     |                                    |                |                  |                 |                |       |

|               | 1 = C2 VIN+ ><br>0 = C2 VIN+ < |                                    |                |                  |                 |                |       |

|               | When C2INV                     | -                                  |                |                  |                 |                |       |

|               | 1 = C2 VIN+ <                  |                                    |                |                  |                 |                |       |

|               | 0 = C2 VIN+ >                  |                                    |                |                  |                 |                |       |

| bit 6         | C1OUT: Com                     | parator 1 Outp                     | ut bit         |                  |                 |                |       |

|               | When C1INV                     | = 0:                               |                |                  |                 |                |       |

|               | 1 = C1 VIN+ >                  | -                                  |                |                  |                 |                |       |

|               | 0 = C1 VIN+ <                  |                                    |                |                  |                 |                |       |

|               | When C1INV                     |                                    |                |                  |                 |                |       |

|               | 1 = C1 VIN+ <<br>0 = C1 VIN+ > |                                    |                |                  |                 |                |       |

| bit 5         |                                | parator 2 Outpu                    | t Inversion bi | t                |                 |                |       |

| 2.1.0         | 1 = C2 output                  | =                                  |                | -                |                 |                |       |

|               | 0 = C2 output                  |                                    |                |                  |                 |                |       |

| bit 4         | C1INV: Comp                    | parator 1 Outpu                    | t Inversion bi | t                |                 |                |       |

|               | 1 = C1 Outpu                   |                                    |                |                  |                 |                |       |

|               | 0 = C1 Outpu                   | it not inverted                    |                |                  |                 |                |       |

| bit 3         | -                              | ator Input Swite                   | ch bit         |                  |                 |                |       |

|               | When CM<2:                     |                                    |                |                  |                 |                |       |

|               |                                | nnects to C1 V                     |                |                  |                 |                |       |

|               |                                | onnects to C2 V<br>nnects to C1 VI |                |                  |                 |                |       |

|               |                                | nnects to C2 V                     |                |                  |                 |                |       |

|               | When CM<2:                     |                                    |                |                  |                 |                |       |

|               |                                | nnects to C1 V                     |                |                  |                 |                |       |

|               |                                | nnects to C1 VI                    |                | 7 5)             |                 |                |       |

| bit 2-0       |                                | mparator Mode                      |                |                  | la a            |                |       |

|               |                                | inputs multiple                    |                | nfigured as anal | log             |                |       |

|               |                                | puts multiplexe                    |                | •                |                 |                |       |

|               | 011 = Two co                   | ommon referen                      | ce comparato   |                  |                 |                |       |

|               |                                | dependent com                      | •              |                  |                 |                |       |

|               |                                | dependent con                      |                | common refere    | ence            |                |       |

|               |                                |                                    |                | figured as digit |                 |                |       |

|               |                                |                                    | 1              | <u>.</u>         |                 |                |       |

# REGISTER 7-2: CMCON0: COMPARATOR CONFIGURATION REGISTER (PIC16F636/639)

# 9.5 Protection Against Spurious Write

There are conditions when the user may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built in. On power-up, WREN is cleared. Also, the Power-up Timer (nominal 64 ms duration) prevents EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during:

- Brown-out

- Power Glitch

- Software Malfunction

# 9.6 Data EEPROM Operation During Code Protection

Data memory can be code-protected by programming the CPD bit in the Configuration Word (Register 12-1) to '0'.

When the data memory is code-protected, the CPU is able to read and write data to the data EEPROM. It is recommended to code-protect the program memory when code-protecting data memory. This prevents anyone from programming zeroes over the existing code (which will execute as NOPS) to reach an added routine, programmed in unused program memory, which outputs the contents of data memory. Programming unused locations in program memory to '0' will also help prevent data memory code protection from becoming breached.

| Name   | Bit 7                                                 | Bit 6  | Bit 5  | Bit 4               | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------------------------------------------------------|--------|--------|---------------------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE                                                   | PEIE   | T0IE   | INTE                | RAIE   | T0IF   | INTF   | RAIF   | x000 0000x           | 0000 000x                       |

| PIR1   | EEIF                                                  | LVDIF  | CRIF   | C2IF <sup>(1)</sup> | C1IF   | OSFIF  | _      | TMR1IF | 0000 00-0            | 0000 00-0                       |

| PIE1   | EEIE                                                  | LVDIE  | CRIE   | C2IE <sup>(1)</sup> | C1IE   | OSFIE  | _      | TMR1IE | 0000 00-0            | 0000 00-0                       |

| EEDAT  | EEDAT7                                                | EEDAT6 | EEDAT5 | EEDAT4              | EEDAT3 | EEDAT2 | EEDAT1 | EEDAT0 | 0000 0000            | 0000 0000                       |

| EEADR  | EEADR7 <sup>(1)</sup>                                 | EEADR6 | EEADR5 | EEADR4              | EEADR3 | EEADR2 | EEADR1 | EEADR0 | 0000 0000            | 0000 0000                       |

| EECON1 | _                                                     | _      | _      | _                   | WRERR  | WREN   | WR     | RD     | x000                 | q000                            |

| EECON2 | 2 EEPROM Control Register 2 (not a physical register) |        |        |                     |        |        |        |        |                      |                                 |

### TABLE 9-1: SUMMARY OF REGISTERS ASSOCIATED WITH DATA EEPROM

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by the data EEPROM module.

Note 1: PIC16F636/639 only.

# PIC12F635/PIC16F636/639

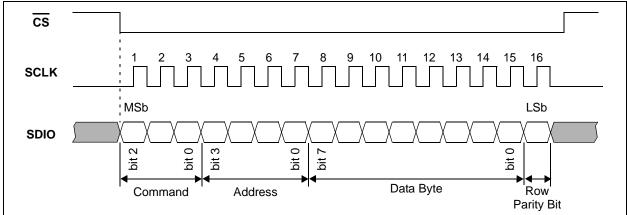

# FIGURE 11-19: DETAILED SPI INTERFACE TIMING (AFE)

# 11.32.2.1 Clamp On Command

This command results in activating (turning on) the modulation transistors of all enabled channels; channels enabled in Configuration Register 0 (Register 11-1).

### 11.32.2.2 Clamp Off Command

This command results in de-activating (turning off) the modulation transistors of all channels.

### 11.32.2.3 Sleep Command

This command places the AFE in Sleep mode – minimizing current draw by disabling all but the essential circuitry. Any other command wakes the AFE (example: Clamp Off command).

### 11.32.2.4 Soft Reset Command

The AFE issues a Soft Reset when it receives an external Soft Reset command. The external Soft Reset command is typically used to end a SPI communication sequence or to initialize the AFE for the next signal detection sequence, etc. See **Section 11.20** "**Soft Reset**" for more details on Soft Reset.

If a Soft Reset command is sent during a "Clamp-on" condition, the AFE still keeps the "Clamp-on" condition after the Soft Reset execution. The Soft Reset is executed in Active mode only, not in Standby mode. The SPI Soft Reset command is ignored if the AFE is not in Active mode.

# 11.32.2.5 AGC Preserve On Command

This command results in preserving the AGC level during each AGC settling time and apply the value to the data slicing circuit for the following data stream. The preserved AGC value is reset by a Soft Reset, and a new AGC value is acquired and preserved when it starts a new AGC settling time. This feature is disabled by an AGC Preserve Off command (see **Section 11.19 "AGC Preserve"**).

### 11.32.2.6 AGC Preserve Off Command

This command disables the AGC preserve feature and returns the AFE to the normal AGC tracking mode, fast tracking during AGC settling time and slow tracking after that (see **Section 11.19 "AGC Preserve"**).

# 11.32.3 CONFIGURATION REGISTERS

The AFE includes 8 Configuration registers, including a column parity register and AFE Status Register. All registers are readable and writable via SPI, except STATUS register, which is readable only. Bit 0 of each register is a row parity bit (except for the AFE Status Register 7) that makes the register contents an odd number.

### REGISTER 11-8: AFE STATUS REGISTER 7

| R-0             | R-0                                 | R-0                                             | R-0                                                  | R-0               | R-0             | R-0              | R-0                                   | R-0   |

|-----------------|-------------------------------------|-------------------------------------------------|------------------------------------------------------|-------------------|-----------------|------------------|---------------------------------------|-------|

| CHZACT          | CHYACT                              | CHXACT                                          | AGCACT                                               | WAKEZ             | WAKEY           | WAKEX            | ALARM                                 | PEI   |

| bit 8           |                                     |                                                 |                                                      |                   |                 |                  |                                       | bit ( |

| Legend:         |                                     |                                                 |                                                      |                   |                 |                  |                                       |       |

| R = Readable    | bit                                 | W = Writable b                                  | ait                                                  | II = Unimplem     | ented bit, read | as 'O'           |                                       |       |

| -n = Value at I |                                     | '1' = Bit is set                                |                                                      | '0' = Bit is clea |                 | x = Bit is unkn  | own                                   |       |

|                 |                                     |                                                 |                                                      |                   |                 |                  | -                                     |       |

| bit 8           | 1 = Channel                         | Z is passing dat                                | bit (cleared via<br>a after TAGC<br>data after TAGC  | ,                 |                 |                  |                                       |       |

| bit 7           | <b>CHYACT</b> : Char<br>1 = Channel | nnel Y Active <sup>(1)</sup><br>Y is passing da | bit (cleared via                                     | Soft Reset)       |                 |                  |                                       |       |

| bit 6           | 1 = Channel                         | X is passing da                                 | bit (cleared via<br>ta after TAGC<br>data after TAGC | ,                 |                 |                  |                                       |       |

| bit 5           | 1 = AGC is a                        |                                                 | 0,                                                   |                   | ,               | vel is approxima | ately > 20 mVPP i                     | ange. |

| bit 4           | 1 = Channel                         | Z caused a AFE                                  | Indicator Status<br>E wake-up (pass<br>a AFE wake-up | ed ÷64 clock co   | ,               |                  |                                       |       |

| bit 3           | 1 = Channel                         | Y caused a AFE                                  | Indicator Status<br>E wake-up (pass<br>a AFE wake-up | ed ÷64 clock co   | ,               |                  |                                       |       |

| bit 2           | 1 = Channel                         | X caused a AFE                                  | Indicator Status<br>E wake-up (pass<br>a AFE wake-up | ed ÷64 clock co   | ,               |                  |                                       |       |

| bit 1           | 1 = The Alarr<br>Configura          |                                                 | t has occurred. I                                    |                   |                 |                  | egister command<br>nding on the state |       |

| bit 0           |                                     | or Indicator bit -                              | - indicates whet                                     |                   |                 | ty error has occ | urred (real time)                     |       |

See Table 11-7 for the bit conditions of the AFE Status Register after various SPI commands and the AFE Power-on Reset.

# TABLE 11-7:AFE STATUS REGISTER BIT CONDITION (AFTER POWER-ON RESET AND<br/>VARIOUS SPI COMMANDS)

| Condition                              | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------------------------------------|--------|--------|--------|--------|-------|-------|-------|-------|-------|

| Condition                              | CHZACT | СНҮАСТ | СНХАСТ | AGCACT | WAKEZ | WAKEY | WAKEX | ALARM | PEI   |

| POR                                    | 0      | 0      | 0      | 0      | 0     | 0     | 0     | 0     | 1     |

| Read Command<br>(STATUS Register only) | u      | u      | u      | u      | u     | u     | u     | 0     | u     |

| Sleep Command                          | u      | u      | u      | u      | u     | u     | u     | u     | u     |

| Soft Reset Executed <sup>(1)</sup>     | 0      | 0      | 0      | 0      | 0     | 0     | 0     | u     | u     |

Legend: u = unchanged

Note 1: See Section 11.20 "Soft Reset" and Section 11.32.2.4 "Soft Reset Command" for the condition of Soft Reset execution.

| Register             | Address | Power-on<br>Reset<br>Wake-up Reset | MCLR Reset<br>WDT Reset<br>Brown-out Reset <sup>(1)</sup><br>Wake-up Reset | Wake-up from Sleep<br>through Interrupt<br>Wake-up from Sleep<br>through WDT Time-out |

|----------------------|---------|------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| W                    | _       | xxxx xxxx                          | uuuu uuuu                                                                  | uuuu uuuu                                                                             |

| INDF                 | 00h/80h | xxxx xxxx                          | xxxx xxxx                                                                  | uuuu uuuu                                                                             |

| TMR0                 | 01h     | xxxx xxxx                          | uuuu uuuu                                                                  | uuuu uuuu                                                                             |

| PCL                  | 02h/82h | 0000 0000                          | 0000 0000                                                                  | PC + 1 <sup>(3)</sup>                                                                 |

| STATUS               | 03h/83h | 0001 1xxx                          | 000q quuu <sup>(4)</sup>                                                   | uuuq quuu <sup>(4)</sup>                                                              |

| FSR                  | 04h/84h | xxxx xxxx                          | uuuu uuuu                                                                  | սսսս սսսս                                                                             |

| PORTA                | 05h     | xx xx00                            | 00 0000                                                                    | uu uu00                                                                               |

| PORTC <sup>(6)</sup> | 07h     | xx xx00                            | 00 0000                                                                    | uu uu00                                                                               |

| PCLATH               | 0Ah/8Ah | 0 0000                             | 0 0000                                                                     | u uuuu                                                                                |

| INTCON               | 0Bh/8Bh | 0000 000x                          | 0000 000x                                                                  | uuuu uuuu <b>(2)</b>                                                                  |

| PIR1                 | 0Ch     | 0000 00-0                          | 0000 00-0                                                                  | uuuu uu-u <b>(2)</b>                                                                  |

| TMR1L                | 0Eh     | xxxx xxxx                          | uuuu uuuu                                                                  | <u>uuuu</u> uuuu                                                                      |

| TMR1H                | 0Fh     | xxxx xxxx                          | <u>uuuu</u> uuuu                                                           | uuuu uuuu                                                                             |

| T1CON                | 10h     | 0000 0000                          | uuuu uuuu                                                                  | -uuu uuuu                                                                             |

| WDTCON               | 18h     | 0 1000                             | 0 1000                                                                     | u uuuu                                                                                |

| CMCON0               | 19h     | 0000 0000                          | 0000 0000                                                                  | uuuu uuuu                                                                             |

| CMCON1               | 1Ah     | 10                                 | 10                                                                         | uu                                                                                    |

| OPTION_REG           | 81h     | 1111 1111                          | 1111 1111                                                                  | uuuu uuuu                                                                             |

| TRISA                | 85h     | 11 1111                            | 11 1111                                                                    | uu luuu                                                                               |

| TRISC <sup>(6)</sup> | 87h     | 11 1111                            | 11 1111                                                                    | uu luuu                                                                               |

| PIE1                 | 8Ch     | 0000 00-0                          | 0000 00-0                                                                  | uuuu uu-u                                                                             |

| PCON                 | 8Eh     | 01 q-qq                            | 0u u-uu <b>(1,5)</b>                                                       | Ou u-uu                                                                               |

| OSCCON               | 8Fh     | -110 q000                          | -110 q000                                                                  | -uuu uuuu                                                                             |

| OSCTUNE              | 90h     | 0 0000                             | u uuuu                                                                     | u uuuu                                                                                |

| WPUDA                | 95h     | 11 -111                            | 11 -111                                                                    | uuuu uuuu                                                                             |

| IOCA                 | 96h     | 00 0000                            | 00 0000                                                                    | uu uuuu                                                                               |

| WDA                  | 97h     | 11 -111                            | 11 -111                                                                    | นนนน นนนน                                                                             |

| VRCON                | 99h     | 0-0- 0000                          | 0-0- 0000                                                                  | u-u- uuuu                                                                             |

| EEDAT                | 9Ah     | 0000 0000                          | 0000 0000                                                                  | uuuu uuuu                                                                             |

| EEADR                | 9Bh     | 0000 0000                          | 0000 0000                                                                  | սսսս սսսս                                                                             |

| EECON1               | 9Ch     | x000                               | d000                                                                       | uuuu                                                                                  |

| EECON2               | 9Dh     |                                    |                                                                            |                                                                                       |

| ADRESL               | 9Eh     | xxxx xxxx                          | <u>uuuu</u> uuuu                                                           | uuuu uuuu                                                                             |

| ADCON1               | 9Fh     | -000                               | -000                                                                       | -uuu                                                                                  |

| LVDCON               | 94h     | 00-000                             | 00-000                                                                     | uu -uuu                                                                               |

| CRCON                | 110h    | 0000                               | 0000                                                                       | uuuu                                                                                  |

### TABLE 12-4: INITIALIZATION CONDITION FOR REGISTERS

$\label{eq:logend: u = unchanged, x = unknown, - = unimplemented bit, reads as `0', q = value depends on condition.$

**Note 1:** If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

4: See Table 12-5 for Reset value for specific condition.

**5:** If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

6: PIC16F636/639 only.

<sup>3:</sup> When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

### TABLE 12-5: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | Status<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 010x             |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | 0uuu             |

| MCLR Reset during Sleep            | 000h                  | 0001 Ouuu          | 0uuu             |

| WDT Reset                          | 000h                  | 0000 uuuu          | 0uuu             |

| WDT Wake-up                        | PC + 1                | սսս0 Օսսս          | uuuu             |

| Brown-out Reset                    | 000h                  | 0001 luuu          | 0110             |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uuuu             |

| Wake-up Reset                      | 000h                  | 0001 1xxx          | 010x             |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and the Global Interrupt Enable bit, GIE, is set, the PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

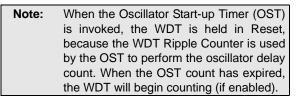

# 12.11 Watchdog Timer (WDT)

The PIC12F635/PIC16F636/639 WDT is code and functionally compatible with other PIC16F WDT modules and adds a 16-bit prescaler to the WDT. This allows the user to have a scaler value for the WDT and TMR0 at the same time. In addition, the WDT time-out value can be extended to 268 seconds. WDT is cleared under certain conditions described in Table 12-7.

### 12.11.1 WDT OSCILLATOR

The WDT derives its time base from the 31 kHz LFINTOSC. The LTS bit does not reflect that the LFINTOSC is enabled.

The value of WDTCON is '---0 1000' on all Resets. This gives a nominal time base of 16 ms, which is compatible with the time base generated with previous PIC12F635/PIC16F636/639 microcontroller versions.

A new prescaler has been added to the path between the INTRC and the multiplexers used to select the path for the WDT. This prescaler is 16 bits and can be programmed to divide the INTRC by 32 to 65536, giving the WDT a nominal range of 1 ms to 268s.

### 12.11.2 WDT CONTROL

The WDTE bit is located in the Configuration Word register. When set, the WDT runs continuously.

When the WDTE bit in the Configuration Word register is set, the SWDTEN bit of the WDTCON register has no effect. If WDTE is clear, then the SWDTEN bit can be used to enable and disable the WDT. Setting the bit will enable it and clearing the bit will disable it.

The PSA and PS<2:0> bits of the OPTION register have the same function as in previous versions of the PIC16F family of microcontrollers. See **Section 5.0 "Timer0 Module"** for more information.

### FIGURE 12-9: WATCHDOG TIMER BLOCK DIAGRAM

### TABLE 12-7: WDT STATUS

| Conditions                                                 | WDT                          |  |

|------------------------------------------------------------|------------------------------|--|

| WDTE = 0                                                   |                              |  |

| CLRWDT Command                                             | Cleared                      |  |

| Oscillator Fail Detected                                   | Cleared                      |  |

| Exit Sleep + System Clock = T1OSC, EXTRC, HFINTOSC, EXTCLK |                              |  |

| Exit Sleep + System Clock = XT, HS, LP                     | Cleared until the end of OST |  |

# PIC12F635/PIC16F636/639

| ADDLW            | Add literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |

| Operands:        | $0 \le k \le 255$                                                                                                          |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the<br>W register. |

Instruction Descriptions

13.2

| BCF              | Bit Clear f                                                         |  |  |

|------------------|---------------------------------------------------------------------|--|--|

| Syntax:          | [label]BCF f,b                                                      |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |  |

| Operation:       | $0 \rightarrow (f < b >)$                                           |  |  |

| Status Affected: | None                                                                |  |  |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |  |  |

| ADDWF            | Add W and f                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                    |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |

| Status Affected: | C, DC, Z                                                                                                                                                                           |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND literal with W                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |

| Operands:        | $0 \le k \le 255$                                                                                                      |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                             |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the<br>next instruction is discarded, and<br>a NOP is executed instead, making<br>this a two-cycle instruction. |

| ANDWF            | AND W with f                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

### 14.7 MPLAB ICE 2000 High-Performance In-Circuit Emulator

The MPLAB ICE 2000 In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers. Software control of the MPLAB ICE 2000 In-Circuit Emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The architecture of the MPLAB ICE 2000 In-Circuit Emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE 2000 In-Circuit Emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows<sup>®</sup> 32-bit operating system were chosen to best make these features available in a simple, unified application.

# 14.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC<sup>®</sup> and MCU devices. It debugs and programs PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The MPLAB REAL ICE probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with the popular MPLAB ICD 2 system (RJ11) or with the new high speed, noise tolerant, lowvoltage differential signal (LVDS) interconnection (CAT5).

MPLAB REAL ICE is field upgradeable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added, such as software breakpoints and assembly code trace. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, real-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 14.9 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low-cost, run-time development tool, connecting to the host PC via an RS-232 or high-speed USB interface. This tool is based on the Flash PIC MCUs and can be used to develop for these and other PIC MCUs and dsPIC DSCs. The MPLAB ICD 2 utilizes the in-circuit debugging capability built into the Flash devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers costeffective, in-circuit Flash debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, single stepping and watching variables, and CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real time. MPLAB ICD 2 also serves as a development programmer for selected PIC devices.

# 14.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an SD/MMC card for file storage and secure data applications.

### 15.4 DC Characteristics: PIC12F635/PIC16F636-I (Industrial) PIC12F635/PIC16F636-E (Extended)

| DC CHARACTERISTICS |      |                                       | Standard Operating Cond<br>Operating temperature |       | -40°C s    | otherwise stated)<br>·85°C for industrial<br>·125°C for extended |                                                                                                                           |

|--------------------|------|---------------------------------------|--------------------------------------------------|-------|------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Sym  | Characteristic                        | Min Typ†                                         |       | Мах        | Units                                                            | Conditions                                                                                                                |

|                    | VIL  | Input Low Voltage                     |                                                  |       |            |                                                                  |                                                                                                                           |

|                    |      | I/O ports:                            |                                                  |       |            |                                                                  |                                                                                                                           |

| D030               |      | with TTL buffer                       | Vss                                              | —     | 0.8        | V                                                                | $4.5V \leq V\text{DD} \leq 5.5V$                                                                                          |

| D030A              |      |                                       | Vss                                              | —     | 0.15 Vdd   | V                                                                | Otherwise                                                                                                                 |

| D031               |      | with Schmitt Trigger buffer           | Vss                                              | —     | 0.2 Vdd    | V                                                                | Entire range                                                                                                              |

| D032               |      | MCLR, OSC1 (RC mode)                  | Vss                                              | _     | 0.2 Vdd    | V                                                                |                                                                                                                           |

| D033               |      | OSC1 (XT and LP modes) <sup>(1)</sup> | Vss                                              | _     | 0.3        | V                                                                |                                                                                                                           |

| D033A              |      | OSC1 (HS mode) <sup>(1)</sup>         | Vss                                              | _     | 0.3 Vdd    | V                                                                |                                                                                                                           |

|                    | Viн  | Input High Voltage                    |                                                  |       |            |                                                                  |                                                                                                                           |

|                    |      | I/O ports:                            |                                                  |       |            |                                                                  |                                                                                                                           |

| D040<br>D040A      |      | with TTL buffer                       | 2.0<br>(0.25 Vdd +<br>0.8)                       | _     | Vdd<br>Vdd | V<br>V                                                           | $4.5V \le VDD \le 5.5V$<br>Otherwise                                                                                      |

| D041               |      | with Schmitt Trigger buffer           | 0.8 VDD                                          | _     | Vdd        | V                                                                | Entire range                                                                                                              |

| D042               |      | MCLR                                  | 0.8 Vdd                                          | _     | Vdd        | V                                                                | 5                                                                                                                         |

| D043               |      | OSC1 (XT and LP modes)                | 1.6                                              | _     | Vdd        | V                                                                | (Note 1)                                                                                                                  |

| D043A              |      | OSC1 (HS mode)                        | 0.7 Vdd                                          | _     | Vdd        | V                                                                | (Note 1)                                                                                                                  |

| D043B              |      | OSC1 (RC mode)                        | 0.9 Vdd                                          | _     | Vdd        | V                                                                |                                                                                                                           |

|                    | lı∟  | Input Leakage Current <sup>(2)</sup>  |                                                  |       |            |                                                                  |                                                                                                                           |

| D060               |      | I/O ports                             | —                                                | ± 0.1 | ± 1        | μA                                                               | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in \ at \ high-impedance} \end{split}$ |

| D060A              |      | Analog inputs                         | —                                                | ± 0.1 | ± 1        | μΑ                                                               | $VSS \leq VPIN \leq VDD$                                                                                                  |

| D060B              |      | VREF                                  | —                                                | ± 0.1 | ± 1        | μΑ                                                               | $VSS \leq VPIN \leq VDD$                                                                                                  |

| D061               |      | MCLR <sup>(3)</sup>                   | —                                                | ± 0.1 | ± 5        | μΑ                                                               | $VSS \leq VPIN \leq VDD$                                                                                                  |

| D063               |      | OSC1                                  | —                                                | ± 0.1 | ± 5        | μA                                                               | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP oscillator configuration                                                        |

| D070               | IPUR | PORTA Weak Pull-up<br>Current         | 50                                               | 250   | 400        | μA                                                               | VDD = 5.0V, VPIN = VSS                                                                                                    |

| D071               | IPDR | PORTA Weak Pull-down<br>Current       | 50                                               | 250   | 400        | μA                                                               | Vdd = 5.0V, Vpin = Vdd                                                                                                    |

|                    | Vol  | Output Low Voltage                    |                                                  |       |            |                                                                  |                                                                                                                           |

| D080               |      | I/O ports                             | —                                                | —     | 0.6        | V                                                                | IOL = 8.5 mA, VDD = 4.5V (Ind.)                                                                                           |

| D083               |      | OSC2/CLKOUT (RC mode)                 | —                                                | -     | 0.6        | V                                                                | IOL = 1.6 mA, VDD = 4.5V (Ind.)<br>IOL = 1.2 mA, VDD = 4.5V (Ext.)                                                        |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

**3:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: See Section 9.4.1 "Using the Data EEPROM" for additional information.

# 15.6 DC Characteristics: PIC16F639-I (Industrial)

| DC CHARACTERISTICS |                | ICS                                                                                                                                                                            |          |                    |             | -40°C ≤        | ess otherwise stated)<br>C ≤ TA ≤ +85°C for industrial<br>≤ VDD ≤ 3.6V |                                                                                                             |  |

|--------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|-------------|----------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|

| Param              |                |                                                                                                                                                                                |          |                    |             |                |                                                                        | Conditions                                                                                                  |  |

| No.                | Sym            | Device Characteristics                                                                                                                                                         | Min      | Тур†               | Мах         | Units          | Vdd                                                                    | Note                                                                                                        |  |

| D010               | IDD            | Supply Current <sup>(1,2,3)</sup>                                                                                                                                              | _        | 11                 | 16          | μA             | 2.0                                                                    | Fosc = 32.768 kHz                                                                                           |  |

|                    |                |                                                                                                                                                                                | —        | 18                 | 28          | μΑ             | 3.0                                                                    | LP Oscillator mode                                                                                          |  |

| D011               |                |                                                                                                                                                                                | _        | 140                | 240         | μΑ             | 2.0                                                                    | Fosc = 1 MHz                                                                                                |  |

|                    |                |                                                                                                                                                                                | —        | 220                | 380         | μΑ             | 3.0                                                                    | XT Oscillator mode                                                                                          |  |

| D012               |                |                                                                                                                                                                                | _        | 260                | 360         | μΑ             | 2.0                                                                    | Fosc = 4 MHz                                                                                                |  |

|                    |                |                                                                                                                                                                                | _        | 420                | 650         | μΑ             | 3.0                                                                    | XT Oscillator mode                                                                                          |  |

| D013               |                |                                                                                                                                                                                | _        | 130                | 220         | μΑ             | 2.0                                                                    | Fosc = 1 MHz                                                                                                |  |

|                    |                |                                                                                                                                                                                | —        | 215                | 360         | μA             | 3.0                                                                    | EC Oscillator mode                                                                                          |  |

| D014               |                |                                                                                                                                                                                | —        | 220                | 340         | μA             | 2.0                                                                    | Fosc = 4 MHz                                                                                                |  |

|                    |                |                                                                                                                                                                                | _        | 375                | 550         | μΑ             | 3.0                                                                    | EC Oscillator mode                                                                                          |  |

| D015               |                |                                                                                                                                                                                | _        | 8                  | 20          | μΑ             | 2.0                                                                    | Fosc = 31 kHz                                                                                               |  |

|                    |                |                                                                                                                                                                                | _        | 16                 | 40          | μΑ             | 3.0                                                                    | LFINTOSC mode                                                                                               |  |

| D016               |                |                                                                                                                                                                                | _        | 340                | 450         | μΑ             | 2.0                                                                    | Fosc = 4 MHz                                                                                                |  |

|                    |                |                                                                                                                                                                                | _        | 500                | 700         | μΑ             | 3.0                                                                    | HFINTOSC mode                                                                                               |  |

| D017               |                |                                                                                                                                                                                | _        | 230                | 400         | μΑ             | 2.0                                                                    | Fosc = 4 MHz                                                                                                |  |

|                    |                |                                                                                                                                                                                | _        | 400                | 680         | μΑ             | 3.0                                                                    | EXTRC mode                                                                                                  |  |

| D020               | IPD            | Power-down Base Current <sup>(4)</sup>                                                                                                                                         | _        | 0.15               | 1.2         | μΑ             | 2.0                                                                    | WDT, BOR, Comparators,                                                                                      |  |

|                    |                |                                                                                                                                                                                | _        | 0.20               | 1.5         | μΑ             | 3.0                                                                    | VREF and T1OSC disabled<br>(excludes AFE)                                                                   |  |

| D021               | IWDT           |                                                                                                                                                                                | _        | 1.2                | 2.2         | μΑ             | 2.0                                                                    | WDT Current <sup>(1)</sup>                                                                                  |  |

|                    |                |                                                                                                                                                                                | _        | 2.0                | 4.0         | μΑ             | 3.0                                                                    |                                                                                                             |  |

| D022A              | IBOR           |                                                                                                                                                                                | _        | 42                 | 60          | μΑ             | 3.0                                                                    | BOR Current <sup>(1)</sup>                                                                                  |  |

| D022B              | ILVD           |                                                                                                                                                                                | _        | 22                 | 28          | μΑ             | 2.0                                                                    | PLVD Current                                                                                                |  |

|                    |                |                                                                                                                                                                                | _        | 25                 | 35          | μΑ             | 3.0                                                                    |                                                                                                             |  |

| D023               | ICMP           |                                                                                                                                                                                | _        | 32                 | 45          | μΑ             | 2.0                                                                    | Comparator Current <sup>(1)</sup>                                                                           |  |

|                    |                |                                                                                                                                                                                | _        | 60                 | 78          | μΑ             | 3.0                                                                    |                                                                                                             |  |

| D024A              | <b>IVREFHS</b> |                                                                                                                                                                                | _        | 30                 | 36          | μΑ             | 2.0                                                                    | CVREF Current <sup>(1)</sup>                                                                                |  |

|                    |                |                                                                                                                                                                                | _        | 45                 | 55          | μΑ             | 3.0                                                                    | (high-range)                                                                                                |  |

| D024B              | IVREFLS        |                                                                                                                                                                                | _        | 39                 | 47          | μΑ             | 2.0                                                                    | CVREF Current <sup>(1)</sup>                                                                                |  |

|                    |                |                                                                                                                                                                                | _        | 59                 | 72          | μΑ             | 3.0                                                                    | (low-range)                                                                                                 |  |