# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                            |

| Supplier Device Package    | 8-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f635-e-sn |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MICROCHIP PIC12F635/PIC16F636/639

# 8/14-Pin Flash-Based, 8-Bit CMOS Microcontrollers With nanoWatt Technology

#### **High-Performance RISC CPU:**

- Only 35 instructions to learn:

- All single-cycle instructions except branches

- Operating speed:

- DC 20 MHz oscillator/clock input

- DC 200 ns instruction cycle

- · Interrupt capability

- 8-level deep hardware stack

- Direct, Indirect and Relative Addressing modes

#### **Special Microcontroller Features:**

- Precision Internal Oscillator:

- Factory calibrated to ±1%, typical

- Software selectable frequency range of 8 MHz to 125 kHz

- Software tunable

- Two-Speed Start-up mode

- Crystal fail detect for critical applications

- Clock mode switching during operation for power savings

- Clock mode switching for low-power operation

- Power-Saving Sleep mode

- Wide operating voltage range (2.0V-5.5V)

- Industrial and Extended Temperature range

- Power-on Reset (POR)

- Wake-up Reset (WUR)

- Independent weak pull-up/pull-down resistors

- Programmable Low-Voltage Detect (PLVD)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR) with software control option

- Enhanced Low-Current Watchdog Timer (WDT) with on-chip oscillator (software selectable nominal 268 seconds with full prescaler) with software enable

- Multiplexed Master Clear with pull-up/input pin

- Programmable code protection (program and data independent)

- High-Endurance Flash/EEPROM cell:

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- Flash/Data EEPROM Retention: > 40 years

#### Low-Power Features:

- Standby Current:

- 1 nA @ 2.0V, typical

- Operating Current:

- 8.5 μA @ 32 kHz, 2.0V, typical

- 100 μA @ 1 MHz, 2.0V, typical

- Watchdog Timer Current:

- 1 μA @ 2.0V, typical

#### **Peripheral Features:**

- 6/12 I/O pins with individual direction control:

- High-current source/sink for direct LED drive

- Interrupt-on-change pin

- Individually programmable weak pull-ups/ pull-downs

- Ultra Low-Power Wake-up

- Analog Comparator module with:

- Up to two analog comparators

- Programmable On-chip Voltage Reference (CVREF) module (% of VDD)

- Comparator inputs and outputs externally accessible

- Timer0: 8-bit timer/counter with 8-bit programmable prescaler

- Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Timer1 Gate (count enable)

- Option to use OSC1 and OSC2 in LP mode as Timer1 oscillator if INTOSC mode selected

- KEELOQ<sup>®</sup> compatible hardware Cryptographic module

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via two pins

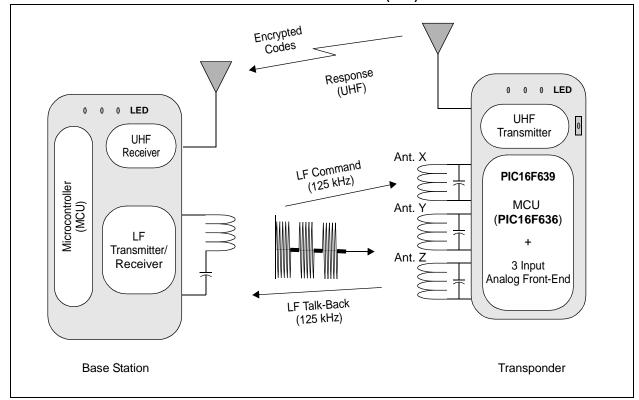

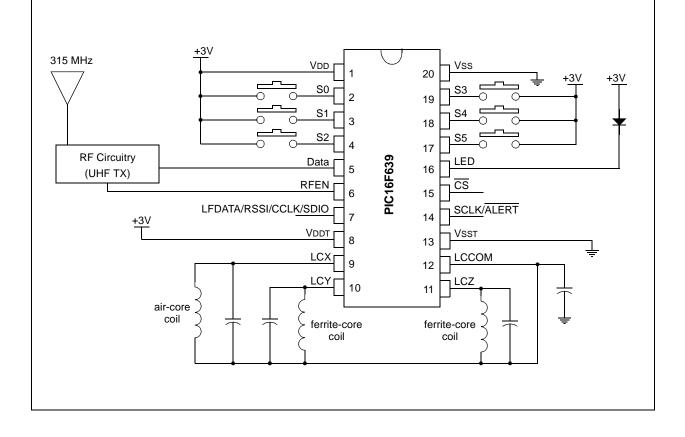

# Low-Frequency Analog Front-End Features (PIC16F639 only):

- Three input pins for 125 kHz LF input signals

- High input detection sensitivity (3 mVPP, typical)

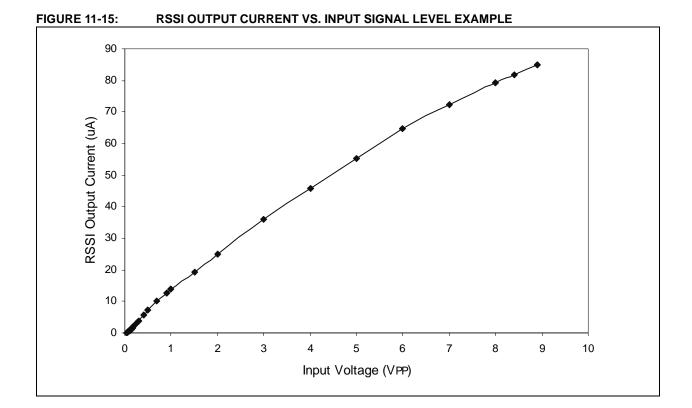

- Demodulated data, Carrier clock or RSSI output selection

- Input carrier frequency: 125 kHz, typical

- Input modulation frequency: 4 kHz, maximum

- 8 internal Configuration registers

- Bidirectional transponder communication (LF talk back)

- Programmable antenna tuning capacitance (up to 63 pF, 1 pF/step)

- Low standby current: 5  $\mu$ A (with 3 channels enabled), typical

- Low operating current: 15 μA (with 3 channels enabled), typical

- Serial Peripheral Interface (SPI) with internal MCU and external devices

- Supports Battery Back-up mode and batteryless

operation with external circuits

|           | Device Program Memory Data Memory I/O | •            | Low Frequency  |     |             |                     |  |

|-----------|---------------------------------------|--------------|----------------|-----|-------------|---------------------|--|

| Device    | Flash (words)                         | SRAM (bytes) | EEPROM (bytes) | 1/0 | Comparators | Analog<br>Front-End |  |

| PIC12F635 | 1024                                  | 64           | 128            | 6   | 1           | N                   |  |

| PIC16F636 | 2048                                  | 128          | 256            | 12  | 2           | N                   |  |

| PIC16F639 | 2048                                  | 128          | 256            | 12  | 2           | Y                   |  |

Note 1: Any references to PORTA, RAn, TRISA and TRISAn refer to GPIO, GPn, TRISIO and TRISIOn, respectively.

2: VDDT is the supply voltage of the Analog Front-End section (PIC16F639 only). VDDT is treated as VDD in this document unless otherwise stated.

**3:** VSST is the ground reference voltage of the Analog Front-End section (PIC16F639 only). VSST is treated as VSS in this document unless otherwise stated.

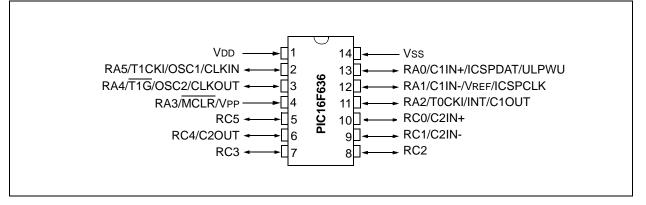

# 14-Pin Diagram (PDIP, SOIC, TSSOP)

# TABLE 2: 14-PIN SUMMARY (PDIP, SOIC, TSSOP)

| I/O                | Pin | Comparators | Timer | Interrupts | Pull-ups         | Basic         |

|--------------------|-----|-------------|-------|------------|------------------|---------------|

| RA0                | 13  | C1IN+       |       | IOC        | Y                | ICSPDAT/ULPWU |

| RA1                | 12  | C1IN-       | _     | IOC        | Y                | VREF/ICSPCLK  |

| RA2                | 11  | C1OUT       | TOCKI | INT/IOC    | Y                | —             |

| RA3 <sup>(1)</sup> | 4   | —           | _     | IOC        | Y <sup>(2)</sup> | MCLR/Vpp      |

| RA4                | 3   | —           | T1G   | IOC        | Y                | OSC2/CLKOUT   |

| RA5                | 2   | —           | T1CKI | IOC        | Y                | OSC1/CLKIN    |

| RC0                | 10  | C2IN+       | —     | —          | —                | —             |

| RC1                | 9   | C2IN-       | —     | —          | —                | —             |

| RC2                | 8   | —           | —     | —          | —                | —             |

| RC3                | 7   | —           | —     | —          | —                | —             |

| RC4                | 6   | C2OUT       | —     | —          | —                | —             |

| RC5                | 5   | —           | —     | —          | —                | —             |

|                    | 1   | —           | —     | —          | —                | Vdd           |

| _                  | 14  |             |       | _          |                  | Vss           |

Note 1: Input only.

2: Only when pin is configured for external MCLR.

#### 2.2.2.2 OPTION Register

The OPTION register is a readable and writable register which contains various control bits to configure:

- TMR0/WDT prescaler

- External RA2/INT interrupt

- TMR0

- Weak pull-up/pull-downs on PORTA

Note: To achieve a 1:1 prescaler assignment for Timer0, assign the prescaler to the WDT by setting the PSA bit of the OPTION register to '1'. See Section 5.1.3 "Software Programmable Prescaler".

## REGISTER 2-2: OPTION\_REG: OPTION REGISTER

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RAPU  | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | RAPU: PORTA Pull-                                                        | -up Enable bi                                                               | t                                                                         |  |  |  |  |

|---------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|

|         | 1 = PORTA pull-ups<br>0 = PORTA pull-ups                                 |                                                                             | by individual PORT latch values                                           |  |  |  |  |

| bit 6   | INTEDG: Interrupt E                                                      | dge Select bi                                                               | it                                                                        |  |  |  |  |

|         | <ul><li>1 = Interrupt on risin</li><li>0 = Interrupt on fallir</li></ul> | • •                                                                         | -                                                                         |  |  |  |  |

| bit 5   | TOCS: Timer0 Clock                                                       | Source Sele                                                                 | ct bit                                                                    |  |  |  |  |

|         | <ul><li>1 = Transition on RA</li><li>0 = Internal instruction</li></ul>  | •                                                                           | < (Fosc/4)                                                                |  |  |  |  |

| bit 4   | T0SE: Timer0 Source Edge Select bit                                      |                                                                             |                                                                           |  |  |  |  |

|         |                                                                          | 5                                                                           | sition on RA2/T0CKI pin<br>sition on RA2/T0CKI pin                        |  |  |  |  |

| bit 3   | PSA: Prescaler Ass                                                       | ignment bit                                                                 |                                                                           |  |  |  |  |

|         | 1 = Prescaler is ass<br>0 = Prescaler is ass                             | 0                                                                           |                                                                           |  |  |  |  |

| bit 2-0 | PS<2:0>: Prescaler                                                       | Rate Select b                                                               | pits                                                                      |  |  |  |  |

|         | Bit Value                                                                | Timer0 Rate                                                                 | WDT Rate                                                                  |  |  |  |  |

|         | 000<br>001<br>010<br>011<br>100<br>101<br>110                            | 1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128<br>1 : 256 | 1 : 1<br>1 : 2<br>1 : 4<br>1 : 8<br>1 : 16<br>1 : 32<br>1 : 64<br>1 : 128 |  |  |  |  |

|         | 111                                                                      | 1.200                                                                       | 1.120                                                                     |  |  |  |  |

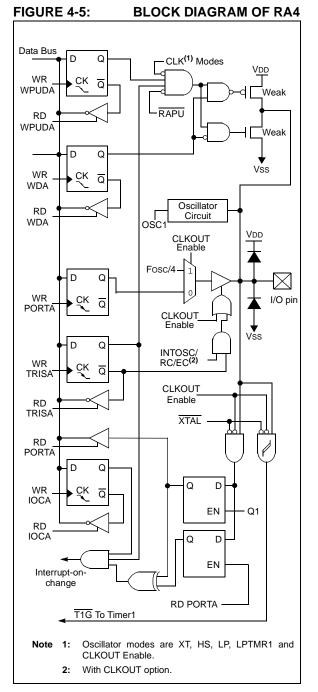

#### 4.2.4.5 RA4/T1G/OSC2/CLKOUT

Figure 4-5 shows the diagram for this pin. The RA4 pin is configurable to function as one of the following:

- a general purpose I/O

- a Timer1 gate input

- a crystal/resonator connection

- a clock output

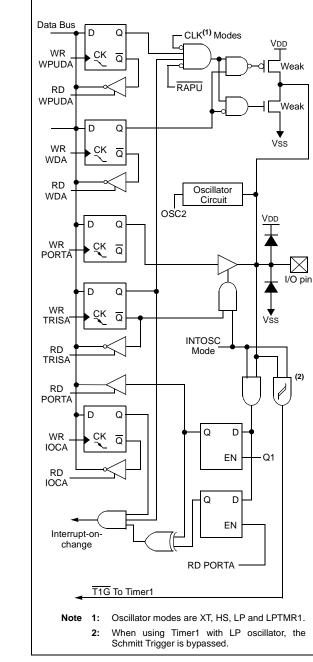

#### 4.2.4.6 RA5/T1CKI/OSC1/CLKIN

Figure 4-6 shows the diagram for this pin. The RA5 pin is configurable to function as one of the following:

**BLOCK DIAGRAM OF RA5**

- a general purpose I/O

- a Timer1 clock input

- a crystal/resonator connection

- a clock input

FIGURE 4-6:

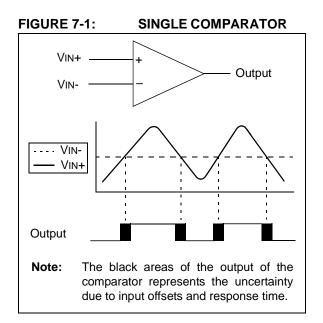

# 7.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. The comparators are very useful mixed signal building blocks because they provide analog functionality independent of the program execution. The Analog Comparator module includes the following features:

- Dual comparators (PIC16F636/639 only)

- Multiple comparator configurations

- Comparator(s) output is available internally/externally

- Programmable output polarity

- Interrupt-on-change

- Wake-up from Sleep

- Timer1 gate (count enable)

- Output synchronization to Timer1 clock input

- Programmable voltage reference

#### 7.1 Comparator Overview

A comparator is shown in Figure 7-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the

comparator is a digital low level. When the analog voltage at  $V_{IN+}$  is greater than the analog voltage at  $V_{IN-}$ , the output of the comparator is a digital high level.

The PIC12F635 contains a single comparator as shown in Figure 7-2.

The PIC16F636/639 devices contains two comparators as shown in Figure 7-3 and Figure 7-4. The comparators are not independently configurable.

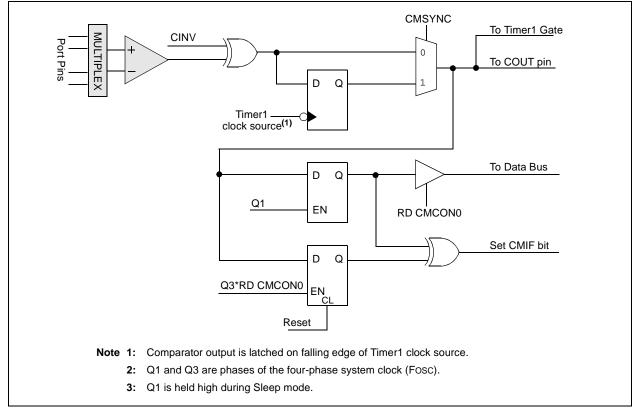

## FIGURE 7-2: COMPARATOR OUTPUT BLOCK DIAGRAM (PIC12F635)

## 7.4 Comparator Control

The CMCON0 register (Register 7-1) provides access to the following comparator features:

- Mode selection

- Output state

- Output polarity

- Input switch

#### 7.4.1 COMPARATOR OUTPUT STATE

Each comparator state can always be read internally via the CxOUT bit of the CMCON0 register. The comparator state may also be directed to the CxOUT pin in the following modes:

#### PIC12F635

- CM<2:0> = 001

- CM<2:0> = 011

- CM<2:0> = 101

#### PIC16F636/639

• CM<2:0> = 110

When one of the above modes is selected, the associated TRIS bit of the CxOUT pin must be cleared.

#### 7.4.2 COMPARATOR OUTPUT POLARITY

Inverting the output of a comparator is functionally equivalent to swapping the comparator inputs. The polarity of a comparator output can be inverted by setting the CXINV bit of the CMCON0 register. Clearing CXINV results in a non-inverted output. A complete table showing the output state versus input conditions and the polarity bit is shown in Table 7-1.

# TABLE 7-1: OUTPUT STATE VS. INPUT CONDITIONS

| Input Conditions | CxINV | CxOUT |

|------------------|-------|-------|

| VIN- > VIN+      | 0     | 0     |

| VIN- < VIN+      | 0     | 1     |

| VIN- > VIN+      | 1     | 1     |

| VIN- < VIN+      | 1     | 0     |

**Note:** CxOUT refers to both the register bit and output pin.

## 7.4.3 COMPARATOR INPUT SWITCH

The inverting input of the comparators may be switched between two analog pins in the following modes:

## PIC12F635

- CM<2:0> = 101

- CM<2:0> = 110

#### PIC16F636/639

- CM<2:0> = 001 (Comparator C1 only)

- CM<2:0> = 010 (Comparators C1 and C2)

In the above modes, both pins remain in Analog mode regardless of which pin is selected as the input. The CIS bit of the CMCON0 register controls the comparator input switch.

| U-0           | U-0                              | R-0                                                                                                                                                    | R/W-0          | U-0              | R/W-1            | R/W-0           | R/W-0 |  |  |  |  |

|---------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------|-----------------|-------|--|--|--|--|

| _             | _                                | IRVST <sup>(1)</sup>                                                                                                                                   | LVDEN          | —                | LVDL2            | LVDL1           | LVDL0 |  |  |  |  |

| bit 7         |                                  |                                                                                                                                                        |                |                  |                  |                 | bit   |  |  |  |  |

| Legend:       |                                  |                                                                                                                                                        |                |                  |                  |                 |       |  |  |  |  |

| R = Readabl   | le bit                           | W = Writable                                                                                                                                           | bit            | U = Unimplen     | nented bit, read | l as '0'        |       |  |  |  |  |

| -n = Value at | POR                              | '1' = Bit is set                                                                                                                                       |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |  |

| bit 7-6       | Unimplemen                       | nted: Read as '                                                                                                                                        | ٥'             |                  |                  |                 |       |  |  |  |  |

| bit 5         | •                                |                                                                                                                                                        |                | Status Flag bit  | (1)              |                 |       |  |  |  |  |

| on o          |                                  | <b>IRVST:</b> Internal Reference Voltage Stable Status Flag bit <sup>(1)</sup><br>1 = Indicates that the PLVD is stable and PLVD interrupt is reliable |                |                  |                  |                 |       |  |  |  |  |

|               |                                  | 0 = Indicates that the PLVD is not stable and PLVD interrupt is reliable                                                                               |                |                  |                  |                 |       |  |  |  |  |

| bit 4         | LVDEN: Low                       | LVDEN: Low-Voltage Detect Module Enable bit                                                                                                            |                |                  |                  |                 |       |  |  |  |  |

|               | 1 = Enables                      | PLVD Module, j                                                                                                                                         | powers up PL   | VD circuit and   | supporting refer | ence circuitry  |       |  |  |  |  |

|               | 0 = Disables                     | PLVD Module,                                                                                                                                           | powers down    | PLVD circuit a   | nd supporting r  | eference circui | try   |  |  |  |  |

| bit 3         | Unimplemer                       | nted: Read as '                                                                                                                                        | 0'             |                  |                  |                 |       |  |  |  |  |

| bit 2-0       | LVDL<2:0>:                       | Low-Voltage De                                                                                                                                         | etection Level | bits (nominal v  | values)          |                 |       |  |  |  |  |

|               | 111 = 4.5V                       |                                                                                                                                                        |                |                  |                  |                 |       |  |  |  |  |

|               | 110 = 4.2V                       | 110 = 4.2V                                                                                                                                             |                |                  |                  |                 |       |  |  |  |  |

|               |                                  | 101 = 4.0V                                                                                                                                             |                |                  |                  |                 |       |  |  |  |  |

|               |                                  | 100 = 2.3V (default)                                                                                                                                   |                |                  |                  |                 |       |  |  |  |  |

|               | 011 = 2.2V<br>010 = 2.1V         |                                                                                                                                                        |                |                  |                  |                 |       |  |  |  |  |

|               | 010 = 2.1V<br>$001 = 2.0V^{(2)}$ | )                                                                                                                                                      |                |                  |                  |                 |       |  |  |  |  |

|               | 000 = Reserved                   |                                                                                                                                                        |                |                  |                  |                 |       |  |  |  |  |

#### REGISTER 8-1: LVDCON: LOW-VOLTAGE DETECT CONTROL REGISTER

- **Note 1:** The IRVST bit is usable only when the HFINTOSC is running.

- 2: Not tested and below minimum operating conditions.

#### TABLE 8-1: REGISTERS ASSOCIATED WITH PROGRAMMABLE LOW-VOLTAGE DETECT

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|-------|-------|-------|-------|-------|-------|--------|----------------------|---------------------------------|

| INTCON | GIE   | PEIE  | T0IE  | INTE  | RAIE  | T0IF  | INTF  | RAIF   | x000 000x            | 0000 000x                       |

| PIE1   | OSFIE | C2IE  | C1IE  | LCDIE | _     | LVDIE | —     | CCP2IE | 0000 -0-0            | 0000 -0-0                       |

| PIR1   | OSFIF | C2IF  | C1IF  | LCDIF | _     | LVDIF | —     | CCP2IF | 0000 -0-0            | 0000 -0-0                       |

| LVDCON | _     | _     | IRVST | LVDEN |       | LVDL2 | LVDL1 | LVDL0  | 00 -100              | 00 -100                         |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used by the PLVD module.

#### FIGURE 11-4: PASSIVE KEYLESS ENTRY (PKE) TRANSPONDER CONFIGURATION EXAMPLE

#### FIGURE 11-3: BIDIRECTIONAL PASSIVE KEYLESS ENTRY (PKE) SYSTEM APPLICATION EXAMPLE

## REGISTER 11-2: CONFIGURATION REGISTER 1

| R/W-0        | R/W-0                                      | R/W-0                                                   | R/W-0          | R/W-0           | R/W-0          | R/W-0          | R/W-0           | R/W-0        |

|--------------|--------------------------------------------|---------------------------------------------------------|----------------|-----------------|----------------|----------------|-----------------|--------------|

| DATOUT1      | DATOUT0                                    | LCXTUN5                                                 | LCXTUN4        | LCXTUN3         | LCXTUN2        | LCXTUN1        | LCXTUN0         | R1PAR        |

| bit 8        |                                            |                                                         |                |                 |                |                |                 | bit 0        |

|              |                                            |                                                         |                |                 |                |                |                 |              |

| Legend:      |                                            |                                                         |                |                 |                |                |                 |              |

| R = Readab   | le bit                                     | W = Writable                                            | e bit          | U = Unimple     | mented bit, r  | ead as '0'     |                 |              |

| -n = Value a | t POR                                      | '1' = Bit is se                                         | et             | '0' = Bit is cl | eared          | x = Bit is unl | known           |              |

|              | 01 = Carrier<br>10 = RSSI o<br>11 = RSSI o | output                                                  |                |                 |                |                |                 |              |

| bit 6-1      |                                            | : <b>0&gt;:</b> LCX Tun<br>0 pF (Default)<br>:<br>63 pF | 0 1            | nce bit         |                |                |                 |              |

| bit 0        | R1PAR: Reg<br>bits                         | gister Parity B                                         | it – set/clear | ed so the 9-bi  | t register con | tains odd pari | ity – an odd nι | umber of set |

#### **REGISTER 11-3: CONFIGURATION REGISTER 2**

| R/W-0   | R/W-0  | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0 |

|---------|--------|---------|---------|---------|---------|---------|---------|-------|

| RSSIFET | CLKDIV | LCYTUN5 | LCYTUN4 | LCYTUN3 | LCYTUN2 | LCYTUN1 | LCYTUN0 | R2PAR |

| bit 8   |        |         |         |         |         |         |         | bit 0 |

| Legend:    |                                   |                                                                    |                             |                                    |           |

|------------|-----------------------------------|--------------------------------------------------------------------|-----------------------------|------------------------------------|-----------|

| R = Read   | R = Readable bit W = Writable bit |                                                                    | U = Unimplemented b         | it, read as '0'                    |           |

| -n = Value | e at POR                          | '1' = Bit is set                                                   | '0' = Bit is cleared        | x = Bit is unknown                 |           |

| bit 8      | 1 = Pull-                         | Pull-down MOSFET on<br>down RSSI MOSFET on<br>down RSSI MOSFET off | LFDATA pad bit (controllab  | le by user in the RSSI mode only)  |           |

| bit 7      | 1 = Carri                         | Carrier Clock Divide-by b<br>ier Clock/4<br>er Clock/1             | it                          |                                    |           |

| bit 6-1    |                                   | <5:0>: LCY Tuning Capa<br>= +0 pF (Default)<br>:<br>= +63 pF       | citance bit                 |                                    |           |

| bit 0      |                                   | l.                                                                 | eared so the 9-bit register | contains odd parity – an odd numbe | er of set |

#### **REGISTER 11-6: CONFIGURATION REGISTER 5**

| R/W-0            | R/W-0                                                      | R/W-0                                                                   | R/W-0             | R/W-0             | R/W-0            | R/W-0           | R/W-0            | R/W-0            |

|------------------|------------------------------------------------------------|-------------------------------------------------------------------------|-------------------|-------------------|------------------|-----------------|------------------|------------------|

| AUTOCHSEL        | AGCSIG                                                     | MODMIN1                                                                 | MODMIN0           | LCZSEN3           | LCZSEN2          | LCZSEN1         | LCZSEN0          | R5PAR            |

| bit 8            |                                                            |                                                                         |                   |                   |                  |                 |                  | bit 0            |

| Legend:          |                                                            |                                                                         |                   |                   |                  |                 |                  |                  |

| •                | •                                                          |                                                                         |                   |                   |                  |                 |                  |                  |

| R = Readable b   |                                                            | W = Writable I                                                          | JIC               | •                 | nented bit, read |                 |                  |                  |

| -n = Value at PC | OR                                                         | '1' = Bit is set                                                        |                   | '0' = Bit is clea | ared             | x = Bit is unkr | nown             |                  |

| bit 8            | 1 = Enabled<br>channel(                                    | .: Auto Channel<br>– AFE selects o<br>(s).<br>I – AFE follows           | channel(s) that I |                   |                  |                 | STAB; or otherwi | se, blocks the   |

| bit 7            | 1 = Enabled<br>when the                                    | nodulator Outpu<br>– No output ur<br>e AGC begins re<br>I – the AFE pas | itil AGC is regue | Ilating at aroun  | d 20 mVpp at i   |                 | AGC Active St    | tatus bit is set |

| bit 6-5          | MODMIN<1:0<br>00 = 50%<br>01 = 75%<br>10 = 25%<br>11 = 12% | <b>D&gt;</b> : Minimum Mc                                               | dulation Depth    | bit               |                  |                 |                  |                  |

| bit 4-1          | LCZSEN<3:0<br>0000 = -0dB<br>:<br>1111 = -30dl             |                                                                         | tivity Reduction  | bit               |                  |                 |                  |                  |

| bit 0            | R5PAR: Regi                                                | ster Parity Bit –                                                       | set/cleared so    | the 9-bit registe | r contains odd   | parity – an odd | d number of set  | bits             |

| Note 1: Ass      | sured monotoni                                             | c increment (or                                                         | decrement) by     | design.           |                  |                 |                  |                  |

# REGISTER 11-7: COLUMN PARITY REGISTER 6

| R/W-0   | R/W-0 |

|---------|---------|---------|---------|---------|---------|---------|---------|-------|

| COLPAR7 | COLPAR6 | COLPAR5 | COLPAR4 | COLPAR3 | COLPAR2 | COLPAR1 | COLPAR0 | R6PAR |

| bit 8   |         |         |         |         |         |         |         | bit 0 |

| Legend:                           |          |                                                                  |                                      |                                                      |

|-----------------------------------|----------|------------------------------------------------------------------|--------------------------------------|------------------------------------------------------|

| R = Readable bit W = Writable bit |          |                                                                  | U = Unimplemented bit,               | read as '0'                                          |

| -n = Value                        | e at POR | '1' = Bit is set                                                 | '0' = Bit is cleared                 | x = Bit is unknown                                   |

|                                   |          |                                                                  |                                      |                                                      |

| bit 8                             |          | 7: Set/Cleared so that this 8th mber of set bits.                | h parity bit + the sum of the Cor    | figuration register row parity bits contain an odd   |

| bit 7                             |          | 6: Set/Cleared such that this 7 odd number of set bits.          | 7th parity bit + the sum of the 7th  | bits in Configuration Registers 0 through 5 contai   |

| bit 6                             |          | 5: Set/Cleared such that this 6 odd number of set bits.          | 6th parity bit + the sum of the 6th  | bits in Configuration Registers 0 through 5 contai   |

| bit 5                             |          | 4: Set/Cleared such that this sold number of set bits.           | 5th parity bit + the sum of the 5th  | bits in Configuration Registers 0 through 5 contai   |

| bit 4                             |          | 3: Set/Cleared such that this 4 odd number of set bits.          | Ith parity bit + the sum of the 4th  | bits in Configuration Registers 0 through 5 contai   |

| bit 3                             |          | 2: Set/Cleared such that this 3 odd number of set bits.          | Brd parity bit + the sum of the 3rd  | bits in Configuration Registers 0 through 5 contai   |

| bit 2                             |          | 1: Set/Cleared such that this 2 odd number of set bits.          | nd parity bit + the sum of the 2nd   | I bits in Configuration Registers 0 through 5 contai |

| bit 1                             |          | <b>0</b> : Set/Cleared such that this 1<br>d number of set bits. | st parity bit + the sum of the 1st b | its in Configuration Registers 0 through 5 contain a |

| bit 0                             | R6PAR:   | Register Parity bit – set/clear                                  | ad so the 9-bit register contains    | odd parity – an odd number of set bits               |

| FIGURE 12-8:              | INT PIN INT           | ERRUPT TIMINO     | 6                                |                     |                        |

|---------------------------|-----------------------|-------------------|----------------------------------|---------------------|------------------------|

| :                         | Q1   Q2   Q3   Q4     | Q1   Q2   Q3   Q4 | Q1   Q2   Q3   Q4                | Q1   Q2   Q3   Q4   | Q1   Q2   Q3   Q4      |

| OSC1 /                    |                       |                   |                                  |                     |                        |

| CLKOUT <sup>(3)</sup>     | (4)                   |                   | \/                               | \/                  |                        |

| INT pin 🕂                 |                       | (1)               | 1 1<br>1 1                       |                     | 1 I<br>1 I<br>1 I      |

| INTF Flag<br>(INTCON<1>)  | , (1) (5)             | ¥ (.)             | Interrupt Latency <sup>(2)</sup> | <b>.</b>            |                        |

| GIE bit<br>(INTCON<7>)    |                       |                   |                                  |                     |                        |

| Instruction Flow          | PC                    |                   | Y PC+1                           |                     | × 0005h                |

| Instruction {             | Inst (PC)             | Inst (PC + 1)     | · _ ·                            | Inst (0004h)        | Inst (0005h)           |

| Instruction {<br>Executed | Inst (PC – 1)         | Inst (PC)         | Dummy Cycle                      | Dummy Cycle         | Inst (0004h)           |

|                           | ag is sampled here (e | <b>3</b>          |                                  | where Toy instructi | an avala tima. Latanav |

- 2: Asynchronous interrupt latency = 3-4 TCY. Synchronous latency = 3 TCY, where TCY = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT is available only in INTOSC and RC Oscillator modes.

- 4: For minimum width of INT pulse, refer to AC specifications in Section 15.0 "Electrical Specifications".

- 5: INTF is enabled to be set any time during the Q4-Q1 cycles.

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4               | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|-------|-------|---------------------|-------|-------|-------|--------|-----------------------|---------------------------------|

| INTCON | GIE   | PEIE  | T0IE  | INTE                | RAIE  | T0IF  | INTF  | RAIF   | 0000 000x             | 0000 000x                       |

| IOCA   | —     | _     | IOCA5 | IOCA4               | IOCA3 | IOCA2 | IOCA1 | IOCA0  | 00 0000               | 00 0000                         |

| PIR1   | EEIF  | LVDIF | CRIF  | C2IF <sup>(1)</sup> | C1IF  | OSFIF | —     | TMR1IF | 0000 00-0             | 0000 00-0                       |

| PIE1   | EEIE  | LVDIE | CRIE  | C2IE <sup>(1)</sup> | C1IE  | OSFIE | _     | TMR1IE | 0000 00-0             | 0000 00-0                       |

#### TABLE 12-6: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0', q = value depends upon condition. Shaded cells are not used by the Interrupt module.

Note 1: PIC16F636/639 only.

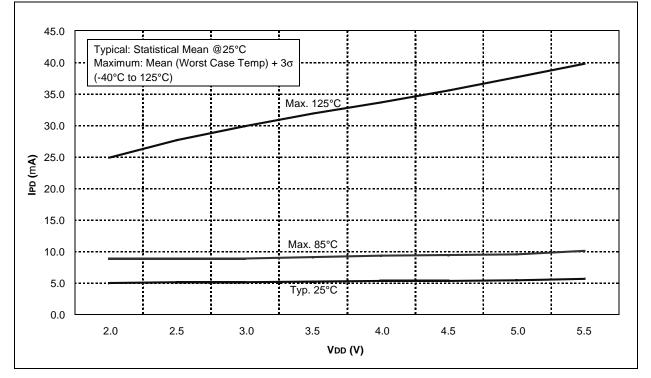

#### 15.1 DC Characteristics: PIC12F635/PIC16F636-I (Industrial) PIC12F635/PIC16F636-E (Extended)

| DC CHARACTERISTICS              |      |                                                                  |                               | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                                 |         |                                                                                      |  |  |

|---------------------------------|------|------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------|--------------------------------------------------------------------------------------|--|--|

| Param<br>No.                    | Sym  | Characteristic                                                   | Min Typ† Max Units Conditions |                                                                                                                                                                                         |                                 |         |                                                                                      |  |  |

| D001<br>D001A<br>D001B<br>D001C | Vdd  | Supply Voltage                                                   | 2.0<br>2.0<br>3.0<br>4.5      |                                                                                                                                                                                         | 5.5<br>5.5<br>5.5<br>5.5<br>5.5 | > > > > | Fosc < = 4 MHz<br>Fosc < = 8 MHz, HFINTOSC, EC<br>Fosc < = 10 MHz<br>Fosc < = 20 MHz |  |  |

| D002                            | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | 1.5*                          | —                                                                                                                                                                                       | _                               | V       | Device in Sleep mode                                                                 |  |  |

| D003                            | VPOR | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —                             | Vss                                                                                                                                                                                     | _                               | V       | See Section 12.3 "Power-on Reset" for details.                                       |  |  |

| D004                            | SVDD | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05*                         | —                                                                                                                                                                                       | —                               | V/ms    | See <b>Section 12.3 "Power-on Reset"</b> for details.                                |  |  |

| D005                            | VBOD | Brown-out Reset                                                  | 2.0                           | 2.1                                                                                                                                                                                     | 2.2                             | V       |                                                                                      |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

# 15.6 DC Characteristics: PIC16F639-I (Industrial)

| DC CHAF      | RACTERIST      | ICS                                                                                                                                                                            |          | g temperati        |             | -40°C ≤              |                          | otherwise stated)<br>TA ≤ +85°C for industrial<br>DD ≤ 3.6V                                        |  |  |

|--------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|-------------|----------------------|--------------------------|----------------------------------------------------------------------------------------------------|--|--|

| Param        |                |                                                                                                                                                                                |          |                    |             |                      |                          | Conditions                                                                                         |  |  |

| No.          | Sym            | Device Characteristics                                                                                                                                                         | Min      | Тур†               | Мах         | Units                | Vdd                      | Note                                                                                               |  |  |

| D010         | IDD            | Supply Current <sup>(1,2,3)</sup>                                                                                                                                              | _        | 11                 | 16          | μΑ                   | 2.0                      | Fosc = 32.768 kHz                                                                                  |  |  |

|              |                |                                                                                                                                                                                | —        | 18                 | 28          | μΑ                   | 3.0                      | LP Oscillator mode                                                                                 |  |  |

| D011         |                |                                                                                                                                                                                | _        | 140                | 240         | μΑ                   | 2.0                      | Fosc = 1 MHz                                                                                       |  |  |

|              |                |                                                                                                                                                                                | —        | 220                | 380         | μΑ                   | 3.0                      | XT Oscillator mode                                                                                 |  |  |

| D012         |                |                                                                                                                                                                                | _        | 260                | 360         | μΑ                   | 2.0                      | Fosc = 4 MHz                                                                                       |  |  |

|              |                |                                                                                                                                                                                | _        | 420                | 650         | μΑ                   | 3.0                      | XT Oscillator mode                                                                                 |  |  |

| D013         |                |                                                                                                                                                                                | _        | 130                | 220         | μΑ                   | 2.0                      | Fosc = 1 MHz                                                                                       |  |  |

|              |                |                                                                                                                                                                                | —        | 215                | 360         | μΑ                   | 3.0                      | EC Oscillator mode                                                                                 |  |  |

| D014         |                |                                                                                                                                                                                | _        | 220                | 340         | μΑ                   | 2.0                      | Fosc = 4 MHz                                                                                       |  |  |

|              |                |                                                                                                                                                                                | —        | 375                | 550         | μΑ                   | 3.0                      | EC Oscillator mode                                                                                 |  |  |

| D015         |                |                                                                                                                                                                                | —        | 8                  | 20          | μΑ                   | 2.0                      | Fosc = 31 kHz                                                                                      |  |  |

|              |                |                                                                                                                                                                                | —        | 16                 | 40          | μA                   | 3.0                      | LFINTOSC mode                                                                                      |  |  |

| D016         |                |                                                                                                                                                                                | _        | 340                | 450         | μA                   | 2.0                      | Fosc = 4 MHz                                                                                       |  |  |

|              |                |                                                                                                                                                                                | _        | 500                | 700         | μA                   | 3.0                      | HFINTOSC mode                                                                                      |  |  |

| D017         |                |                                                                                                                                                                                | _        | 230                | 400         | μA                   | 2.0                      | Fosc = 4 MHz                                                                                       |  |  |

|              |                |                                                                                                                                                                                | _        | 400                | 680         | μA                   | 3.0                      | EXTRC mode                                                                                         |  |  |

| D020         | IPD            | Power-down Base Current <sup>(4)</sup>                                                                                                                                         | _        | 0.15               | 1.2         | μA                   | 2.0                      | WDT, BOR, Comparators,                                                                             |  |  |

|              |                |                                                                                                                                                                                | —        | 0.20               | 1.5         | μΑ                   | 3.0                      | VREF and T1OSC disabled<br>(excludes AFE)                                                          |  |  |

| D021         | IWDT           |                                                                                                                                                                                | _        | 1.2                | 2.2         | μA                   | 2.0                      | WDT Current <sup>(1)</sup>                                                                         |  |  |

|              |                |                                                                                                                                                                                | _        | 2.0                | 4.0         | μA                   | 3.0                      |                                                                                                    |  |  |

| D022A        | IBOR           |                                                                                                                                                                                | _        | 42                 | 60          | μA                   | 3.0                      | BOR Current <sup>(1)</sup>                                                                         |  |  |

| D022B        | ILVD           |                                                                                                                                                                                | _        | 22                 | 28          | μA                   | 2.0                      | PLVD Current                                                                                       |  |  |

|              |                |                                                                                                                                                                                | _        | 25                 | 35          | μA                   | 3.0                      |                                                                                                    |  |  |

| D023         | ICMP           |                                                                                                                                                                                | _        | 32                 | 45          | μA                   | 2.0                      | Comparator Current <sup>(1)</sup>                                                                  |  |  |

|              |                |                                                                                                                                                                                | _        | 60                 | 78          | μA                   | 3.0                      |                                                                                                    |  |  |

| D024A        | <b>IVREFHS</b> |                                                                                                                                                                                | _        | 30                 | 36          | μA                   | 2.0                      | CVREF Current <sup>(1)</sup>                                                                       |  |  |

|              |                |                                                                                                                                                                                | _        | 45                 | 55          | μA                   | 3.0                      | (high-range)                                                                                       |  |  |

| D024B        | IVREFLS        |                                                                                                                                                                                | _        | 39                 | 47          | μA                   | 2.0                      | CVREF Current <sup>(1)</sup>                                                                       |  |  |

|              |                |                                                                                                                                                                                | _        | 59                 | 72          | μA                   | 3.0                      | (low-range)                                                                                        |  |  |

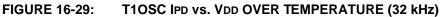

| D025         | IT10SC         |                                                                                                                                                                                | —        | 4.5                | 7.0         | μA                   | 2.0                      | T1OSC Current <sup>(1)</sup>                                                                       |  |  |

|              |                |                                                                                                                                                                                | _        | 5.0                | 8.0         | μA                   | 3.0                      | ]                                                                                                  |  |  |

| D026         | ІАСТ           | Active Current of AFE only<br>(receiving signal)<br>1 LC Input Channel Signal<br>3 LC Input Channel Signals                                                                    | _        | 10<br>13           | —<br>18     | μA<br>μA             | 3.6<br>3.6               | CS = VDD; Input = Continuous      Wave (CW);      Amplitude = 300 mVPP.      All channels enabled. |  |  |

| D027<br>D028 | ISTDBY         | Standby Current of AFE only<br>(not receiving signal)<br>1 LC Input Channel Enabled<br>2 LC Input Channels Enabled<br>3 LC Input Channels Enabled<br>Sleep Current of AFE only | <br><br> | 3<br>4<br>5<br>0.2 | 5<br>6<br>7 | μΑ<br>μΑ<br>μΑ<br>μΑ | 3.6<br>3.6<br>3.6<br>3.6 | CS = VDD; ALERT = VDD                                                                              |  |  |

|              |                | "Typ" column is at 3.0V. 25°C unless othe                                                                                                                                      |          |                    |             |                      |                          | ,                                                                                                  |  |  |

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The test conditions for all <u>IDD measurements</u> in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled. MCU only, Analog Front-End not included.

The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. MCU only, Analog Front-End not included.

3: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

4: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

## 15.12 SPI Timing: Analog Front-End (AFE) for PIC16F639

| AC CHA | RACTER | RISTICS                                             | Standar                                                                                                   | d Operat | ing Cond | itions (unless otherwise stated) |                                                                |  |  |

|--------|--------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------|----------|----------------------------------|----------------------------------------------------------------|--|--|

|        |        |                                                     | Supply Voltage<br>Operating temperature<br>LC Signal Input<br>Carrier Frequency<br>LCCOM connected to Vss |          |          | -40°C ≤                          | /DD ≤ $3.6V$<br>TAMB ≤ $+85$ °C for industrial<br>dal 300 mVPP |  |  |

| Param  | Sym    | Characteristic                                      | Min                                                                                                       | Typ†     | Max      | Units                            | Conditions                                                     |  |  |

| AF33   | FSCLK  | SCLK Frequency                                      | —                                                                                                         | _        | 3        | MHz                              |                                                                |  |  |

| AF34   | Tcssc  | CS fall to first SCLK edge setup time               | 100                                                                                                       | -        | —        | ns                               |                                                                |  |  |

| AF35   | Tsu    | SDI setup time                                      | 30                                                                                                        | —        | —        | ns                               |                                                                |  |  |

| AF36   | THD    | SDI hold time                                       | 50                                                                                                        | _        | —        | ns                               |                                                                |  |  |

| AF37   | Тні    | SCLK high time                                      | 150                                                                                                       | _        | —        | ns                               |                                                                |  |  |

| AF38   | Tlo    | SCLK low time                                       | 150                                                                                                       | _        | _        | ns                               |                                                                |  |  |

| AF39   | TDO    | SDO setup time                                      | —                                                                                                         | _        | 150      | ns                               |                                                                |  |  |

| AF40   | Tsccs  | SCLK last edge to CS rise setup time                | 100                                                                                                       | —        | _        | ns                               |                                                                |  |  |

| AF41   | Тсѕн   | CS high time                                        | 500                                                                                                       | _        | —        | ns                               |                                                                |  |  |

| AF42   | Tcs1   | CS rise to SCLK edge setup time                     | 50                                                                                                        | —        | —        | ns                               |                                                                |  |  |

| AF43   | Tcs0   | SCLK edge to $\overline{\text{CS}}$ fall setup time | 50                                                                                                        | —        | _        | ns                               | SCLK edge when $\overline{\text{CS}}$ is high                  |  |  |

| AF44   | TSPIR  | Rise time of SPI data<br>(SPI Read command)         | _                                                                                                         | 10       | _        | ns                               | VDD = 3.0V. Time is measured from 10% to 90% of amplitude      |  |  |

| AF45   | TSPIF  | Fall time of SPI data<br>(SPI Read command)         | _                                                                                                         | 10       | _        | ns                               | VDD = 3.0V. Time is measured from 90% to 10% of amplitude      |  |  |

\* Parameter is characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

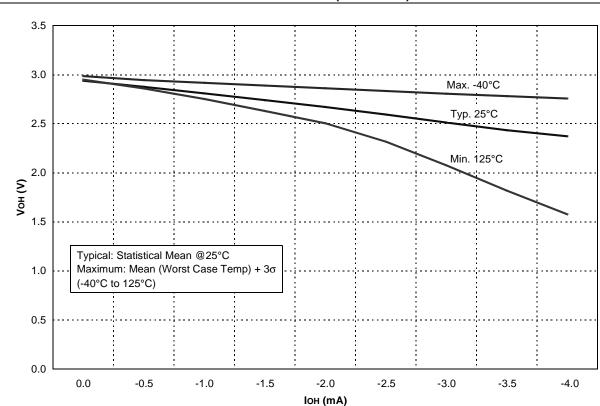

FIGURE 16-25: VOH vs. IOH OVER TEMPERATURE (VDD = 3.0V)

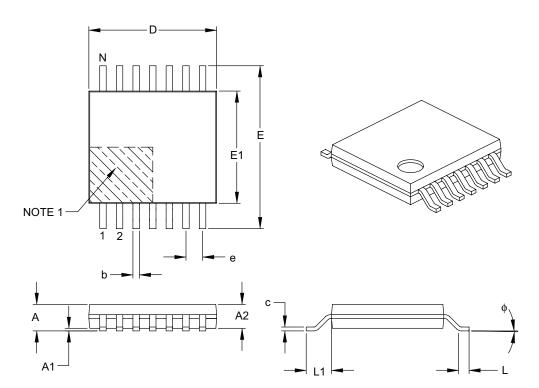

#### 14-Lead Plastic Thin Shrink Small Outline (ST) – 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units                   | MILLIMETERS |          |      |  |

|--------------------------|-------------------------|-------------|----------|------|--|

|                          | <b>Dimension Limits</b> | MIN         | NOM      | MAX  |  |

| Number of Pins           | N                       |             | 14       |      |  |

| Pitch                    | e                       |             | 0.65 BSC |      |  |

| Overall Height           | A                       | -           | -        | 1.20 |  |

| Molded Package Thickness | A2                      | 0.80        | 1.00     | 1.05 |  |

| Standoff                 | A1                      | 0.05        | -        | 0.15 |  |

| Overall Width            | E                       | 6.40 BSC    |          |      |  |

| Molded Package Width     | E1                      | 4.30        | 4.40     | 4.50 |  |

| Molded Package Length    | D                       | 4.90        | 5.00     | 5.10 |  |

| Foot Length              | L                       | 0.45        | 0.60     | 0.75 |  |

| Footprint                | L1                      | 1.00 REF    |          |      |  |

| Foot Angle               | φ                       | 0°          | -        | 8°   |  |

| Lead Thickness           | С                       | 0.09        | -        | 0.20 |  |

| Lead Width               | b                       | 0.19        | -        | 0.30 |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-087B

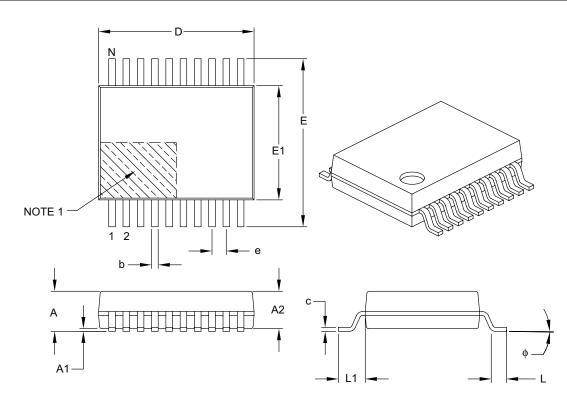

#### 20-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |          |      |  |

|--------------------------|------------------|-------------|----------|------|--|

|                          | Dimension Limits | MIN         | NOM      | MAX  |  |

| Number of Pins           | N                |             | 20       |      |  |

| Pitch                    | e                |             | 0.65 BSC |      |  |

| Overall Height           | A                | -           | -        | 2.00 |  |

| Molded Package Thickness | A2               | 1.65        | 1.75     | 1.85 |  |

| Standoff                 | A1               | 0.05        | -        | -    |  |

| Overall Width            | E                | 7.40        | 7.80     | 8.20 |  |

| Molded Package Width     | E1               | 5.00        | 5.30     | 5.60 |  |

| Overall Length           | D                | 6.90        | 7.20     | 7.50 |  |

| Foot Length              | L                | 0.55        | 0.75     | 0.95 |  |

| Footprint                | L1               | 1.25 REF    |          |      |  |

| Lead Thickness           | С                | 0.09        | -        | 0.25 |  |

| Foot Angle               | φ                | 0°          | 4°       | 8°   |  |

| Lead Width               | b                | 0.22        | -        | 0.38 |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B