# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, WDT                                    |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 16-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 16-QFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f636-i-ml |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

#### **PIC12F635 PINOUT DESCRIPTIONS TABLE 1-1:**

| Name                    | Function | Input<br>Type | Output<br>Type | Description                                                                                                                                             |

|-------------------------|----------|---------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| GP0/C1IN+/ICSPDAT/ULPWU | GP0      | TTL           |                | General purpose I/O. Individually controlled<br>interrupt-on-change. Individually enabled pull-up/pull-down.<br>Selectable Ultra Low-Power Wake-up pin. |

|                         | C1IN+    | AN            | _              | Comparator 1 input – positive.                                                                                                                          |

|                         | ICSPDAT  | TTL           | CMOS           | Serial programming data I/O.                                                                                                                            |

|                         | ULPWU    | AN            |                | Ultra Low-Power Wake-up input.                                                                                                                          |

| GP1/C1IN-/ICSPCLK       | GP1      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change. Individually enabled pull-up/pull-down.                                               |

|                         | C1IN-    | AN            | _              | Comparator 1 input – negative.                                                                                                                          |

|                         | ICSPCLK  | ST            | _              | Serial programming clock.                                                                                                                               |

| GP2/T0CKI/INT/C1OUT     | GP2      | ST            | CMOS           | General purpose I/O. Individually controlled interrupt-on-change. Individually enabled pull-up/pull-down.                                               |

|                         | T0CKI    | ST            | _              | External clock for Timer0.                                                                                                                              |

|                         | INT      | ST            | _              | External interrupt.                                                                                                                                     |

|                         | C1OUT    | _             | CMOS           | Comparator 1 output.                                                                                                                                    |

| GP3/MCLR/Vpp            | GP3      | TTL           | _              | General purpose input. Individually controlled interrupt-on-change.                                                                                     |

|                         | MCLR     | ST            | _              | Master Clear Reset. Pull-up enabled when configured as MCL                                                                                              |

|                         | Vpp      | ΗV            |                | Programming voltage.                                                                                                                                    |

| GP4/T1G/OSC2/CLKOUT     | GP4      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change. Individually enabled pull-up/pull-down.                                               |

|                         | T1G      | ST            | _              | Timer1 gate.                                                                                                                                            |

|                         | OSC2     | _             | XTAL           | XTAL connection.                                                                                                                                        |

|                         | CLKOUT   | _             | CMOS           | TOSC/4 reference clock.                                                                                                                                 |

| GP5/T1CKI/OSC1/CLKIN    | GP5      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change. Individually enabled pull-up/pull-down.                                               |

|                         | T1CKI    | ST            |                | Timer1 clock.                                                                                                                                           |

|                         | OSC1     | XTAL          |                | XTAL connection.                                                                                                                                        |

|                         | CLKIN    | ST            | _              | Tosc reference clock.                                                                                                                                   |

| Vdd                     | Vdd      | D             |                | Power supply for microcontroller.                                                                                                                       |

|                         | Vss      | D             |                | Ground reference for microcontroller.                                                                                                                   |

HV = High Voltage TTL = TTL compatible input

ST

XTAL = Crystal

## PIC12F635/PIC16F636/639

| Addr | Name                 | Bit 7      | Bit 6                        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1     | Bit 0               | Value on<br>POR/BOR/<br>WUR | Page      |

|------|----------------------|------------|------------------------------|--------------|--------------|--------------|--------------|-----------|---------------------|-----------------------------|-----------|

| Bank | 1                    |            |                              |              |              |              |              |           |                     |                             |           |

| 80h  | INDF                 |            | ig this loca<br>vsical regis |              | contents of  | FSR to ad    | dress data   | memory    |                     | XXXX XXXX                   | 32,137    |

| 81h  | OPTION_REG           | RAPU       | INTEDG                       | TOCS         | T0SE         | PSA          | PS2          | PS1       | PS0                 | 1111 1111                   | 63,137    |

| 82h  | PCL                  | Program (  | Counter's (                  | PC) Least    | Significant  | Byte         |              |           |                     | 0000 0000                   | 32,137    |

| 83h  | STATUS               | IRP        | RP1                          | RP0          | TO           | PD           | Z            | DC        | С                   | 0001 1xxx                   | 26,137    |

| 84h  | FSR                  | Indirect D | ata Memor                    | y Address    | Pointer      |              |              |           |                     | xxxx xxxx                   | 32,137    |

| 85h  | TRISA                | —          | _                            | TRISA5       | TRISA4       | TRISA3       | TRISA2       | TRISA1    | TRISA0              | 11 1111                     | 11 1111   |

| 86h  | _                    | Unimplem   | nented                       |              |              |              |              |           |                     | —                           |           |

| 87h  | TRISC                |            |                              | TRISC5       | TRISC4       | TRISC3       | TRISC2       | TRISC1    | TRISC0              | 11 1111                     | 11 1111   |

| 88h  | _                    | Unimplem   | nented                       |              |              |              |              |           |                     | —                           |           |

| 89h  | _                    | Unimplem   | nented                       |              |              |              |              |           |                     | _                           | _         |

| 8Ah  | PCLATH               | _          | _                            | —            | Write Buff   | er for uppe  | er 5 bits of | Program C | ounter              | 0 0000                      | 32,137    |

| 8Bh  | INTCON               | GIE        | PEIE                         | TOIE         | INTE         | RAIE         | T0IF         | INTF      | RAIF <sup>(3)</sup> | 0000 000x                   | 28,137    |

| 8Ch  | PIE1                 | EEIE       | LVDIE                        | CRIE         | C2IE         | C1IE         | OSFIE        | _         | TMR1IE              | 0000 00-0                   | 29,137    |

| 8Dh  | —                    | Unimplem   | nented                       |              |              |              |              |           |                     | —                           | _         |

| 8Eh  | PCON                 | _          | _                            | ULPWUE       | SBOREN       | WUR          | _            | POR       | BOR                 | 01 q-qq                     | Ou u-uu   |

| 8Fh  | OSCCON               |            | IRCF2                        | IRCF1        | IRCF0        | OSTS         | HTS          | LTS       | SCS                 | -110 q000                   | -110 x000 |

| 90h  | OSCTUNE              | —          | _                            |              | TUN4         | TUN3         | TUN2         | TUN1      | TUN0                | 0 0000                      | u uuuu    |

| 91h  | —                    | Unimplem   | nented                       |              |              |              |              |           |                     | —                           | _         |

| 92h  | —                    | Unimplem   | nented                       |              |              |              |              |           |                     | —                           | _         |

| 93h  |                      | Unimplem   | nented                       |              |              |              |              |           |                     | -                           | _         |

| 94h  | LVDCON               | _          | _                            | IRVST        | LVDEN        | _            | LVDL2        | LVDL1     | LVDL0               | 00 -000                     | 00 -000   |

| 95h  | WPUDA <sup>(2)</sup> | —          | —                            | WPUDA5       | WPUDA4       | —            | WPUDA2       | WPUDA1    | WPUDA0              | 11 -111                     | 11 -111   |

| 96h  | IOCA                 | —          | _                            | IOCA5        | IOCA4        | IOCA3        | IOCA2        | IOCA1     | IOCA0               | 00 0000                     | 00 0000   |

| 97h  | WDA <sup>(2)</sup>   | —          | —                            | WDA5         | WDA4         | —            | WDA2         | WDA1      | WDA0                | 11 -111                     | 11 -111   |

| 9Bh  | _                    | Unimplem   | nented                       |              |              |              |              |           |                     | —                           | —         |

| 99h  | VRCON                | VREN       | _                            | VRR          | —            | VR3          | VR2          | VR1       | VR0                 | 0-0- 0000                   | 0-0- 0000 |

| 9Ah  | EEDAT                | EEDAT7     | EEDAT6                       | EEDAT5       | EEDAT4       | EEDAT3       | EEDAT2       | EEDAT1    | EEDAT0              | 0000 0000                   | 0000 0000 |

| 9Bh  | EEADR                | EEADR7     | EEADR6                       | EEADR5       | EEADR4       | EEADR3       | EEADR2       | EEADR1    | EEADR0              | 0000 0000                   | 0000 0000 |

| 9Ch  | EECON1               | —          | _                            | _            | —            | WRERR        | WREN         | WR        | RD                  | x000                        | q000      |

| 9Dh  | EECON2               | EEPROM     | Control R                    | egister 2 (r | not a physic | cal register | r)           |           |                     |                             |           |

| 9Eh  | _                    | Unimplem   | nented                       |              |              |              |              |           |                     | _                           | _         |

| 9Fh  | _                    | Unimplem   | nented                       |              |              |              |              |           |                     | _                           | _         |

#### TABLE 2-4: PIC16F636/639 SPECIAL FUNCTION REGISTERS SUMMARY BANK 1

Legend: -= Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: RA3 pull-up is enabled when pin is configured as MCLR in the Configuration Word register.

3: MCLR and WDT Reset do not affect the previous value data latch. The RAIF bit will be cleared upon Reset but will set again if the mismatch exists.

#### 3.5.2.1 OSCTUNE Register

The HFINTOSC is factory calibrated but can be adjusted in software by writing to the OSCTUNE register (Register 3-2).

The default value of the OSCTUNE register is '0'. The value is a 5-bit two's complement number.

When the OSCTUNE register is modified, the HFINTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

#### REGISTER 3-2: OSCTUNE: OSCILLATOR TUNING REGISTER

| U-0   | U-0      | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|----------|-----|-------|-------|-------|-------|-------|

| —     | — — TUN4 |     | TUN3  | TUN2  | TUN1  | TUN0  |       |

| bit 7 |          |     |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | Unimplemented: Read as '0'                                        |

|---------|-------------------------------------------------------------------|

| bit 4-0 | TUN<4:0>: Frequency Tuning bits                                   |

|         | 01111 = Maximum frequency                                         |

|         | 01110 =                                                           |

|         | •                                                                 |

|         | •                                                                 |

|         | •                                                                 |

|         | 00001 =                                                           |

|         | 00000 = Oscillator module is running at the calibrated frequency. |

|         | 11111 =                                                           |

|         | •                                                                 |

|         | •                                                                 |

|         | •                                                                 |

|         | 10000 = Minimum frequency                                         |

## PIC12F635/PIC16F636/639

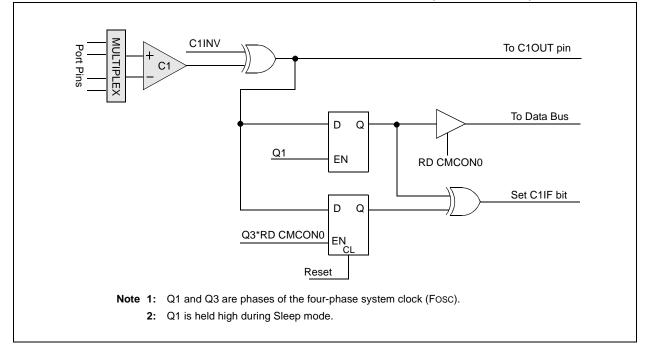

#### FIGURE 7-3: COMPARATOR C1 OUTPUT BLOCK DIAGRAM (PIC16F636/639)

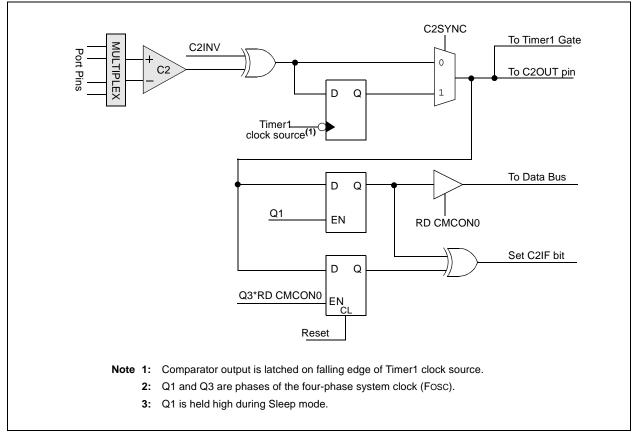

#### FIGURE 7-4: COMPARATOR C2 OUTPUT BLOCK DIAGRAM (PIC16F636/639)

### 7.11 Comparator Voltage Reference

The Comparator Voltage Reference module provides an internally generated voltage reference for the comparators. The following features are available:

- Independent from Comparator operation

- Two 16-level voltage ranges

- · Output clamped to Vss

- Ratiometric with VDD

- Fixed Voltage Reference

The VRCON register (Register 7-5) controls the Voltage Reference module shown in Figure 7-10.

#### 7.11.1 INDEPENDENT OPERATION

The comparator voltage reference is independent of the comparator configuration. Setting the VREN bit of the VRCON register will enable the voltage reference.

#### 7.11.2 OUTPUT VOLTAGE SELECTION

The CVREF voltage reference has 2 ranges with 16 voltage levels in each range. Range selection is controlled by the VRR bit of the VRCON register. The 16 levels are set with the VR<3:0> bits of the VRCON register.

The CVREF output voltage is determined by the following equations:

#### EQUATION 7-1: CVREF OUTPUT VOLTAGE (INTERNAL CVREF)

VRR = 1 (low range):  $CVREF = (VR < 3:0 > /24) \times VDD$  VRR = 0 (high range):  $CVREF = (VDD/4) + (VR < 3:0 > \times VDD/32)$

#### EQUATION 7-2: CVREF OUTPUT VOLTAGE (EXTERNAL CVREF)

VRR = 1 (low range):

$CVREF = (VR < 3:0 > /24) \times VLADDER$

VRR = 0 (high range):

$CVREF = (VLADDER/4) + (VR < 3:0 > \times VLADDER/32)$

VLADDER = VDD or ([VREF+] - [VREF-]) or VREF+

The full range of VSS to VDD cannot be realized due to the construction of the module. See Figure 7-10.

#### 7.11.3 OUTPUT CLAMPED TO Vss

The CVREF output voltage can be set to Vss with no power consumption by configuring VRCON as follows:

- VREN = 0

- VRR = 1

- VR<3:0> = 0000

This allows the comparator to detect a zero-crossing while not consuming additional CVREF module current.

#### 7.11.4 OUTPUT RATIOMETRIC TO VDD

The comparator voltage reference is VDD derived and therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the Comparator Voltage Reference can be found in **Section 15.0 "Electrical Specifications"**.

## TABLE 7-2:SUMMARY OF REGISTERS ASSOCIATED WITH THE COMPARATOR AND VOLTAGE<br/>REFERENCE MODULES

| Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|-------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| CMCON0 | —     | COUT  | _      | CINV   | CIS    | CM2    | CM1    | CM0    | -0-0 0000            | -0-0 0000                       |

| CMCON1 | _     | —     | _      | _      | —      | _      | T1GSS  | CMSYNC | 10                   | 10                              |

| INTCON | GIE   | PEIE  | TOIE   | INTE   | RAIE   | T0IF   | INTF   | RAIF   | x000 000x            | x000 000x                       |

| PIE1   | EEIE  | LVDIE | CRIE   |        | C1IE   | OSFIE  |        | TMR1IE | 000- 00-0            | 000- 00-0                       |

| PIR1   | EEIF  | LVDIF | CRIF   | _      | C1IF   | OSFIF  | _      | TMR1IF | 000- 00-0            | 000- 00-0                       |

| PORTA  | _     | —     | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xx xxxx              | uu uuuu                         |

| PORTC  | _     | —     | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xx xxxx              | uu uuuu                         |

| TRISA  | _     | —     | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111              | 11 1111                         |

| TRISC  | _     | —     | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 11 1111              | 11 1111                         |

| VRCON  | VREN  | _     | VRR    | _      | VR3    | VR2    | VR1    | VR0    | 0-0- 0000            | 0-0- 0000                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for comparator.

NOTES:

#### 11.20 Soft Reset

The AFE issues a Soft Reset in the following events:

- a) After Power-on Reset (POR),

- b) After Inactivity timer time-out,

- c) If an "Abort" occurs,

- d) After receiving SPI Soft Reset command.

The "Abort" occurs if there is no positive signal detected at the end of the AGC stabilization period (TAGC). The Soft Reset initializes internal circuits and brings the AFE into a low current Standby mode operation. The internal circuits that are initialized by the Soft Reset include:

- Output Enable Filter

- AGC circuits

- Demodulator

- 32 kHz Internal Oscillator

The Soft Reset has no effect on the Configuration register setup, except for some of the AFE Status Register 7 bits. (Register 11-8).

The circuit initialization takes one internal clock cycle (1/32 kHz = 31.25  $\mu$ s). During the initialization, the modulation transistors between each input and LCCOM pins are turned-on to discharge any internal/external parasitic charges. The modulation transistors are turned-off immediately after the initialization time.

The Soft Reset is executed in Active mode only. It is not valid in Standby mode.

### 11.21 Minimum Modulation Depth Requirement for Input Signal

The AFE demodulates the modulated input signal if the modulation depth of the input signal is greater than the minimum requirement that is programmed in the AFE Configuration Register 5 (Register 11-6). Figure 11-7 shows the definition of the modulation depth and examples. MODMIN<6:5> of the Configuration Register 5 offer four options. They are 75%, 50%, 25% and 12%, with a default setting of 50%.

The purpose of this feature is to enhance the demodulation integrity of the input signal. The 12% setting is the best choice for the input signal with weak modulation depth, which is typically observed near the high-voltage base station antenna and also at far-distance from the base station antenna. It gives the best demodulation sensitivity, but is very susceptible to noise spikes that can result in a bit detection error. The 75% setting can reduce the bit errors caused by noise, but gives the least demodulation sensitivity. See Table 11-3 for minimum modulation depth requirement settings.

#### TABLE 11-3: SETTING FOR MINIMUM MODULATION DEPTH REQUIREMENT

| _     | IIN Bits<br>Register 5) | Modulation Depth |

|-------|-------------------------|------------------|

| Bit 6 | Bit 5                   |                  |

| 0     | 0                       | 50% (default)    |

| 0     | 1                       | 75%              |

| 1     | 0                       | 25%              |

| 1     | 1                       | 12%              |

## 12.0 SPECIAL FEATURES OF THE CPU

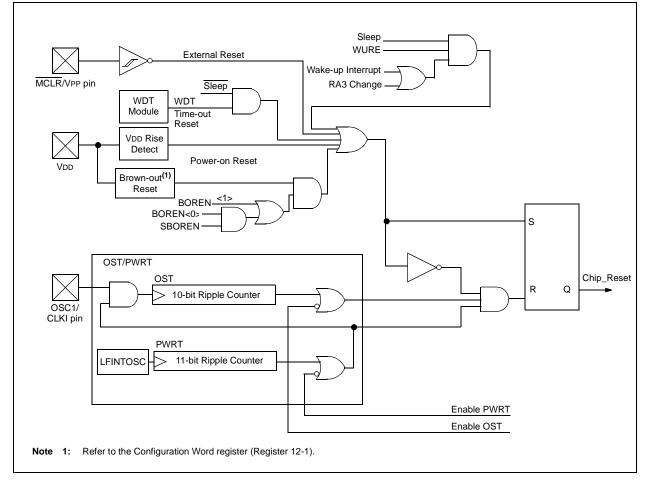

The PIC12F635/PIC16F636/639 has a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving features and offer code protection.

These features are:

- Reset

- Power-on Reset (POR)

- Wake-up Reset (WUR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- · Oscillator selection

- Sleep

- Code protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup>

The PIC12F635/PIC16F636/639 has two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 64 ms (nominal) on power-up only, designed to keep the part in Reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which can use the Power-up Timer to provide at least a nominal 64 ms Reset. With these three functions on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low-current Power-down mode. The user can wake-up from Sleep through:

- External Reset

- Watchdog Timer Wake-up

- An Interrupt

Several oscillator options are also made available to allow the part to fit the application. The INTOSC option saves system cost while the LP crystal option saves power. A set of Configuration bits are used to select various options (see Register 12-1).

## 12.1 Configuration Bits

The Configuration Word bits can be programmed (read as '0'), or left unprogrammed (read as '1') to select various device configurations as shown in Register 12-1. These bits are mapped in program memory location 2007h.

Note: Address 2007h is beyond the user program memory space. It belongs to the special configuration memory space (2000h-3FFFh), which can be accessed only during programming. See "PIC12F6XX/16F6XX Memory Programming Specification" (DS41204) for more information.

#### 12.2 Reset

The PIC12F635/PIC16F636/639 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) Wake-up Reset (WUR)

- c) WDT Reset during normal operation

- d) WDT Reset during Sleep

- e) MCLR Reset during normal operation

- f) MCLR Reset during Sleep

- g) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- Power-on Reset

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

- Brown-out Reset

They are not affected by a WDT wake-up since this is viewed as the resumption of normal operation. TO and  $\overline{PD}$  bits are set or cleared differently in different Reset situations, as indicated in Table 12-3. These bits are used in software to determine the nature of the Reset. See Table 12-4 for a full description of Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 12-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See **Section 15.0** "**Electrical Specifications**" for pulse width specifications.

#### FIGURE 12-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

## 15.6 DC Characteristics: PIC16F639-I (Industrial)

| DC CHAF      | RACTERIST      | ICS                                                                                                                                                                            |          | g temperati        |             | -40°C ≤        |                          | otherwise stated)<br>TA ≤ +85°C for industrial<br>DD ≤ 3.6V                                     |  |  |

|--------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|-------------|----------------|--------------------------|-------------------------------------------------------------------------------------------------|--|--|

| Param        |                |                                                                                                                                                                                |          |                    |             |                |                          | Conditions                                                                                      |  |  |

| No.          | Sym            | Device Characteristics                                                                                                                                                         | Min      | Тур†               | Мах         | Units          | Vdd                      | Note                                                                                            |  |  |

| D010         | IDD            | Supply Current <sup>(1,2,3)</sup>                                                                                                                                              | _        | 11                 | 16          | μA             | 2.0                      | Fosc = 32.768 kHz                                                                               |  |  |

|              |                |                                                                                                                                                                                | —        | 18                 | 28          | μΑ             | 3.0                      | LP Oscillator mode                                                                              |  |  |

| D011         |                |                                                                                                                                                                                | _        | 140                | 240         | μΑ             | 2.0                      | Fosc = 1 MHz                                                                                    |  |  |

|              |                |                                                                                                                                                                                | —        | 220                | 380         | μΑ             | 3.0                      | XT Oscillator mode                                                                              |  |  |

| D012         |                |                                                                                                                                                                                | _        | 260                | 360         | μΑ             | 2.0                      | Fosc = 4 MHz                                                                                    |  |  |

|              |                |                                                                                                                                                                                | _        | 420                | 650         | μΑ             | 3.0                      | XT Oscillator mode                                                                              |  |  |

| D013         |                |                                                                                                                                                                                | _        | 130                | 220         | μΑ             | 2.0                      | Fosc = 1 MHz                                                                                    |  |  |

|              |                |                                                                                                                                                                                | —        | 215                | 360         | μΑ             | 3.0                      | EC Oscillator mode                                                                              |  |  |

| D014         |                |                                                                                                                                                                                | —        | 220                | 340         | μΑ             | 2.0                      | Fosc = 4 MHz                                                                                    |  |  |

|              |                |                                                                                                                                                                                | _        | 375                | 550         | μΑ             | 3.0                      | EC Oscillator mode                                                                              |  |  |

| D015         |                |                                                                                                                                                                                | _        | 8                  | 20          | μA             | 2.0                      | Fosc = 31 kHz                                                                                   |  |  |

|              |                |                                                                                                                                                                                | _        | 16                 | 40          | μΑ             | 3.0                      | LFINTOSC mode                                                                                   |  |  |

| D016         |                |                                                                                                                                                                                | _        | 340                | 450         | μΑ             | 2.0                      | Fosc = 4 MHz                                                                                    |  |  |

|              |                |                                                                                                                                                                                | _        | 500                | 700         | μΑ             | 3.0                      | HFINTOSC mode                                                                                   |  |  |

| D017         |                |                                                                                                                                                                                | _        | 230                | 400         | μΑ             | 2.0                      | Fosc = 4 MHz                                                                                    |  |  |

|              |                |                                                                                                                                                                                | _        | 400                | 680         | μΑ             | 3.0                      | EXTRC mode                                                                                      |  |  |

| D020         | IPD            | Power-down Base Current <sup>(4)</sup>                                                                                                                                         | _        | 0.15               | 1.2         | μΑ             | 2.0                      | WDT, BOR, Comparators,                                                                          |  |  |

|              |                |                                                                                                                                                                                | _        | 0.20               | 1.5         | μΑ             | 3.0                      | VREF and T1OSC disabled<br>(excludes AFE)                                                       |  |  |

| D021         | IWDT           |                                                                                                                                                                                | _        | 1.2                | 2.2         | μΑ             | 2.0                      | WDT Current <sup>(1)</sup>                                                                      |  |  |

|              |                |                                                                                                                                                                                | _        | 2.0                | 4.0         | μA             | 3.0                      |                                                                                                 |  |  |

| D022A        | IBOR           |                                                                                                                                                                                | _        | 42                 | 60          | μΑ             | 3.0                      | BOR Current <sup>(1)</sup>                                                                      |  |  |

| D022B        | ILVD           |                                                                                                                                                                                | _        | 22                 | 28          | μA             | 2.0                      | PLVD Current                                                                                    |  |  |

|              |                |                                                                                                                                                                                | _        | 25                 | 35          | μΑ             | 3.0                      |                                                                                                 |  |  |

| D023         | ICMP           |                                                                                                                                                                                | _        | 32                 | 45          | μΑ             | 2.0                      | Comparator Current <sup>(1)</sup>                                                               |  |  |

|              |                |                                                                                                                                                                                | _        | 60                 | 78          | μΑ             | 3.0                      |                                                                                                 |  |  |

| D024A        | <b>IVREFHS</b> |                                                                                                                                                                                | _        | 30                 | 36          | μΑ             | 2.0                      | CVREF Current <sup>(1)</sup>                                                                    |  |  |

|              |                |                                                                                                                                                                                | _        | 45                 | 55          | μΑ             | 3.0                      | (high-range)                                                                                    |  |  |

| D024B        | IVREFLS        |                                                                                                                                                                                | _        | 39                 | 47          | μΑ             | 2.0                      | CVREF Current <sup>(1)</sup>                                                                    |  |  |

|              |                |                                                                                                                                                                                | _        | 59                 | 72          | μΑ             | 3.0                      | (low-range)                                                                                     |  |  |

| D025         | IT10SC         |                                                                                                                                                                                | —        | 4.5                | 7.0         | μA             | 2.0                      | T1OSC Current <sup>(1)</sup>                                                                    |  |  |

|              |                |                                                                                                                                                                                | _        | 5.0                | 8.0         | μA             | 3.0                      | 7                                                                                               |  |  |

| D026         | ІАСТ           | Active Current of AFE only<br>(receiving signal)<br>1 LC Input Channel Signal<br>3 LC Input Channel Signals                                                                    | _        | 10<br>13           | —<br>18     | μΑ<br>μΑ       | 3.6<br>3.6               | CS = VDD; Input = Continuous     Wave (CW);     Amplitude = 300 mVPP.     All channels enabled. |  |  |

| D027<br>D028 | ISTDBY         | Standby Current of AFE only<br>(not receiving signal)<br>1 LC Input Channel Enabled<br>2 LC Input Channels Enabled<br>3 LC Input Channels Enabled<br>Sleep Current of AFE only | <br><br> | 3<br>4<br>5<br>0.2 | 5<br>6<br>7 | μΑ<br>μΑ<br>μΑ | 3.6<br>3.6<br>3.6<br>3.6 | $\overline{CS} = VDD; \overline{ALERT} = VDD$<br>$\overline{CS} = VDD; \overline{ALERT} = VDD$  |  |  |

|              |                | "Typ" column is at 3.0V. 25°C unless othe                                                                                                                                      |          |                    |             |                |                          | ,                                                                                               |  |  |

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The test conditions for all <u>IDD measurements</u> in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled. MCU only, Analog Front-End not included.

The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. MCU only, Analog Front-End not included.

3: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

4: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

#### TABLE 15-2: OSCILLATOR PARAMETERS

|              | Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                                        |                   |      |      |      |                                                                   |                                                                                                       |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------|------|------|------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No. | Sym                                                                                                                  | Characteristic                                         | Freq<br>Tolerance | Min  | Тур† | Max  | Units                                                             | Conditions                                                                                            |  |  |

| OS06         | TWARM                                                                                                                | Internal Oscillator Switch when running <sup>(3)</sup> | —                 |      | —    | 2    | Tosc                                                              | Slowest clock                                                                                         |  |  |

| OS07         | Tsc                                                                                                                  | Fail-Safe Sample Clock<br>Period <sup>(1)</sup>        | —                 | _    | 21   | —    | ms                                                                | LFINTOSC/64                                                                                           |  |  |

| OS08         | HFosc                                                                                                                | Internal Calibrated                                    | ±1%               | 7.92 | 8.0  | 8.08 | MHz                                                               | VDD = 3.5V, 25°C                                                                                      |  |  |

|              | HFINTOSC Frequency <sup>(2)</sup>                                                                                    | ±2%                                                    | 7.84              | 8.0  | 8.16 | MHz  | $2.5V \le VDD \le 5.5V$ ,<br>$0^{\circ}C \le TA \le +85^{\circ}C$ |                                                                                                       |  |  |

|              |                                                                                                                      |                                                        | ±5%               | 7.60 | 8.0  | 8.40 | MHz                                                               | $2.0V \le VDD \le 5.5V$ ,<br>-40°C $\le$ TA $\le$ +85°C (Ind.),<br>-40°C $\le$ TA $\le$ +125°C (Ext.) |  |  |

| OS09*        | LFosc                                                                                                                | Internal Uncalibrated<br>LFINTOSC Frequency            | —                 | 15   | 31   | 45   | kHz                                                               |                                                                                                       |  |  |

| OS10*        | TIOSCST                                                                                                              | HFINTOSC Oscillator                                    | _                 | 5.5  | 12   | 24   | μs                                                                | VDD = 2.0V, -40°C to +85°C                                                                            |  |  |

|              |                                                                                                                      | Wake-up from Sleep                                     | —                 | 3.5  | 7    | 14   | μs                                                                | VDD = 3.0V, -40°C to +85°C                                                                            |  |  |

|              |                                                                                                                      | Start-up Time                                          | —                 | 3    | 6    | 11   | μs                                                                | $VDD = 5.0V, -40^{\circ}C \text{ to } +85^{\circ}C$                                                   |  |  |

.... . . N . .

> \* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- 2: To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

3: By design.

#### TABLE 15-6: COMPARATOR SPECIFICATIONS

| Standard O | neratina | Conditions | (unlass | otherwise s | (hatet |

|------------|----------|------------|---------|-------------|--------|

| Stanuaru U | perating | Conditions | lainess | otherwise s | (aleu) |

| Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |         |                                           |         |     |       |           |       |               |  |

|---------------------------------------------------------------|---------|-------------------------------------------|---------|-----|-------|-----------|-------|---------------|--|

| Param<br>No.                                                  | Sym     | Characteristics                           |         | Min | Тур†  | Мах       | Units | Comments      |  |

| CM01                                                          | Vos     | Input Offset Voltage                      |         | —   | ± 5.0 | ± 10      | mV    | (Vdd - 1.5)/2 |  |

| CM02                                                          | Vсм     | Input Common Mode Voltage                 |         | 0   | —     | Vdd - 1.5 | V     |               |  |

| CM03*                                                         | CMRR    | Common Mode Rejection Ratio               |         | +55 | —     | —         | dB    |               |  |

| CM04*                                                         | Trt     | Response Time                             | Falling | _   | 150   | 600       | ns    | (NOTE 1)      |  |

|                                                               |         |                                           | Rising  | —   | 200   | 1000      | ns    |               |  |

| CM05*                                                         | Тмc2coV | Comparator Mode Change to<br>Output Valid |         | _   | _     | 10        | μs    |               |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Response time is measured with one comparator input at (VDD - 1.5)/2 - 100 mV to (VDD - 1.5)/2 + 20 mV.

#### TABLE 15-7: COMPARATOR VOLTAGE REFERENCE (CVREF) SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                              |     |                  |                |            |                                             |  |

|----------------------------------------------------------------------------------------------------------------------|------|------------------------------|-----|------------------|----------------|------------|---------------------------------------------|--|

| Param<br>No.                                                                                                         | Sym  | Characteristics              | Min | Тур†             | Max            | Units      | Comments                                    |  |

| CV01*                                                                                                                | CLSB | Step Size <sup>(2)</sup>     | _   | VDD/24<br>VDD/32 |                | V<br>V     | Low Range (VRR = 1)<br>High Range (VRR = 0) |  |

| CV02*                                                                                                                | CACC | Absolute Accuracy            |     | _                | ± 1/2<br>± 1/2 | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |  |

| CV03*                                                                                                                | CR   | Unit Resistor Value (R)      | _   | 2k               | _              | Ω          |                                             |  |

| CV04*                                                                                                                | CST  | Settling Time <sup>(1)</sup> | —   | —                | 10             | μs         |                                             |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Settling time measured while VRR = 1 and VR<3:0> transitions from '0000' to '1111'.

2: See Section 7.11 "Comparator Voltage Reference" for more information.

#### TABLE 15-8: PIC12F635/PIC16F636 PLVD CHARACTERISTICS:

| DC CHARACTERISTICS  |                    |                 | Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ Operating VoltageVDD Range 2.0V-5.5V |          |       |       |                          |  |

|---------------------|--------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|-------|--------------------------|--|

| Sym. Characteristic |                    |                 | Min                                                                                                                                                       | Тур†     | Мах   | Units | Conditions               |  |

| Vplvd               | PLVD               | LVDL<2:0> = 001 | 1.900                                                                                                                                                     | 2.0      | 2.125 | V     |                          |  |

|                     | Voltage            | LVDL<2:0> = 010 | 2.000                                                                                                                                                     | 2.1      | 2.225 | V     |                          |  |

|                     |                    | LVDL<2:0> = 011 | 2.100                                                                                                                                                     | 2.2      | 2.325 | V     |                          |  |

|                     |                    | LVDL<2:0> = 100 | 2.200                                                                                                                                                     | 2.3      | 2.425 | V     |                          |  |

|                     |                    | LVDL<2:0> = 101 | 3.825                                                                                                                                                     | 4.0      | 4.200 | V     |                          |  |

|                     |                    | LVDL<2:0> = 110 | 4.025                                                                                                                                                     | 4.2      | 4.400 | V     |                          |  |

|                     |                    | LVDL<2:0> = 111 | 4.325                                                                                                                                                     | 4.5      | 4.700 | V     |                          |  |

| *TPLVDS             | PLVD Settling time |                 | _                                                                                                                                                         | 50<br>25 | _     | μs    | VDD = 5.0V<br>VDD = 3.0V |  |

These parameters are characterized but not tested

Data in 'Typ' column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

†

| AC CHARACTERISTICS |          |                                                                              | Standard Operating Conditions<br>Supply Voltage<br>Operating temperature<br>LC Signal Input<br>Carrier Frequency<br>LCCOM connected to VSS |                      |                      | s (unless otherwise stated)<br>2.0V ≤ VDD ≤ 3.6V<br>-40°C ≤ TAMB ≤ +85°C for industrial<br>Sinusoidal 300 mVPP<br>125 kHz |                                                                                                                                                                                                                                     |  |

|--------------------|----------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Sym.     | Characteristic                                                               | Min                                                                                                                                        | Тур†                 | Мах                  | Units                                                                                                                     | Conditions                                                                                                                                                                                                                          |  |

| AF01               | VSENSE   | LC Input Sensitivity                                                         | 1                                                                                                                                          | 3.0                  | 6                    | тVрр                                                                                                                      | VDD = 3.0V<br>Output enable filter disabled<br>AGCSIG = 0; MODMIN = 00<br>(33% modulation depth setting)<br>Input = Continuous Wave (CW)<br>Output = Logic level transition from low-to-<br>high at sensitivity level for CW input. |  |

| AF02               | Vde_Q    | Coil de-Q'ing Voltage -<br>RF Limiter (RFLM) must be active                  | 3                                                                                                                                          | -                    | 5                    | V                                                                                                                         | VDD = 3.0V, Force IIN = 5 $\mu$ A                                                                                                                                                                                                   |  |

| AF03               | Rflm     | RF Limiter Turn-on Resistance<br>(LCX, LCY, LCZ)                             | -                                                                                                                                          | 300                  | 700                  | Ohm                                                                                                                       | VDD = 2.0V, VIN = 8 VDC                                                                                                                                                                                                             |  |

| AF04               | Sadj     | Sensitivity Reduction                                                        |                                                                                                                                            | 0<br>-30             | _                    | dB<br>dB                                                                                                                  | VDD = 3.0V<br>No sensitivity reduction selected<br>Max reduction selected<br>Monotonic increment in attenuation value from<br>setting = 0000 to 1111 by design                                                                      |  |

| AF05               | VIN_MOD  | Minimum Modulation Depth<br>75% ± 12%<br>50% ± 12%<br>25% ± 12%<br>12% ± 12% | 63<br>38<br>13<br>0                                                                                                                        | 75<br>50<br>25<br>12 | 87<br>62<br>37<br>24 | %<br>%<br>%                                                                                                               | VDD = 3.0V                                                                                                                                                                                                                          |  |

| AF06               | CTUNX    | LCX Tuning Capacitor                                                         | _                                                                                                                                          | 0                    | _                    | pF                                                                                                                        | VDD = 3.0V,<br>Config. Reg. 1, bits <6:1> Setting = 000000                                                                                                                                                                          |  |

|                    |          |                                                                              | 44                                                                                                                                         | 63                   | 82                   | pF                                                                                                                        | 63 pF +/- 30%<br>Config. Reg. 1, bits <6:1> Setting = 111111<br>63 steps, 1 pF/step<br>Monotonic increment in capacitor value from<br>setting = 000000 to 111111 by design                                                          |  |

| AF07               | CTUNY    | LCY Tuning Capacitor                                                         | _                                                                                                                                          | 0                    | _                    | pF                                                                                                                        | VDD = 3.0V,<br>Config. Reg. 2, bits <6:1> Setting = 000000                                                                                                                                                                          |  |

|                    |          |                                                                              | 44                                                                                                                                         | 63                   | 82                   | pF                                                                                                                        | 63 pF +/- 30%<br>Config. Reg. 2, bits <6:1> Setting = 111111<br>63 steps, 1 pF/step<br>Monotonic increment in capacitor value from<br>setting = 000000 to 111111 by design                                                          |  |

| AF08               | CTUNZ    | LCZ Tuning Capacitor                                                         | _                                                                                                                                          | 0                    | _                    | pF                                                                                                                        | VDD = 3.0V,<br>Config. Reg. 3, bits<6:1> Setting = 000000                                                                                                                                                                           |  |

|                    |          |                                                                              | 44                                                                                                                                         | 63                   | 82                   | pF                                                                                                                        | 63 pF +/- 30%<br>Config. Reg. 3, bits<6:1> Setting = 111111<br>63 steps, 1 pF/step<br>Monotonic increment in capacitor value from<br>setting = 000000 to 111111 by design                                                           |  |

| AF09               | FCARRIER | Carrier frequency                                                            | _                                                                                                                                          | 125                  | _                    | kHz                                                                                                                       | Characterized at bench.                                                                                                                                                                                                             |  |

| AF10               | FMOD     | Input modulation frequency                                                   | -                                                                                                                                          | _                    | 10                   | kHz                                                                                                                       | Input data rate, characterized at bench.                                                                                                                                                                                            |  |

| AF11               | C_Q      | Q of Trimming Capacitors                                                     | 50*                                                                                                                                        | —                    | _                    | pF                                                                                                                        | Characterized at bench test                                                                                                                                                                                                         |  |

| AF12               | Tdr      | Demodulator Charge Time<br>(delay time of demodulated output<br>to rise)     | -                                                                                                                                          | 50                   | _                    | μs                                                                                                                        | VDD = 3.0V<br>MOD depth setting = 50%<br>Input conditions:<br>Amplitude = 300 mVPP<br>Modulation depth = 80%                                                                                                                        |  |

| AF13               | Tdf      | Demodulator Discharge Time<br>(delay time of demodulated output<br>to fall)  | _                                                                                                                                          | 50                   | _                    | μs                                                                                                                        | VDD = 3.0V<br>MOD depth setting = 50%<br>Input conditions:<br>Amplitude = 300 mVPP<br>Modulation depth = 80%                                                                                                                        |  |

### 15.11 AC Characteristics: Analog Front-End for PIC16F639 (Industrial)

Parameter is characterized but not tested. Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested. Required output enable filter high time must account for input path analog delays (= **Тоен** - TDR + TDF). Required output enable filter low time must account for input path analog delays (= **ToeL** + TDR - TDF). t

Note 1:

2:

## 17.1 Package Marking Information (Continued)

14-Lead PDIP

14-Lead SOIC

14-Lead TSSOP

16-Lead QFN

## 20-Lead SSOP

Example

Example

Example

Example

#### Example

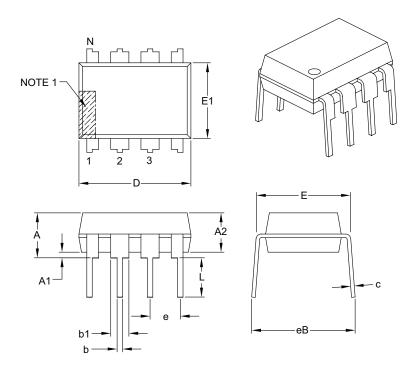

#### 17.2 Package Details

The following sections give the technical details of the packages.

#### 8-Lead Plastic Dual In-Line (P or PA) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | INCHES           |          |      |      |  |

|----------------------------|------------------|----------|------|------|--|

| Dimensi                    | Dimension Limits |          |      | MAX  |  |

| Number of Pins             | Ν                | 8        |      |      |  |

| Pitch                      | е                | .100 BSC |      |      |  |

| Top to Seating Plane       | Α                | -        | -    | .210 |  |

| Molded Package Thickness   | A2               | .115     | .130 | .195 |  |

| Base to Seating Plane      | A1               | .015     | -    | -    |  |

| Shoulder to Shoulder Width | E                | .290     | .310 | .325 |  |

| Molded Package Width       | E1               | .240     | .250 | .280 |  |

| Overall Length             | D                | .348     | .365 | .400 |  |

| Tip to Seating Plane       | L                | .115     | .130 | .150 |  |

| Lead Thickness             | С                | .008     | .010 | .015 |  |

| Upper Lead Width           | b1               | .040     | .060 | .070 |  |

| Lower Lead Width           | b                | .014     | .018 | .022 |  |

| Overall Row Spacing §      | eB               | -        | -    | .430 |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located with the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-018B

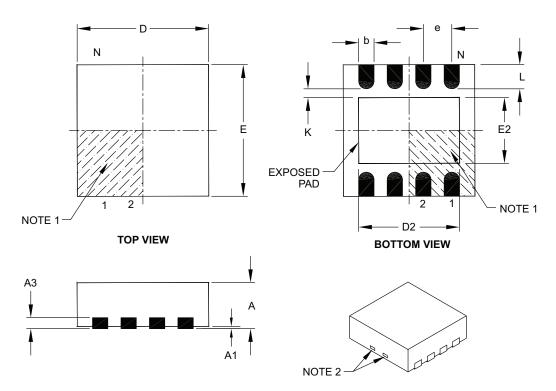

#### 8-Lead Plastic Dual Flat, No Lead Package (MD) – 4x4x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |          |      |      |  |

|------------------------|-------------|----------|------|------|--|

| Dim                    | MIN         | NOM      | MAX  |      |  |

| Number of Pins         | N           |          | 8    |      |  |

| Pitch                  | e           | 0.80 BSC |      |      |  |

| Overall Height         | А           | 0.80     | 0.90 | 1.00 |  |

| Standoff               | A1          | 0.00     | 0.02 | 0.05 |  |

| Contact Thickness      | A3          | 0.20 REF |      |      |  |

| Overall Length         | D           | 4.00 BSC |      |      |  |

| Exposed Pad Width      | E2          | 0.00     | 2.20 | 2.80 |  |

| Overall Width          | E           | 4.00 BSC |      |      |  |

| Exposed Pad Length     | D2          | 0.00     | 3.00 | 3.60 |  |

| Contact Width          | b           | 0.25     | 0.30 | 0.35 |  |

| Contact Length         | L           | 0.30     | 0.55 | 0.65 |  |

| Contact-to-Exposed Pad | K           | 0.20     | _    | -    |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-131C

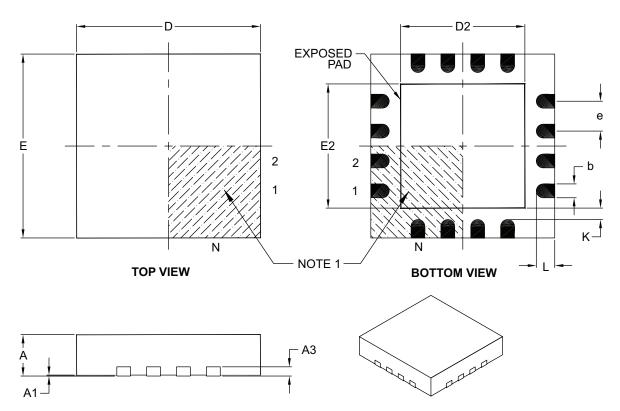

### 16-Lead Plastic Quad Flat, No Lead Package (ML) – 4x4x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units      | MILLIMETERS |      |      |  |

|------------------------|------------|-------------|------|------|--|

| Dimens                 | ion Limits | MIN         | NOM  | MAX  |  |

| Number of Pins         | Ν          |             | 16   |      |  |

| Pitch                  | е          | 0.65 BSC    |      |      |  |

| Overall Height         | А          | 0.80        | 0.90 | 1.00 |  |