# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | ·                                                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, WDT                                    |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                           |

| Supplier Device Package    | 14-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f636-i-sl |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

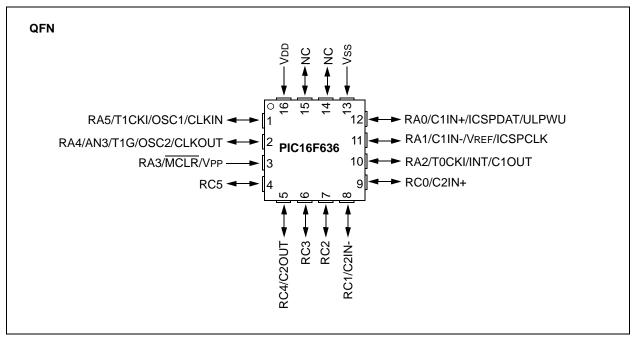

#### **16-Pin Diagram**

#### TABLE 3: 16-PIN SUMMARY

| I/O                | Pin | Comparators | Timer | Interrupts | Pull-ups         | Basic         |

|--------------------|-----|-------------|-------|------------|------------------|---------------|

| RA0                | 12  | C1IN+       |       | IOC        | Y                | ICSPDAT/ULPWU |

| RA1                | 11  | C1IN-       | —     | IOC        | Y                | VREF/ICSPCLK  |

| RA2                | 10  | C1OUT       | TOCKI | INT/IOC    | Y                | —             |

| RA3 <sup>(1)</sup> | 3   | _           | —     | IOC        | Y <sup>(2)</sup> | MCLR/VPP      |

| RA4                | 2   |             | T1G   | IOC        | Y                | OSC2/CLKOUT   |

| RA5                | 1   |             | T1CKI | IOC        | Y                | OSC1/CLKIN    |

| RC0                | 9   | C2IN+       | —     | —          | —                | —             |

| RC1                | 8   | C2IN-       | —     | —          | —                | —             |

| RC2                | 7   |             | —     | —          | —                | —             |

| RC3                | 6   | _           | _     | _          | —                | —             |

| RC4                | 5   | C2OUT       | —     | —          | —                | —             |

| RC5                | 4   | —           | _     | _          | —                | —             |

| _                  | 16  |             | —     | —          | —                | Vdd           |

| _                  | 13  | _           |       | _          |                  | Vss           |

| _                  | 14  | _           | _     | _          | _                | NC            |

|                    | 15  |             |       |            |                  | NC            |

Note 1: Input only.

2: Only when pin is configured for external MCLR.

#### **PIC12F635 PINOUT DESCRIPTIONS TABLE 1-1:**

| Name                    | Function | Input<br>Type | Output<br>Type | Description                                                                                                                                             |

|-------------------------|----------|---------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| GP0/C1IN+/ICSPDAT/ULPWU | GP0      | TTL           |                | General purpose I/O. Individually controlled<br>interrupt-on-change. Individually enabled pull-up/pull-down.<br>Selectable Ultra Low-Power Wake-up pin. |

|                         | C1IN+    | AN            | _              | Comparator 1 input – positive.                                                                                                                          |

|                         | ICSPDAT  | TTL           | CMOS           | Serial programming data I/O.                                                                                                                            |

|                         | ULPWU    | AN            |                | Ultra Low-Power Wake-up input.                                                                                                                          |

| GP1/C1IN-/ICSPCLK       | GP1      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change. Individually enabled pull-up/pull-down.                                               |

|                         | C1IN-    | AN            | _              | Comparator 1 input – negative.                                                                                                                          |

|                         | ICSPCLK  | ST            | _              | Serial programming clock.                                                                                                                               |

| GP2/T0CKI/INT/C1OUT     | GP2      | ST            | CMOS           | General purpose I/O. Individually controlled interrupt-on-change. Individually enabled pull-up/pull-down.                                               |

|                         | T0CKI    | ST            | _              | External clock for Timer0.                                                                                                                              |

|                         | INT      | ST            | _              | External interrupt.                                                                                                                                     |

|                         | C1OUT    | _             | CMOS           | Comparator 1 output.                                                                                                                                    |

| GP3/MCLR/Vpp            | GP3      | TTL           | _              | General purpose input. Individually controlled interrupt-on-change.                                                                                     |

|                         | MCLR     | ST            | _              | Master Clear Reset. Pull-up enabled when configured as MCL                                                                                              |

|                         | Vpp      | HV            |                | Programming voltage.                                                                                                                                    |

| GP4/T1G/OSC2/CLKOUT     | GP4      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change. Individually enabled pull-up/pull-down.                                               |

|                         | T1G      | ST            | _              | Timer1 gate.                                                                                                                                            |

|                         | OSC2     | _             | XTAL           | XTAL connection.                                                                                                                                        |

|                         | CLKOUT   | _             | CMOS           | TOSC/4 reference clock.                                                                                                                                 |

| GP5/T1CKI/OSC1/CLKIN    | GP5      | TTL           | CMOS           | General purpose I/O. Individually controlled interrupt-on-change. Individually enabled pull-up/pull-down.                                               |

|                         | T1CKI    | ST            |                | Timer1 clock.                                                                                                                                           |

|                         | OSC1     | XTAL          |                | XTAL connection.                                                                                                                                        |

|                         | CLKIN    | ST            | _              | Tosc reference clock.                                                                                                                                   |

| Vdd                     | Vdd      | D             |                | Power supply for microcontroller.                                                                                                                       |

|                         | Vss      | D             |                | Ground reference for microcontroller.                                                                                                                   |

HV = High Voltage TTL = TTL compatible input

ST

XTAL = Crystal

### PIC12F635/PIC16F636/639

#### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register which contains the various enable and flag bits for TMR0 register overflow, PORTA change and external RA2/INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER

| Logondi |       |       |       |                       |                     |       |       |

|---------|-------|-------|-------|-----------------------|---------------------|-------|-------|

| bit 7   |       |       |       |                       |                     |       | bit 0 |

| GIE     | PEIE  | TOIE  | INTE  | RAIE <sup>(1,3)</sup> | T0IF <sup>(2)</sup> | INTF  | RAIF  |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0                 | R/W-0               | R/W-0 | R/W-x |

| Legena:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7      | <b>GIE:</b> Global Interrupt Enable bit<br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts                                                                                                                                         |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6      | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts                                                                                                              |

| bit 5      | <b>T0IE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt                                                                                                                            |

| bit 4      | INTE: RA2/INT External Interrupt Enable bit<br>1 = Enables the RA2/INT external interrupt<br>0 = Disables the RA2/INT external interrupt                                                                                                              |

| bit 3      | <b>RAIE:</b> PORTA Change Interrupt Enable bit <sup>(1,3)</sup><br>1 = Enables the PORTA change interrupt<br>0 = Disables the PORTA change interrupt                                                                                                  |

| bit 2      | <b>T0IF:</b> Timer0 Overflow Interrupt Flag bit <sup>(2)</sup><br>1 = TMR0 register has overflowed (must be cleared in software)<br>0 = TMR0 register did not overflow                                                                                |

| bit 1      | INTF: RA2/INT External Interrupt Flag bit<br>1 = The RA2/INT external interrupt occurred (must be cleared in software)<br>0 = The RA2/INT external interrupt did not occur                                                                            |

| bit 0      | <ul> <li>RAIF: PORTA Change Interrupt Flag bit</li> <li>1 = When at least one of the PORTA general purpose I/O pins changed state (must be cleared in software)</li> <li>0 = None of the PORTA general purpose I/O pins have changed state</li> </ul> |

| Note 1: 10 | OCA register must also be enabled.                                                                                                                                                                                                                    |

2: T0IF bit is set when Timer0 rolls over. Timer0 is unchanged on Reset and should be initialized before clearing T0IF bit.

3: Includes ULPWU interrupt.

# 3.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

#### 3.1 Overview

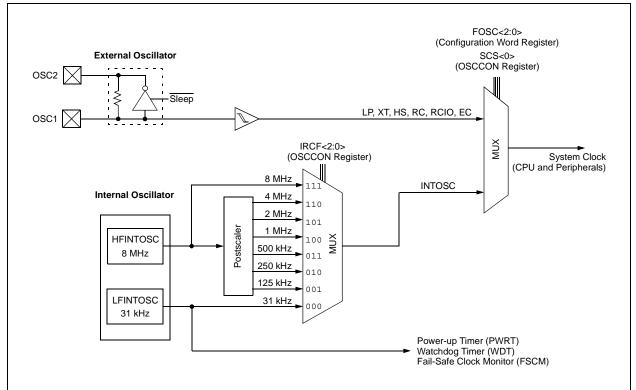

The Oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 3-1 illustrates a block diagram of the Oscillator module.

Clock sources can be configured from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be configured from one of two internal oscillators, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal via software.

- Two-Speed Start-up mode, which minimizes latency between external oscillator start-up and code execution.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, EC or RC modes) and switch automatically to the internal oscillator.

The Oscillator module can be configured in one of eight clock modes.

- 1. EC External clock with I/O on OSC2/CLKOUT.

- 2. LP 32 kHz Low-Power Crystal mode.

- 3. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode.

- 4. HS High Gain Crystal or Ceramic Resonator mode.

- 5. RC External Resistor-Capacitor (RC) with Fosc/4 output on OSC2/CLKOUT.

- 6. RCIO External Resistor-Capacitor (RC) with I/O on OSC2/CLKOUT.

- 7. INTOSC Internal oscillator with Fosc/4 output on OSC2 and I/O on OSC1/CLKIN.

- 8. INTOSCIO Internal oscillator with I/O on OSC1/CLKIN and OSC2/CLKOUT.

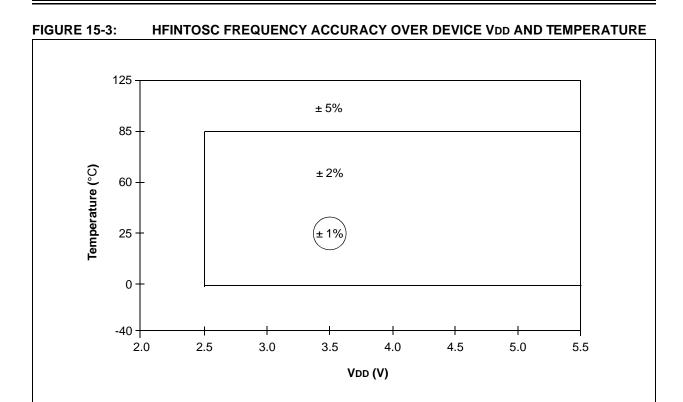

Clock Source modes are configured by the FOSC<2:0> bits in the Configuration Word register (CONFIG). The internal clock can be generated from two internal oscillators. The HFINTOSC is a calibrated high-frequency oscillator. The LFINTOSC is an uncalibrated low-frequency oscillator.

#### FIGURE 3-1: PIC<sup>®</sup> MCU CLOCK SOURCE BLOCK DIAGRAM

#### 3.5.3 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a postscaler and multiplexer (see Figure 3-1). Select 31 kHz, via software, using the IRCF<2:0> bits of the OSCCON register. See **Section 3.5.4** "**Frequency Select Bits (IRCF)**" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<2:0> bits of the OSCCON register = 000) as the system clock source (SCS bit of the OSCCON register = 1), or when any of the following are enabled:

- Two-Speed Start-up IESO bit of the Configuration Word register = 1 and IRCF<2:0> bits of the OSCCON register = 000

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor (FSCM)

The LF Internal Oscillator (LTS) bit of the OSCCON register indicates whether the LFINTOSC is stable or not.

#### 3.5.4 FREQUENCY SELECT BITS (IRCF)

The output of the 8 MHz HFINTOSC and 31 kHz LFINTOSC connects to a postscaler and multiplexer (see Figure 3-1). The Internal Oscillator Frequency Select bits IRCF<2:0> of the OSCCON register select the frequency output of the internal oscillators. One of eight frequencies can be selected via software:

- 8 MHz

- 4 MHz (Default after Reset)

- 2 MHz

- 1 MHz

- 500 kHz

- 250 kHz

- 125 kHz

- 31 kHz (LFINTOSC)

| Note: | Following any Reset, the IRCF<2:0> bits of |  |  |  |

|-------|--------------------------------------------|--|--|--|

|       | the OSCCON register are set to '110' and   |  |  |  |

|       | the frequency selection is set to 4 MHz.   |  |  |  |

|       | The user can modify the IRCF bits to       |  |  |  |

|       | select a different frequency.              |  |  |  |

#### 3.5.5 HF AND LF INTOSC CLOCK SWITCH TIMING

When switching between the LFINTOSC and the HFINTOSC, the new oscillator may already be shut down to save power (see Figure 3-6). If this is the case, there is a delay after the IRCF<2:0> bits of the OSCCON register are modified before the frequency selection takes place. The LTS and HTS bits of the OSCCON register will reflect the current active status of the LFINTOSC and HFINTOSC oscillators. The timing of a frequency selection is as follows:

- 1. IRCF<2:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. CLKOUT is held low and the clock switch circuitry waits for a rising edge in the new clock.

- CLKOUT is now connected with the new clock. LTS and HTS bits of the OSCCON register are updated as required.

- 6. Clock switch is complete.

See Figure 3-1 for more details.

If the internal oscillator speed selected is between 8 MHz and 125 kHz, there is no start-up delay before the new frequency is selected. This is because the old and new frequencies are derived from the HFINTOSC via the postscaler and multiplexer.

Start-up delay specifications are located in the A/C Specifications (Oscillator Module) in **Section 15.0 "Electrical Specifications"**.

#### 4.3 PORTC

PORTC is a general purpose I/O port consisting of 6 bidirectional pins. The pins can be configured for either digital I/O or analog input to comparator. For specific information about individual functions, refer to the appropriate section in this data sheet.

| Note: | The CMCON0 register must be initialized      |  |  |

|-------|----------------------------------------------|--|--|

|       | to configure an analog channel as a digital  |  |  |

|       | input. Pins configured as analog inputs will |  |  |

|       | read '0'.                                    |  |  |

#### EXAMPLE 4-3: INITIALIZING PORTC

| BANKSEL | PORTC  | ;                      |

|---------|--------|------------------------|

| CLRF    | PORTC  | ;Init PORTC            |

| MOVLW   | 07h    | ;Set RC<4,1:0> to      |

| MOVWF   | CMCON0 | ;digital I/O           |

| BANKSEL | TRISC  | ;                      |

| MOVLW   | 0Ch    | ;Set RC<3:2> as inputs |

| MOVWF   | TRISC  | ;and set RC<5:4,1:0>   |

|         |        | ;as outputs            |

#### REGISTER 4-6: PORTC: PORTC REGISTER

| U-0   | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-6 | Unimplemented: Read as '0' |

|---------|----------------------------|

|         |                            |

bit 5-0 RC<5:0>: PORTC General Purpose I/O Pin bits 1 = Port pin is > VIH 0 = Port pin is < VIL

#### REGISTER 4-7: TRISC: PORTC TRI-STATE REGISTER

| U-0   | U-0 | R/W-1  | R/W-1  | R-1    | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0

TRISC<5:0>: PORTC Tri-State Control bits

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

#### 6.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- Timer1 interrupt enable bit of the PIE1 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TTMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

#### 6.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- PEIE bit of the INTCON register must be set

The device will wake-up on an overflow and execute the next instruction. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine (0004h).

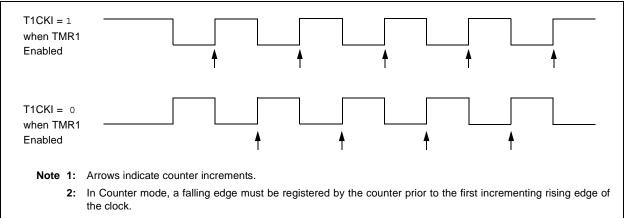

#### FIGURE 6-2: TIMER1 INCREMENTING EDGE

#### 6.9 Comparator Synchronization

The same clock used to increment Timer1 can also be used to synchronize the comparator output. This feature is enabled in the Comparator module.

When using the comparator for Timer1 gate, the comparator output should be synchronized to Timer1. This ensures Timer1 does not miss an increment if the comparator changes.

For more information, see **Section 7.0 "Comparator Module"**.

#### 7.9 Comparator Gating Timer1

This feature can be used to time the duration or interval of analog events. Clearing the T1GSS bit of the CMCON1 register will enable Timer1 to increment based on the output of the comparator (or Comparator C2 for PIC16F636/639). This requires that Timer1 is on and gating is enabled. See **Section 6.0 "Timer1 Module with Gate Control"** for details.

It is recommended to synchronize the comparator with Timer1 by setting the CxSYNC bit when the comparator is used as the Timer1 gate source. This ensures Timer1 does not miss an increment if the comparator changes during an increment.

| Note: | Reference | ces  | to    | the    | compa  | arator | in   | this |

|-------|-----------|------|-------|--------|--------|--------|------|------|

|       | section   | sp   | ecifi | ically | are    | refer  | ring | to   |

|       | Compara   | ator | C2    | on th  | e PIC1 | 6F636  | 6/63 | 9.   |

### 7.10 Synchronizing Comparator Output to Timer1

The comparator (or Comparator C2 for PIC16F636/639) output can be synchronized with Timer1 by setting the CxSYNC bit of the CMCON1 register. When enabled, the comparator output is latched on the falling edge of the Timer1 clock source. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figure 7-2) and the Timer1 Block Diagram (Figure 6-1) for more information.

| Note: | Reference | ces  | to    | the   | compa  | arator | in   | this |

|-------|-----------|------|-------|-------|--------|--------|------|------|

|       | section   | spe  | ecifi | cally | are    | referi | ring | to   |

|       | Compara   | ator | C2    | on th | e PIC1 | 6F636  | 6/63 | 9.   |

### 10.0 KEELOQ<sup>®</sup> COMPATIBLE CRYPTOGRAPHIC MODULE

To obtain information regarding the implementation of the KEELOQ module, Microchip Technology requires the execution of the "KEELOQ<sup>®</sup> Encoder License Agreement".

The "KEELOQ<sup>®</sup> Encoder License Agreement" may be accessed through the Microchip web site located at <u>www.microchip.com/KEELOQ</u>. Further information may be obtained by contacting your local Microchip Sales Representative.

#### 11.14.2 INACTIVITY TIMER

The Inactivity Timer is used to automatically return the AFE to Standby mode, if there is no input signal. The time-out period is approximately 16 ms (TINACT), based on the 32 kHz internal clock.

The purpose of the Inactivity Timer is to minimize AFE current draw by automatically returning the AFE to the lower current Standby mode, if there is no input signal for approximately 16 ms.

The timer is reset when:

- An amplitude change in LF input signal, either high-to-low or low-to-high

- CS pin is low (any SPI command)

- Timer-related Soft Reset

The timer starts when:

• AFE receives any LF signal

The timer causes an AFE Soft Reset when:

• A previously received LF signal does not change either high-to-low or low-to-high for TINACT

The Soft Reset returns the AFE to Standby mode where most of the analog circuits, such as the AGC, demodulator and RC oscillator, are powered down. This returns the AFE to the lower Standby Current mode.

#### 11.14.3 ALARM TIMER

The Alarm Timer is used to notify the MCU that the AFE is receiving LF signal that does not pass the output enable filter requirement. The time-out period is approximately 32 ms (TALARM) in the presence of continuing noise.

The Alarm Timer time-out occurs if there is an input signal for longer than 32 ms that does not meet the output enable filter requirements. The Alarm Timer time-out causes:

- a) The ALERT pin to go low.

- b) The ALARM bit to set in the AFE Status Configuration 7 register (Register 11-8).

The MCU is informed of the Alarm timer time-out by monitoring the ALERT pin. If the Alarm timer time-out occurs, the MCU can take appropriate actions such as lowering channel sensitivity or disabling channels. If the noise source is ignored, the AFE can return to a lower standby current draw state. The timer is reset when the:

- CS pin is low (any SPI command).

- Output enable filter is disabled.

- LFDATA pin is enabled (signal passed output enable filter).

The timer starts when:

Receiving a LF signal.

The timer causes a low output on the ALERT pin when:

• Output enable filter is enabled and modulated input signal is present for TALARM, but does not pass the output enable filter requirement.

**Note:** The Alarm timer is disabled if the output enable filter is disabled.

#### 11.14.4 PULSE WIDTH TIMER

The Pulse Width Timer is used to verify that the received output enable sequence meets both the minimum TOEH and minimum TOEL requirements.

#### 11.14.5 PERIOD TIMER

The Period Timer is used to verify that the received output enable sequence meets the maximum TOET requirement.

#### 11.14.6 AGC SETTLING TIMER (TAGC)

This timer is used to keep the output enable filter in Reset while the AGC settles on the input signal. The time-out period is approximately 3.5 ms. At end of this time (TAGC), the input should remain high (TPAGC), otherwise the counting is aborted and a Soft Reset is issued. See Figure 11-6 for details.

- Note 1: The AFE needs continuous and uninterrupted high input signal during AGC settling time (TAGC). Any absence of signal during this time may reset the timer and a new input signal is needed for AGC settling time, or may result in improper AGC gain settings which will produce invalid output.

- 2: The rest of the AFE section wakes up if any of these input channels receive the AGC settling time correctly. AFE Status Register 7 bits <4:2> (Register 11-8) indicate which input channels have waken up the AFE first. Valid input signal on multiple input pins can cause more than one channel's indicator bit to be set.

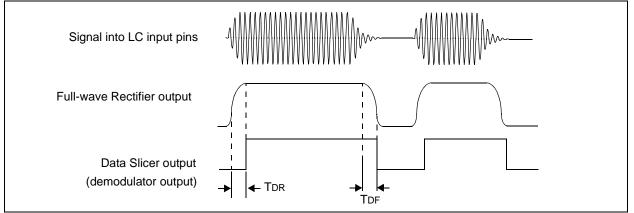

#### 11.29 Demodulator

The demodulator recovers the modulation data from the received signal, containing carrier plus data, by appropriate envelope detection. The demodulator has a fast rise (charge) time (TDR) and a fall time (TDF) appropriate to an envelope of input signal (see **Section 15.0 "Electrical Specifications"** for TDR and TDF specifications). The demodulator contains the full-wave rectifier, low-pass filter, peak detector and data slicer.

#### FIGURE 11-9: DEMODULATOR CHARGE AND DISCHARGE

#### 11.30 Power-On Reset

This circuit remains in a Reset state until a sufficient supply voltage is applied to the AFE. The Reset releases when the supply is sufficient for correct AFE operation, nominally VPOR of AFE.

The Configuration registers are all cleared on a Power-on Reset. As the Configuration registers are protected by odd row and column parity, the ALERT pin will be pulled down – indicating to the microcontroller section that the AFE configuration memory is cleared and requires loading.

#### 11.31 LFDATA Output Selection

The LFDATA output can be configured to pass the Demodulator output, Received Signal Strength Indicator (RSSI) output, or Carrier Clock. See Configuration Register 1 (Register 11-2) for more details.

#### 11.31.1 DEMODULATOR OUTPUT

The demodulator output is the default configuration of the output selection. This is the output of an envelope detection circuit. See Figure 11-9 for the demodulator output. For a clean data output or to save operating power, the input channels can be individually enabled or disabled. If more than one channel is enabled, the output is the sum of each output of all enabled channels. There will be no valid output if all three channels are disabled. When the demodulated output is selected, the output is available in two different conditions depending on how the options of Configuration Register 0 (Register 11-1) are set: Output Enable Filter is disabled or enabled.

#### **Related Configuration register bits:**

- Configuration Register 1 (Register 11-2), DATOUT <8:7>:

- <u>bit 8</u> <u>bit 7</u>

- 0 0: Demodulator Output

- 0 1: Carrier Clock Output

- 1 0: RSSI Output

- 0 1: RSSI Output

- Configuration Register 0 (Register 11-1): all bits

## PIC12F635/PIC16F636/639

| ADDLW            | Add literal and W                                                                                                          |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                          |  |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                          |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                   |  |  |  |  |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the<br>W register. |  |  |  |  |

Instruction Descriptions

13.2

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ADDWF            | Add W and f                                                                                                                                                                        |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                                  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                    |  |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                           |  |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |  |  |  |  |  |  |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND literal with W                                                                                                     |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                      |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |  |  |  |  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                             |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the<br>next instruction is discarded, and<br>a NOP is executed instead, making<br>this a two-cycle instruction. |

| ANDWF            | AND W with f                                                                                                                                                    |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                               |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |  |  |

| DC CHARACTERISTICS |       |                                                                         | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |          |          |                                                                |  |

|--------------------|-------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|----------|----------|----------------------------------------------------------------|--|

| Param<br>No.       | Sym   | Characteristic                                                          | Min                                                                                                                                | Тур† | Max      | Units    | Conditions                                                     |  |

| D001               | Vdd   | Supply Voltage                                                          | 2.0                                                                                                                                | —    | 3.6      | V        | Fosc ≤ 10 MHz                                                  |  |

| D001A              | Vddt  | Supply Voltage (AFE)                                                    | 2.0                                                                                                                                | _    | 3.6      | V        | Analog Front-End VDD voltage. Treated as VDD in this document. |  |

| D002               | Vdr   | RAM Data Retention<br>Voltage <sup>(1)</sup>                            | 1.5*                                                                                                                               | _    | _        | V        | Device in Sleep mode                                           |  |

| D003               | VPOR  | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal        | —                                                                                                                                  | Vss  | _        | V        | See <b>Section 12.3</b> " <b>Power-on Reset</b> " for details. |  |

| D003A              | VPORT | VDD Start Voltage (AFE)<br>to ensure internal Power-<br>on Reset signal |                                                                                                                                    | _    | 1.8      | V        | Analog Front-End POR voltage.                                  |  |

| D004               | Svdd  | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal            | 0.05*                                                                                                                              | —    |          | V/ms     | See <b>Section 12.3</b> " <b>Power-on Reset</b> " for details. |  |

| D005               | VBOD  | Brown-out Reset                                                         | 2.0                                                                                                                                | 2.1  | 2.2      | V        |                                                                |  |

| D006               | Rм    | Turn-on Resistance or<br>Modulation Transistor                          | _                                                                                                                                  | 50   | 100      | Ohm      | VDD = 3.0V                                                     |  |

| D007               | Rpu   | Digital Input Pull-Up<br>Resistor<br>CS, SCLK                           | 50                                                                                                                                 | 200  | 350      | kOhm     | VDD = 3.6V                                                     |  |

| D008               | Iail  | Analog Input Leakage<br>Current<br>LCX, LCY, LCZ<br>LCCOM               | _                                                                                                                                  | _    | ±1<br>±1 | μΑ<br>μΑ | VDD = 3.6V, VSS $\leq$ VIN $\leq$ VDD, tested at Sleep mode    |  |

#### DC Characteristics: PIC16F639-I (Industrial) 15.5

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance † only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

### PIC12F635/PIC16F636/639

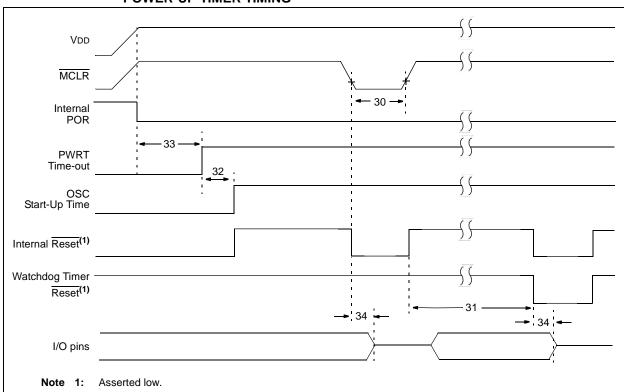

### FIGURE 15-7: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

#### TABLE 15-6: COMPARATOR SPECIFICATIONS

| Standard O | neratina | Conditions | (unlass | otherwise stated | ۱ |

|------------|----------|------------|---------|------------------|---|

| Stanuaru U | perating | Conditions | (uniess | otherwise stated | ) |

| Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |         |                                           |         |     |       |           |       |               |

|---------------------------------------------------------------|---------|-------------------------------------------|---------|-----|-------|-----------|-------|---------------|

| Param<br>No.                                                  | Sym     | Characteristics                           |         | Min | Тур†  | Max       | Units | Comments      |

| CM01                                                          | Vos     | Input Offset Voltage                      |         | —   | ± 5.0 | ± 10      | mV    | (Vdd - 1.5)/2 |

| CM02                                                          | Vсм     | Input Common Mode Voltage                 |         | 0   | _     | Vdd - 1.5 | V     |               |

| CM03*                                                         | CMRR    | Common Mode Rejection Ratio               |         | +55 | _     | _         | dB    |               |

| CM04*                                                         | Trt     | Response Time                             | Falling | _   | 150   | 600       | ns    | (NOTE 1)      |

|                                                               |         |                                           | Rising  | _   | 200   | 1000      | ns    |               |

| CM05*                                                         | Тмc2coV | Comparator Mode Change to<br>Output Valid |         | _   |       | 10        | μs    |               |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Response time is measured with one comparator input at (VDD - 1.5)/2 - 100 mV to (VDD - 1.5)/2 + 20 mV.

#### TABLE 15-7: COMPARATOR VOLTAGE REFERENCE (CVREF) SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                              |     |                  |                |            |                                             |

|----------------------------------------------------------------------------------------------------------------------|------|------------------------------|-----|------------------|----------------|------------|---------------------------------------------|

| Param<br>No.                                                                                                         | Sym  | Characteristics              | Min | Тур†             | Max            | Units      | Comments                                    |

| CV01*                                                                                                                | CLSB | Step Size <sup>(2)</sup>     | _   | VDD/24<br>VDD/32 |                | V<br>V     | Low Range (VRR = 1)<br>High Range (VRR = 0) |

| CV02*                                                                                                                | CACC | Absolute Accuracy            |     | _                | ± 1/2<br>± 1/2 | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |

| CV03*                                                                                                                | CR   | Unit Resistor Value (R)      | _   | 2k               | _              | Ω          |                                             |

| CV04*                                                                                                                | CST  | Settling Time <sup>(1)</sup> | —   | —                | 10             | μs         |                                             |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Settling time measured while VRR = 1 and VR<3:0> transitions from '0000' to '1111'.

2: See Section 7.11 "Comparator Voltage Reference" for more information.

#### TABLE 15-8: PIC12F635/PIC16F636 PLVD CHARACTERISTICS:

| DC CHARACTERISTICS |                 |                 | Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ Operating VoltageVDD Range 2.0V-5.5V |          |       |       |                          |

|--------------------|-----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|-------|--------------------------|

| Sym.               | Cł              | naracteristic   | Min                                                                                                                                                       | Тур†     | Мах   | Units | Conditions               |

| Vplvd              | PLVD            | LVDL<2:0> = 001 | 1.900                                                                                                                                                     | 2.0      | 2.125 | V     |                          |

| Voltage            | LVDL<2:0> = 010 | 2.000           | 2.1                                                                                                                                                       | 2.225    | V     |       |                          |

|                    |                 | LVDL<2:0> = 011 | 2.100                                                                                                                                                     | 2.2      | 2.325 | V     |                          |

|                    |                 | LVDL<2:0> = 100 | 2.200                                                                                                                                                     | 2.3      | 2.425 | V     |                          |

|                    |                 | LVDL<2:0> = 101 | 3.825                                                                                                                                                     | 4.0      | 4.200 | V     |                          |

|                    |                 | LVDL<2:0> = 110 | 4.025                                                                                                                                                     | 4.2      | 4.400 | V     |                          |

|                    |                 | LVDL<2:0> = 111 | 4.325                                                                                                                                                     | 4.5      | 4.700 | V     |                          |

| *TPLVDS            | PLVD Settling   | ı time          | _                                                                                                                                                         | 50<br>25 | _     | μs    | VDD = 5.0V<br>VDD = 3.0V |

These parameters are characterized but not tested

Data in 'Typ' column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

†

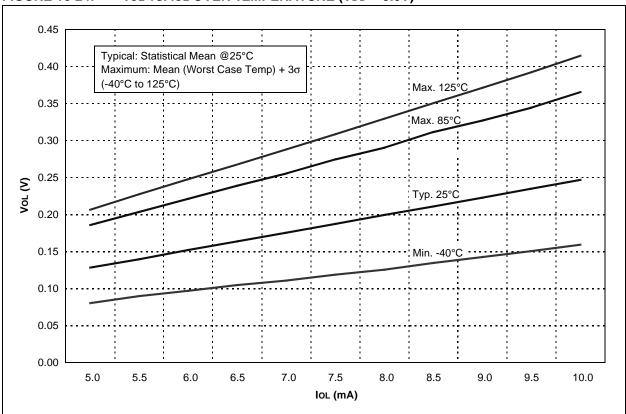

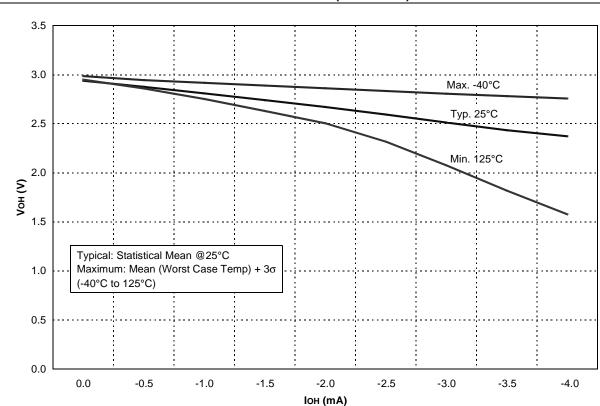

FIGURE 16-25: VOH vs. IOH OVER TEMPERATURE (VDD = 3.0V)

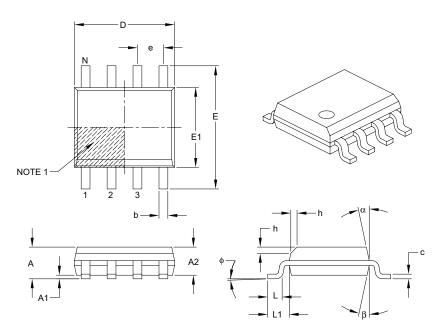

#### 8-Lead Plastic Small Outline (SN or OA) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |     |      |  |

|--------------------------|------------------|-------------|-----|------|--|

|                          | Dimension Limits | MIN         | NOM | MAX  |  |

| Number of Pins           | N                |             | 8   |      |  |

| Pitch                    | е                | 1.27 BSC    |     |      |  |

| Overall Height           | А                | -           | -   | 1.75 |  |

| Molded Package Thickness | A2               | 1.25        | -   | -    |  |

| Standoff §               | A1               | 0.10        | -   | 0.25 |  |

| Overall Width            | E                | 6.00 BSC    |     |      |  |

| Molded Package Width     | E1               | 3.90 BSC    |     |      |  |

| Overall Length           | D                | 4.90 BSC    |     |      |  |

| Chamfer (optional)       | h                | 0.25        | -   | 0.50 |  |

| Foot Length              | L                | 0.40        | -   | 1.27 |  |

| Footprint                | L1               | 1.04 REF    |     |      |  |

| Foot Angle               | φ                | 0°          | -   | 8°   |  |

| Lead Thickness           | С                | 0.17        | -   | 0.25 |  |

| Lead Width               | b                | 0.31        | _   | 0.51 |  |

| Mold Draft Angle Top     | α                | 5°          | -   | 15°  |  |

| Mold Draft Angle Bottom  | β                | 5°          | _   | 15°  |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-057B

#### APPENDIX A: DATA SHEET REVISION HISTORY

#### **Revision A**

This is a new data sheet.

#### **Revision B**

Added PIC16F639 to the data sheet.

#### **Revision C (12/2006)**

Added Characterization data; Updated Package Drawings; Added Comparator Voltage Reference section.

#### Revision D (03/2007)

Replaced Package Drawings (Rev. AM); Replaced Development Support Section. Updated Product ID System.

### INDEX

| Α                                                |

|--------------------------------------------------|

| Absolute Maximum Ratings                         |

| AC Characteristics                               |

| Analog Front-End (AFE) for PIC16F639187          |

| Industrial and Extended 179                      |

| Load Conditions178                               |

| AGC Settling                                     |

| Analog Front-End                                 |

| Configuration Registers                          |

| Summary Table                                    |

| Analog Front-End (AFE)                           |

| AFE Status Register Bit Condition                |

| AGC                                              |

| AGC Preserve                                     |

| Battery Back-up and Batteryless Operation        |

| Block Diagrams                                   |

| Bidirectional PKE System Application Example 102 |

| Functional100                                    |

| LC Input Path 101                                |

| Output Enable Filter Timing103                   |

| Output Enable Filter Timing (Detailed)104        |

| Carrier Clock Detector                           |

| Carrier Clock Output                             |

| Examples                                         |

| Command Decoder/Controller                       |

| Data Slicer                                      |

| Demodulator                                      |

| De-Q'ing of Antenna Circuit                      |

| Error Detection                                  |

| Factory Calibration                              |

| Fixed Gain Amplifiers                            |

| Input Sensitivity Control                        |

| LF Field Powering/Battery Back-up                |

| Examples 110                                     |

| LFDATA Output Selection111                       |

| Case I 112                                       |

| Case II                                          |

| Low Current Modes                                |

| Operating                                        |

| Sleep                                            |

| Modulation Circuit                               |

| Modulation Circuit                               |

| Examples                                         |

| Output Enable Filter                             |

| Configurable Smart                               |

| Output Enable Filter Timing (Table)              |

| Power-on Reset                                   |

| RF Limiter97                                     |

| RSSI                                             |

| Output Path Diagram116                           |

| Power-up Sequence Diagram118                     |

| SPI Read Sequence Diagram                        |

| SPI Write Sequence Diagram                       |

| RSSI Output Current vs. Input Signal Level       |

| Example                                          |

| Soft Reset                                       |

| Soft Reset                                       |

| Timers                                           |

| Alarm                                            |

|                                                  |

| Auto Channel Selection                 | 98  |

|----------------------------------------|-----|

| Inactivity                             | 99  |

| Period                                 | 99  |

| Preamble Counters                      | 99  |

| Pulse Width                            | 99  |

| RC Oscillator                          |     |

| Tuning Capacitor                       | 97  |

| Variable Attenuator                    | 97  |

| Analog Input Connection Considerations | 73  |

| Assembler                              |     |

| MPASM Assembler                        | 160 |

#### В

| Block Diagrams                           |

|------------------------------------------|

| Analog Input Model73                     |

| Clock Source                             |

| Comparator71                             |

| Comparator C1                            |

| Comparator C2                            |

| Comparator Modes                         |

| Crystal Operation                        |

| External RC Mode                         |

| Fail-Safe Clock Monitor (FSCM)           |

| Functional (AFE)                         |

| In-Circuit Serial Programming Connection |

| Interrupt Logic140                       |

| On-Chip Reset Circuit                    |

| PIC12F635 Device                         |

| PIC16F636 Device 10                      |

| PIC16F639 Device 11                      |

| RA0 Pin 52                               |

| RA1 Pin 53                               |

| RA2 Pin 53                               |

| RA3 Pin 54                               |

| RA4 Pin 55                               |

| RA5 Pin 55                               |

| RC0 and RC1 Pins 58                      |

| RC2, RC3 and RC5 Pins 58                 |

| RC4 Pin 59                               |

| Recommended MCLR Circuit                 |

| Resonator Operation                      |

| Timer1 65                                |

| TMR0/WDT Prescaler 61                    |

| Watchdog Timer (WDT) 143                 |

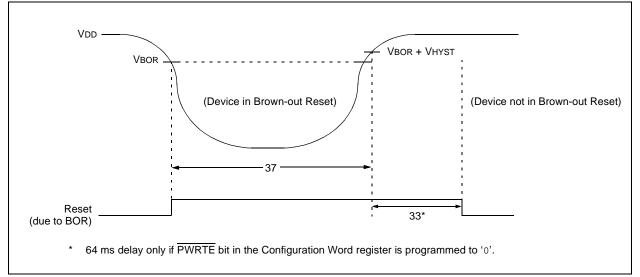

| Brown-out Reset (BOR) 134                |

| Associated 135                           |

| Specifications 183                       |

| Timing and Characteristics               |

### С

| C Compilers         |     |

|---------------------|-----|

| MPLAB C18           | 160 |

| MPLAB C30           | 160 |

| Clock Sources       |     |

| External Modes      | 37  |

| EC                  | 37  |

| HS                  | 38  |

| LP                  | 38  |

| OST                 | 37  |

| RC                  | 39  |

| XT                  | 38  |

| Internal Modes      | 39  |

| Frequency Selection | 41  |

| HFINTOSC            |     |

|                     |     |