Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, WDT                                    |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

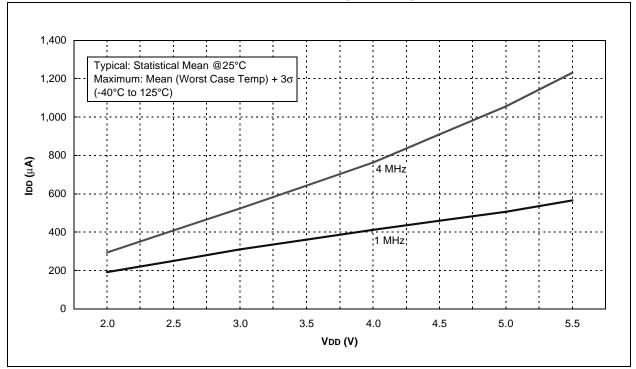

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                          |

| Supplier Device Package    | 14-TSSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f636-i-st |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.0 MEMORY ORGANIZATION

#### 2.1 Program Memory Organization

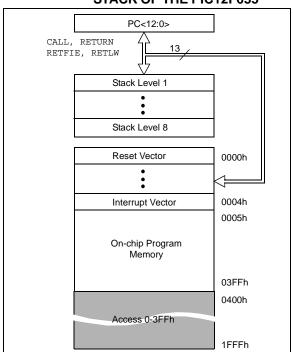

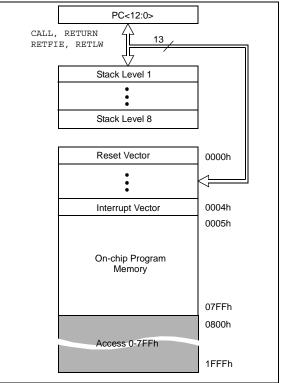

The PIC12F635/PIC16F636/639 devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first  $1K \times 14$  (0000h-03FFh, for the PIC12F635) and  $2K \times 14$  (0000h-07FFh, for the PIC16F636/639) is physically implemented. Accessing a location above these boundaries will cause a wraparound within the first  $2K \times 14$  space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 2-1).

#### 2.2 Data Memory Organization

The data memory (see Figure 2-2) is partitioned into two banks, which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). The Special Function Registers are located in the first 32 locations of each bank. Register locations 20h-7Fh in Bank 0 and A0h-BFh in Bank 1 are GPRs, implemented as static RAM for the PIC16F636/639. For the PIC12F635, register locations 40h through 7Fh are GPRs implemented as static RAM. Register locations F0h-FFh in Bank 1 point to addresses 70h-7Fh in Bank 0. All other RAM is unimplemented and returns '0' when read. RP0 of the STATUS register is the bank select bit.

| <u>RP1</u> | <u>RP0</u> |

|------------|------------|

|------------|------------|

| 0 | 0 | $\rightarrow$ | Bank 0 is selected |

|---|---|---------------|--------------------|

| 0 | 1 | $\rightarrow$ | Bank 1 is selected |

| 1 | 0 | $\rightarrow$ | Bank 2 is selected |

| 1 | 1 | $\rightarrow$ | Bank 3 is selected |

#### FIGURE 2-1: PROGRAM MEMORY MAP AND STACK OF THE PIC12F635

#### FIGURE 2-2: PROGRAM MEMORY MAP AND STACK OF THE PIC16F636/639

| Addr   | Name   | Bit 7         | Bit 6                                                                                             | Bit 5         | Bit 4          | Bit 3          | Bit 2         | Bit 1     | Bit 0               | Value on<br>POR/BOR/<br>WUR | Page    |

|--------|--------|---------------|---------------------------------------------------------------------------------------------------|---------------|----------------|----------------|---------------|-----------|---------------------|-----------------------------|---------|

| Bank ( | )      |               |                                                                                                   |               |                |                |               |           |                     |                             |         |

| 00h    | INDF   |               | Addressing this location uses contents of FSR to address data memory<br>(not a physical register) |               |                |                |               |           |                     |                             | 32,137  |

| 01h    | TMR0   | Timer0 Mod    | dule Registe                                                                                      | r             |                |                |               |           |                     | xxxx xxxx                   | 61,137  |

| 02h    | PCL    | Program C     | ounter's (PC                                                                                      | c) Least Sigr | nificant Byte  |                |               |           |                     | 0000 0000                   | 32,137  |

| 03h    | STATUS | IRP           | RP1                                                                                               | RP0           | TO             | PD             | Z             | DC        | С                   | 0001 1xxx                   | 26,137  |

| 04h    | FSR    | Indirect Da   | ta Memory A                                                                                       | Address Poir  | nter           | •              | •             | •         |                     | xxxx xxxx                   | 32,137  |

| 05h    | GPIO   | _             | _                                                                                                 | GP5           | GP4            | GP3            | GP2           | GP1       | GP0                 | xx xx00                     | 47,137  |

| 06h    | _      | Unimpleme     | ented                                                                                             |               |                |                | •             | •         |                     | —                           | _       |

| 07h    | _      | Unimpleme     | ented                                                                                             |               |                |                |               |           |                     | _                           | _       |

| 08h    | _      | Unimpleme     | ented                                                                                             |               |                |                |               |           |                     | _                           | _       |

| 09h    | _      | Unimpleme     | ented                                                                                             |               |                |                |               |           |                     | _                           | _       |

| 0Ah    | PCLATH | _             | _                                                                                                 | _             | Write Buffer   | for upper 5 b  | its of Progra | m Counter |                     | 0 0000                      | 32,137  |

| 0Bh    | INTCON | GIE           | PEIE                                                                                              | TOIE          | INTE           | RAIE           | T0IF          | INTF      | RAIF <sup>(2)</sup> | 0000 000x                   | 28,137  |

| 0Ch    | PIR1   | EEIF          | LVDIF                                                                                             | CRIF          | —              | C1IF           | OSFIF         | —         | TMR1IF              | 000- 00-0                   | 30,137  |

| 0Dh    |        | Unimpleme     | ented                                                                                             |               |                | 1              |               |           |                     |                             |         |

| 0Eh    | TMR1L  | Holding Re    | gister for the                                                                                    | e Least Sign  | ificant Byte o | f the 16-bit T | MR1           |           |                     | xxxx xxxx                   | 64,137  |

| 0Fh    | TMR1H  | Holding Re    | gister for the                                                                                    | e Most Signi  | ficant Byte of | the 16-bit TM  | /IR1          |           |                     | xxxx xxxx                   | 64,137  |

| 10h    | T1CON  | T1GINV        | TMR1GE                                                                                            | T1CKPS1       | T1CKPS0        | T1OSCEN        | T1SYNC        | TMR1CS    | TMR10N              | 0000 0000                   | 68,137  |

| 11h    | _      | Unimpleme     | ented                                                                                             |               | 1              |                |               |           |                     | _                           | _       |

| 12h    | _      | Unimpleme     | ented                                                                                             |               |                |                |               |           |                     | _                           | _       |

| 13h    | _      | Unimpleme     | ented                                                                                             |               |                |                |               |           |                     | _                           | _       |

| 14h    | _      | Unimpleme     | ented                                                                                             |               |                |                |               |           |                     | _                           | _       |

| 15h    | _      | Unimpleme     | ented                                                                                             |               |                |                |               |           |                     | _                           | _       |

| 16h    | _      | Unimplemented |                                                                                                   |               |                |                |               |           |                     | _                           | _       |

| 17h    | _      | Unimpleme     | ented                                                                                             |               |                |                |               |           |                     | _                           | _       |

| 18h    | WDTCON | _             | _                                                                                                 | _             | WDTPS3         | WDTPS2         | WDTPS1        | WDTPS0    | SWDTEN              | 0 1000                      | 144,137 |

| 19h    | CMCON0 | _             | COUT                                                                                              | -             | CINV           | CIS            | CM2           | CM1       | CM0                 | -0-0 0000                   | 79,137  |

| 1Ah    | CMCON1 | _             | _                                                                                                 | -             | _              | _              | _             | T1GSS     | CMSYNC              | 10                          | 82,137  |

| 1Bh    | _      | Unimpleme     | ented                                                                                             |               |                |                |               |           |                     | _                           | _       |

| 1Ch    | _      | Unimpleme     | ented                                                                                             |               |                |                |               |           |                     | _                           | _       |

| 1Dh    |        | Unimpleme     | ented                                                                                             |               |                |                |               |           |                     | _                           | _       |

| 1Eh    | _      | Unimpleme     | ented                                                                                             |               |                |                |               |           |                     | _                           | _       |

| 1Fh    | _      | Unimpleme     | ented                                                                                             |               |                |                |               |           |                     | _                           | _       |

Legend: Note

1:

– = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

<u>Other (non Power-up)</u> Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

MCLR and WDT Reset do not affect the previous value data latch. The RAIF bit will be cleared upon Reset but will set again if the mismatch or units. 2: match exists.

| Addr   | Name   | Bit 7         | Bit 6                        | Bit 5       | Bit 4         | Bit 3         | Bit 2         | Bit 1      | Bit 0               | Value on<br>POR/BOR/<br>WUR | Page    |

|--------|--------|---------------|------------------------------|-------------|---------------|---------------|---------------|------------|---------------------|-----------------------------|---------|

| Bank ( | C      |               |                              |             |               |               |               |            |                     |                             |         |

| 00h    | INDF   |               | ng this loca<br>ysical regis |             | ontents of F  | SR to addr    | ess data m    | emory      |                     | XXXX XXXX                   | 32,137  |

| 01h    | TMR0   | Timer0 M      | odule Reg                    | ster        |               |               |               |            |                     | xxxx xxxx                   | 61,137  |

| 02h    | PCL    | Program       | Counter's                    | PC) Least   | Significant   | Byte          |               |            |                     | 0000 0000                   | 32,137  |

| 03h    | STATUS | IRP           | RP1                          | RP0         | TO            | PD            | Z             | DC         | С                   | 0001 1xxx                   | 26,137  |

| 04h    | FSR    | Indirect D    | ata Memo                     | y Address   | Pointer       | •             |               |            |                     | xxxx xxxx                   | 32,137  |

| 05h    | PORTA  | _             | —                            | RA5         | RA4           | RA3           | RA2           | RA1        | RA0                 | xx xx00                     | 48,137  |

| 06h    | _      | Unimplen      | nented                       |             |               |               |               |            |                     |                             |         |

| 07h    | PORTC  | _             | —                            | RC5         | RC4           | RC3           | RC2           | RC1        | RC0                 | xx xx00                     | 57,137  |

| 08h    | _      | Unimplen      | nented                       |             |               |               |               |            |                     |                             | _       |

| 09h    | _      | Unimplen      | nented                       |             |               |               |               |            |                     | —                           | _       |

| 0Ah    | PCLATH | _             |                              |             | Write Buffe   | er for upper  | 5 bits of Pro | ogram Coui | nter                | 0 0000                      | 32,137  |

| 0Bh    | INTCON | GIE           | PEIE                         | T0IE        | INTE          | RAIE          | T0IF          | INTF       | RAIF <sup>(2)</sup> | 0000 000x                   | 28,137  |

| 0Ch    | PIR1   | EEIF          | LVDIF                        | CRIF        | C2IF          | C1IF          | OSFIF         | _          | TMR1IF              | 0000 00-0                   | 30,137  |

| 0Dh    | —      | Unimplen      | nented                       |             |               |               |               |            |                     | _                           | _       |

| 0Eh    | TMR1L  | Holding F     | Register for                 | the Least S | Significant E | Byte of the 1 | 6-bit TMR1    |            |                     | xxxx xxxx                   | 64,137  |

| 0Fh    | TMR1H  | Holding F     | Register for                 | the Most S  | Significant B | yte of the 1  | 6-bit TMR1    |            |                     | xxxx xxxx                   | 64,137  |

| 10h    | T1CON  | T1GINV        | TMR1GE                       | T1CKPS1     | T1CKPS0       | T1OSCEN       | T1SYNC        | TMR1CS     | TMR1ON              | 0000 0000                   | 68,137  |

| 11h    | _      | Unimplen      | nented                       |             |               |               |               |            |                     | _                           | _       |

| 12h    | _      | Unimplen      | nented                       |             |               |               |               |            |                     | —                           | _       |

| 13h    | _      | Unimplen      | nented                       |             |               |               |               |            |                     | —                           | _       |

| 14h    | _      | Unimplen      | nented                       |             |               |               |               |            |                     | —                           | _       |

| 15h    |        | Unimplemented |                              |             |               |               |               |            |                     | _                           |         |

| 16h    |        | Unimplemented |                              |             |               |               |               |            | _                   |                             |         |

| 17h    |        | Unimplen      | nented                       |             |               |               |               |            |                     |                             | _       |

| 18h    | WDTCON | —             | —                            | _           | WDTPS3        | WDTPS2        | WDTPS1        | WDTPS0     | SWDTEN              | 0 1000                      | 144,137 |

| 19h    | CMCON0 | C2OUT         | C10UT                        | C2INV       | C1INV         | CIS           | CM2           | CM1        | CM0                 | 0000 0000                   | 79,137  |

| 1Ah    | CMCON1 | —             | —                            |             |               | —             | _             | T1GSS      | C2SYNC              | 10                          | 82,137  |

| 1Bh    | —      | Unimplen      | nented                       |             |               |               |               |            |                     | _                           | _       |

| 1Ch    | —      | Unimplen      | nented                       |             |               |               |               |            |                     | _                           | _       |

| 1Dh    | —      | Unimplen      | nented                       |             |               |               |               |            |                     | —                           | _       |

| 1Eh    | —      | Unimplen      | nented                       |             |               |               |               |            |                     | —                           | _       |

| 1Fh    | —      | Unimplen      | nented                       |             |               |               |               |            |                     | —                           | _       |

| <b>TABLE 2-3:</b> | PIC16F636/639 SPECIAL | <b>FUNCTION REGISTERS SUMMARY BANK 0</b> |

|-------------------|-----------------------|------------------------------------------|

|                   |                       |                                          |

Legend: -= Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note** 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: MCLR and WDT Reset do not affect the previous value data latch. The RAIF bit will be cleared upon Reset but will set again if the mismatch exists.

#### REGISTER 4-3: WDA: WEAK PULL-UP/PULL-DOWN DIRECTION REGISTER

| U-0   | U-0 | R/W-1 | R/W-1 | U-0 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-----|-------|-------|-------|

| —     | —   | WDA5  | WDA4  | —   | WDA2  | WDA1  | WDA0  |

| bit 7 |     |       |       |     |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 7-6 | Unimplemented: Read as '0'                                                                   |

|---------|----------------------------------------------------------------------------------------------|

| bit 5-4 | WDA<5:4>: Pull-up/Pull-down Selection bits<br>1 = Pull-up selected<br>0 = Pull-down selected |

| bit 3   | Unimplemented: Read as '0'                                                                   |

| bit 2-0 | WDA<2:0>: Pull-up/Pull-down Selection bits<br>1 = Pull-up selected<br>0 = Pull-down selected |

- **Note 1:** The weak pull-up/pull-down device is enabled only when the global RAPU bit is enabled, the pin is in Input mode (TRIS = 1), the individual WDA bit is enabled (WDA = 1) and the pin is not configured as an analog input or clock function.

- 2: RA3 pull-up is enabled when the pin is configured as MCLR in the Configuration Word register and the device is not in Programming mode.

#### REGISTER 4-4: WPUDA: WEAK PULL-UP/PULL-DOWN ENABLE REGISTER

| U-0   | U-0 | R/W-1                 | R/W-1                 | U-0 | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----------------------|-----------------------|-----|--------|--------|--------|

| —     | —   | WPUDA5 <sup>(3)</sup> | WPUDA4 <sup>(3)</sup> |     | WPUDA2 | WPUDA1 | WPUDA0 |

| bit 7 |     |                       |                       |     |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                               |

|---------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | WPUDA<5:4>: Pull-up/Pull-down Direction Selection bits <sup>(3)</sup><br>1 = Pull-up/pull-down enabled<br>0 = Pull-up/pull-down disabled |

| bit 3   | Unimplemented: Read as '0'                                                                                                               |

| bit 2-0 | WPUDA<2:0>: Pull-up/Pull-down Direction Selection bits<br>1 = Pull-up/pull-down enabled<br>0 = Pull-up/pull-down disabled                |

- Note 1: The weak pull-up/pull-down direction device is enabled only when the global RAPU bit is enabled, the pin is in Input mode (TRIS = 1), the individual WPUDA bit is enabled (WPUDA = 1) and the pin is not configured as an analog input or clock function.

- 2: RA3 pull-up is enabled when the pin is configured as MCLR in the Configuration Word register and the device is not in Programming mode.

- 3: WPUDA5 bit can be written if INTOSC is enabled and T1OSC is disabled; otherwise, the bit can not be written and reads as '1'. WPUDA4 bit can be written if not configured as OSC2; otherwise, the bit can not be written and reads as '1'

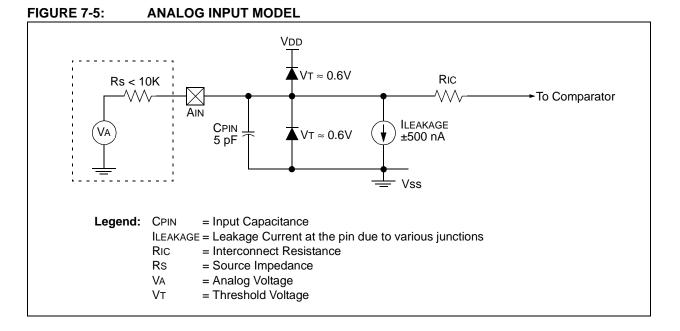

#### 7.2 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 7-5. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSs. The analog input, therefore, must be between VSs and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

### 9.0 DATA EEPROM MEMORY

The EEPROM data memory is readable and writable during normal operation (full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers. There are four SFRs used to read and write this memory:

- EECON1

- EECON2 (not a physically implemented register)

- EEDAT

- EEADR

**REGISTER 9-1:**

EEDAT holds the 8-bit data for read/write and EEADR holds the address of the EEPROM location being accessed. PIC16F636/639 has 256 bytes of data EEPROM and the PIC12F635 has 128 bytes.

The EEPROM data memory allows byte read and write. A byte write automatically erases the location and writes the new data (erase before write). The EEPROM data memory is rated for high erase/write cycles. The write time is controlled by an on-chip timer. The write time will vary with voltage and temperature as well as from chip-to-chip. Please refer to A/C specifications in **Section 15.0 "Electrical Specifications"** for exact limits.

When the data memory is code-protected, the CPU may continue to read and write the data EEPROM memory. The device programmer can no longer access the data EEPROM data and will read zeroes.

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| EEDAT7 | EEDAT6 | EEDAT5 | EEDAT4 | EEDAT3 | EEDAT2 | EEDAT1 | EEDAT0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

|        |        |        |        |        |        |        |        |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0 **EEDATn**: Byte Value to Write To or Read From Data EEPROM bits

**EEDAT: EEPROM DATA REGISTER**

#### **REGISTER 9-2: EEADR: EEPROM ADDRESS REGISTER**

| R/W-0                 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-----------------------|--------|--------|--------|--------|--------|--------|--------|

| EEADR7 <sup>(1)</sup> | EEADR6 | EEADR5 | EEADR4 | EEADR3 | EEADR2 | EEADR1 | EEADR0 |

| bit 7                 |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 **EEADR**: Specifies One of 256 Locations for EEPROM Read/Write Operation bits

Note 1: PIC16F636/639 only. Read as '0' on PIC12F635.

#### 9.1 EECON1 AND EECON2 Registers

EECON1 is the control register with four low-order bits physically implemented. The upper four bits are non-implemented and read as '0's.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit, clear it and rewrite the location. The data and address will be cleared. Therefore, the EEDAT and EEADR registers will need to be re-initialized.

Interrupt flag, EEIF bit of the PIR1 register, is set when write is complete. This bit must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence.

Note: The EECON1, EEDAT and EEADR registers should not be modified during a data EEPROM write (WR bit = 1).

#### **REGISTER 9-3: EECON1: EEPROM CONTROL REGISTER**

| U-0   | U-0 | U-0 | U-0 | R/W-x | R/W-0 | R/S-0 | R/S-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | —   | —   | WRERR | WREN  | WR    | RD    |

| bit 7 |     |     |     |       |       |       | bit 0 |

| Legend:                 |                  |                             |                    |

|-------------------------|------------------|-----------------------------|--------------------|

| S = Bit can only be set |                  |                             |                    |

| R = Readable bit        | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR       | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                                                                                             |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | WRERR: EEPROM Error Flag bit                                                                                                                                                                                           |

|         | <ul> <li>1 = A write operation is prematurely terminated (any MCLR Reset, any WDT Reset during normal operation or BOR Reset)</li> <li>0 = The write operation completed</li> </ul>                                    |

| bit 2   | WREN: EEPROM Write Enable bit                                                                                                                                                                                          |

|         | <ul> <li>1 = Allows write cycles</li> <li>0 = Inhibits write to the data EEPROM</li> </ul>                                                                                                                             |

| bit 1   | WR: Write Control bit                                                                                                                                                                                                  |

|         | <ul> <li>1 = Initiates a write cycle (The bit is cleared by hardware once write is complete. The WR bit can only be set, not cleared, in software.)</li> <li>0 = Write cycle to the data EEPROM is complete</li> </ul> |

| bit 0   | RD: Read Control bit                                                                                                                                                                                                   |

|         | <ul> <li>1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bit can only<br/>be set, not cleared, in software.)</li> </ul>                                                          |

0 = Does not initiate an EEPROM read

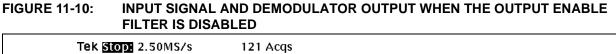

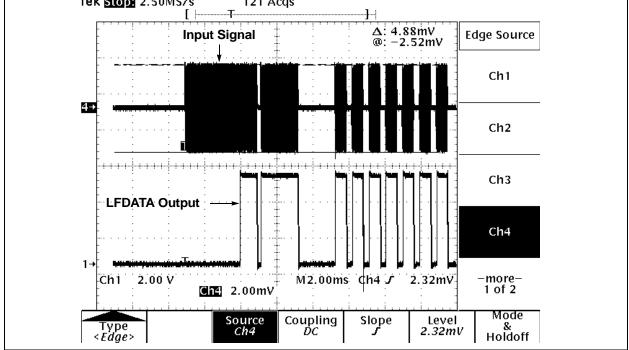

**Case I. When Output Enable Filter is disabled:** Demodulated output is available immediately after the AGC stabilization time (TAGC). Figure 11-10 shows an example of demodulated output when the Output Enable Filter is disabled.

**Case II. When Output Enable Filter is enabled**: Demodulated output is available only if the incoming signal meets the enable filter timing criteria that is defined in the Configuration Register 0 (Register 11-1). If the criteria is met, the output is available after the low timing (TOEL) of the Enable Filter. Figure 11-11 and Figure 11-12 shows examples of demodulated output when the Output Enable Filter is enabled.

#### REGISTER 12-1: CONFIG: CONFIGURATION WORD REGISTER

|               | —                                                                                                                                                       | _                                                                                                                                                                                                           | WURE                                                                                                                                | FCMEN                                                                                                                | IESO                                                                                                                             | BOREN1                                                                                                       | BOREN0                          |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------|

| bit 15        |                                                                                                                                                         |                                                                                                                                                                                                             |                                                                                                                                     | •                                                                                                                    |                                                                                                                                  |                                                                                                              | bit 8                           |

|               |                                                                                                                                                         |                                                                                                                                                                                                             |                                                                                                                                     |                                                                                                                      |                                                                                                                                  |                                                                                                              |                                 |

|               |                                                                                                                                                         |                                                                                                                                                                                                             |                                                                                                                                     | 1                                                                                                                    | 1                                                                                                                                | -                                                                                                            | 1                               |

| CPD           | D CP                                                                                                                                                    | MCLRE                                                                                                                                                                                                       | PWRTE                                                                                                                               | WDTE                                                                                                                 | FOSC2                                                                                                                            | FOSC1                                                                                                        | FOSC0                           |

| bit 7         |                                                                                                                                                         |                                                                                                                                                                                                             |                                                                                                                                     |                                                                                                                      |                                                                                                                                  |                                                                                                              | bit 0                           |

|               |                                                                                                                                                         |                                                                                                                                                                                                             |                                                                                                                                     |                                                                                                                      |                                                                                                                                  |                                                                                                              |                                 |

| Legend:       | - L L - L - L - L                                                                                                                                       |                                                                                                                                                                                                             |                                                                                                                                     | D D                                                                                                                  |                                                                                                                                  |                                                                                                              |                                 |

| R = Reada     |                                                                                                                                                         | W = Writable bit                                                                                                                                                                                            |                                                                                                                                     | P = Programm                                                                                                         |                                                                                                                                  | U = Unimplement<br>x = Bit is unknow                                                                         | nted bit, read as '0'           |

| -n = Value    | alfor                                                                                                                                                   | '1' = Bit is set                                                                                                                                                                                            |                                                                                                                                     | '0' = Bit is clea                                                                                                    | lieu                                                                                                                             | X = DILIS UNKNOV                                                                                             | VII                             |

| bit 15-13     | Unimplement                                                                                                                                             | ed: Read as '1'                                                                                                                                                                                             |                                                                                                                                     |                                                                                                                      |                                                                                                                                  |                                                                                                              |                                 |

| bit 12        | <u> </u>                                                                                                                                                | up Reset Enable                                                                                                                                                                                             | bit                                                                                                                                 |                                                                                                                      |                                                                                                                                  |                                                                                                              |                                 |

|               |                                                                                                                                                         | ake-up and conti                                                                                                                                                                                            |                                                                                                                                     |                                                                                                                      |                                                                                                                                  |                                                                                                              |                                 |

|               |                                                                                                                                                         | nd Reset enabled                                                                                                                                                                                            |                                                                                                                                     |                                                                                                                      |                                                                                                                                  |                                                                                                              |                                 |

| bit 11        | 1 = Fail-Safe C                                                                                                                                         | Safe Clock Monito<br>Clock Monitor is en<br>Clock Monitor is di                                                                                                                                             | nabled                                                                                                                              |                                                                                                                      |                                                                                                                                  |                                                                                                              |                                 |

| bit 10        | <b>IESO:</b> Internal External Switchover bit<br>1 = Internal External Switchover mode is enabled<br>0 = Internal External Switchover mode is disabled  |                                                                                                                                                                                                             |                                                                                                                                     |                                                                                                                      |                                                                                                                                  |                                                                                                              |                                 |

| bit 9-8       | 11 = BOR ena<br>10 = BOR ena<br>01 = BOR con                                                                                                            | Brown-out Rese<br>bled, SBOREN bi<br>bled during opera<br>trolled by SBORE<br>SBOREN bits dis                                                                                                               | t disabled<br>tion and disabl<br>N bit of the PC                                                                                    | ed in Sleep, SB                                                                                                      | OREN bit disable                                                                                                                 | ed                                                                                                           |                                 |

| bit 7         | 1 = Data memo                                                                                                                                           | de Protection bit <sup>(2</sup><br>bry code protectio                                                                                                                                                       | n is disabled                                                                                                                       |                                                                                                                      |                                                                                                                                  |                                                                                                              |                                 |

| bit 6         | <b>CP</b> : Code Prot<br>1 = Program m                                                                                                                  | ory code protectic<br>ection bit <sup>(3)</sup><br>lemory code prote<br>lemory code prote                                                                                                                   | ection is disable                                                                                                                   |                                                                                                                      |                                                                                                                                  |                                                                                                              |                                 |

| bit 5         | $1 = \overline{\text{MCLR}} \text{ pin}$                                                                                                                | R pin function sele<br>function is MCLR<br>function is digital                                                                                                                                              |                                                                                                                                     | ternally tied to \                                                                                                   | /DD                                                                                                                              |                                                                                                              |                                 |

| bit 4         | 0 = MCLR pin function is digital input, MCLR internally tied to VDD<br><b>PWRTE:</b> Power-up Timer Enable bit<br>1 = PWRT disabled<br>0 = PWRT enabled |                                                                                                                                                                                                             |                                                                                                                                     |                                                                                                                      |                                                                                                                                  |                                                                                                              |                                 |

| bit 3         | <b>WDTE:</b> Watcher<br>1 = WDT enab                                                                                                                    | dog Timer Enable                                                                                                                                                                                            |                                                                                                                                     | OTEN bit of the V                                                                                                    | NDTCON registe                                                                                                                   | er                                                                                                           |                                 |

| bit 2-0       | FOSC<2:0>: C<br>111 = EXTRC<br>110 = EXTRC<br>101 = INTOS<br>100 = INTOS<br>011 = EC: I/C<br>010 = HS osc<br>001 = XT osc                               | Descillator Selectio<br>Coscillator: Exter<br>CIO oscillator: Exter<br>CIO oscillator: CLK<br>CIO oscillator: I/C<br>0 function on RA4<br>cillator: High-spee<br>cillator: Crystal/res<br>illator: Low-powe | n bits<br>nal RC on RA5<br>ernal RC on RA<br>OUT function o<br>) function on R<br>/OSC2/CLKOU<br>od crystal/reson<br>sonator on RA4 | /OSC1/CLKIN, 1<br>5/OSC1/CLKIN,<br>n RA4/OSC2/C<br>A4/OSC2/CLKC<br>IT pin, CLKIN of<br>ator on RA4/OS<br>/OSC2/CLKOU | CLKOUT function<br>I/O function on I<br>LKOUT pin, I/O f<br>DUT pin, I/O func<br>n RA5/OSC1/CL<br>SC2/CLKOUT an<br>T and RA5/OSC | n on RA4/OSC2/0<br>RA4/OSC2/CLKO<br>function on RA5/0<br>tion on RA5/OSC<br>KIN<br>d RA5/OSC1/CLP<br>1/CLKIN | UT pin<br>DSC1/CLKIN<br>1/CLKIN |

| Note 1:<br>2: | Enabling Brown-out<br>The entire data EEF                                                                                                               |                                                                                                                                                                                                             |                                                                                                                                     |                                                                                                                      |                                                                                                                                  |                                                                                                              |                                 |

- 3: The entire program memory will be erased when the code protection is turned off.

- 4: When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled.

#### 12.10 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W and STATUS registers). This must be implemented in software.

Since the lower 16 bytes of all banks are common in the PIC12F635/PIC16F636/639 (see Figure 2-2), temporary holding registers, W\_TEMP and STATUS\_TEMP, should be placed in here. These 16 locations do not require banking and therefore, make it easier to context save and restore. The same code shown in Example 12-1 can be used to:

- Store the W register.

- Store the STATUS register.

- · Execute the ISR code.

- · Restore the Status (and Bank Select Bit register).

- Restore the W register.

| Note: | The PIC12F635/PIC16F636/639 normally    |

|-------|-----------------------------------------|

|       | does not require saving the PCLATH.     |

|       | However, if computed GOTO's are used in |

|       | the ISR and the main code, the PCLATH   |

|       | must be saved and restored in the ISR.  |

#### EXAMPLE 12-1: SAVING STATUS AND W REGISTERS IN RAM

| MOVWF<br>SWAPF | W_TEMP<br>STATUS,W | ;Copy W to TEMP register<br>;Swap status to be saved into W                                   |

|----------------|--------------------|-----------------------------------------------------------------------------------------------|

| SWAFT          | SIA105,W           | ;Swap status to be saved into w<br>;Swaps are used because they do not affect the status bits |

|                | STATUS_TEMP        | ;Save status to bank zero STATUS_TEMP register                                                |

| :              |                    |                                                                                               |

| :(ISR)         |                    | ;Insert user code here                                                                        |

| :              |                    |                                                                                               |

| SWAPF          | STATUS_TEMP,W      | ;Swap STATUS_TEMP register into W                                                             |

|                |                    | ;(sets bank to original state)                                                                |

| MOVWF          | STATUS             | ;Move W into STATUS register                                                                  |

| SWAPF          | W_TEMP,F           | ;Swap W_TEMP                                                                                  |

| SWAPF          | W_TEMP,W           | ;Swap W_TEMP into W                                                                           |

|                |                    |                                                                                               |

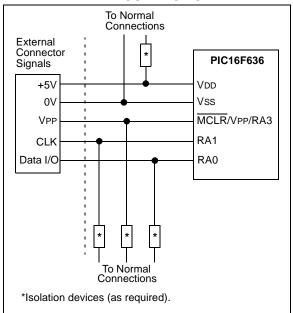

#### 12.15 In-Circuit Serial Programming

The PIC12F635/PIC16F636/639 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for:

- Power

- Ground

- Programming Voltage

This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RA0 and RA1 pins low, while raising the MCLR (VPP) pin from VIL to VIHH. See the 'PIC12F6XX/16F6XX *Memory Programming Specification*" (DS41204) for more information. RA0 becomes the programming data and RA1 becomes the programming clock. Both RA0 and RA1 are Schmitt Trigger inputs in this mode.

After Reset, to place the device into Program/Verify mode, the Program Counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending on whether the command was a load or a read. For complete details of serial programming, please refer to the "PIC12F6XX/16F6XX Memory Programming Specification" (DS41204).

A typical In-Circuit Serial Programming connection is shown in Figure 12-11.

#### FIGURE 12-11: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

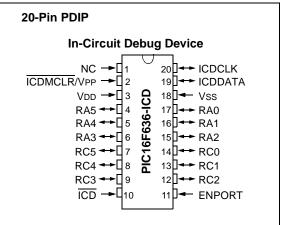

#### 12.16 In-Circuit Debugger

Since in-circuit debugging requires the loss of clock, data and MCLR pins, MPLAB<sup>®</sup> ICD 2 development with a 14-pin device is not practical. A special 20-pin PIC16F636 ICD device is used with MPLAB ICD 2 to provide separate clock, data and MCLR pins and frees all normally available pins to the user.

Use of the ICD device requires the purchase of a special header. On the top of the header is an MPLAB ICD 2 connector. On the bottom of the header is a 14-pin socket that plugs into the user's target via the 14-pin stand-off connector.

When the  $\overline{\text{ICD}}$  pin on the PIC16F636 ICD device is held low, the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB ICD 2. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 12-9 shows which features are consumed by the background debugger:

#### TABLE 12-9:DEBUGGER RESOURCES

| Resource       | Description                         |

|----------------|-------------------------------------|

| I/O pins       | ICDCLK, ICDDATA                     |

| Stack          | 1 level                             |

| Program Memory | Address 0h must be NOP<br>700h-7FFh |

For more information, see the "*MPLAB*<sup>®</sup> *ICD 2 In-Circuit Debugger User's Guide*" (DS51331), available on Microchip's web site (www.microchip.com).

#### FIGURE 12-12: 20-PIN ICD PINOUT

| ADDLW            | Add literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |

| Operands:        | $0 \le k \le 255$                                                                                                          |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the<br>W register. |

Instruction Descriptions

13.2

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ADDWF            | Add W and f                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                    |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |

| Status Affected: | C, DC, Z                                                                                                                                                                           |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND literal with W                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |

| Operands:        | $0 \le k \le 255$                                                                                                      |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                             |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the<br>next instruction is discarded, and<br>a NOP is executed instead, making<br>this a two-cycle instruction. |

| ANDWF            | AND W with f                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                               |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ensuremath{\left[0,1\right]} \end{array}$                                                                                                                                                                                                                                                    |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                       |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', then a NOP is<br>executed instead, making it a<br>two-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                       |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a two-cycle<br>instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                          |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                               |