# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, WDT                                   |

| Number of I/O              | 11                                                                      |

| Program Memory Size        | 3.5KB (2K x 14)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 20-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f639-e-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

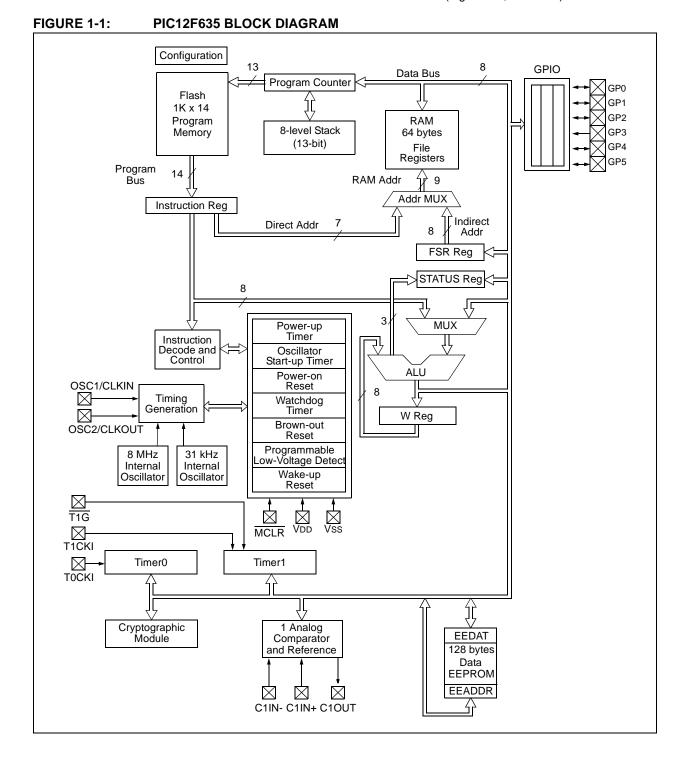

### 1.0 DEVICE OVERVIEW

This document contains device specific information for the PIC12F635/PIC16F636/639 devices.

Block Diagrams and pinout descriptions of the devices are as follows:

- PIC12F635 (Figure 1-1, Table 1-1)

- PIC16F636 (Figure 1-2, Table 1-2)

- PIC16F639 (Figure 1-3, Table 1-3)

NOTES:

| TABLE 2-5: | PIC12F635/PIC16F636/639 SPECIAL FUNCTION REGISTERS SUMMARY BANK 2 |

|------------|-------------------------------------------------------------------|

|            |                                                                   |

| Addr   | Name                  | Bit 7      | Bit 6                                                            | Bit 5    | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Value on<br>POR/BOR/<br>WUR | Page      |

|--------|-----------------------|------------|------------------------------------------------------------------|----------|-------|-------|-------|--------|--------|-----------------------------|-----------|

| Bank 2 | 3ank 2                |            |                                                                  |          |       |       |       |        |        |                             |           |

| 10Ch   | _                     | Unimpleme  | ented                                                            |          |       |       |       |        |        | _                           | —         |

| 10Dh   | _                     | Unimpleme  | ented                                                            |          |       |       |       |        |        | —                           | _         |

| 10Eh   | _                     | Unimpleme  | Inimplemented                                                    |          |       |       |       |        |        |                             | _         |

| 10Fh   | _                     | Unimpleme  | Jnimplemented                                                    |          |       |       |       |        |        |                             | —         |

| 110h   | CRCON                 | GO/DONE    | ENC/DEC                                                          | —        | _     | _     | _     | CRREG1 | CRREG0 | 0000                        | 0000      |

| 111h   | CRDAT0 <sup>(2)</sup> | Cryptograp | Cryptographic Data Register 0                                    |          |       |       |       |        |        | 0000 0000                   | 0000 0000 |

| 112h   | CRDAT1 <sup>(2)</sup> | Cryptograp | hic Data Re                                                      | gister 1 |       |       |       |        |        | 0000 0000                   | 0000 0000 |

| 113h   | CRDAT2 <sup>(2)</sup> | Cryptograp | hic Data Re                                                      | gister 2 |       |       |       |        |        | 0000 0000                   | 0000 0000 |

| 114h   | CRDAT3 <sup>(2)</sup> | Cryptograp | Cryptographic Data Register 3 0000 0000 0000 0000 0000 0000 0000 |          |       |       |       |        |        |                             | 0000 0000 |

| 115h   | —                     | Unimpleme  | ented                                                            |          |       |       |       |        |        | —                           | —         |

| 116h   | —                     | Unimpleme  | ented                                                            |          |       |       |       |        |        | —                           | —         |

Legend: -= Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: CRDAT<3:0> registers are KEELOQ<sup>®</sup> hardware peripheral related registers and require the execution of the "KEELOQ Encoder License Agreement" regarding implementation of the module and access to related registers. The "KEELOQ Encoder License Agreement" may be accessed through the Microchip web site located at <u>www.microchip.com/KEELOQ</u> or by contacting your local Microchip Sales Representative. NOTES:

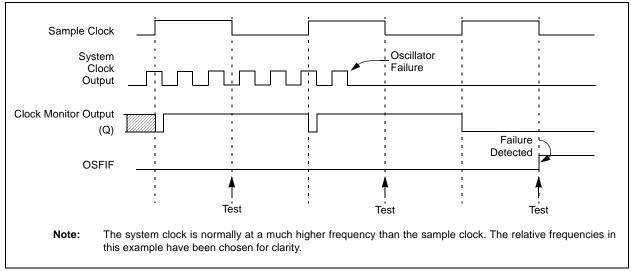

#### FIGURE 3-9: FSCM TIMING DIAGRAM

| Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4               | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets <sup>(1)</sup> |

|-----------------------|-------|-------|-------|---------------------|-------|-------|-------|--------|----------------------|------------------------------------------------|

| CONFIG <sup>(2)</sup> | CPD   | CP    | MCLRE | PWRTE               | WDTE  | FOSC2 | FOSC1 | FOSC0  | _                    | _                                              |

| INTCON                | GIE   | PEIE  | TOIE  | INTE                | RAIE  | T0IF  | INTF  | RAIF   | x000 000x            | 0000 000x                                      |

| OSCCON                | —     | IRCF2 | IRCF1 | IRCF0               | OSTS  | HTS   | LTS   | SCS    | -110 x000            | -110 x000                                      |

| OSCTUNE               | —     | —     | —     | TUN4                | TUN3  | TUN2  | TUN1  | TUN0   | 0 0000               | u uuuu                                         |

| PIE1                  | EEIE  | LVDIE | CRIE  | C2IE <sup>(3)</sup> | C1IE  | OSFIE | —     | TMR1IE | 000- 00-0            | 000- 00-0                                      |

| PIR1                  | EEIF  | LVDIF | CRIF  | C2IF <sup>(3)</sup> | C1IF  | OSFIF | —     | TMR1IF | 000- 00-0            | 000- 00-0                                      |

$\label{eq:local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_local_$

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: See Configuration Word register (CONFIG) for operation of all register bits.

3: PIC16F636/639 only.

#### 4.0 I/O PORTS

There are as many as twelve general purpose I/O pins available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

#### 4.1 PORTA and the TRISA Registers

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 4-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin). The exception is RA3, which is input only and its TRIS bit will always read as '1'. Example 4-1 shows how to initialize PORTA.

Note: PORTA = GPIO TRISA = TRISIO

Reading the PORTA register (Register 4-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch. RA3 reads '0' when MCLRE = 1.

The TRISA register controls the direction of the PORTA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

Note: The CMCON0 register must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

#### EXAMPLE 4-1: INITIALIZING PORTA

| BANKSEI | L PORTA     | i                      |

|---------|-------------|------------------------|

| CLRF    | PORTA       | ;Init PORTA            |

| MOVLW   | 07h         | ;Set RA<2:0> to        |

| MOVWF   | CMCON0      | ;digital I/O           |

| BSF     | STATUS, RPO | ;Bank 1                |

| BCF     | STATUS, RP1 | ;                      |

| MOVLW   | 0Ch         | ;Set RA<3:2> as inputs |

| MOVWF   | TRISA       | ;and set RA<5:4,1:0>   |

|         |             | ;as outputs            |

#### 4.2 Additional Pin Functions

Every PORTA pin on the PIC12F635/PIC16F636/639 has an interrupt-on-change option and a weak pull-up/pull-down option. RA0 has an Ultra Low-Power Wake-up option. The next three sections describe these functions.

#### 4.2.1 WEAK PULL-UP/PULL-DOWN

Each of the PORTA pins, except RA3, has an internal weak pull-up and pull-down. The WDA bits select either a pull-up or pull-down for an individual port bit. Individual control bits can turn on the pull-up or pull-down. These pull-ups/pull-downs are automatically turned off when the port pin is configured as an output, as an alternate function or on a Power-on Reset, setting the RAPU bit of the OPTION register. A weak pull-up on RA3 is enabled when configured as MCLR in the Configuration Word register and disabled when high voltage is detected, to reduce current consumption through RA3, while in Programming mode.

Note: PORTA = GPIO

TRISA = TRISIO

#### 4.2.3 ULTRA LOW-POWER WAKE-UP

The Ultra Low-Power Wake-up (ULPWU) on RA0 allows a slow falling voltage to generate an interrupt-on-change on RA0 without excess current consumption. The mode is selected by setting the ULPWUE bit of the PCON register. This enables a small current sink which can be used to discharge a capacitor on RA0.

To use this feature, the RA0 pin is configured to output '1' to charge the capacitor, interrupt-on-change for RA0 is enabled and RA0 is configured as an input. The ULPWUE bit is set to begin the discharge and a SLEEP instruction is performed. When the voltage on RA0 drops below VIL, an interrupt will be generated which will cause the device to wake-up. Depending on the state of the GIE bit of the INTCON register, the device will either jump to the interrupt vector (0004h) or execute the next instruction when the interrupt event occurs. See Section 4.2.2 "Interrupt-on-Change" and Section 12.9.3 "PORTA Interrupt" more for information.

This feature provides a low-power technique for periodically waking up the device from Sleep. The time-out is dependent on the discharge time of the RC circuit on RA0. See Example 4-2 for initializing the Ultra Low Power Wake-up module.

The series resistor provides overcurrent protection for the RAO pin and can allow for software calibration of the time-out (see Figure 4-1). A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired interrupt delay. This technique will compensate for the affects of temperature, voltage and component accuracy. The Ultra Low-Power Wake-up peripheral can also be configured as a simple Programmable Low-Voltage Detect or temperature sensor.

Note: For more information, refer to the Application Note AN879, "Using the Microchip Ultra Low-Power Wake-up Module" (DS00879).

#### EXAMPLE 4-2: ULTRA LOW-POWER

### WAKE-UP INITIALIZATION

| BANKSEI | J PORTA     | ;                   |

|---------|-------------|---------------------|

| BSF     | PORTA,0     | ;Set RA0 data latch |

| MOVLW   | H'7'        | ;Turn off           |

| MOVWF   | CMCON0      | ; comparators       |

| BANKSEI | TRISA       | ;                   |

| BCF     | TRISA,0     | ;Output high to     |

| CALL    | CapDelay    | ; charge capacitor  |

| BSF     | PCON,ULPWUE | ;Enable ULP Wake-up |

| BSF     | IOCA,0      | ;Select RA0 IOC     |

| BSF     | TRISA,0     | ;RA0 to input       |

| MOVLW   | B'10001000' | ;Enable interrupt   |

| MOVWF   | INTCON      | ; and clear flag    |

| SLEEP   |             | ;Wait for IOC       |

| NOP     |             | ;                   |

|         |             |                     |

### 5.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the OPTION register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are 8 prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be assigned to the WDT module.

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

When the prescaler is assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

#### 5.1.3.1 Switching Prescaler Between Timer0 and WDT Modules

As a result of having the prescaler assigned to either Timer0 or the WDT, it is possible to generate an unintended device Reset when switching prescaler values. When changing the prescaler assignment from Timer0 to the WDT module, the instruction sequence shown in Example 5-1, must be executed.

### EXAMPLE 5-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BANKSEL<br>CLRWDT | TMR0            | ;<br>;Clear WDT               |

|-------------------|-----------------|-------------------------------|

| CLRF              | TMR 0           | ;Clear TMR0 and<br>;prescaler |

| BANKSEL           | OPTION REG      | ; prescarer                   |

| BSF               | OPTION_REG, PSA | ,<br>;Select WDT              |

| CLRWDT            |                 | ;                             |

|                   |                 | ;                             |

| MOVLW             | b'11111000'     | ;Mask prescaler               |

| ANDWF             | OPTION_REG,W    | ;bits                         |

| IORLW             | b'00000101'     | ;Set WDT prescaler            |

| MOVWF             | OPTION_REG      | ;to 1:32                      |

|                   |                 |                               |

When changing the prescaler assignment from the WDT to the Timer0 module, the following instruction sequence must be executed (see Example 5-2).

| EXAMPLE 5-2: | CHANGING PRESCALER         |

|--------------|----------------------------|

|              | (WDT $\rightarrow$ TIMER0) |

|                      | Clear WDT and        |

|----------------------|----------------------|

| BANKSEL OPTION_REG ; | Mask TMR0 select and |

| MOVLW b'11110000' ;  | prescaler bits       |

| ANDWF OPTION_REG,W ; | Set prescale to 1:16 |

#### 5.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The T0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The T0IF bit must be cleared in software. The Timer0 interrupt enable is the T0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the                         |

|-------|--------------------------------------------------------------|

|       | processor from Sleep since the timer is frozen during Sleep. |

|       |                                                              |

### 5.1.5 USING TIMER0 WITH AN EXTERNAL CLOCK

When Timer0 is in Counter mode, the synchronization of the T0CKI input and the Timer0 register is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, the high and low periods of the external clock source must meet the timing requirements as shown in the **Section 15.0 "Electrical Specifications"**.

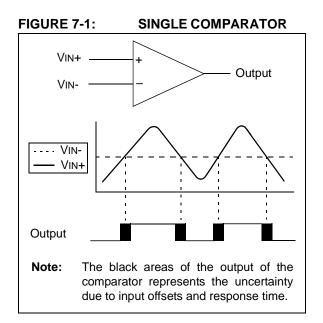

### 7.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. The comparators are very useful mixed signal building blocks because they provide analog functionality independent of the program execution. The Analog Comparator module includes the following features:

- Dual comparators (PIC16F636/639 only)

- Multiple comparator configurations

- Comparator(s) output is available internally/externally

- Programmable output polarity

- Interrupt-on-change

- Wake-up from Sleep

- Timer1 gate (count enable)

- Output synchronization to Timer1 clock input

- Programmable voltage reference

#### 7.1 Comparator Overview

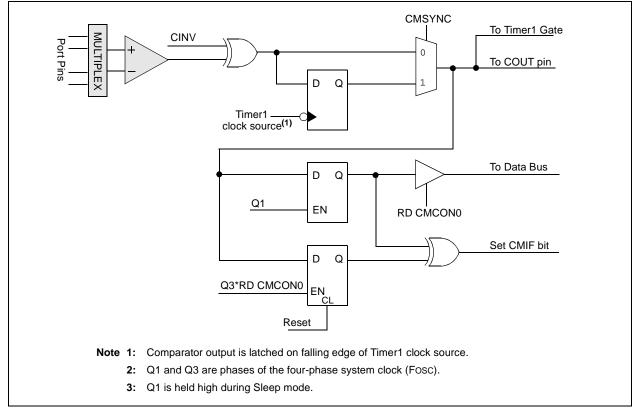

A comparator is shown in Figure 7-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the

comparator is a digital low level. When the analog voltage at  $V_{IN+}$  is greater than the analog voltage at  $V_{IN-}$ , the output of the comparator is a digital high level.

The PIC12F635 contains a single comparator as shown in Figure 7-2.

The PIC16F636/639 devices contains two comparators as shown in Figure 7-3 and Figure 7-4. The comparators are not independently configurable.

#### FIGURE 7-2: COMPARATOR OUTPUT BLOCK DIAGRAM (PIC12F635)

### TABLE 7-2:SUMMARY OF REGISTERS ASSOCIATED WITH THE COMPARATOR AND VOLTAGE<br/>REFERENCE MODULES

| Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|-------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| CMCON0 | —     | COUT  | _      | CINV   | CIS    | CM2    | CM1    | CM0    | -0-0 0000            | -0-0 0000                       |

| CMCON1 | _     | —     | _      | _      | —      | _      | T1GSS  | CMSYNC | 10                   | 10                              |

| INTCON | GIE   | PEIE  | TOIE   | INTE   | RAIE   | T0IF   | INTF   | RAIF   | x000 000x            | x000 000x                       |

| PIE1   | EEIE  | LVDIE | CRIE   |        | C1IE   | OSFIE  |        | TMR1IE | 000- 00-0            | 000- 00-0                       |

| PIR1   | EEIF  | LVDIF | CRIF   | _      | C1IF   | OSFIF  | _      | TMR1IF | 000- 00-0            | 000- 00-0                       |

| PORTA  | _     | —     | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xx xxxx              | uu uuuu                         |

| PORTC  | _     | —     | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xx xxxx              | uu uuuu                         |

| TRISA  | _     | —     | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111              | 11 1111                         |

| TRISC  | _     | —     | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 11 1111              | 11 1111                         |

| VRCON  | VREN  | _     | VRR    | _      | VR3    | VR2    | VR1    | VR0    | 0-0- 0000            | 0-0- 0000                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for comparator.

| U-0           | U-0                                         | R-0                                                                                                                                                                                | R/W-0          | U-0              | R/W-1            | R/W-0           | R/W-0 |  |  |  |  |

|---------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------|-----------------|-------|--|--|--|--|

| _             | _                                           | IRVST <sup>(1)</sup>                                                                                                                                                               | LVDEN          | —                | LVDL2            | LVDL1           | LVDL0 |  |  |  |  |

| bit 7         |                                             |                                                                                                                                                                                    |                |                  |                  |                 | bit   |  |  |  |  |

| Legend:       |                                             |                                                                                                                                                                                    |                |                  |                  |                 |       |  |  |  |  |

| R = Readabl   | le bit                                      | W = Writable                                                                                                                                                                       | bit            | U = Unimplen     | nented bit, read | l as '0'        |       |  |  |  |  |

| -n = Value at | POR                                         | '1' = Bit is set                                                                                                                                                                   |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |  |

| bit 7-6       | Unimplemen                                  | nted: Read as '                                                                                                                                                                    | ٥'             |                  |                  |                 |       |  |  |  |  |

| bit 5         | •                                           | nal Reference V                                                                                                                                                                    |                | Status Flag bit  | (1)              |                 |       |  |  |  |  |

| on o          |                                             |                                                                                                                                                                                    |                |                  |                  |                 |       |  |  |  |  |

|               |                                             | <ul> <li>1 = Indicates that the PLVD is stable and PLVD interrupt is reliable</li> <li>0 = Indicates that the PLVD is not stable and PLVD interrupt must not be enabled</li> </ul> |                |                  |                  |                 |       |  |  |  |  |

| bit 4         | LVDEN: Low-Voltage Detect Module Enable bit |                                                                                                                                                                                    |                |                  |                  |                 |       |  |  |  |  |

|               | 1 = Enables                                 | PLVD Module, j                                                                                                                                                                     | powers up PL   | VD circuit and   | supporting refer | ence circuitry  |       |  |  |  |  |

|               | 0 = Disables                                | PLVD Module,                                                                                                                                                                       | powers down    | PLVD circuit a   | nd supporting r  | eference circui | try   |  |  |  |  |

| bit 3         | Unimplemer                                  | nted: Read as '                                                                                                                                                                    | 0'             |                  |                  |                 |       |  |  |  |  |

| bit 2-0       | LVDL<2:0>:                                  | Low-Voltage De                                                                                                                                                                     | etection Level | bits (nominal v  | values)          |                 |       |  |  |  |  |

|               | 111 = 4.5V                                  |                                                                                                                                                                                    |                |                  |                  |                 |       |  |  |  |  |

|               | 110 = 4.2V                                  |                                                                                                                                                                                    |                |                  |                  |                 |       |  |  |  |  |

|               |                                             | 101 = 4.0V                                                                                                                                                                         |                |                  |                  |                 |       |  |  |  |  |

|               |                                             | 100 = 2.3V (default)                                                                                                                                                               |                |                  |                  |                 |       |  |  |  |  |

|               | 011 = 2.2V<br>010 = 2.1V                    |                                                                                                                                                                                    |                |                  |                  |                 |       |  |  |  |  |

|               | 010 = 2.1V<br>$001 = 2.0V^{(2)}$            | )                                                                                                                                                                                  |                |                  |                  |                 |       |  |  |  |  |

|               | 001 = 2.000                                 |                                                                                                                                                                                    |                |                  |                  |                 |       |  |  |  |  |

#### REGISTER 8-1: LVDCON: LOW-VOLTAGE DETECT CONTROL REGISTER

- **Note 1:** The IRVST bit is usable only when the HFINTOSC is running.

- 2: Not tested and below minimum operating conditions.

#### TABLE 8-1: REGISTERS ASSOCIATED WITH PROGRAMMABLE LOW-VOLTAGE DETECT

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|-------|-------|-------|-------|-------|-------|--------|----------------------|---------------------------------|

| INTCON | GIE   | PEIE  | T0IE  | INTE  | RAIE  | T0IF  | INTF  | RAIF   | x000 000x            | 0000 000x                       |

| PIE1   | OSFIE | C2IE  | C1IE  | LCDIE | _     | LVDIE | —     | CCP2IE | 0000 -0-0            | 0000 -0-0                       |

| PIR1   | OSFIF | C2IF  | C1IF  | LCDIF | _     | LVDIF | —     | CCP2IF | 0000 -0-0            | 0000 -0-0                       |

| LVDCON | _     | _     | IRVST | LVDEN |       | LVDL2 | LVDL1 | LVDL0  | 00 -100              | 00 -100                         |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used by the PLVD module.

### 9.0 DATA EEPROM MEMORY

The EEPROM data memory is readable and writable during normal operation (full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers. There are four SFRs used to read and write this memory:

- EECON1

- EECON2 (not a physically implemented register)

- EEDAT

- EEADR

**REGISTER 9-1:**

EEDAT holds the 8-bit data for read/write and EEADR holds the address of the EEPROM location being accessed. PIC16F636/639 has 256 bytes of data EEPROM and the PIC12F635 has 128 bytes.

The EEPROM data memory allows byte read and write. A byte write automatically erases the location and writes the new data (erase before write). The EEPROM data memory is rated for high erase/write cycles. The write time is controlled by an on-chip timer. The write time will vary with voltage and temperature as well as from chip-to-chip. Please refer to A/C specifications in **Section 15.0 "Electrical Specifications"** for exact limits.

When the data memory is code-protected, the CPU may continue to read and write the data EEPROM memory. The device programmer can no longer access the data EEPROM data and will read zeroes.

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| EEDAT7 | EEDAT6 | EEDAT5 | EEDAT4 | EEDAT3 | EEDAT2 | EEDAT1 | EEDAT0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

|        |        |        |        |        |        |        |        |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0 **EEDATn**: Byte Value to Write To or Read From Data EEPROM bits

EEDAT: EEPROM DATA REGISTER

#### REGISTER 9-2: EEADR: EEPROM ADDRESS REGISTER

| R/W-0                 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-----------------------|--------|--------|--------|--------|--------|--------|--------|

| EEADR7 <sup>(1)</sup> | EEADR6 | EEADR5 | EEADR4 | EEADR3 | EEADR2 | EEADR1 | EEADR0 |

| bit 7                 |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0 **EEADR**: Specifies One of 256 Locations for EEPROM Read/Write Operation bits

Note 1: PIC16F636/639 only. Read as '0' on PIC12F635.

#### 9.1 EECON1 AND EECON2 Registers

EECON1 is the control register with four low-order bits physically implemented. The upper four bits are non-implemented and read as '0's.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set in software. They are cleared in hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit, clear it and rewrite the location. The data and address will be cleared. Therefore, the EEDAT and EEADR registers will need to be re-initialized.

Interrupt flag, EEIF bit of the PIR1 register, is set when write is complete. This bit must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence.

Note: The EECON1, EEDAT and EEADR registers should not be modified during a data EEPROM write (WR bit = 1).

#### **REGISTER 9-3: EECON1: EEPROM CONTROL REGISTER**

| U-0   | U-0 | U-0 | U-0 | R/W-x | R/W-0 | R/S-0 | R/S-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| —     | —   | —   | —   | WRERR | WREN  | WR    | RD    |

| bit 7 |     |     |     |       |       |       | bit 0 |

| Legend:                 |                  |                             |                    |

|-------------------------|------------------|-----------------------------|--------------------|

| S = Bit can only be set |                  |                             |                    |

| R = Readable bit        | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR       | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-4 | Unimplemented: Read as '0'                                                                                                                                                                                             |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | WRERR: EEPROM Error Flag bit                                                                                                                                                                                           |

|         | <ul> <li>1 = A write operation is prematurely terminated (any MCLR Reset, any WDT Reset during normal operation or BOR Reset)</li> <li>0 = The write operation completed</li> </ul>                                    |

| bit 2   | WREN: EEPROM Write Enable bit                                                                                                                                                                                          |

|         | <ul> <li>1 = Allows write cycles</li> <li>0 = Inhibits write to the data EEPROM</li> </ul>                                                                                                                             |

| bit 1   | WR: Write Control bit                                                                                                                                                                                                  |

|         | <ul> <li>1 = Initiates a write cycle (The bit is cleared by hardware once write is complete. The WR bit can only be set, not cleared, in software.)</li> <li>0 = Write cycle to the data EEPROM is complete</li> </ul> |

| bit 0   | RD: Read Control bit                                                                                                                                                                                                   |

|         | <ul> <li>1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bit can only<br/>be set, not cleared, in software.)</li> </ul>                                                          |

0 = Does not initiate an EEPROM read

#### **REGISTER 11-4: CONFIGURATION REGISTER 3**

| U-0   | U-0 | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0 |

|-------|-----|---------|---------|---------|---------|---------|---------|-------|

| —     | —   | LCZTUN5 | LCZTUN4 | LCZTUN3 | LCZTUN2 | LCZTUN1 | LCZTUN0 | R3PAR |

| bit 8 |     |         |         |         |         |         |         | bit 0 |

| Legend:                        |                          |                      |

|--------------------------------|--------------------------|----------------------|

| R = Readable bit W = Writa     | ble bit U = Unimplemen   | ted bit, read as '0' |

| -n = Value at POR '1' = Bit is | set '0' = Bit is cleared | d x = Bit is unknown |

bit 8-7 Unimplemented: Read as '0'

- bit 6-1 LCZTUN<5:0>: LCZ Tuning Capacitance bit 000000 = +0 pF (Default) : 111111 = +63 pF

- bit 0 **R3PAR**: Register Parity Bit set/cleared so the 9-bit register contains odd parity an odd number of set bits

#### **REGISTER 11-5: CONFIGURATION REGISTER 4**

| R/W-0   | R/W-0 |

|---------|---------|---------|---------|---------|---------|---------|---------|-------|

| LCXSEN3 | LCXSEN2 | LCXSEN1 | LCXSEN0 | LCYSEN3 | LCYSEN2 | LCYSEN1 | LCYSEN0 | R4PAR |

| bit 8   |         |         |         |         |         |         |         | bit 0 |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 8-5 LCXSEN<3:0><sup>(1)</sup>: Typical LCX Sensitivity Reduction bit

|         | 0000 = -0 dB (Default)                                                                                            |

|---------|-------------------------------------------------------------------------------------------------------------------|

|         | 0001 = -2  dB                                                                                                     |

|         | 0010 = -4  dB                                                                                                     |

|         | 0011 = -6  dB                                                                                                     |

|         | 0100 = -8  dB                                                                                                     |

|         | 0101 = -10  dB                                                                                                    |

|         | 0110 = -12 dB                                                                                                     |

|         | 0111 = -14 dB                                                                                                     |

|         | 1000 = -16 dB                                                                                                     |

|         | 1001 = -18 dB                                                                                                     |

|         | 1010 = -20 dB                                                                                                     |

|         | 1011 = -22 dB                                                                                                     |

|         | 1100 = -24 dB                                                                                                     |

|         | 1101 = -26 dB                                                                                                     |

|         | 1110 = -28 dB                                                                                                     |

|         | 1111 = -30 dB                                                                                                     |

| bit 4-1 | LCYSEN<3:0> <sup>(1)</sup> : Typical LCY Sensitivity Reduction bit                                                |

|         | 0000 = -0  dB (Default)                                                                                           |

|         |                                                                                                                   |

|         | 1111 = -30  dB                                                                                                    |

| L:1.0   |                                                                                                                   |

| bit 0   | <b>R4PAR</b> : Register Parity Bit – set/cleared so the 9-bit register contains odd parity – an odd number of set |

|         | bits                                                                                                              |

|         |                                                                                                                   |

Note 1: Assured monotonic increment (or decrement) by design.

| SUBWF            | Subtract W from f                                                                                                                                                                          |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                 |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                         |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                      |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                   |  |  |  |

| Description:     | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is<br>'0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f. |  |  |  |

|                  | C = 0 W > f                                                                                                                                                                                |  |  |  |

| <b>C</b> = 0 | W > f                     |

|--------------|---------------------------|

| <b>C</b> = 1 | $W \leq f$                |

| DC = 0       | W<3:0>>f<3:0>             |

| DC = 1       | $W < 3:0 > \le f < 3:0 >$ |

| XORLW            | Exclusive OR literal with W                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                   |

| Operands:        | $0 \le k \le 255$                                                                                                          |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |

| Status Affected: | Z                                                                                                                          |

| Description:     | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |

| SWAPF            | Swap Nibbles in f                                                                                                                                                                  | XORWF            | Exclusive OR W with f                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                                         | Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                    | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                         |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$                                                                                                                                         | Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                               |

|                  | $(f < 7:4 >) \rightarrow (destination < 3:0 >)$                                                                                                                                    | Status Affected: | Z                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                               | Description:     | Exclusive OR the contents of the                                                                                                                        |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>'0', the result is placed in the W<br>register. If 'd' is '1', the result is<br>placed in register 'f'. |                  | W register with register 'f'. If 'd' is<br>'0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

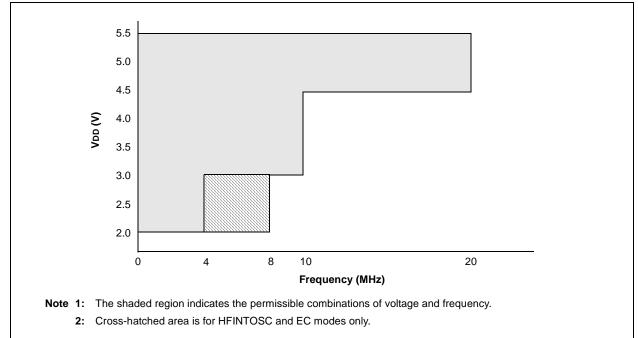

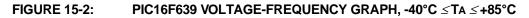

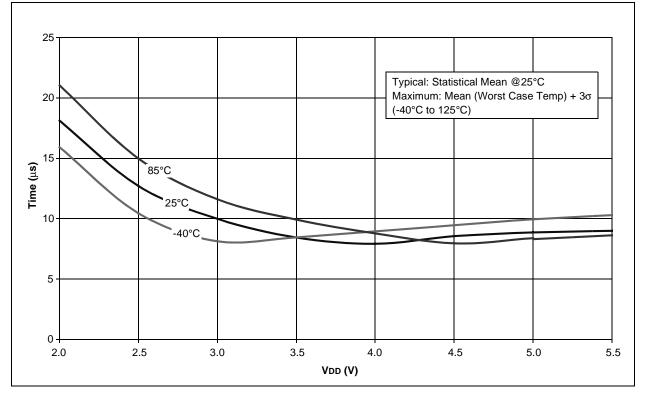

#### 15.1 DC Characteristics: PIC12F635/PIC16F636-I (Industrial) PIC12F635/PIC16F636-E (Extended)

| DC CHARACTERISTICS              |      | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}\mbox{C} \leq \mbox{Ta} \leq +85^{\circ}\mbox{C for industrial} \\ & -40^{\circ}\mbox{C} \leq \mbox{Ta} \leq +125^{\circ}\mbox{C for extended} \end{array}$ |                               |     |                          |         |                                                                                      |

|---------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----|--------------------------|---------|--------------------------------------------------------------------------------------|

| Param<br>No.                    | Sym  | Characteristic                                                                                                                                                                                                                                                                            | Min Typ† Max Units Conditions |     |                          |         |                                                                                      |

| D001<br>D001A<br>D001B<br>D001C | Vdd  | Supply Voltage                                                                                                                                                                                                                                                                            | 2.0<br>2.0<br>3.0<br>4.5      |     | 5.5<br>5.5<br>5.5<br>5.5 | > > > > | Fosc < = 4 MHz<br>Fosc < = 8 MHz, HFINTOSC, EC<br>Fosc < = 10 MHz<br>Fosc < = 20 MHz |

| D002                            | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>                                                                                                                                                                                                                                              | 1.5*                          | _   | _                        | V       | Device in Sleep mode                                                                 |

| D003                            | VPOR | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal                                                                                                                                                                                                                          | —                             | Vss | _                        | V       | See Section 12.3 "Power-on Reset" for details.                                       |

| D004                            | SVDD | VDD Rise Rate to ensure<br>internal Power-on Reset<br>signal                                                                                                                                                                                                                              | 0.05*                         | —   | —                        | V/ms    | See <b>Section 12.3 "Power-on Reset"</b> for details.                                |

| D005                            | VBOD | Brown-out Reset                                                                                                                                                                                                                                                                           | 2.0                           | 2.1 | 2.2                      | V       |                                                                                      |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

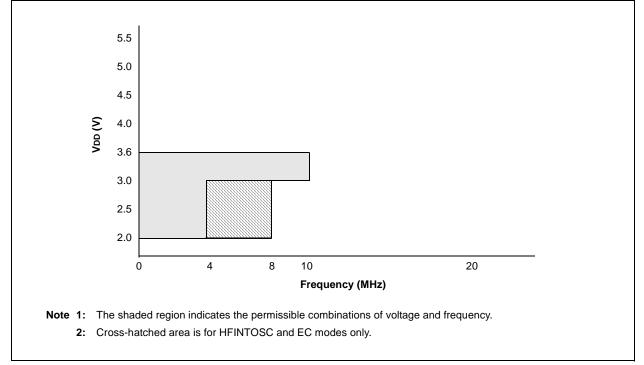

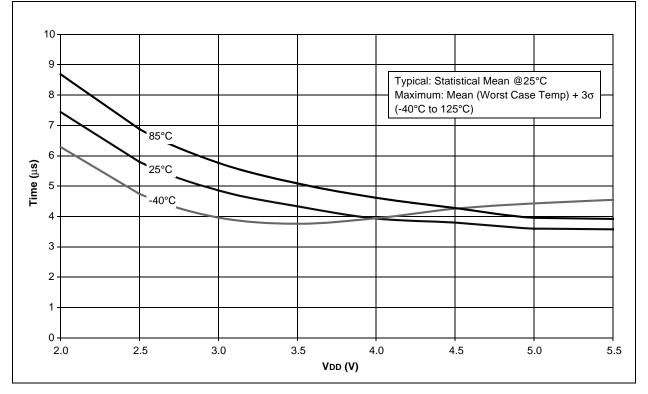

#### FIGURE 16-34: MAXIMUM HFINTOSC START-UP TIMES vs. VDD OVER TEMPERATURE

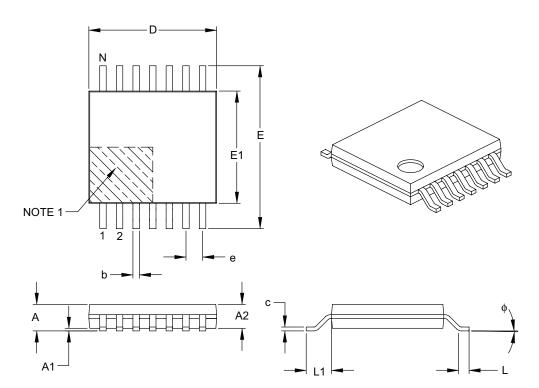

#### 14-Lead Plastic Thin Shrink Small Outline (ST) – 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          | MILLIMETERS | 3    |

|--------------------------|------------------|----------|-------------|------|

|                          | Dimension Limits | MIN      | NOM         | MAX  |

| Number of Pins           | N                |          | 14          |      |

| Pitch                    | e                |          | 0.65 BSC    |      |

| Overall Height           | A                | -        | -           | 1.20 |

| Molded Package Thickness | A2               | 0.80     | 1.00        | 1.05 |

| Standoff                 | A1               | 0.05     | -           | 0.15 |

| Overall Width            | E                |          | 6.40 BSC    |      |

| Molded Package Width     | E1               | 4.30     | 4.40        | 4.50 |

| Molded Package Length    | D                | 4.90     | 5.00        | 5.10 |

| Foot Length              | L                | 0.45     | 0.60        | 0.75 |

| Footprint                | L1               | 1.00 REF |             |      |

| Foot Angle               | φ                | 0°       | -           | 8°   |

| Lead Thickness           | С                | 0.09     | -           | 0.20 |

| Lead Width               | b                | 0.19     | -           | 0.30 |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-087B

| INTOSC                                   |

|------------------------------------------|

| INTOSCIO                                 |

| LFINTOSC                                 |

|                                          |

| Clock Switching                          |

| CMCON0 Register                          |

| CMCON1 Register                          |

| Code Examples                            |

| Assigning Prescaler to Timer0            |

| Assigning Prescaler to WDT               |

| Data EEPROM Read                         |

| Data EEPROM Write                        |

| Indirect Addressing                      |

| Initializing PORTA47                     |

| Initializing PORTC57                     |

| Saving Status and W Registers in RAM142  |

| Ultra Low-Power Wake-up Initialization51 |

| Write Verify93                           |

| Code Protection146                       |

| Comparator71                             |

| Associated registers85                   |

| C2OUT as T1 Gate81                       |

| Configurations74                         |

| I/O Operating Modes74                    |

| Interrupts77                             |

| Operation                                |

| Operation During Sleep79                 |

| Response Time                            |

| Synchronizing CxOUT w/Timer181           |

| Comparator Voltage Reference (CVREF)     |

| Response Time                            |

| Specifications                           |

| Comparator Voltage Reference (CVREF)     |

| Effects of a Reset                       |

| Specifications                           |

| Comparators                              |

| C2OUT as T1 Gate                         |

| Effects of a Reset                       |

| Specifications                           |

| CONFIG Register                          |

| Configuration Bits                       |

| CPU Features                             |

| Customer Change Notification Service     |

| Customer Notification Service            |

|                                          |

| Customer Support                         |

### D

| Data EEPROM Memory                                 |

|----------------------------------------------------|

| Associated Registers94                             |

| Code Protection                                    |

| Protection Against Spurious Write                  |

| Using                                              |

| Data Memory17                                      |

| DC and AC Characteristics                          |

| Graphs and Tables191                               |

| DC Characteristics                                 |

| Extended (PIC12F635/PIC16F636)169                  |

| Industrial (PIC12F635/PIC16F636)167                |

| Industrial (PIC16F639)174                          |

| Industrial/Extended (PIC12F635/PIC16F636) 166, 171 |

| Industrial/Extended (PIC16F639) 173, 175           |

| Development Support159                             |

| Device Overview                                    |

| E                                                  |

|                                                    |

| EEADR Register                     |  |

|------------------------------------|--|

| EECON1 (EEPROM Control 1) Register |  |

| EECON1 Register<br>EECON2 (EEPROM Control 2) Register |     |

|-------------------------------------------------------|-----|

| EEDAT Register                                        |     |

| EEPROM Data Memory                                    |     |

| Reading                                               | 93  |

| Write Verify                                          | 93  |

| Writing                                               |     |

| Electrical Specifications                             | 163 |

| Errata                                                |     |

#### F

| Fail-Safe Clock Monitor       | 45  |

|-------------------------------|-----|

| Fail-Safe Condition Clearing  |     |

| Fail-Safe Detection           |     |

| Fail-Safe Operation           | 45  |

| Reset or Wake-up from Sleep   | 45  |

| Firmware Instructions         | 149 |

| Fuses. See Configuration Bits |     |

#### G

| General Purpose Register (GPR) | File 18 |

|--------------------------------|---------|

|--------------------------------|---------|

#### I

| ID Locations                                | 146 |

|---------------------------------------------|-----|

| In-Circuit Debugger                         | 147 |

| In-Circuit Serial Programming (ICSP)        |     |

| Indirect Addressing, INDF and FSR Registers | 32  |

| Instruction Format                          |     |

| Instruction Set                             | 149 |

| ADDLW                                       |     |

| ADDWF                                       | 151 |

| ANDLW                                       |     |

| ANDWF                                       | -   |

| BCF                                         |     |

| BSF                                         |     |

| BTFSC                                       | 151 |

| BTFSS                                       |     |

| CALL                                        |     |

| CLRF                                        |     |

| CLRW                                        | 152 |

| CLRWDT                                      | 152 |

| COMF                                        | 152 |

| DECF                                        | 152 |

| DECFSZ                                      | 153 |

| GOTO                                        |     |

| INCF                                        | 153 |

| INCFSZ                                      | 153 |

| IORLW                                       | 153 |

| IORWF                                       | 153 |

| MOVF                                        | 154 |

| MOVLW                                       | 154 |

| MOVWF                                       | 154 |

| NOP                                         | 154 |

| RETFIE                                      | 155 |

| RETLW                                       | 155 |

| RETURN                                      | 155 |

| RLF                                         | 156 |

| RRF                                         | 156 |

| SLEEP                                       | 156 |

| SUBLW                                       | 156 |

| SUBWF                                       | 157 |

| SWAPF                                       | 157 |

| XORLW                                       |     |

| XORWF                                       | -   |

| Summary Table                               | 150 |

| INTCON Register                             |     |