# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, WDT                                    |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 20-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f639-i-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

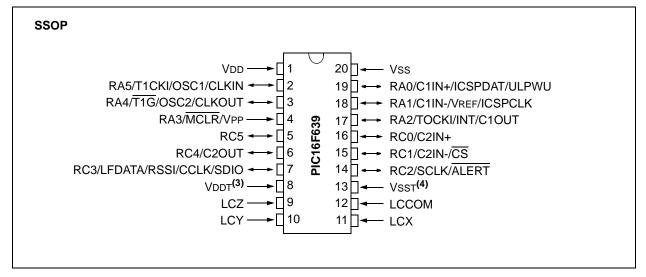

### 20-Pin Diagram

| TABLE 4: 20-PIN SUMMARY |

|-------------------------|

|-------------------------|

| I/O                | Pin | Analog Front-End | Comparators | Timer | Interrupts | Pull-ups | Basic           |

|--------------------|-----|------------------|-------------|-------|------------|----------|-----------------|

| RA0                | 19  |                  | C1IN+       | _     | IOC        | Y        | ICSPDAT/ULPWU   |

| RA1                | 18  | —                | C1IN-       | _     | IOC        | Y        | VREF/ICSPCLK    |

| RA2                | 17  | —                | C1OUT       | T0CKI | INT/IOC    | Y        | —               |

| RA3 <sup>(1)</sup> | 4   | _                | _           | _     | IOC        | Y(2)     | MCLR/Vpp        |

| RA4                | 3   | —                | —           | T1G   | IOC        | Y        | OSC2/CLKOUT     |

| RA5                | 2   |                  | —           | T1CKI | IOC        | Y        | OSC1/CLKIN      |

| RC0                | 16  | —                | C2IN+       | —     | —          | -        | —               |

| RC1                | 15  | —                | C2IN-       | —     | —          | —        | CS              |

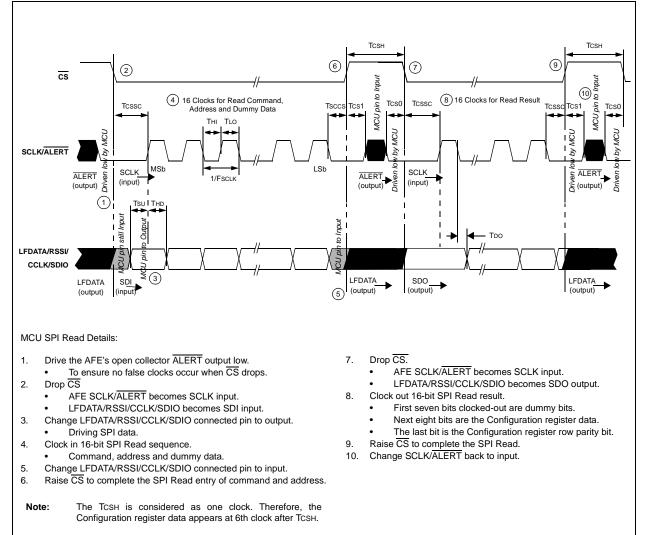

| RC2                | 14  | ALERT            | —           | —     | —          | _        | SCLK            |

| RC3                | 7   | LFDATA/RSSI      | —           | —     | _          |          | CCLK/SDIO       |

| RC4                | 6   |                  | C2OUT       | —     |            |          | —               |

| RC5                | 5   |                  | —           | —     | —          |          | —               |

| _                  | 8   | —                | —           | —     | —          | -        | Vddt(3)         |

| —                  | 13  |                  | —           | —     | —          |          | Vsst <b>(4)</b> |

|                    | 11  | LCX              | —           | —     | —          |          | —               |

| —                  | 10  | LCY              | —           | —     | _          |          | —               |

| —                  | 9   | LCZ              | —           |       | _          | _        | —               |

| —                  | 12  | LCCOM            |             | _     | _          | _        | _               |

|                    | 1   | _                | _           | _     | _          | _        | Vdd             |

|                    | 20  |                  |             | _     | _          | —        | Vss             |

Note 1: Input only.

2: Only when pin is configured for external MCLR.

**3:** VDDT is the supply voltage of the Analog Front-End section (PIC16F639 only). VDDT is treated as VDD in this document unless otherwise stated.

4: VSST is the ground reference voltage of the Analog Front-End section (PIC16F639 only). VSST is treated as VSS in this document unless otherwise stated.

#### TABLE 1-3: PIC16F639 PINOUT DESCRIPTIONS

| Name                                                                 | Function | Input<br>Type   | Output<br>Type | Description                                                                                                                                            |  |  |  |

|----------------------------------------------------------------------|----------|-----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| LCCOM                                                                | LCCOM    | AN              | -              | Common reference for analog inputs.                                                                                                                    |  |  |  |

| LCX                                                                  | LCX      | AN              | —              | 125 kHz analog X channel input.                                                                                                                        |  |  |  |

| LCY                                                                  | LCY      | AN              | _              | 125 kHz analog Y channel input.                                                                                                                        |  |  |  |

| LCZ                                                                  | LCZ      | AN              | _              | 125 kHz analog Z channel input.                                                                                                                        |  |  |  |

| RA0/C1IN+/ICSPDAT/ULPWU                                              | RA0      | TTL             | _              | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up/pull-down.<br>Selectable Ultra Low-Power Wake-up pin. |  |  |  |

|                                                                      | C1IN+    | AN              | —              | Comparator1 input – positive.                                                                                                                          |  |  |  |

|                                                                      | ICSPDAT  | TTL             | CMOS           | Serial Programming Data IO.                                                                                                                            |  |  |  |

|                                                                      | ULPWU    | AN              | —              | Ultra Low-Power Wake-up input.                                                                                                                         |  |  |  |

| RA1/C1IN-/VREF/ICSPCLK                                               | RA1      | TTL             | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up/pull-down.                                            |  |  |  |

|                                                                      | C1IN-    | AN              | —              | Comparator1 input – negative.                                                                                                                          |  |  |  |

|                                                                      | VREF     | AN              | _              | External voltage reference                                                                                                                             |  |  |  |

|                                                                      | ICSPCLK  | ST              | —              | Serial Programming Clock.                                                                                                                              |  |  |  |

| RA2/T0CKI/INT/C1OUT                                                  | RA2      | ST              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up/pull-down.                                            |  |  |  |

|                                                                      | TOCKI    | ST              | —              | External clock for Timer0.                                                                                                                             |  |  |  |

|                                                                      | INT      | ST              | —              | External Interrupt.                                                                                                                                    |  |  |  |

|                                                                      | C1OUT    | _               | CMOS           | Comparator1 output.                                                                                                                                    |  |  |  |

| RA3/MCLR/Vpp                                                         | RA3      | TTL             | —              | General purpose input. Individually controlled interrupt-on-change.                                                                                    |  |  |  |

|                                                                      | MCLR     | ST              | -              | Master Clear Reset. Pull-up enabled when configured as MCLF                                                                                            |  |  |  |

|                                                                      | Vpp      | HV              | —              | Programming voltage.                                                                                                                                   |  |  |  |

| RA4/T1G/OSC2/CLKOUT                                                  | RA4      | TTL             | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up/pull-down.                                            |  |  |  |

|                                                                      | T1G      | ST              | —              | Timer1 gate.                                                                                                                                           |  |  |  |

|                                                                      | OSC2     |                 | XTAL           | XTAL connection.                                                                                                                                       |  |  |  |

|                                                                      | CLKOUT   | _               | CMOS           | Tosc reference clock.                                                                                                                                  |  |  |  |

| RA5/T1CKI/OSC1/CLKIN                                                 | RA5      | TTL             | CMOS           | General purpose I/O. Individually controlled interrupt-on-change<br>Individually enabled pull-up/pull-down.                                            |  |  |  |

|                                                                      | T1CKI    | ST              | _              | Timer1 clock.                                                                                                                                          |  |  |  |

|                                                                      | OSC1     | XTAL            | _              | XTAL connection.                                                                                                                                       |  |  |  |

|                                                                      | CLKIN    | ST              | _              | Tosc/4 reference clock.                                                                                                                                |  |  |  |

| RC0/C2IN+                                                            | RC0      | TTL             | CMOS           | General purpose I/O.                                                                                                                                   |  |  |  |

|                                                                      | C2IN+    | AN              | _              | Comparator1 input – positive.                                                                                                                          |  |  |  |

| RC1/C2IN-/CS                                                         | RC1      | TTL             | CMOS           | General purpose I/O.                                                                                                                                   |  |  |  |

|                                                                      | C2IN-    | AN              |                | Comparator1 input – negative.                                                                                                                          |  |  |  |

|                                                                      | CS       | TTL             | —              | Chip select input for SPI communication with internal pull-up resistor.                                                                                |  |  |  |

| RC2/SCLK/ALERT                                                       | RC2      | TTL             | CMOS           | General purpose I/O.                                                                                                                                   |  |  |  |

|                                                                      | SCLK     | TTL             | —              | Digital clock input for SPI communication.                                                                                                             |  |  |  |

|                                                                      | ALERT    |                 | OD             | Output with internal pull-up resistor for AFE error signal.                                                                                            |  |  |  |

| Legend: AN = Analog input<br>HV = High Voltage<br>TTL = TTL compatil |          | CM<br>ST<br>XTA | = Sch          | OS compatible input or output D = Direct<br>mitt Trigger input with CMOS levels OD = Open Drain<br>stal                                                |  |  |  |

| Indirect addr. <sup>(1)</sup><br>TMR0 | Address<br>00h |                               | Address    |                       | Address |          | A -I -I |

|---------------------------------------|----------------|-------------------------------|------------|-----------------------|---------|----------|---------|

| TMR0                                  | 00h            |                               |            |                       |         |          | Addres  |

|                                       |                | Indirect addr. <sup>(1)</sup> | 80h        | Accesses              | 100h    | Accesses | 180h    |

| DCI                                   | 01h            | OPTION_REG                    | 81h        | 00h-0Bh               | 101h    | 80h-8Bh  | 181h    |

| FCL                                   | 02h            | PCL                           | 82h        |                       | 102h    |          | 182h    |

| STATUS                                | 03h            | STATUS                        | 83h        |                       | 103h    |          | 183h    |

| FSR                                   | 04h            | FSR                           | 84h        |                       | 104h    |          | 184h    |

| GPIO                                  | 05h            | TRISIO                        | 85h        |                       | 105h    |          | 185h    |

|                                       | 06h            |                               | 86h        |                       | 106h    |          | 186h    |

|                                       | 07h            |                               | 87h        |                       | 107h    |          | 187h    |

|                                       | 08h            |                               | 88h        |                       | 108h    |          | 188h    |

|                                       | 09h            |                               | 89h        |                       | 109h    |          | 189h    |

| PCLATH                                | 0Ah            | PCLATH                        | 8Ah        |                       | 10Ah    |          | 18Ah    |

| INTCON                                | 0Bh            | INTCON                        | 8Bh        |                       | 10Bh    |          | 18Bh    |

| PIR1                                  | 0Ch            | PIE1                          | 8Ch        |                       | 10Ch    |          | 18Ch    |

|                                       | 0Dh            |                               | 8Dh        |                       | 10Dh    |          | 18Dh    |

| TMR1L                                 | 0Eh            | PCON                          | 8Eh        |                       | 10Eh    |          | 18Eh    |

| TMR1H                                 | 0Fh            | OSCCON                        | 8Fh        |                       | 10Fh    |          | 18Fh    |

| T1CON                                 | 10h            | OSCTUNE                       | 90h        | CRCON                 | 110h    |          | 190h    |

|                                       | 11h            |                               | 91h        | CRDAT0 <sup>(2)</sup> | 111h    |          | 191h    |

|                                       | 12h            |                               | 92h        | CRDAT1 <sup>(2)</sup> | 112h    |          | 192h    |

|                                       | 13h            |                               | 93h        | CRDAT2 <sup>(2)</sup> | 113h    |          | 193h    |

|                                       | 14h            | LVDCON                        | 94h        | CRDAT3 <sup>(2)</sup> | 114h    |          | 194h    |

|                                       | 15h            | WPUDA                         | 95h        |                       | 115h    |          | 195h    |

|                                       | 16h            | IOCA                          | 96h        |                       | 116h    |          | 196h    |

|                                       | 17h            | WDA                           | 97h        |                       | 117h    |          | 197h    |

|                                       | 18h            | , TIDA                        | 98h        |                       | 118h    |          | 198h    |

|                                       | 19h            | VRCON                         | 99h        |                       | 119h    |          | 199h    |

|                                       | 1Ah            | EEDAT                         | 9Ah        |                       | 11Ah    |          | 19Ah    |

|                                       | 1Bh            | EEADR                         | 9Bh        |                       | 11Bh    |          | 19Bh    |

|                                       | 1Ch            | EECON1                        | 9Ch        |                       | 11Ch    |          | 19Ch    |

|                                       | 1Dh            | EECON2 <sup>(1)</sup>         | 9Dh        |                       | 11Dh    |          | 19Dh    |

|                                       | 1Eh            | ELCONZ                        | 9Eh        |                       | 11Eh    |          | 19Eh    |

|                                       | 1En<br>1Fh     |                               | 9En<br>9Fh |                       | 11Fh    |          | 19En    |

|                                       |                |                               | 4 4        |                       | _       |          | 1A0h    |

|                                       | 20h            |                               | A0h        |                       | 120h    |          | TAUN    |

|                                       | 3Fh            |                               |            |                       |         |          |         |

| General                               | 40h            |                               |            |                       |         |          |         |

| Purpose                               |                |                               |            |                       |         |          |         |

| Register                              |                |                               | EFh        | _                     | 16Fh    |          | 1EFh    |

| 64 Bytes                              |                | Accesses                      | F0h        | Accesses              | 170h    | Accesses | 1F0h    |

|                                       | 7Fh            | 70h-7Fh                       | FFh        | 70h-7Fh               | 17Fh    | Bank 0   | 1FFh    |

| Bank 0                                |                | Bank 1                        |            | Bank 2                |         | Bank 3   |         |

PIC12F635 SPECIAL FUNCTION REGISTERS

FIGURE 2-3:

# 2: CRDAT<3:0> registers are KEELOQ® hardware peripheral related registers and require the execution of the

"KEELOQ® Encoder License Agreement" regarding implementation of the module and access to related registers. The "KEELOQ® Encoder License Agreement" may be accessed through the Microchip web site located at <u>www.microchip.com/KEELOQ</u> or by contacting your local Microchip Sales Representative.

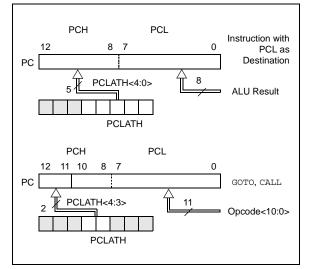

# 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-5 shows the two situations for the loading of the PC. The upper example in Figure 2-5 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-5 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 2-5: LOADING OF PC IN DIFFERENT SITUATIONS

#### 2.3.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<12:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper 5 bits to the PCLATH register. When the lower 8 bits are written to the PCL register, all 13 bits of the program counter will change to the values contained in the PCLATH register.

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). Care should be exercised when jumping into a look-up table or program branch table (computed GOTO) by modifying the PCL register. Assuming that PCLATH is set to the table start address, if the table length is greater than 255 instructions or if the lower 8 bits of the memory address rolls over from 0xFF to 0x00 in the middle of the table, then PCLATH must be incremented for each address rollover that occurs between the table beginning and the target location within the table.

For more information refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

### 2.3.2 STACK

The PIC12F635/PIC16F636/639 family has an 8-level x 13-bit wide hardware stack (see Figure 2-1). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

| Note 1: | There are no Status bits to indicate stack |

|---------|--------------------------------------------|

|         | overflow or stack underflow conditions.    |

2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

# 2.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR and the IRP bit of the STATUS register, as shown in Figure 2-6.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 2-1.

| EXAMPL   | E 2-1: | INDIRECT ADDRESSING |                      |  |  |  |

|----------|--------|---------------------|----------------------|--|--|--|

|          | MOVLW  | 0x20                | ;initialize pointer  |  |  |  |

|          | MOVWF  | FSR                 | ;to RAM              |  |  |  |

| NEXT     | CLRF   | INDF                | ;clear INDF register |  |  |  |

|          | INCF   | FSR                 | ; INC POINTER        |  |  |  |

|          | BTFSS  | FSR,4               | ;all done?           |  |  |  |

|          | GOTO   | NEXT                | ;no clear next       |  |  |  |

| CONTINUE |        |                     | ;yes continue        |  |  |  |

| R/W-1        | R/W-1        | R/W-1                                                | R/W-1           | R/W-1            | R/W-1           | R/W-1           | R/W-1 |  |  |  |

|--------------|--------------|------------------------------------------------------|-----------------|------------------|-----------------|-----------------|-------|--|--|--|

| RAPU         | INTEDG       | TOCS                                                 | TOSE            | PSA              | PS2             | PS1             | PS0   |  |  |  |

| bit 7        |              |                                                      |                 | •<br>•           |                 |                 | bit   |  |  |  |

|              |              |                                                      |                 |                  |                 |                 |       |  |  |  |

| Legend:      |              |                                                      |                 |                  |                 |                 |       |  |  |  |

| R = Readab   | ole bit      | W = Writable                                         | bit             | U = Unimpler     | nented bit, rea | ad as '0'       |       |  |  |  |

| -n = Value a | t POR        | '1' = Bit is se                                      | t               | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |  |  |  |

|              |              |                                                      |                 |                  |                 |                 |       |  |  |  |

| bit 7        | RAPU: POR    | TA Pull-up Ena                                       | ble bit         |                  |                 |                 |       |  |  |  |

|              |              | pull-ups are dis                                     |                 |                  |                 |                 |       |  |  |  |

|              |              | pull-ups are ena                                     | -               | dual PORT late   | ch values       |                 |       |  |  |  |

| bit 6        |              | errupt Edge Se                                       |                 |                  |                 |                 |       |  |  |  |

|              |              | on rising edge                                       |                 |                  |                 |                 |       |  |  |  |

|              | •            | on falling edge                                      | -               |                  |                 |                 |       |  |  |  |

| bit 5        |              | 0 Clock Source                                       |                 |                  |                 |                 |       |  |  |  |

|              |              | 1 = Transition on T0CKI pin                          |                 |                  |                 |                 |       |  |  |  |

|              | 0 = Internal | instruction cycle                                    | e clock (Fosc/  | 4)               |                 |                 |       |  |  |  |

| bit 4        | TOSE: TMR    | OSE: TMR0 Source Edge Select bit                     |                 |                  |                 |                 |       |  |  |  |

|              |              | 1 = Increment on high-to-low transition on T0CKI pin |                 |                  |                 |                 |       |  |  |  |

|              | 0 = Increme  | nt on low-to-hig                                     | h transition on | n T0CKI pin      |                 |                 |       |  |  |  |

| bit 3        | PSA: Presca  | aler Assignmen <sup>.</sup>                          | t bit           |                  |                 |                 |       |  |  |  |

|              |              | er is assigned to                                    |                 |                  |                 |                 |       |  |  |  |

|              | 0 = Prescale | er is assigned to                                    | the Timer0 m    | nodule           |                 |                 |       |  |  |  |

| bit 2-0      | PS<2:0>: Pi  | rescaler Rate S                                      | elect bits      |                  |                 |                 |       |  |  |  |

|              | BI           | T VALUE TMR0 R                                       | ATE WDT RA      | TE               |                 |                 |       |  |  |  |

|              |              | 000 1:2                                              | 1:1             |                  |                 |                 |       |  |  |  |

|              |              | 001 1:4                                              |                 |                  |                 |                 |       |  |  |  |

|              |              | 010 1:8                                              |                 |                  |                 |                 |       |  |  |  |

|              |              | 011 1 : 1<br>100 1 : 3                               |                 |                  |                 |                 |       |  |  |  |

|              |              | 100 1:3                                              |                 |                  |                 |                 |       |  |  |  |

|              |              | 110 1 : 12                                           |                 |                  |                 |                 |       |  |  |  |

|              |              | 111 1:2                                              |                 | 5                |                 |                 |       |  |  |  |

#### **REGISTER 5-1: OPTION\_REG: OPTION REGISTER**

Note 1: A dedicated 16-bit WDT postscaler is available. See Section 12.11 "Watchdog Timer (WDT)" for more information.

#### TABLE 5-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

| Name       | Bit 7    | Bit 6      | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|----------|------------|--------|--------|--------|--------|--------|--------|-----------------------|---------------------------------|

| TMR0       | Timer0 N | /lodule Re | gister |        |        |        |        |        | xxxx xxxx             | uuuu uuuu                       |

| INTCON     | GIE      | PEIE       | TOIE   | INTE   | RAIE   | TOIF   | INTF   | RAIF   | 0000 000x             | 0000 000x                       |

| OPTION_REG | RAPU     | INTEDG     | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111             | 1111 1111                       |

| TRISA      | _        | —          | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111               | 11 1111                         |

**Legend:** – = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Timer0 module.

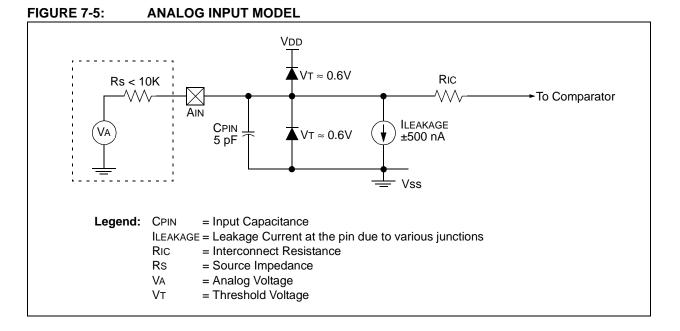

### 7.2 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 7-5. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSs. The analog input, therefore, must be between VSs and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

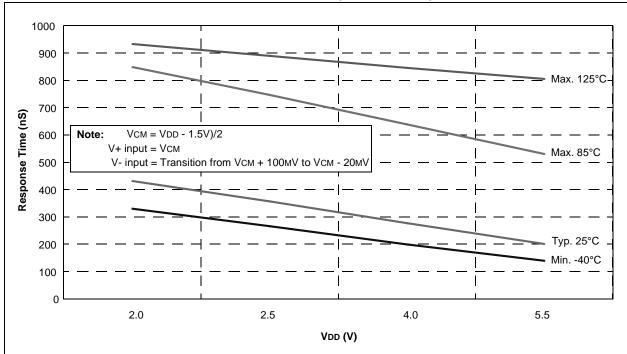

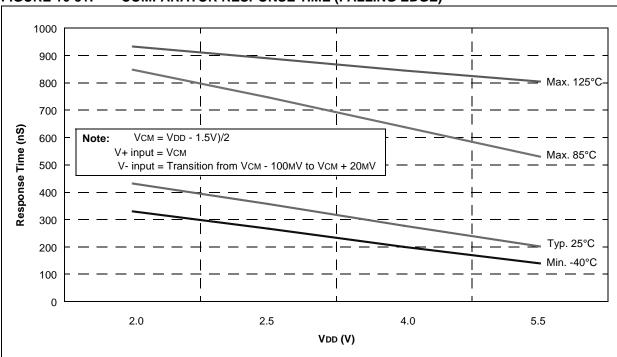

#### 7.5 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Specifications in **Section 15.0 "Electrical Specifications"** for more details.

#### 7.6 Comparator Interrupt Operation

The comparator interrupt flag is set whenever there is a change in the output value of the comparator. Changes are recognized by means of a mismatch circuit which consists of two latches and an exclusive-or gate (see Figures 7-8 and 7-9). One latch is updated with the comparator output level when the CMCON0 register is read. This latch retains the value until the next read of the CMCON0 register or the occurrence of a Reset. The other latch of the mismatch circuit is updated on every Q1 system clock. A mismatch condition will occur when a comparator output change is clocked through the second latch on the Q1 clock cycle. The mismatch condition will persist, holding the CxIF bit of the PIR1 register true, until either the CMCON0 register is read or the comparator output returns to the previous state.

| Note: | A write operation to the CMCON0 register |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|

|       | will also clear the mismatch condition   |  |  |  |  |  |  |  |

|       | because all writes include a read        |  |  |  |  |  |  |  |

|       | operation at the beginning of the write  |  |  |  |  |  |  |  |

|       | cycle.                                   |  |  |  |  |  |  |  |

Software will need to maintain information about the status of the comparator output to determine the actual change that has occurred.

The CxIF bit of the PIR1 register, is the comparator interrupt flag. This bit must be reset in software by clearing it to '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CxIE bit of the PIE1 register and the PEIE and GIE bits of the INTCON register must all be set to enable comparator interrupts. If any of these bits are cleared, the interrupt is not enabled, although the CxIF bit of the PIR1 register will still be set if an interrupt condition occurs.

The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON0. This will end the mismatch condition. See Figures 7-8 and 7-9.

- b) Clear the CxIF interrupt flag.

A persistent mismatch condition will preclude clearing the CxIF interrupt flag. Reading CMCON0 will end the mismatch condition and allow the CxIF bit to be cleared.

Note: If a change in the CMCON0 register (CxOUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CxIF interrupt flag may not get set.

| R-0           | R-0                                                                  | R/W-0                              | R/W-0          | R/W-0            | R/W-0           | R/W-0          | R/W-0 |  |  |  |  |

|---------------|----------------------------------------------------------------------|------------------------------------|----------------|------------------|-----------------|----------------|-------|--|--|--|--|

| C2OUT         | C1OUT                                                                | C2INV                              | C1INV          | CIS              | CM2             | CM1            | CM0   |  |  |  |  |

| bit 7         |                                                                      |                                    |                |                  |                 |                | bit 0 |  |  |  |  |

|               |                                                                      |                                    |                |                  |                 |                |       |  |  |  |  |

| Legend:       |                                                                      |                                    |                |                  |                 |                |       |  |  |  |  |

| R = Readable  | e bit                                                                | W = Writable                       | bit            | U = Unimpler     | mented bit, rea | d as '0'       |       |  |  |  |  |

| -n = Value at | POR                                                                  | '1' = Bit is set                   |                | '0' = Bit is cle | eared           | x = Bit is unk | nown  |  |  |  |  |

|               |                                                                      |                                    |                |                  |                 |                |       |  |  |  |  |

| bit 7         |                                                                      | parator 2 Outp                     | ut bit         |                  |                 |                |       |  |  |  |  |

|               | When C2INV                                                           |                                    |                |                  |                 |                |       |  |  |  |  |

|               | 1 = C2 VIN+ ><br>0 = C2 VIN+ <                                       |                                    |                |                  |                 |                |       |  |  |  |  |

|               | When C2INV                                                           | -                                  |                |                  |                 |                |       |  |  |  |  |

|               | 1 = C2 VIN+ <                                                        |                                    |                |                  |                 |                |       |  |  |  |  |

|               | 0 = C2 VIN+ >                                                        |                                    |                |                  |                 |                |       |  |  |  |  |

| bit 6         | C1OUT: Com                                                           | parator 1 Outp                     | ut bit         |                  |                 |                |       |  |  |  |  |

|               | When C1INV                                                           | = 0:                               |                |                  |                 |                |       |  |  |  |  |

|               | 1 = C1 VIN+ >                                                        |                                    |                |                  |                 |                |       |  |  |  |  |

|               |                                                                      | 0 = C1 VIN + < C1 VIN -            |                |                  |                 |                |       |  |  |  |  |

|               | $\frac{\text{When C1INV} = 1:}{1 = \text{C1 Vin} + < \text{C1 Vin}}$ |                                    |                |                  |                 |                |       |  |  |  |  |

|               | 1 = C1 VIN+ < 0 = C1 VIN+ > 0                                        |                                    |                |                  |                 |                |       |  |  |  |  |

| bit 5         |                                                                      | -                                  | t Inversion bi | t                |                 |                |       |  |  |  |  |

| 2.1.0         | C2INV: Comparator 2 Output Inversion bit<br>1 = C2 output inverted   |                                    |                |                  |                 |                |       |  |  |  |  |

|               | 0 = C2 output                                                        |                                    |                |                  |                 |                |       |  |  |  |  |

| bit 4         | C1INV: Comp                                                          | parator 1 Outpu                    | t Inversion bi | t                |                 |                |       |  |  |  |  |

|               | 1 = C1 Outpu                                                         |                                    |                |                  |                 |                |       |  |  |  |  |

|               | 0 = C1 Outpu                                                         | it not inverted                    |                |                  |                 |                |       |  |  |  |  |

| bit 3         | -                                                                    | ator Input Swite                   | ch bit         |                  |                 |                |       |  |  |  |  |

|               | When CM<2:                                                           |                                    |                |                  |                 |                |       |  |  |  |  |

|               |                                                                      | nnects to C1 V                     |                |                  |                 |                |       |  |  |  |  |

|               |                                                                      | onnects to C2 V<br>nnects to C1 VI |                |                  |                 |                |       |  |  |  |  |

|               |                                                                      | nnects to C2 V                     |                |                  |                 |                |       |  |  |  |  |

|               | When CM<2:                                                           |                                    |                |                  |                 |                |       |  |  |  |  |

|               |                                                                      | nnects to C1 V                     |                |                  |                 |                |       |  |  |  |  |

|               |                                                                      | nnects to C1 VI                    |                | 7 5)             |                 |                |       |  |  |  |  |

| bit 2-0       |                                                                      | mparator Mode                      |                |                  | la a            |                |       |  |  |  |  |

|               |                                                                      | inputs multiple                    |                | nfigured as anal | log             |                |       |  |  |  |  |

|               |                                                                      | puts multiplexe                    |                | •                |                 |                |       |  |  |  |  |

|               | 011 = Two co                                                         | ommon referen                      | ce comparato   |                  |                 |                |       |  |  |  |  |

|               |                                                                      | dependent com                      | •              |                  |                 |                |       |  |  |  |  |

|               |                                                                      | dependent con                      |                | common refere    | ence            |                |       |  |  |  |  |

|               |                                                                      |                                    |                | figured as digit |                 |                |       |  |  |  |  |

|               |                                                                      |                                    | 1              | <u>.</u>         |                 |                |       |  |  |  |  |

### REGISTER 7-2: CMCON0: COMPARATOR CONFIGURATION REGISTER (PIC16F636/639)

# TABLE 11-1:TYPICAL OUTPUT ENABLEFILTER TIMING

| OEH<br><1:0> | OEL<br><1:0> | Тоен<br>(ms) | TOEL<br>(ms)  | Toet<br>(ms) |  |  |  |  |  |  |

|--------------|--------------|--------------|---------------|--------------|--|--|--|--|--|--|

| 01           | 00           | 1            | 1             | 3            |  |  |  |  |  |  |

| 01           | 01           | 1            | 1             | 3            |  |  |  |  |  |  |

| 01           | 10           | 1            | 2             | 4            |  |  |  |  |  |  |

| 01           | 11           | 1            | 4             | 6            |  |  |  |  |  |  |

|              |              |              |               |              |  |  |  |  |  |  |

| 10           | 00           | 2            | 1             | 4            |  |  |  |  |  |  |

| 10           | 01           | 2            | 1             | 4            |  |  |  |  |  |  |

| 10           | 10           | 2            | 2             | 5            |  |  |  |  |  |  |

| 10           | 11           | 2            | 4             | 8            |  |  |  |  |  |  |

|              | •            | •            | •             | •            |  |  |  |  |  |  |

| 11           | 00           | 4            | 1             | 6            |  |  |  |  |  |  |

| 11           | 01           | 4            | 1             | 6            |  |  |  |  |  |  |

| 11           | 10           | 4            | 2             | 8            |  |  |  |  |  |  |

| 11           | 11           | 4            | 4             | 10           |  |  |  |  |  |  |

|              |              |              |               |              |  |  |  |  |  |  |

| 00           | XX           | F            | ilter Disable | ed           |  |  |  |  |  |  |

**Note 1:** Typical at room temperature and VDD = 3.0V, 32 kHz oscillator.

TOEH is measured from the rising edge of the demodulator output to the first falling edge. The pulse width must fall within TOEH  $\leq t \leq$  TOET.

TOEL is measured from the falling edge of the demodulator output to the rising edge of the next pulse. The pulse width must fall within TOEL  $\leq t \leq$  TOET.

TOET is measured from rising edge to the next rising edge (i.e., the sum of TOEH and TOEL). The pulse width must be  $t \leq$  TOET. If the Configuration Register 0 (Register 11-1), OEL<8:7> is set to '00', then TOEH must not exceed TOET and TOEL must not exceed TINACT.

The filter will reset, requiring a complete new successive high and low period to enable LFDATA, under the following conditions.

- The received high is not greater than the configured minimum TOEH value.

- During TOEH, a loss of signal > 56 μs. A loss of signal < 56 μs may or may not cause a filter Reset.

- The received low is not greater than the configured minimum TOEL value.

- The received sequence exceeds the maximum TOET value:

- TOEH + TOEL > TOET

- or TOEH > TOET

- or TOEL > TOET

- A Soft Reset SPI command is received.

If the filter resets due to a long high (TOEH > TOET), the high-pulse timer will not begin timing again until after a gap of TE and another low-to-high transition occurs on the demodulator output.

Disabling the output enable filter disables the TOEH and TOEL requirement and the AFE passes all received LF data. See Figure 11-10, Figure 11-11 and Figure 11-12 for examples.

When viewed from an application perspective, from the pin input, the actual output enable filter timing must factor in the analog delays in the input path (such as demodulator charge and discharge times).

- TOEH TDR + TDF

- TOEL + TDR TDF

The output enable filter starts immediately after TgAP, the gap after AGC stabilization period.

# 11.16 Input Sensitivity Control

The AFE is designed to have typical input sensitivity of 3 mVPP. This means any input signal with amplitude greater than 3 mVPP can be detected. The AFE's internal AGC loop regulates the detecting signal amplitude when the input level is greater than approximately 20 mVPP. This signal amplitude is called "AGC-active level". The AGC loop regulates the input voltage so that the input signal amplitude range will be kept within the linear range of the detection circuits without saturation. The AGC Active Status bit AGCACT<5>, in the AFE Status Register 7 (Register 11-8) is set if the AGC loop regulates the input voltage.

Table 11-2 shows the input sensitivity comparison when the AGCSIG option is used. When AGCSIG option bit is set, the demodulated output is available only when the AGC loop is active (see Table 11-1). The AFE has also input sensitivity reduction options per each channel. The Configuration Register 3 (Register 11-4), Configuration Register 4 (Register 11-5) and Configuration Register 5 (Register 11-6) have the option to reduce the channel gains from 0 dB to approximately -30 dB.

### REGISTER 11-2: CONFIGURATION REGISTER 1

| R/W-0        | R/W-0                                      | R/W-0                                                   | R/W-0          | R/W-0           | R/W-0          | R/W-0              | R/W-0           | R/W-0        |

|--------------|--------------------------------------------|---------------------------------------------------------|----------------|-----------------|----------------|--------------------|-----------------|--------------|

| DATOUT1      | DATOUT0                                    | LCXTUN5                                                 | LCXTUN4        | LCXTUN3         | LCXTUN2        | LCXTUN1            | LCXTUN0         | R1PAR        |

| bit 8        |                                            |                                                         |                |                 |                |                    |                 | bit 0        |

|              |                                            |                                                         |                |                 |                |                    |                 |              |

| Legend:      |                                            |                                                         |                |                 |                |                    |                 |              |

| R = Readab   | le bit                                     | W = Writable                                            | e bit          | U = Unimple     | mented bit, r  | ead as '0'         |                 |              |

| -n = Value a | ue at POR '1' = Bit is set                 |                                                         | et             | '0' = Bit is cl | eared          | x = Bit is unknown |                 |              |

|              | 01 = Carrier<br>10 = RSSI o<br>11 = RSSI o | output                                                  |                |                 |                |                    |                 |              |

| bit 6-1      |                                            | : <b>0&gt;:</b> LCX Tun<br>0 pF (Default)<br>:<br>63 pF | 0 1            | nce bit         |                |                    |                 |              |

| bit 0        | R1PAR: Reg<br>bits                         | gister Parity B                                         | it – set/clear | ed so the 9-bi  | t register con | tains odd pari     | ity – an odd nι | umber of set |

#### **REGISTER 11-3: CONFIGURATION REGISTER 2**

| R/W-0   | R/W-0  | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0 |

|---------|--------|---------|---------|---------|---------|---------|---------|-------|

| RSSIFET | CLKDIV | LCYTUN5 | LCYTUN4 | LCYTUN3 | LCYTUN2 | LCYTUN1 | LCYTUN0 | R2PAR |

| bit 8   |        |         |         |         |         |         |         | bit 0 |

| Legend:           |                                                                                   |                                                                    |                             |                                    |           |  |  |  |

|-------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------|------------------------------------|-----------|--|--|--|

| R = Read          | able bit                                                                          | W = Writable bit                                                   | U = Unimplemented b         | U = Unimplemented bit, read as '0' |           |  |  |  |

| -n = Value at POR |                                                                                   | '1' = Bit is set                                                   | '0' = Bit is cleared        | x = Bit is unknown                 |           |  |  |  |

| bit 8             | 1 = Pull-                                                                         | Pull-down MOSFET on<br>down RSSI MOSFET on<br>down RSSI MOSFET off | LFDATA pad bit (controllab  | le by user in the RSSI mode only)  |           |  |  |  |

| bit 7             | CLKDIV: Carrier Clock Divide-by bit<br>1 = Carrier Clock/4<br>0 = Carrier Clock/1 |                                                                    |                             |                                    |           |  |  |  |

| bit 6-1           |                                                                                   | <5:0>: LCY Tuning Capa<br>= +0 pF (Default)<br>:<br>= +63 pF       | citance bit                 |                                    |           |  |  |  |

| bit 0             |                                                                                   | l.                                                                 | eared so the 9-bit register | contains odd parity – an odd numbe | er of set |  |  |  |

### 12.2 Reset

The PIC12F635/PIC16F636/639 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) Wake-up Reset (WUR)

- c) WDT Reset during normal operation

- d) WDT Reset during Sleep

- e) MCLR Reset during normal operation

- f) MCLR Reset during Sleep

- g) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- Power-on Reset

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

- Brown-out Reset

They are not affected by a WDT wake-up since this is viewed as the resumption of normal operation. TO and  $\overline{PD}$  bits are set or cleared differently in different Reset situations, as indicated in Table 12-3. These bits are used in software to determine the nature of the Reset. See Table 12-4 for a full description of Reset states of all registers.

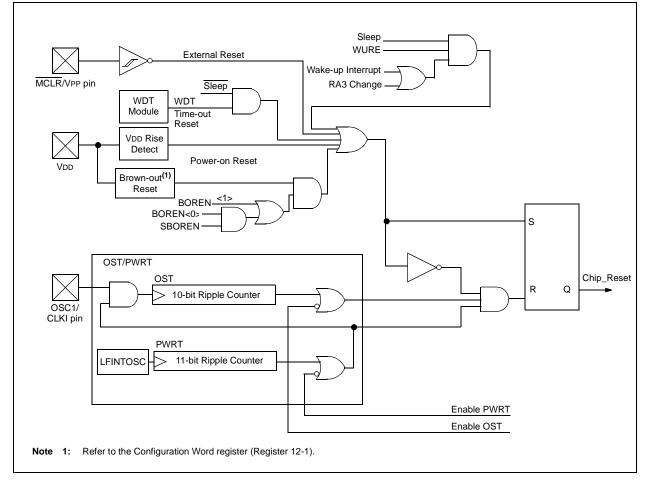

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 12-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See **Section 15.0** "**Electrical Specifications**" for pulse width specifications.

#### FIGURE 12-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### FIGURE 12-10: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| ; Q1  Q2  Q3  Q4; Q1  Q2 Q3  Q4<br>OSC1 //////////////////////////////////// | Q1                                      |              | Q1 Q2 Q3 Q4                | Q1   Q2   Q3   Q4  <br> / | Q1 Q2 Q3 Q4; |

|------------------------------------------------------------------------------|-----------------------------------------|--------------|----------------------------|---------------------------|--------------|

| CLKOUT <sup>(4)</sup>                                                        | Tost <sup>(2)</sup>                     |              |                            | \                         |              |

| INT pin                                                                      |                                         |              | 1                          |                           |              |

| INTF Flag<br>(INTCON<1>)                                                     |                                         | Interr       | upt Latency <sup>(3)</sup> |                           |              |

| GIE bit<br>(INTCON<7>)                                                       | Processor in<br>Sleep                   |              | <u>.</u>                   |                           |              |

| INSTRUCTION FLOW                                                             | :                                       | <br>         | 1<br>1<br>1.               |                           |              |

| PC X PC X PC+1                                                               | X PC + 2                                | X PC + 2     | PC+2                       | <u> </u>                  | 0005h        |

| Instruction [ Inst(PC) = Sleep Inst(PC + 1)                                  | 1<br>1<br>1                             | Inst(PC + 2) | I I I                      | Inst(0004h)               | Inst(0005h)  |

| Instruction [ Inst(PC – 1) Sleep                                             | 1 I I I I I I I I I I I I I I I I I I I | Inst(PC + 1) | Dummy Cycle                | Dummy Cycle               | Inst(0004h)  |

| Note 1: XT. HS or LP Oscillator mode assum                                   | ed.                                     |              |                            |                           |              |

- 2: TOST = 1024 TOSC (drawing not to scale). This delay does not apply to EC and RC Oscillator modes.

- 3: GIE = 1 assumed. In this case after wake-up, the processor jumps to 0004h. If GIE = 0, execution will continue in-line.

- 4: CLKOUT is not available in XT, HS, LP or EC Oscillator modes, but shown here for timing reference.

#### 12.13 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out using ICSP for verification purposes.

| Note: | The entire data EEPROM and Flash pro-  |

|-------|----------------------------------------|

|       | gram memory will be erased when the    |

|       | code protection is turned off. See the |

|       | "PIC12F6XX/16F6XX Memory Program-      |

|       | ming Specification" (DS41204) for more |

|       | information.                           |

### 12.14 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable during Program/Verify mode. Only the Least Significant 7 bits of the ID locations are used.

#### 14.7 MPLAB ICE 2000 High-Performance In-Circuit Emulator

The MPLAB ICE 2000 In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers. Software control of the MPLAB ICE 2000 In-Circuit Emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The architecture of the MPLAB ICE 2000 In-Circuit Emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE 2000 In-Circuit Emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows<sup>®</sup> 32-bit operating system were chosen to best make these features available in a simple, unified application.

#### 14.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC<sup>®</sup> and MCU devices. It debugs and programs PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The MPLAB REAL ICE probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with the popular MPLAB ICD 2 system (RJ11) or with the new high speed, noise tolerant, lowvoltage differential signal (LVDS) interconnection (CAT5).

MPLAB REAL ICE is field upgradeable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added, such as software breakpoints and assembly code trace. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, real-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 14.9 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low-cost, run-time development tool, connecting to the host PC via an RS-232 or high-speed USB interface. This tool is based on the Flash PIC MCUs and can be used to develop for these and other PIC MCUs and dsPIC DSCs. The MPLAB ICD 2 utilizes the in-circuit debugging capability built into the Flash devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers costeffective, in-circuit Flash debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, single stepping and watching variables, and CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real time. MPLAB ICD 2 also serves as a development programmer for selected PIC devices.

### 14.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an SD/MMC card for file storage and secure data applications.

# 15.3 DC Characteristics: PIC12F635/PIC16F636-E (Extended) (Continued)

| DC CHA | RACTER | ISTICS                 |     | ing tempo |       |       |     | otherwise stated)<br>125°C for extended |

|--------|--------|------------------------|-----|-----------|-------|-------|-----|-----------------------------------------|

| Param  | 0      | Device Oberneteristics | Min | Turt      | Maria | Unite |     | Conditions                              |

| No.    | Sym    | Device Characteristics | Min | Тур†      | Max   | Units | Vdd | Note                                    |

| D020   | IPD    | Power-down Base        |     | 0.15      | 1.2   | μA    | 2.0 | WDT, BOR, Comparators,                  |

|        |        | Current <sup>(4)</sup> | —   | 0.20      | 1.5   | μA    | 3.0 | VREF and T1OSC disabled                 |

|        |        |                        | _   | 0.35      | 1.8   | μA    | 5.0 |                                         |

| D021   |        |                        | —   | 1.0       | 17.5  | μA    | 2.0 | WDT Current <sup>(1)</sup>              |

|        |        |                        | —   | 2.0       | 19    | μA    | 3.0 |                                         |

|        |        |                        | —   | 3.0       | 22    | μA    | 5.0 |                                         |

| D022A  |        |                        | —   | 42        | 60    | μA    | 3.0 | BOR Current <sup>(1)</sup>              |

|        |        |                        | —   | 85        | 122   | μA    | 5.0 |                                         |

| D022B  |        |                        | -   | 22        | 48    | μA    | 2.0 | PLVD Current                            |

|        |        |                        | —   | 25        | 55    | μΑ    | 3.0 |                                         |

|        |        |                        | —   | 33        | 65    | μA    | 5.0 |                                         |

| D023   |        |                        |     | 32.3      | 45    | μΑ    | 2.0 | Comparator Current <sup>(1)</sup>       |

|        |        |                        | —   | 60        | 78    | μA    | 3.0 |                                         |

|        |        |                        | —   | 120       | 160   | μA    | 5.0 |                                         |

| D024A  |        |                        |     | 30        | 36    | μA    | 2.0 | CVREF Current <sup>(1)</sup>            |

|        |        |                        | —   | 45        | 55    | μA    | 3.0 | (high-range)                            |

|        |        |                        | —   | 75        | 95    | μA    | 5.0 |                                         |

| D024B  |        |                        | _   | 39        | 47    | μA    | 2.0 | CVREF Current <sup>(1)</sup>            |

|        |        |                        | —   | 59        | 72    | μA    | 3.0 | (low-range)                             |

|        |        |                        | —   | 98        | 124   | μA    | 5.0 |                                         |

| D025   |        |                        | —   | 4.5       | 25    | μA    | 2.0 | T1OSC Current <sup>(3)</sup>            |

|        |        |                        | —   | 5.0       | 30    | μA    | 3.0 |                                         |

|        |        |                        | —   | 6.0       | 40    | μA    | 5.0 |                                         |

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in Active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

- 3: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

- 4: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

#### 15.4 DC Characteristics: PIC12F635/PIC16F636-I (Industrial) PIC12F635/PIC16F636-E (Extended) (Continued)

| DC CH        | ARACTE | RISTICS                                                             | Standard Operating temport |      | -40°C | $\leq$ TA $\leq$ + | o <b>therwise stated)</b><br>-85°C for industrial<br>-125°C for extended |

|--------------|--------|---------------------------------------------------------------------|----------------------------|------|-------|--------------------|--------------------------------------------------------------------------|

| Param<br>No. | Sym    | Characteristic                                                      | Min                        | Тур† | Max   | Units              | Conditions                                                               |

|              | Voн    | Output High Voltage                                                 |                            |      |       |                    |                                                                          |

| D090         |        | I/O ports                                                           | Vdd - 0.7                  | —    | —     | V                  | IOH = -3.0 mA, VDD = 4.5V (Ind.)                                         |

| D092         |        | OSC2/CLKOUT (RC mode)                                               | Vdd - 0.7                  | _    | —     | V                  | IOH = -1.3 mA, VDD = 4.5V (Ind.)<br>IOH = -1.0 mA, VDD = 4.5V (Ext.)     |

| D100         | IULP   | Ultra Low-power Wake-up<br>Current                                  | _                          | 200  |       | nA                 |                                                                          |

|              |        | Capacitive Loading Specs<br>on Output Pins                          |                            |      |       |                    |                                                                          |

| D101         | COSC2  | OSC2 pin                                                            | _                          | _    | 15*   | pF                 | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1   |

| D101A        | Сю     | All I/O pins                                                        | _                          | —    | 50*   | pF                 |                                                                          |

|              |        | Data EEPROM Memory                                                  |                            |      |       |                    |                                                                          |

| D120         | ED     | Byte Endurance                                                      | 100K                       | 1M   | _     | E/W                | -40°C ≤ TA ≤ +85°C                                                       |

| D120A        | ED     | Byte Endurance                                                      | 10K                        | 100K | _     | E/W                | +85°C ≤ TA ≤ +125°C                                                      |

| D121         | Vdrw   | VDD for Read/Write                                                  | Vmin                       | _    | 5.5   | V                  | Using EECON1 to read/write<br>VMIN = Minimum operating<br>voltage        |

| D122         | TDEW   | Erase/Write cycle time                                              | _                          | 5    | 6     | ms                 |                                                                          |

| D123         | Tretd  | Characteristic Retention                                            | 40                         | _    | —     | Year               | Provided no other specifications are violated                            |

| D124         | Tref   | Number of Total Erase/Write<br>Cycles before Refresh <sup>(4)</sup> | 1M                         | 10M  | —     | E/W                | $-40^{\circ}C \le TA \le +85^{\circ}C$                                   |

|              |        | Program Flash Memory                                                |                            |      |       |                    |                                                                          |

| D130         | Eр     | Cell Endurance                                                      | 10K                        | 100K | —     | E/W                | $-40^{\circ}C \le TA \le +85^{\circ}C$                                   |

| D130A        | ED     | Cell Endurance                                                      | 1K                         | 10K  | —     | E/W                | $+85^{\circ}C \le TA \le +125^{\circ}C$                                  |