Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Operating Temperature  Mounting Type | -40°C ~ 125°C (TA) Surface Mount                                     |

|--------------------------------------|----------------------------------------------------------------------|

| Oscillator Type                      | Internal                                                             |

| Data Converters                      | A/D 30x10b                                                           |

| Voltage - Supply (Vcc/Vdd)           | 3V ~ 5.5V                                                            |

| RAM Size                             | 112K x 8                                                             |

| EEPROM Size                          | -                                                                    |

| Program Memory Type                  | FLASH                                                                |

| Program Memory Size                  | 1.6MB (1.6M x 8)                                                     |

| Number of I/O                        | 118                                                                  |

| Peripherals                          | I <sup>2</sup> S, POR, PWM, WDT                                      |

| Connectivity                         | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI |

| Speed                                | 100MHz                                                               |

| Core Size                            | 16-Bit                                                               |

| Core Processor                       | C166SV2                                                              |

| Product Status                       | Not For New Designs                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 4.7.1<br>4.7.2 | Testing Waveforms                                |     |

|----------------|--------------------------------------------------|-----|

| 4.7.2.1        | Phase Locked Loop (PLL)                          | 117 |

| 4.7.2.2        | Wakeup Clock 1                                   | 120 |

| 4.7.2.3        | Selecting and Changing the Operating Frequency 1 | 20  |

| 4.7.3          | External Clock Input Parameters                  | 121 |

| 4.7.4          | Pad Properties                                   | 123 |

| 4.7.5          | External Bus Timing                              | 27  |

| 4.7.5.1        | Bus Cycle Control with the READY Input           | 32  |

| 4.7.6          | Synchronous Serial Interface Timing              | 35  |

| 4.7.7          | Debug Interface Timing                           | 39  |

| 5              | Package and Reliability                          | 45  |

| 5.1            |                                                  | 145 |

| 5.2            | Thermal Considerations                           | 47  |

| 5.3            | Quality Declarations                             | 48  |

Table 5 Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.      | Туре | Function                                        |

|-----|-------------------|------------|------|-------------------------------------------------|

| 70  | P11.4             | O0 / I     | St/B | Bit 4 of Port 11, General Purpose Input/Output  |

|     | CCU61_CC6<br>2    | O1         | St/B | CCU61 Channel 2 Output                          |

|     | U3C1_DOUT         | O2         | St/B | USIC3 Channel 1 Shift Data Output               |

|     | RxDC5B            | I          | St/B | CAN Node 5 Receive Data Input                   |

|     | CCU61_CC6<br>2INB | I          | St/B | CCU61 Channel 2 Input                           |

|     | U3C1_DX0B         | I          | St/B | USIC3 Channel 1 Shift Data Input                |

| 71  | P12.10            | O0 / I     | St/B | Bit 10 of Port 12, General Purpose Input/Output |

|     | CC2_CC16          | O1         | St/B | CAPCOM2 Channel 16 Compare Output               |

|     | CCU63_COU<br>T62  | O2         | St/B | CCU63 Channel 2 Output                          |

|     | U4C0_DX1C         | I          | St/B | USIC4 Channel 0 Shift Clock Input               |

|     | U3C1_DX1C         | I          | St/B | USIC3 Channel 1 Shift Clock Input               |

| 72  | P2.2              | O0 / I     | St/B | Bit 2 of Port 2, General Purpose Input/Output   |

|     | TxDC1             | O1         | St/B | CAN Node 1 Transmit Data Output                 |

|     | CCU63_CC6<br>2    | O2         | St/B | CCU63 Channel 2 Output                          |

|     | AD15              | OH /<br>IH | St/B | External Bus Interface Address/Data Line 15     |

|     | CCU63_CC6<br>2INB | I          | St/B | CCU63 Channel 2 Input                           |

|     | ESR2_5            | I          | St/B | ESR2 Trigger Input 5                            |

| 73  | P11.3             | O0 / I     | St/B | Bit 3 of Port 11, General Purpose Input/Output  |

|     | CCU61_COU<br>T63  | O1         | St/B | CCU61 Channel 3 Output                          |

|     | CCU61_COU<br>T62  | O2         | St/B | CCU61 Channel 2 Output                          |

|     | TxDC5             | О3         | St/B | CAN Node 5 Transmit Data Input                  |

|     | CCU61_T13<br>HRF  | I          | St/B | External Run Control Input for T13 of CCU61     |

|     | U4C0_DX1A         | I          | St/B | USIC4 Channel 0 Shift Clock Input               |

Table 5 Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.      | Туре | Function                                       |

|-----|------------------|------------|------|------------------------------------------------|

| 123 | P10.5            | O0 / I     | St/B | Bit 5 of Port 10, General Purpose Input/Output |

|     | U0C1_SCLK<br>OUT | O1         | St/B | USIC0 Channel 1 Shift Clock Output             |

|     | CCU60_COU<br>T62 | O2         | St/B | CCU60 Channel 2 Output                         |

|     | U2C0_DOUT        | О3         | St/B | USIC2 Channel 0 Shift Data Output              |

|     | AD5              | OH /<br>IH | St/B | External Bus Interface Address/Data Line 5     |

|     | U0C1_DX1B        | I          | St/B | USIC0 Channel 1 Shift Clock Input              |

| 124 | P3.5             | O0 / I     | St/B | Bit 5 of Port 3, General Purpose Input/Output  |

|     | U2C1_SCLK<br>OUT | O1         | St/B | USIC2 Channel 1 Shift Clock Output             |

|     | U2C0_SELO<br>2   | O2         | St/B | USIC2 Channel 0 Select/Control 2 Output        |

|     | U0C0_SELO<br>5   | О3         | St/B | USIC0 Channel 0 Select/Control 5 Output        |

|     | U2C1_DX1A        | I          | St/B | USIC2 Channel 1 Shift Clock Input              |

| 125 | P0.6             | O0 / I     | St/B | Bit 6 of Port 0, General Purpose Input/Output  |

|     | U1C1_DOUT        | 01         | St/B | USIC1 Channel 1 Shift Data Output              |

|     | TxDC1            | O2         | St/B | CAN Node 1 Transmit Data Output                |

|     | CCU61_COU<br>T63 | О3         | St/B | CCU61 Channel 3 Output                         |

|     | A6               | ОН         | St/B | External Bus Interface Address Line 6          |

|     | U1C1_DX0A        | I          | St/B | USIC1 Channel 1 Shift Data Input               |

|     | CCU61_CTR<br>APA | I          | St/B | CCU61 Emergency Trap Input                     |

|     | U1C1_DX1B        | I          | St/B | USIC1 Channel 1 Shift Clock Input              |

Table 5 Pin Definitions and Functions (cont'd)

| I abit | 1 1111 00         |            | is and | i dilotions (cont d)                           |

|--------|-------------------|------------|--------|------------------------------------------------|

| Pin    | Symbol            | Ctrl.      | Туре   | Function                                       |

| 129    | P10.7             | O0 / I     | St/B   | Bit 7 of Port 10, General Purpose Input/Output |

|        | U0C1_DOUT         | 01         | St/B   | USIC0 Channel 1 Shift Data Output              |

|        | CCU60_COU<br>T63  | O2         | St/B   | CCU60 Channel 3 Output                         |

|        | AD7               | OH /<br>IH | St/B   | External Bus Interface Address/Data Line 7     |

|        | U0C1_DX0B         | I          | St/B   | USIC0 Channel 1 Shift Data Input               |

|        | CCU60_CCP<br>OS0A | I          | St/B   | CCU60 Position Input 0                         |

|        | RxDC4C            | I          | St/B   | CAN Node 4 Receive Data Input                  |

|        | T4INB             | I          | St/B   | GPT12E Timer T4 Count/Gate Input               |

| 130    | P0.7              | O0 / I     | St/B   | Bit 7 of Port 0, General Purpose Input/Output  |

|        | U1C1_DOUT         | 01         | St/B   | USIC1 Channel 1 Shift Data Output              |

|        | U1C0_SELO<br>3    | O2         | St/B   | USIC1 Channel 0 Select/Control 3 Output        |

|        | TxDC3             | О3         | St/B   | CAN Node 3 Transmit Data Output                |

|        | A7                | ОН         | St/B   | External Bus Interface Address Line 7          |

|        | U1C1_DX0B         | I          | St/B   | USIC1 Channel 1 Shift Data Input               |

|        | CCU61_CTR<br>APB  | I          | St/B   | CCU61 Emergency Trap Input                     |

| 131    | P3.7              | O0 / I     | St/B   | Bit 7 of Port 3, General Purpose Input/Output  |

|        | U2C1_DOUT         | 01         | St/B   | USIC2 Channel 1 Shift Data Output              |

|        | U2C0_SELO<br>3    | O2         | St/B   | USIC2 Channel 0 Select/Control 3 Output        |

|        | U0C0_SELO<br>7    | О3         | St/B   | USIC0 Channel 0 Select/Control 7 Output        |

|        | U2C1_DX0B         | I          | St/B   | USIC2 Channel 1 Shift Data Input               |

|        |                   |            | . —    |                                                |

Table 5 Pin Definitions and Functions (cont'd)

|     |                   | 1      |      |                                                |

|-----|-------------------|--------|------|------------------------------------------------|

| Pin | Symbol            | Ctrl.  | Туре | Function                                       |

| 151 | P1.3              | O0 / I | St/B | Bit 3 of Port 1, General Purpose Input/Output  |

|     | CCU62_COU<br>T63  | O1     | St/B | CCU62 Channel 3 Output                         |

|     | U1C0_SELO<br>7    | O2     | St/B | USIC1 Channel 0 Select/Control 7 Output        |

|     | U2C0_SELO<br>4    | О3     | St/B | USIC2 Channel 0 Select/Control 4 Output        |

|     | A11               | ОН     | St/B | External Bus Interface Address Line 11         |

|     | ESR2_4            | I      | St/B | ESR2 Trigger Input 4                           |

|     | CCU62_T12<br>HRB  | I      | St/B | External Run Control Input for T12 of CCU62    |

| 152 | P13.3             | O0 / I | St/B | Bit 3 of Port 13, General Purpose Input/Output |

|     | CC1_CC11          | O1 / I | St/B | CAPCOM1 CC11IO Capture Inp./ Compare Out.      |

|     | CCU60_CC6         | O2     | St/B | CCU60 Channel 0 Output                         |

|     | U4C1_SCLK<br>OUT  | О3     | St/B | USIC4 Channel 1 Shift Clock Output             |

|     | TMS_E             | IH     | St/B | JTAG Test Mode Selection Input                 |

|     | CCU60_CC6<br>0INC | I      | St/B | CCU60 Channel 0 Input                          |

| 153 | P9.4              | O0 / I | St/B | Bit 4 of Port 9, General Purpose Input/Output  |

|     | CCU63_COU<br>T61  | O1     | St/B | CCU63 Channel 1 Output                         |

|     | U2C0_DOUT         | O2     | St/B | USIC2 Channel 0 Shift Data Output              |

|     | CCU62_COU<br>T63  | О3     | St/B | CCU62 Channel 3 Output                         |

Table 5 Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.  | Туре | Function                                       |

|-----|-------------------|--------|------|------------------------------------------------|

| 162 | P13.5             | O0 / I | St/B | Bit 5 of Port 13, General Purpose Input/Output |

|     | CC1_CC13          | O1 / I | St/B | CAPCOM1 CC13IO Capture Inp./ Compare Out.      |

|     | CCU60_COU<br>T62  | O2     | St/B | CCU60 Channel 2 Output                         |

|     | U3C0_MCLK<br>OUT  | О3     | St/B | USIC3 Channel 0 Master Clock Output            |

|     | U4C1_DX0B         | I      | St/B | USIC4 Channel 1 Shift Data Input               |

|     | TDI_E             | IH     | St/B | JTAG Test Data Input                           |

| 163 | P1.6              | O0 / I | St/B | Bit 6 of Port 1, General Purpose Input/Output  |

|     | CCU62_CC6         | O1 / I | St/B | CCU62 Channel 1 Output                         |

|     | U1C1_SELO<br>2    | O2     | St/B | USIC1 Channel 1 Select/Control 2 Output        |

|     | U2C0_DOUT         | О3     | St/B | USIC2 Channel 0 Shift Data Output              |

|     | A14               | ОН     | St/B | External Bus Interface Address Line 14         |

|     | U2C0_DX0D         | I      | St/B | USIC2 Channel 0 Shift Data Input               |

|     | CCU62_CC6<br>1INA | I      | St/B | CCU62 Channel 1 Input                          |

|     | U4C1_DX0A         | I      | St/B | USIC4 Channel 1 Shift Data Input               |

| 164 | P9.7              | O0 / I | St/B | Bit 7 of Port 9, General Purpose Input/Output  |

|     | CCU62_COU<br>T60  | O1     | St/B | CCU62 Channel 0 Output                         |

|     | CCU62_COU<br>T63  | O2     | St/B | CCU62 Channel 3 Output                         |

|     | CCU63_CTR<br>APB  | I      | St/B | CCU63 Emergency Trap Input                     |

|     | U2C0_DX1D         | I      | St/B | USIC2 Channel 0 Shift Clock Input              |

|     | CCU60_CCP<br>OS0B | I      | St/B | CCU60 Position Input 0                         |

## **Functional Description**

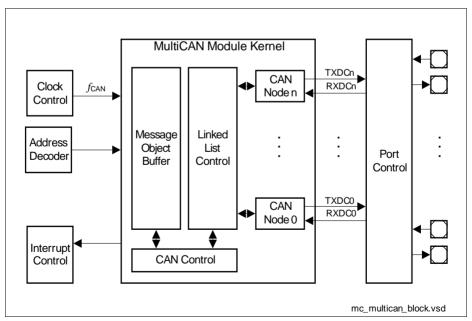

### 3.14 MultiCAN Module

The MultiCAN module contains independently operating CAN nodes with Full-CAN functionality which are able to exchange Data and Remote Frames using a gateway function. Transmission and reception of CAN frames is handled in accordance with CAN specification V2.0 B (active). Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

All CAN nodes share a common set of message objects. Each message object can be individually allocated to one of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects can be combined to build gateways between the CAN nodes or to set up a FIFO buffer.

Note: The number of CAN nodes and message objects depends on the selected device type.

The message objects are organized in double-chained linked lists, where each CAN node has its own list of message objects. A CAN node stores frames only into message objects that are allocated to its own message object list and it transmits only messages belonging to this message object list. A powerful, command-driven list controller performs all message object list operations.

Figure 12 Block Diagram of MultiCAN Module

## 4 Electrical Parameters

The operating range for the XE169xH is defined by its electrical parameters. For proper operation the specified limits must be respected when integrating the device in its target environment.

### 4.1 General Parameters

These parameters are valid for all subsequent descriptions, unless otherwise noted.

Table 11 Absolute Maximum Rating Parameters

| Parameter                                                 | Symbol               |      | Values |                        | Unit | Note /                     |

|-----------------------------------------------------------|----------------------|------|--------|------------------------|------|----------------------------|

|                                                           |                      | Min. | Тур.   | Max.                   |      | Test Condition             |

| Output current on a pin when high value is driven         | I <sub>OH</sub> SR   | -30  | _      | -                      | mA   |                            |

| Output current on a pin when low value is driven          | I <sub>OL</sub> SR   | -    | _      | 30                     | mA   |                            |

| Overload current                                          | $I_{OV}SR$           | -10  | _      | 10                     | mA   | 1)                         |

| Absolute sum of overload currents                         | $\Sigma  I_{OV} $ SR | -    | _      | 100                    | mA   | 1)                         |

| Junction Temperature                                      | $T_{J}SR$            | -40  | _      | 150                    | °C   |                            |

| Storage Temperature                                       | $T_{\rm ST}{ m SR}$  | -65  | _      | 150                    | °C   |                            |

| Digital supply voltage for IO pads and voltage regulators | $V_{DDP}SR$          | -0.5 | _      | 6.0                    | V    |                            |

| Voltage on any pin with respect to ground (Vss)           | $V_{IN}SR$           | -0.5 | _      | V <sub>DDP</sub> + 0.5 | V    | $V_{IN} \leq V_{DDP(max)}$ |

Overload condition occurs if the input voltage V<sub>IN</sub> is out of the absolute maximum rating range. In this case the current must be limited to the listed values by design measures.

Note: Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for an extended time may affect device reliability. During absolute maximum rating overload conditions  $(V_{\rm IN} > V_{\rm DDP} \ {\rm or} \ V_{\rm IN} < V_{\rm SS})$  the voltage on  $V_{\rm DDP}$  pins with respect to ground  $(V_{\rm SS})$  must not exceed the values defined by the absolute maximum ratings.

#### **Electrical Parameters**

Table 12 Operating Conditions (cont'd)

| Parameter                                                 | Symbol                        |      | Values                    |                           | Unit | Note /<br>Test Condition                            |

|-----------------------------------------------------------|-------------------------------|------|---------------------------|---------------------------|------|-----------------------------------------------------|

|                                                           |                               | Min. | Тур.                      | Max.                      |      |                                                     |

| Overload current coupling factor for digital I/O pins     | K <sub>OVD</sub><br>CC        | _    | 1.0 x<br>10 <sup>-2</sup> | 3.0 x<br>10 <sup>-2</sup> |      | $I_{\rm OV}$ < 0 mA; not subject to production test |

|                                                           |                               | _    | 1.0 x<br>10 <sup>-4</sup> | 5.0 x<br>10 <sup>-3</sup> |      | $I_{\rm OV}$ > 0 mA; not subject to production test |

| Absolute sum of overload currents                         | $\Sigma  I_{\mathrm{OV}} $ SR | _    | _                         | 50                        | mA   | not subject to production test                      |

| Digital core supply voltage for domain M <sup>8)</sup>    | $V_{DDIM}$ CC                 | _    | 1.5                       | -                         |      |                                                     |

| Digital core supply voltage for domain 18)                | $V_{ m DDI1}$ CC              | -    | 1.5                       | _                         |      |                                                     |

| Digital supply voltage for IO pads and voltage regulators | $V_{DDP}SR$                   | 3.0  | -                         | 5.5                       | V    |                                                     |

| Digital ground voltage                                    | $V_{\rm SS}{\rm SR}$          | -    | 0                         | _                         | V    |                                                     |

- 1) To ensure the stability of the voltage regulators the EVRs must be buffered with ceramic capacitors. Separate buffer capacitors with the recomended values shall be connected as close as possible to each  $V_{\rm DDIM}$  and  $V_{\rm DDIM}$  pin to keep the resistance of the board tracks below 2 Ohm. Connect all  $V_{\rm DDIM}$  pins together. The minimum capacitance value is required for proper operation under all conditions (e.g. temperature). Higher values slightly increase the startup time.

- 2) Use one Capacitor for each pin.

- This is the reference load. For bigger capacitive loads, use the derating factors listed in the PAD properties section.

- 4) The timing is valid for pin drivers operating in default current mode (selected after reset). Reducing the output current may lead to increased delays or reduced driving capability (C<sub>1</sub>).

- 5) The operating frequency range may be reduced for specific device types. This is indicated in the device designation (...FxxL). 80 MHz devices are marked ...F80L.

- 6) Overload conditions occur if the standard operating conditions are exceeded, i.e. the voltage on any pin exceeds the specified range: V<sub>OV</sub> > V<sub>IHmax</sub> (I<sub>OV</sub> > 0) or V<sub>OV</sub> < V<sub>ILmin</sub> ((I<sub>OV</sub> < 0). The absolute sum of input overload currents on all pins may not exceed 50 mA. The supply voltages must remain within the specified limits. Proper operation under overload conditions depends on the application. Overload conditions must not occur on pin XTAL1 (powered by V<sub>DDIM</sub>).

## 4.3.1 DC Parameters for Upper Voltage Area

Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{\rm OV}$ .

Note: Operating Conditions apply.

**Table 15** is valid under the following conditions:  $V_{\rm DDP}$ typ. 5 V;  $V_{\rm DDP} \ge$  4.5 V;  $V_{\rm DDP} \le$  5.5 V

Table 15 DC Characteristics for Upper Voltage Range

| Parameter                                                                                   | Symbol                   |                                                               | Values    |                                    | Unit | Note /                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------|-----------|------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                             |                          | Min.                                                          | Тур. Мах. |                                    |      | Test Condition                                                                                                                                                                      |

| Pin capacitance (digital inputs/outputs). To be doubled for double bond pins. <sup>1)</sup> | C <sub>IO</sub> CC       | _                                                             | _         | 10                                 | pF   | not subject to production test                                                                                                                                                      |

| Input Hysteresis <sup>2)</sup>                                                              | HYS CC                   | $0.11 \text{ x}$ $V_{\text{DDP}}$                             | _         | _                                  | V    | $R_{\rm S}$ = 0 Ohm                                                                                                                                                                 |

| Absolute input leakage current on pins of analog ports <sup>3)</sup>                        | I <sub>OZ1</sub>  <br>CC | _                                                             | 10        | 200                                | nA   | $\begin{aligned} &V_{\text{IN}} \!\!> V_{\text{SS}} \; \text{V}; \\ &V_{\text{IN}} \!\!< V_{\text{DDP}} \end{aligned}$                                                              |

| Absolute input leakage current for all other pins. To be doubled for double                 | I <sub>OZ2</sub>  <br>CC | -                                                             | 0.2       | 5                                  | μΑ   | $T_{\rm J} \leq$ 110 °C;<br>$V_{\rm IN} > V_{\rm SS}$ V;<br>$V_{\rm IN} < V_{\rm DDP}$                                                                                              |

| bond pins. <sup>3)1)4)</sup>                                                                |                          | _                                                             | 0.2       | 15                                 | μА   | $T_{\rm J} {\leq} 150~{\rm ^{\circ}C};$ $V_{\rm IN} {>} V_{\rm SS}~{\rm V};$ $V_{\rm IN} {<} V_{\rm DDP}$                                                                           |

| Pull Level Force Current <sup>5)</sup>                                                      | I <sub>PLF</sub>   SR    | 250                                                           | -         | -                                  | μΑ   | $ \begin{aligned} & V_{\text{IN}} \!\! \geq \\ & V_{\text{IHmin}}(pulldown \\ & \_enabled) \ ; \\ & V_{\text{IN}} \!\! \leq V_{\text{ILmax}}(pull \\ & up\_enabled) \end{aligned} $ |

| Pull Level Keep Current <sup>6)</sup>                                                       | I <sub>PLK</sub>  <br>SR | _                                                             | _         | 30                                 | μА   | $ \begin{aligned} V_{\text{IN}} &\geq V_{\text{IHmin}}(pull \\ up\_enabled) \;; \\ V_{\text{IN}} &\leq V_{\text{ILmax}}(pull \\ down\_enabled) \end{aligned} $                      |

| Input high voltage (all except XTAL1)                                                       | $V_{IH}SR$               | $\begin{array}{c} \text{0.7 x} \\ V_{\text{DDP}} \end{array}$ | _         | V <sub>DDP</sub> + 0.3             | V    |                                                                                                                                                                                     |

| Input low voltage (all except XTAL1)                                                        | $V_{IL}SR$               | -0.3                                                          | _         | $0.3 \text{ x}$ $V_{\mathrm{DDP}}$ | V    |                                                                                                                                                                                     |

#### **Electrical Parameters**

## 4.3.3 Power Consumption

The power consumed by the XE169xH depends on several factors such as supply voltage, operating frequency, active circuits, and operating temperature. The power consumption specified here consists of two components:

- The switching current I<sub>S</sub> depends on the device activity

- The leakage current I<sub>LK</sub> depends on the device temperature

To determine the actual power consumption, always both components, switching current  $I_{\rm S}$  and leakage current  $I_{\rm LK}$  must be added:

$$I_{\text{DDP}} = I_{\text{S}} + I_{\text{LK}}.$$

Note: The power consumption values are not subject to production test. They are verified by design/characterization.

To determine the total power consumption for dimensioning the external power supply, also the pad driver currents must be considered.

The given power consumption parameters and their values refer to specific operating conditions:

### Active mode:

Regular operation, i.e. peripherals are active, code execution out of Flash.

## Stopover mode:

Crystal oscillator and PLL stopped, Flash switched off, clock in domain DMP\_1 stopped.

Note: The maximum values cover the complete specified operating range of all manufactured devices.

The typical values refer to average devices under typical conditions, such as nominal supply voltage, room temperature, application-oriented activity.

After a power reset, the decoupling capacitors for  $V_{\rm DDIM}$  and  $V_{\rm DDI1}$  are charged with the maximum possible current.

For additional information, please refer to Section 5.2, Thermal Considerations.

Note: Operating Conditions apply.

## 4.5 System Parameters

The following parameters specify several aspects which are important when integrating the XE169xH into an application system.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

Table 21 Various System Parameters

| Parameter                                                             | Symbol              |                                       | Values   |                                       | Unit | Note /<br>Test Condition         |

|-----------------------------------------------------------------------|---------------------|---------------------------------------|----------|---------------------------------------|------|----------------------------------|

|                                                                       |                     | Min.                                  | Тур.     | Max.                                  |      |                                  |

| Short-term deviation of internal clock source frequency <sup>1)</sup> | $\Delta f_{INT}$ CC | -1                                    | -        | 1                                     | %    | $\Delta T_{J} \leq 10^{\circ}C$  |

| Internal clock source frequency                                       | $f_{INT}CC$         | 4.8                                   | 5.0      | 5.2                                   | MHz  |                                  |

| Wakeup clock source                                                   | $f_{WU}CC$          | 400                                   | _        | 700                                   | kHz  | FREQSEL= 00                      |

| frequency <sup>2)</sup>                                               |                     | 210                                   | _        | 390                                   | kHz  | FREQSEL= 01                      |

|                                                                       |                     | 140                                   | _        | 260                                   | kHz  | FREQSEL= 10                      |

|                                                                       |                     | 110                                   | _        | 200                                   | kHz  | FREQSEL= 11                      |

| Startup time from power-<br>on with code execution<br>from Flash      | $t_{SPO}$ CC        | 1.9                                   | 2.6      | 3.2                                   | ms   | <i>f</i> <sub>WU</sub> = 500 kHz |

| Startup time from stopover mode with code execution from PSRAM        | t <sub>SSO</sub> CC | 11 /<br>f <sub>WU</sub> <sup>3)</sup> | -        | 12 /<br>f <sub>WU</sub> <sup>3)</sup> | μS   |                                  |

| Core voltage (PVC) supervision level                                  | $V_{PVC}CC$         | V <sub>LV</sub> - 0.03                | $V_{LV}$ | $V_{\rm LV}$ + 0.07 <sup>4)</sup>     | V    | 5)                               |

| Supply watchdog (SWD) supervision level                               | $V_{ m SWD}$ CC     | V <sub>LV</sub> - 0.10 <sup>6)</sup>  | $V_{LV}$ | <i>V</i> <sub>LV</sub> + 0.15         | V    | voltage_range=<br>lower 5)       |

|                                                                       |                     | V <sub>LV</sub> - 0.15                | $V_{LV}$ | <i>V</i> <sub>LV</sub> + 0.15         | V    | voltage_range=<br>upper 5)       |

The short-term frequency deviation refers to a timeframe of a few hours and is measured relative to the current frequency at the beginning of the respective timeframe. This parameter is useful to determine a time span for re-triggering a LIN synchronization.

<sup>2)</sup> This parameter is tested for the fastest and the slowest selection. The medium selections are not subject to production test - verified by design/characterization

<sup>3)</sup>  $f_{WU}$  in MHz

#### **Electrical Parameters**

Table 24 Flash Parameters (cont'd)

| Parameter              | Symbol Values Un   |      | Unit | Note / |            |                                                                                                    |

|------------------------|--------------------|------|------|--------|------------|----------------------------------------------------------------------------------------------------|

|                        |                    | Min. | Тур. | Max.   |            | Test Condition                                                                                     |

| Number of erase cycles | N <sub>ER</sub> SR | _    | _    | 15.000 | cycle<br>s | t <sub>RET</sub> ≥ 5 years;<br>Valid for up to<br>64 user<br>selected<br>sectors (data<br>storage) |

|                        |                    | _    | _    | 1.000  | cycle<br>s | t <sub>RET</sub> ≥ 20 years                                                                        |

- All Flash module(s) can be erased/programmed while code is executed and/or data is read from only one Flash module or from PSRAM. The Flash module that delivers code/data can, of course, not be erased/programmed.

- Flash module 6 can be erased/programmed while code is executed and/or data is read from any other Flash module.

- 3) Value of IMB\_IMBCTRL.WSFLASH.

- 4) Value of IMB IMBCTRL.WSFLE.

- 5) Programming and erase times depend on the internal Flash clock source. The control state machine needs a few system clock cycles. This increases the stated durations noticably only at extremely low system clock frequencies.

Access to the XE169xH Flash modules is controlled by the IMB. Built-in prefetch mechanisms optimize the performance for sequential access.

Flash access waitstates only affect non-sequential access. Due to prefetch mechanisms, the performance for sequential access (depending on the software structure) is only partially influenced by waitstates.

## 4.7.2 Definition of Internal Timing

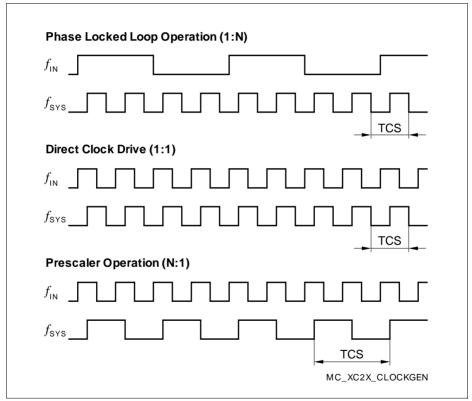

The internal operation of the XE169xH is controlled by the internal system clock  $f_{\rm SYS}$ .

Because the system clock signal  $f_{\rm SYS}$  can be generated from a number of internal and external sources using different mechanisms, the duration of the system clock periods (TCSs) and their variation (as well as the derived external timing) depend on the mechanism used to generate  $f_{\rm SYS}$ . This must be considered when calculating the timing for the XE169xH.

Figure 19 Generation Mechanisms for the System Clock

Note: The example of PLL operation shown in Figure 19 uses a PLL factor of 1:4; the example of prescaler operation uses a divider factor of 2:1.

The specification of the external timing (AC Characteristics) depends on the period of the system clock (TCS).

Data Sheet 116 V1.3, 2011-07

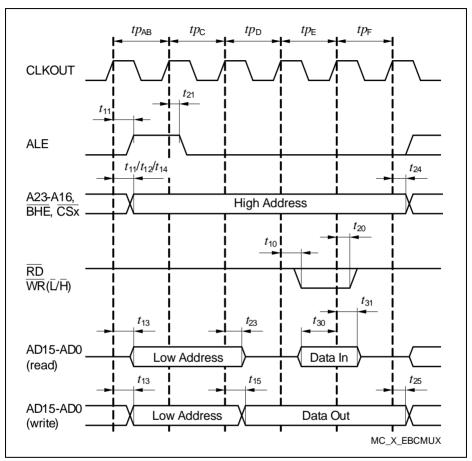

Figure 23 Multiplexed Bus Cycle

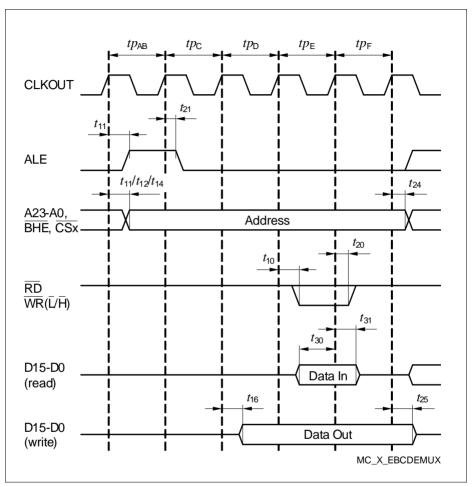

Figure 24 Demultiplexed Bus Cycle

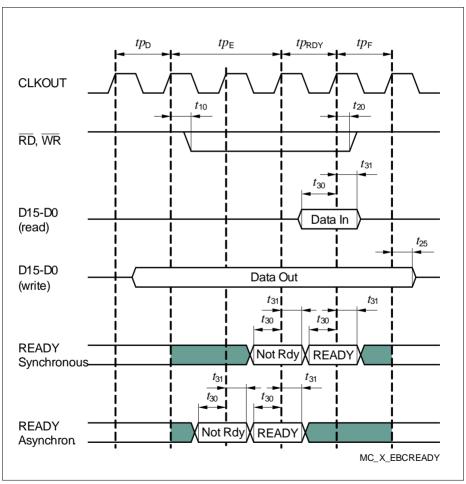

## 4.7.5.1 Bus Cycle Control with the READY Input

The duration of an external bus cycle can be controlled by the external circuit using the READY input signal. The polarity of this input signal can be selected.

Synchronous READY permits the shortest possible bus cycle but requires the input signal to be synchronous to the reference signal CLKOUT.

An asynchronous READY signal puts no timing constraints on the input signal but incurs a minimum of one waitstate due to the additional synchronization stage. The minimum

duration of an asynchronous READY signal for safe synchronization is one CLKOUT period plus the input setup time.

An active READY signal can be deactivated in response to the trailing (rising) edge of the corresponding command ( $\overline{RD}$  or  $\overline{WR}$ ).

If the next bus cycle is controlled by READY, an active READY signal must be disabled before the first valid sample point in the next bus cycle. This sample point depends on the programmed phases of the next cycle.

Figure 25 READY Timing

Data Sheet 133 V1.3, 2011-07

#### **Electrical Parameters**

Note: If the READY input is sampled inactive at the indicated sampling point ("Not Rdy") a READY-controlled waitstate is inserted (tpRDY),

sampling the READY input active at the indicated sampling point ("Ready") terminates the currently running bus cycle.

Note the different sampling points for synchronous and asynchronous READY. This example uses one mandatory waitstate (see tpE) before the READY input value is used.

### **Electrical Parameters**

Table 39 JTAG Interface Timing for Upper Voltage Range (cont'd)

| Parameter                                                                | Symbol             | Values |      |      | Unit | Note /         |

|--------------------------------------------------------------------------|--------------------|--------|------|------|------|----------------|

|                                                                          |                    | Min.   | Тур. | Max. |      | Test Condition |

| TCK low time                                                             | t <sub>3</sub> SR  | 16     | _    | _    | ns   |                |

| TCK clock rise time                                                      | t <sub>4</sub> SR  | _      | _    | 8    | ns   |                |

| TCK clock fall time                                                      | t <sub>5</sub> SR  | _      | _    | 8    | ns   |                |

| TDI/TMS setup to TCK rising edge                                         | t <sub>6</sub> SR  | 6      | _    | -    | ns   |                |

| TDI/TMS hold after TCK rising edge                                       | t <sub>7</sub> SR  | 6      | _    | -    | ns   |                |

| TDO valid from TCK falling edge (propagation delay) <sup>2)</sup>        | t <sub>8</sub> CC  | _      | 25   | 29   | ns   |                |

| TDO high impedance to valid output from TCK falling edge <sup>3)2)</sup> | t <sub>9</sub> CC  | _      | 25   | 29   | ns   |                |

| TDO valid output to high impedance from TCK falling edge <sup>2)</sup>   | t <sub>10</sub> CC | _      | 25   | 29   | ns   |                |

| TDO hold after TCK falling edge <sup>2)</sup>                            | t <sub>18</sub> CC | 5      | -    | -    | ns   |                |

<sup>1)</sup> Under typical conditions, the JTAG interface can operate at transfer rates up to 20 MHz.

**Table 40** is valid under the following conditions:  $C_L$ = 20 pF; voltage\_range= lower

Table 40 JTAG Interface Timing for Lower Voltage Range

| Parameter                        | Symbol            | Values |      |      | Unit | Note /         |

|----------------------------------|-------------------|--------|------|------|------|----------------|

|                                  |                   | Min.   | Тур. | Max. |      | Test Condition |

| TCK clock period                 | t <sub>1</sub> SR | 50     | _    | _    | ns   |                |

| TCK high time                    | t <sub>2</sub> SR | 16     | _    | _    | ns   |                |

| TCK low time                     | t <sub>3</sub> SR | 16     | _    | _    | ns   |                |

| TCK clock rise time              | t <sub>4</sub> SR | -      | _    | 8    | ns   |                |

| TCK clock fall time              | t <sub>5</sub> SR | _      | _    | 8    | ns   |                |

| TDI/TMS setup to TCK rising edge | t <sub>6</sub> SR | 6      | -    | -    | ns   |                |

Data Sheet 142 V1.3, 2011-07

<sup>2)</sup> The falling edge on TCK is used to generate the TDO timing.

<sup>3)</sup> The setup time for TDO is given implicitly by the TCK cycle time.

## Package and Reliability

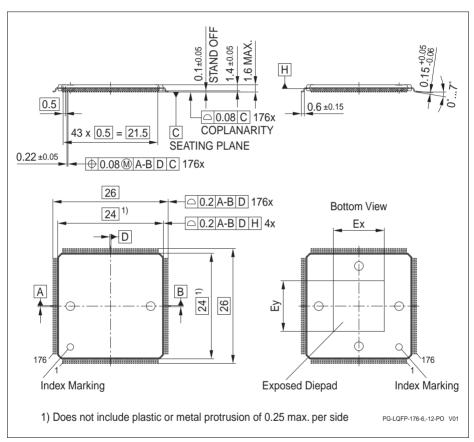

If different device types are considered or planned for an application, it must be ensured that the board layout fits all packages under consideration.

## **Package Outlines**

Figure 32 PG-LQFP-176-12 (Plastic Green Thin Quad Flat Package)

All dimensions in mm.

You can find complete information about Infineon packages, packing and marking in our Infineon Internet Page "Packages": http://www.infineon.com/packages

Data Sheet 146 V1.3, 2011-07