Welcome to **E-XFL.COM**

**Embedded - System On Chip (SoC):** The Heart of Modern Embedded Systems

Embedded - System On Chip (SoC) refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

What are **Embedded - System On Chip (SoC)**?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

| Details                 |                                                                            |

|-------------------------|----------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                   |

| Architecture            | MCU, FPGA                                                                  |

| Core Processor          | Dual ARM® Cortex®-A9 MPCore™ with CoreSight™                               |

| Flash Size              | -                                                                          |

| RAM Size                | 64KB                                                                       |

| Peripherals             | DMA, POR, WDT                                                              |

| Connectivity            | EBI/EMI, Ethernet, I <sup>2</sup> C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Speed                   | 800MHz                                                                     |

| Primary Attributes      | FPGA - 350K Logic Elements                                                 |

| Operating Temperature   | 0°C ~ 85°C (TJ)                                                            |

| Package / Case          | 1152-BBGA, FCBGA                                                           |

| Supplier Device Package | 1152-FBGA, FC (35x35)                                                      |

| Purchase URL            | https://www.e-xfl.com/product-detail/intel/5asxbb3d4f35c5n                 |

|                         |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Advantage          | Supporting Feature                                                                                                                                                                                                                                                                   |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lowest system cost | <ul> <li>Requires as few as four power supplies to operate</li> <li>Available in thermal composite flip chip ball-grid array (BGA) packaging</li> <li>Includes innovative features such as Configuration via Protocol (CvP), partial reconfiguration, and design security</li> </ul> |

# **Summary of Arria V Features**

Table 2: Summary of Features for Arria V Devices

| Feature                         | Description                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Technology                      | <ul> <li>TSMC's 28-nm process technology:</li> <li>Arria V GX, GT, SX, and ST—28-nm low power (28LP) process</li> <li>Arria V GZ—28-nm high performance (28HP) process</li> <li>Lowest static power in its class (less than 1.2 W for 500K logic elements (LEs) at 85°C junction under typical conditions)</li> <li>0.85 V, 1.1 V, or 1.15 V core nominal voltage</li> </ul> |

| Packaging                       | <ul> <li>Thermal composite flip chip BGA packaging</li> <li>Multiple device densities with identical package footprints for seamless migration between different device densities</li> <li>Leaded<sup>(1)</sup>, lead-free (Pb-free), and RoHS-compliant options</li> </ul>                                                                                                  |

| High-performance<br>FPGA fabric | <ul> <li>Enhanced 8-input ALM with four registers</li> <li>Improved routing architecture to reduce congestion and improve compilation time</li> </ul>                                                                                                                                                                                                                        |

| Internal memory<br>blocks       | <ul> <li>M10K—10-kilobits (Kb) memory blocks with soft error correction code (ECC) (Arria V GX, GT, SX, and ST devices only)</li> <li>M20K—20-Kb memory blocks with hard ECC (Arria V GZ devices only)</li> <li>Memory logic array block (MLAB)-640-bit distributed LUTRAM where you can use up to 50% of the ALMs as MLAB memory</li> </ul>                                 |

Send Feedback

$<sup>^{(1)}</sup>$  Contact Altera for availability.

| Feature       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration | <ul> <li>Tamper protection-comprehensive design protection to protect your valuable IP investments</li> <li>Enhanced advanced encryption standard (AES) design security features</li> <li>CvP</li> <li>Partial and dynamic reconfiguration of the FPGA</li> <li>Active serial (AS) x1 and x4, passive serial (PS), JTAG, and fast passive parallel (FPP) x8, x16, and x32 (Arria V GZ) configuration options</li> <li>Remote system upgrade</li> </ul> |

# **Arria V Device Variants and Packages**

Table 3: Device Variants for the Arria V Device Family

| Variant    | Description                                                                                                                                                                        |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arria V GX | FPGA with integrated 6.5536 Gbps transceivers that provides bandwidth, cost, and power levels that are optimized for high-volume data and signal-processing applications           |

| Arria V GT | FPGA with integrated 10.3125 Gbps transceivers that provides enhanced high-speed serial I/O bandwidth for cost-sensitive data and signal processing applications                   |

| Arria V GZ | FPGA with integrated 12.5 Gbps transceivers that provides enhanced high-speed serial I/O bandwidth for high-performance and cost-sensitive data and signal processing applications |

| Arria V SX | SoC with integrated ARM-based HPS and 6.5536 Gbps transceivers                                                                                                                     |

| Arria V ST | SoC with integrated ARM-based HPS and 10.3125 Gbps transceivers                                                                                                                    |

## Arria V GX

This section provides the available options, maximum resource counts, and package plan for the Arria V GX devices.

The information in this section is correct at the time of publication. For the latest information and to get more details, refer to the Altera Product Selector.

#### **Related Information**

#### **Altera Product Selector**

Provides the latest information about Altera products.

| Resource            |                        | Member Code |            |        |        |  |  |

|---------------------|------------------------|-------------|------------|--------|--------|--|--|

| Neso                | Resource               |             | <b>C</b> 7 | D3     | D7     |  |  |

| Transceiver         | 6 Gbps <sup>(4)</sup>  | 3 (9)       | 6 (24)     | 6 (24) | 6 (36) |  |  |

| Transcerver         | 10 Gbps <sup>(5)</sup> | 4           | 12         | 12     | 20     |  |  |

| GPIO <sup>(6)</sup> | GPIO <sup>(6)</sup>    |             | 544        | 704    | 704    |  |  |

| LVDS                | Transmitter            | 68          | 120        | 160    | 160    |  |  |

| LVD3                | Receiver               | 80          | 136        | 176    | 176    |  |  |

| PCIe Hard IP Block  |                        | 1           | 2          | 2      | 2      |  |  |

| Hard Memor          | y Controller           | 2           | 4          | 4      | 4      |  |  |

• High-Speed Differential I/O Interfaces and DPA in Arria V Devices chapter, Arria V Device Handbook

Provides the number of LVDS channels in each device package.

• Transceiver Architecture in Arria V Devices

Describes 10 Gbps channels usage conditions and SFF-8431 compliance requirements.

## **Package Plan**

Table 7: Package Plan for Arria V GT Devices

| Memb       | F672<br>(27 mm) |            | F896<br>(31 mm) |      |            | F1152<br>(35 mm) |      |            | F151<br>(40 mr |      |            |         |

|------------|-----------------|------------|-----------------|------|------------|------------------|------|------------|----------------|------|------------|---------|

| er<br>Code |                 | ХС         | VR              |      | ХС         | VR               |      | ХС         | VR             |      | 2          | KCVR    |

|            | GPIO            | 6-<br>Gbps | 10-<br>Gbps     | GPIO | 6-<br>Gbps | 10-<br>Gbps      | GPIO | 6-<br>Gbps | 10-<br>Gbps    | GPIO | 6-<br>Gbps | 10-Gbps |

| C3         | 336             | 3 (9)      | 4               | 416  | 3 (9)      | 4                | _    | _          | _              | _    | _          | _       |

| C7         | _               | _          | _               | 384  | 6 (18)     | 8                | 544  | 6 (24)     | 12             | _    | _          | _       |

| D3         | _               | _          | _               | 384  | 6 (18)     | 8                | 544  | 6 (24)     | 12             | 704  | 6 (24)     | 12      |

| D7         | _               | _          | _               | _    | _          | _                | 544  | 6 (24)     | 12             | 704  | 6 (36)     | 20      |

The 6-Gbps transceiver counts are for dedicated 6-Gbps channels. You can also configure any pair of 10-Gbps channels as three 6-Gbps channels—the total number of 6-Gbps channels are shown in brackets. For example, you can also configure the Arria V GT D7 device in the F1517 package with nine 6-Gbps

<sup>(4)</sup> The 6 Gbps transceiver counts are for dedicated 6-Gbps channels. You can also configure any pair of 10 Gbps channels as three 6 Gbps channels-the total number of 6 Gbps channels are shown in brackets.

<sup>(5)</sup> Chip-to-chip connections only. For 10 Gbps channel usage conditions, refer to the Transceiver Architecture in Arria V Devices chapter.

<sup>(6)</sup> The number of GPIOs does not include transceiver I/Os. In the Quartus Prime software, the number of user I/Os includes transceiver I/Os.

| Resource            |                              | Member Code |            |            |            |  |  |

|---------------------|------------------------------|-------------|------------|------------|------------|--|--|

| nesc                | Resource                     |             | <b>E</b> 3 | <b>E</b> 5 | <b>E</b> 7 |  |  |

| Memory              | M20K                         | 11,700      | 19,140     | 28,800     | 34,000     |  |  |

| (Kb)                | MLAB                         | 2,594       | 4,245      | 4,718      | 5,306      |  |  |

| Variable-pred       | Variable-precision DSP Block |             | 1,044      | 1,092      | 1,139      |  |  |

| 18 x 18 Multi       | 18 x 18 Multiplier           |             | 2,088      | 2,184      | 2,278      |  |  |

| PLL                 | PLL                          |             | 20         | 24         | 24         |  |  |

| 12.5 Gbps Tr        | ansceiver                    | 24          | 24         | 36         | 36         |  |  |

| GPIO <sup>(7)</sup> |                              | 414         | 414        | 674        | 674        |  |  |

| LVDS                | Transmitter                  | 99          | 99         | 166        | 166        |  |  |

| LVDS                | Receiver                     | 108         | 108        | 168        | 168        |  |  |

| PCIe Hard IF        | Block                        | 1           | 1          | 1          | 1          |  |  |

High-Speed Differential I/O Interfaces and DPA in Arria V Devices chapter, Arria V Device Handbook

Provides the number of LVDS channels in each device package.

## **Package Plan**

Table 9: Package Plan for Arria V GZ Devices

| Member<br>Code | H780<br>(33 mm) |      | ber (33 mm) (35 mm) |      | F1517<br>(40 mm) |      |

|----------------|-----------------|------|---------------------|------|------------------|------|

|                | GPIO            | XCVR | GPIO                | XCVR | GPIO             | XCVR |

| E1             | 342             | 12   | 414                 | 24   | _                | _    |

| E3             | 342             | 12   | 414                 | 24   | _                | _    |

| E5             | _               | _    | 534                 | 24   | 674              | 36   |

| E7             | _               | _    | 534                 | 24   | 674              | 36   |

## **Arria V SX**

This section provides the available options, maximum resource counts, and package plan for the Arria V SX devices.

The information in this section is correct at the time of publication. For the latest information and to get more details, refer to the Altera Product Selector.

<sup>&</sup>lt;sup>(7)</sup> The number of GPIOs does not include transceiver I/Os. In the Quartus Prime software, the number of user I/Os includes transceiver I/Os.

#### **Altera Product Selector**

Provides the latest information about Altera products.

## **Available Options**

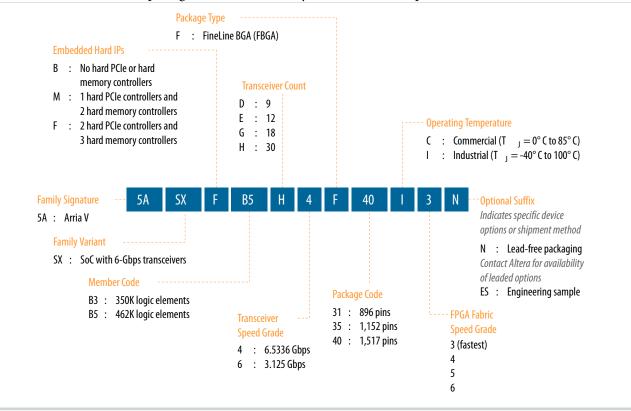

#### Figure 4: Sample Ordering Code and Available Options for Arria V SX Devices

The -3 FPGA fabric speed grade is available only for industrial temperature devices.

#### **Maximum Resources**

Table 10: Maximum Resource Counts for Arria V SX Devices

| Poso                         | urce               | Member Code |         |  |

|------------------------------|--------------------|-------------|---------|--|

| neso                         | ruice              | В3          | B5      |  |

| Logic Elements (LE)          | (K)                | 350         | 462     |  |

| ALM                          |                    | 132,075     | 174,340 |  |

| Register                     | Register           |             | 697,360 |  |

| Memory (Kb)                  | M10K               | 17,290      | 22,820  |  |

| Memory (Ro)                  | MLAB               | 2,014       | 2,658   |  |

| Variable-precision DSP Block |                    | 809         | 1,090   |  |

| 18 x 18 Multiplier           | 18 x 18 Multiplier |             | 2,180   |  |

#### **Altera Product Selector**

Provides the latest information about Altera products.

## **Available Options**

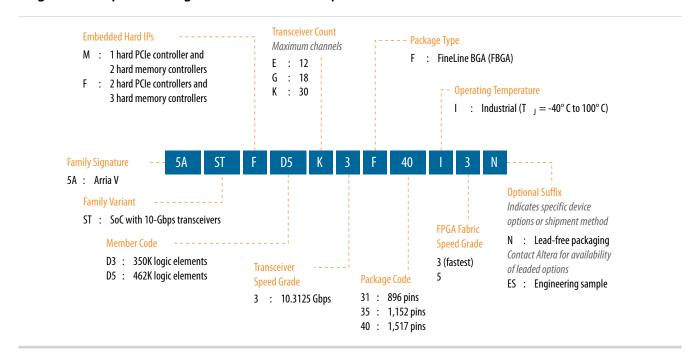

Figure 5: Sample Ordering Code and Available Options for Arria V ST Devices

#### **Maximum Resources**

**Table 12: Maximum Resource Counts for Arria V ST Devices**

| Resource             |                        | Member Code |         |  |

|----------------------|------------------------|-------------|---------|--|

| Reso                 | ource                  | D3          | D5      |  |

| Logic Elements (LE)  | (K)                    | 350         | 462     |  |

| ALM                  |                        | 132,075     | 174,340 |  |

| Register             |                        | 528,300     | 697,360 |  |

| Memory (Kb)          | M10K                   | 17,290      | 22,820  |  |

| Memory (Rb)          | MLAB                   | 2,014       | 2,658   |  |

| Variable-precision D | SP Block               | 809         | 1,090   |  |

| 18 x 18 Multiplier   |                        | 1,618       | 2,180   |  |

| FPGA PLL             | FPGA PLL               |             | 14      |  |

| HPS PLL              |                        | 3           | 3       |  |

| Transceiver          | 6-Gbps                 | 30          | 30      |  |

| Transcerver          | 10-Gbps <sup>(9)</sup> | 16          | 16      |  |

| Poso                        | ource          | Member Code |           |  |  |

|-----------------------------|----------------|-------------|-----------|--|--|

| nesu                        | raice          | D3          | D5        |  |  |

| FPGA GPIO <sup>(10)</sup>   |                | 540         | 540       |  |  |

| HPS I/O                     |                | 208         | 208       |  |  |

| LVDS                        | Transmitter    | 120         | 120       |  |  |

| LVD3                        | Receiver       | 136         | 136       |  |  |

| PCIe Hard IP Block          |                | 2           | 2         |  |  |

| FPGA Hard Memory Controller |                | 3           | 3         |  |  |

| HPS Hard Memory Controller  |                | 1           | 1         |  |  |

| ARM Cortex-A9 MP            | Core Processor | Dual-core   | Dual-core |  |  |

• High-Speed Differential I/O Interfaces and DPA in Arria V Devices chapter, Arria V Device Handbook

Provides the number of LVDS channels in each device package.

Transceiver Architecture in Arria V Devices

Describes 10 Gbps channels usage conditions and SFF-8431 compliance requirements.

### **Package Plan**

### Table 13: Package Plan for Arria V ST Devices

The HPS I/O counts are the number of I/Os in the HPS and does not correlate with the number of HPS-specific I/O pins in the FPGA. Each HPS-specific pin in the FPGA may be mapped to several HPS I/Os.

| Memb       | F896<br>(31 mm) |     |        | F1152<br>(35 mm) |               |        | F1517<br>(40 mm) |      |      |        |         |    |

|------------|-----------------|-----|--------|------------------|---------------|--------|------------------|------|------|--------|---------|----|

| er<br>Code | FPGA            | HPS | XCVR   |                  | FPGA HPS XCVR |        | FPGA HPS XCVR    |      | KCVR |        |         |    |

|            | GPIO            |     | 6 Gbps | 10<br>Gbps       | GPIO I/O      | 6 Gbps | 10<br>Gbps       | GPIO | 1/0  | 6 Gbps | 10 Gbps |    |

| D3         | 250             | 208 | 12     | 6                | 385           | 208    | 18               | 8    | 540  | 208    | 30      | 16 |

| D5         | 250             | 208 | 12     | 6                | 385           | 208    | 18               | 8    | 540  | 208    | 30      | 16 |

<sup>(9)</sup> Chip-to-chip connections only. For 10 Gbps channel usage conditions, refer to the Transceiver Architecture in Arria V Devices chapter.

<sup>(10)</sup> The number of GPIOs does not include transceiver I/Os. In the Quartus Prime software, the number of user I/Os includes transceiver I/Os.

# I/O Vertical Migration for Arria V Devices

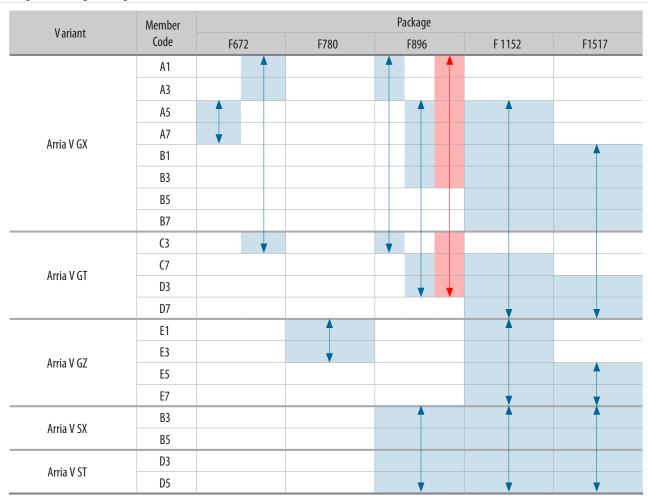

#### Figure 6: Vertical Migration Capability Across Arria V Device Packages and Densities

The arrows indicate the vertical migration paths. Some packages have several migration paths. The devices included in each vertical migration path are shaded. You can also migrate your design across device densities in the same package option if the devices have the same dedicated pins, configuration pins, and power pins.

You can achieve the vertical migration shaded in red if you use only up to 320 GPIOs, up to nine 6 Gbps transceiver channels, and up to four 10 Gbps transceiver (for Arria V GT devices). This migration path is not shown in the Quartus Prime software Pin Migration View.

**Note:** To verify the pin migration compatibility, use the Pin Migration View window in the Quartus Prime software Pin Planner.

**Note:** Except for Arria V GX A5 and A7, and Arria V GT C7 devices, all other Arria V GX and GT devices require a specific power-up sequence. If you plan to migrate your design from Arria V GX A5 and A7, and Arria V GT C7 devices to other Arria V devices, your design must adhere to the same required power-up sequence.

- Managing Device I/O Pins chapter, Quartus Prime Handbook Provides more information about vertical I/O migrations.

- Power Management in Arria V Devices

Describes the power-up sequence required for Arria V GX and GT devices.

# **Adaptive Logic Module**

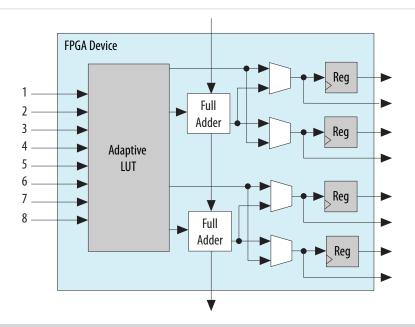

Arria V devices use a 28 nm ALM as the basic building block of the logic fabric.

The ALM, as shown in following figure, uses an 8-input fracturable look-up table (LUT) with four dedicated registers to help improve timing closure in register-rich designs and achieve an even higher design packing capability than previous generations.

Figure 7: ALM for Arria V Devices

You can configure up to 50% of the ALMs in the Arria V devices as distributed memory using MLABs.

#### **Related Information**

**Embedded Memory Capacity in Arria V Devices on page 20**

Lists the embedded memory capacity for each device.

## Variable-Precision DSP Block

Arria V devices feature a variable-precision DSP block that supports these features:

- Configurable to support signal processing precisions ranging from 9 x 9, 18 x 18, 27 x 27, and 36 x 36 bits natively

- A 64-bit accumulator

- Double accumulator

- A hard preadder that is available in both 18- and 27-bit modes

- Cascaded output adders for efficient systolic finite impulse response (FIR) filters

- Dynamic coefficients

- 18-bit internal coefficient register banks

- Enhanced independent multiplier operation

- Efficient support for single-precision floating point arithmetic

- The inferability of all modes by the Quartus Prime design software

#### Table 14: Variable-Precision DSP Block Configurations for Arria V Devices

| Usage Example                                       | Multiplier Size (Bit)       | DSP Block Resource |

|-----------------------------------------------------|-----------------------------|--------------------|

| Low precision fixed point for video applications    | Three 9 x 9                 | 1                  |

| Medium precision fixed point in FIR filters         | Two 18 x 18                 | 1                  |

| FIR filters                                         | Two 18 x 18 with accumulate | 1                  |

| Single-precision floating-<br>point implementations | One 27 x 27                 | 1                  |

| Very high precision fixed point implementations     | One 36 x 36                 | 2                  |

You can configure each DSP block during compilation as independent three 9 x 9, two 18 x 18, or one  $27 \times 27$  multipliers. Using two DSP block resources, you can also configure a  $36 \times 36$  multiplier for high-precision applications. With a dedicated 64 bit cascade bus, you can cascade multiple variable-precision DSP blocks to implement even higher precision DSP functions efficiently.

**Table 15: Number of Multipliers in Arria V Devices**

The table lists the variable-precision DSP resources by bit precision for each Arria V device.

| Variant | Mem<br>ber | Variable-<br>precision | Independ            | ent Input and<br>Ope  | 18 x 18<br>Multiplier | 18 x 18 Multiplier<br>Adder Summed |               |                   |

|---------|------------|------------------------|---------------------|-----------------------|-----------------------|------------------------------------|---------------|-------------------|

| Variant | Code       | DSP Block              | 9 x 9<br>Multiplier | 18 x 18<br>Multiplier | 27 x 27<br>Multiplier | 36 x 36<br>Multiplier              | Adder<br>Mode | with 36 bit Input |

|         | A1         | 240                    | 720                 | 480                   | 240                   | _                                  | 240           | 240               |

|         | A3         | 396                    | 1,188               | 792                   | 396                   | _                                  | 396           | 396               |

|         | A5         | 600                    | 1,800               | 1,200                 | 600                   | _                                  | 600           | 600               |

| Arria V | A7         | 800                    | 2,400               | 1,600                 | 800                   | _                                  | 800           | 800               |

| GX      | B1         | 920                    | 2,760               | 1,840                 | 920                   | _                                  | 920           | 920               |

|         | В3         | 1,045                  | 3,135               | 2,090                 | 1,045                 | _                                  | 1,045         | 1,045             |

|         | B5         | 1,092                  | 3,276               | 2,184                 | 1,092                 | _                                  | 1,092         | 1,092             |

|         | B7         | 1,156                  | 3,468               | 2,312                 | 1,156                 | _                                  | 1,156         | 1,156             |

|         | C3         | 396                    | 1,188               | 792                   | 396                   | _                                  | 396           | 396               |

| Arria V | C7         | 800                    | 2,400               | 1,600                 | 800                   | _                                  | 800           | 800               |

| GT      | D3         | 1,045                  | 3,135               | 2,090                 | 1,045                 | _                                  | 1,045         | 1,045             |

|         | D7         | 1,156                  | 3,468               | 2,312                 | 1,156                 | _                                  | 1,156         | 1,156             |

|         | E1         | 800                    | 2,400               | 1,600                 | 800                   | 400                                | 800           | 800               |

| Arria V | Е3         | 1,044                  | 3,132               | 2,088                 | 1,044                 | 522                                | 1,044         | 1,044             |

| GZ      | E5         | 1,092                  | 3,276               | 2,184                 | 1,092                 | 546                                | 1,092         | 1,092             |

|         | E7         | 1,139                  | 3,417               | 2,278                 | 1,139                 | 569                                | 1,139         | 1,139             |

| Arria V | В3         | 809                    | 2,427               | 1,618                 | 809                   | _                                  | 809           | 809               |

| SX      | B5         | 1,090                  | 3,270               | 2,180                 | 1,090                 | _                                  | 1,090         | 1,090             |

| Arria V | D3         | 809                    | 2,427               | 1,618                 | 809                   | _                                  | 809           | 809               |

| ST      | D5         | 1,090                  | 3,270               | 2,180                 | 1,090                 | _                                  | 1,090         | 1,090             |

# **Embedded Memory Blocks**

The embedded memory blocks in the devices are flexible and designed to provide an optimal amount of small- and large-sized memory arrays to fit your design requirements.

# **Types of Embedded Memory**

The Arria V devices contain two types of memory blocks:

- 20 Kb M20K or 10 Kb M10K blocks—blocks of dedicated memory resources. The M20K and M10K blocks are ideal for larger memory arrays while still providing a large number of independent ports.

- 640 bit memory logic array blocks (MLABs)—enhanced memory blocks that are configured from dual-purpose logic array blocks (LABs). The MLABs are ideal for wide and shallow memory arrays. The MLABs are optimized for implementation of shift registers for digital signal processing (DSP) applications, wide shallow FIFO buffers, and filter delay lines. Each MLAB is made up of ten adaptive logic modules (ALMs). In the Arria V devices, you can configure these ALMs as ten 32 x 2 blocks, giving you one 32 x 20 simple dual-port SRAM block per MLAB. You can also configure these ALMs, in Arria V GZ devices, as ten 64 x 1 blocks, giving you one 64 x 10 simple dual-port SRAM block per MLAB.

# **Embedded Memory Capacity in Arria V Devices**

Table 16: Embedded Memory Capacity and Distribution in Arria V Devices

|            |                 | M20K  |                 | M1    | M10K            |       | .AB             |                       |

|------------|-----------------|-------|-----------------|-------|-----------------|-------|-----------------|-----------------------|

| Variant    | Membe<br>r Code | Block | RAM Bit<br>(Kb) | Block | RAM Bit<br>(Kb) | Block | RAM Bit<br>(Kb) | Total RAM Bit<br>(Kb) |

|            | A1              | _     | _               | 800   | 8,000           | 741   | 463             | 8,463                 |

|            | A3              | _     | _               | 1,051 | 10,510          | 1538  | 961             | 11,471                |

|            | A5              | _     | _               | 1,180 | 11,800          | 1877  | 1,173           | 12,973                |

| Arria V GX | A7              | _     | _               | 1,366 | 13,660          | 2317  | 1,448           | 15,108                |

| Allia V GA | B1              | _     | _               | 1,510 | 15,100          | 2964  | 1,852           | 16,952                |

|            | В3              | _     | _               | 1,726 | 17,260          | 3357  | 2,098           | 19,358                |

|            | B5              | _     | _               | 2,054 | 20,540          | 4052  | 2,532           | 23,072                |

|            | В7              | _     | _               | 2,414 | 24,140          | 4650  | 2,906           | 27,046                |

|            | C3              | _     | _               | 1,051 | 10,510          | 1538  | 961             | 11,471                |

| Arria V GT | C7              | _     | _               | 1,366 | 13,660          | 2317  | 1,448           | 15,108                |

| Allia V GI | D3              | _     | _               | 1,726 | 17,260          | 3357  | 2,098           | 19,358                |

|            | D7              | _     | _               | 2,414 | 24,140          | 4650  | 2,906           | 27,046                |

|            | E1              | 585   | 11,700          | _     | _               | 4,151 | 2,594           | 14,294                |

| Arria V GZ | E3              | 957   | 19,140          | _     | _               | 6,792 | 4,245           | 23,385                |

| Arria v GZ | E5              | 1,440 | 28,800          | _     | _               | 7,548 | 4,718           | 33,518                |

|            | E7              | 1,700 | 34,000          | _     | _               | 8,490 | 5,306           | 39,306                |

| Arria V SX | В3              | _     | _               | 1,729 | 17,290          | 3223  | 2,014           | 19,304                |

| Allia v SA | B5              | _     | _               | 2,282 | 22,820          | 4253  | 2,658           | 25,478                |

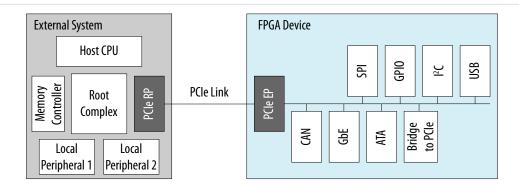

# PCIe Gen1, Gen2, and Gen 3 Hard IP

Arria V devices contain PCIe hard IP that is designed for performance and ease-of-use. The PCIe hard IP consists of the MAC, data link, and transaction layers.

The PCIe hard IP supports PCIe Gen3, Gen 2, and Gen 1 end point and root port for up to x8 lane configuration.

The PCIe endpoint support includes multifunction support for up to eight functions, as shown in the following figure. The integrated multifunction support reduces the FPGA logic requirements by up to 20,000 LEs for PCIe designs that require multiple peripherals.

Figure 8: PCIe Multifunction for Arria V Devices

The Arria V PCIe hard IP operates independently from the core logic. This independent operation allows the PCIe link to wake up and complete link training in less than 100 ms while the Arria V device completes loading the programming file for the rest of the device.

In addition, the PCIe hard IP in the Arria V device provides improved end-to-end datapath protection using ECC.

# **External Memory Interface**

This section provides an overview of the external memory interface in Arria V devices.

# **Hard and Soft Memory Controllers**

Arria V GX,GT, SX, and ST devices support up to four hard memory controllers for DDR3 and DDR2 SDRAM devices. Each controller supports 8 to 32 bit components of up to 4 gigabits (Gb) in density with two chip selects and optional ECC. For the Arria V SoC devices, an additional hard memory controller in the HPS supports DDR3, DDR2, and LPDDR2 SDRAM devices.

All Arria V devices support soft memory controllers for DDR3, DDR2, and LPDDR2 SDRAM devices, QDR II+, QDR II, and DDR II+ SRAM devices, and RLDRAM II devices for maximum flexibility.

**Note:** DDR3 SDRAM leveling is supported only in Arria V GZ devices.

#### **External Memory Interface Spec Estimator**

For the latest information and to estimate the external memory system performance specification, use Altera's External Memory Interface Spec Estimator tool.

## **Low-Power Serial Transceivers**

Arria V devices deliver the industry's lowest power consumption per transceiver channel:

- 12.5 Gbps transceivers at less than 170 mW

- 10 Gbps transceivers at less than 165 mW

- 6 Gbps transceivers at less than 105 mW

Arria V transceivers are designed to be compliant with a wide range of protocols and data rates.

### **Transceiver Channels**

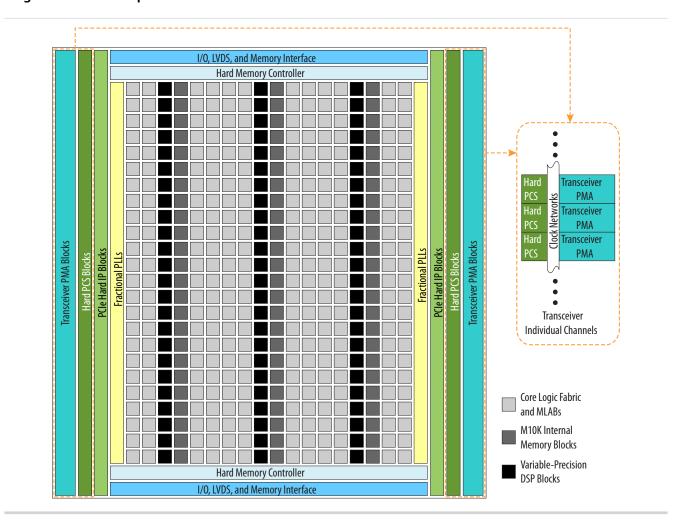

The transceivers are positioned on the left and right outer edges of the device. The transceiver channels consist of the physical medium attachment (PMA), physical coding sublayer (PCS), and clock networks.

The following figures are graphical representations of a top view of the silicon die, which corresponds to a reverse view for flip chip packages. Different Arria V devices may have different floorplans than the ones shown in the figures.

Figure 9: Device Chip Overview for Arria V GX and GT Devices

| Features                                                  | Capability                                                                                                                                                                            |  |  |  |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PLL-based clock recovery                                  | Superior jitter tolerance                                                                                                                                                             |  |  |  |

| Programmable serializer and deserializer (SERDES)         | Flexible SERDES width                                                                                                                                                                 |  |  |  |

| Equalization and pre-emphasis                             | <ul> <li>Arria V GX, GT, SX, and ST devices—Up to 14.37 dB of pre-emphasis and up to 4.7 dB of equalization</li> <li>Arria V GZ devices—4-tap pre-emphasis and de-emphasis</li> </ul> |  |  |  |

| Ring oscillator transmit PLLs                             | 611 Mbps to 10.3125 Gbps                                                                                                                                                              |  |  |  |

| LC oscillator ATX transmit PLLs (Arria V GZ devices only) | 600 Mbps to 12.5 Gbps                                                                                                                                                                 |  |  |  |

| Input reference clock range                               | 27 MHz to 710 MHz                                                                                                                                                                     |  |  |  |

| Transceiver dynamic reconfiguration                       | Allows the reconfiguration of a single channel without affecting the operation of other channels                                                                                      |  |  |  |

#### **PCS Features**

The Arria V core logic connects to the PCS through an 8, 10, 16, 20, 32, 40, 64, 66, or 67 bit interface, depending on the transceiver data rate and protocol. Arria V devices contain PCS hard IP to support PCIe Gen1, Gen2, and Gen3, GbE, Serial RapidIO (SRIO), GPON, and CPRI.

All other standard and proprietary protocols within the following speed ranges are also supported:

- 611 Mbps to 6.5536 Gbps—supported through the custom double-width mode (up to 6.5536 Gbps) and custom single-width mode (up to 3.75 Gbps) of the transceiver PCS hard IP.

- 6.5536 Gbps to 10.3125 Gbps—supported through dedicated 80 or 64 bit interface that bypass the PCS hard IP and connects the PMA directly to the core logic. In Arria V GZ, this is supported in the transceiver PCS hard IP.

Table 21: Transceiver PCS Features for Arria V GX, GT, ST, and SX Devices

| PCS Support <sup>(13)</sup>           | Data Rates<br>(Gbps) | Transmitter Data Path Feature      | Receiver Data Path Feature                            |

|---------------------------------------|----------------------|------------------------------------|-------------------------------------------------------|

| Custom single- and double-width modes | 0.611 to ~6.5536     | Phase compensation FIFO            | <ul><li>Word aligner</li><li>8B/10B decoder</li></ul> |

| SRIO                                  | 1.25 to 6.25         | Byte serializer     8B/10B encoder | Byte deserializer                                     |

| Serial ATA                            | 1.5, 3.0, 6.0        | OB/10B chedder                     | Phase compensation FIFO                               |

$<sup>^{(13)}</sup>$  Data rates above 6.5536 Gbps up to 10.3125 Gbps, such as 10GBASE-R, are supported through the soft PCS.

Table 22: Transceiver PCS Features for Arria V GZ Devices

| Protocol Data Rates (Gbps)                            |                             | Transmitter Data Path Features                                                                                                                                                    | Receiver Data Path Features                                                                                                                                                                          |  |  |

|-------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Custom PHY GPON                                       | 0.6 to 9.80<br>1.25 and 2.5 | <ul> <li>Phase compensation FIFO</li> <li>Byte serializer</li> <li>8B/10B encoder</li> <li>Bit-slip</li> <li>Channel bonding</li> </ul>                                           | <ul> <li>Word aligner</li> <li>Deskew FIFO</li> <li>Rate match FIFO</li> <li>8B/10B decoder</li> <li>Byte deserializer</li> <li>Byte ordering</li> </ul>                                             |  |  |

| Custom 10G PHY                                        | 9.98 to 12.5                | <ul><li>TX FIFO</li><li>Gear box</li><li>Bit-slip</li></ul>                                                                                                                       | <ul><li>RX FIFO</li><li>Gear box</li></ul>                                                                                                                                                           |  |  |

| PCIe Gen1 (x1, x2 x4, x8)  PCIe Gen2 (x1, x2, x4, x8) | 2.5 and 5.0                 | <ul> <li>Phase compensation FIFO</li> <li>Byte serializer</li> <li>8B/10B encoder</li> <li>Bit-slip</li> <li>Channel bonding</li> <li>PIPE 2.0 interface to core logic</li> </ul> | <ul> <li>Word aligner</li> <li>Deskew FIFO</li> <li>Rate match FIFO</li> <li>8B/10B decoder</li> <li>Byte deserializer,</li> <li>Byte ordering</li> <li>PIPE 2.0 interface to core logic</li> </ul>  |  |  |

| PCIe Gen3<br>(x1, x2, x4, x8)                         | 8.0                         | <ul> <li>Phase compensation FIFO</li> <li>128B/130B encoder</li> <li>Scrambler</li> <li>Gear box</li> <li>Bit-slip</li> </ul>                                                     | <ul> <li>Block synchronization</li> <li>Rate match FIFO</li> <li>128B/130B decoder</li> <li>Descrambler</li> <li>Phase compensation FIFO</li> </ul>                                                  |  |  |

| 10GbE                                                 | 10.3125                     | <ul><li>TX FIFO</li><li>64B/66B encoder</li><li>Scrambler</li><li>Gear box</li></ul>                                                                                              | <ul> <li>RX FIFO</li> <li>64B/66B decoder</li> <li>Descrambler</li> <li>Block synchronization</li> <li>Gear box</li> </ul>                                                                           |  |  |

| Interlaken                                            | 3.125 to 12.5               | <ul> <li>TX FIFO</li> <li>Frame generator</li> <li>CRC-32 generator</li> <li>Scrambler</li> <li>Disparity generator</li> <li>Gear box</li> </ul>                                  | <ul> <li>RX FIFO</li> <li>Frame generator</li> <li>CRC-32 checker</li> <li>Frame decoder</li> <li>Descrambler</li> <li>Disparity checker</li> <li>Block synchronization</li> <li>Gear box</li> </ul> |  |  |

| Protocol                                        | Data Rates<br>(Gbps)          | Transmitter Data Path Features                                                                                                                                                                 | Receiver Data Path Features                                                                                                                                                                                          |

|-------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40GBASE-R<br>Ethernet<br>100GBASE-R<br>Ethernet | 4 x 10.3125<br>10 x 10.3125   | <ul> <li>TX FIFO</li> <li>64B/66B encoder</li> <li>Scrambler</li> <li>Alignment marker insertion</li> <li>Gearbox</li> <li>Block stripper</li> </ul>                                           | <ul> <li>RX FIFO</li> <li>64B/66B decoder</li> <li>Descrambler</li> <li>Lane reorder</li> <li>Deskew</li> <li>Alignment marker lock</li> <li>Block synchronization</li> <li>Gear box</li> <li>Destripper</li> </ul>  |

| 40G and 100G OTN                                | (4+1) x 11.3<br>(10+1) x 11.3 | <ul><li> TX FIFO</li><li> Channel bonding</li><li> Byte serializer</li></ul>                                                                                                                   | <ul><li>RX FIFO</li><li>Lane deskew</li><li>Byte deserializer</li></ul>                                                                                                                                              |

| GbE                                             | 1.25                          | <ul> <li>Phase compensation FIFO</li> <li>Byte serializer</li> <li>8B/10B encoder</li> <li>Bit-slip</li> <li>Channel bonding</li> <li>GbE state machine</li> </ul>                             | <ul> <li>Word aligner</li> <li>Deskew FIFO</li> <li>Rate match FIFO</li> <li>8B/10B decoder</li> <li>Byte deserializer</li> <li>Byte ordering</li> <li>GbE state machine</li> </ul>                                  |

| XAUI                                            | 3.125 to 4.25                 | <ul> <li>Phase compensation FIFO</li> <li>Byte serializer</li> <li>8B/10B encoder</li> <li>Bit-slip</li> <li>Channel bonding</li> <li>XAUI state machine for bonding four channels</li> </ul>  | <ul> <li>Word aligner</li> <li>Deskew FIFO</li> <li>Rate match FIFO</li> <li>8B/10B decoder</li> <li>Byte deserializer</li> <li>Byte ordering</li> <li>XAUI state machine for realigning four channels</li> </ul>    |

| SRIO                                            | 1.25 to 6.25                  | <ul> <li>Phase compensation FIFO</li> <li>Byte serializer</li> <li>8B/10B encoder</li> <li>Bit-slip</li> <li>Channel bonding</li> <li>SRIO V2.1-compliant x2 and x4 channel bonding</li> </ul> | <ul> <li>Word aligner</li> <li>Deskew FIFO</li> <li>Rate match FIFO</li> <li>8B/10B decoder</li> <li>Byte deserializer</li> <li>Byte ordering</li> <li>SRIO V2.1-compliant x2 and x4 deskew state machine</li> </ul> |

# **Partial Reconfiguration**

**Note:** Partial reconfiguration is an advanced feature of the device family. If you are interested in using partial reconfiguration, contact Altera for support.

Partial reconfiguration allows you to reconfigure part of the device while other sections of the device remain operational. This capability is important in systems with critical uptime requirements because it allows you to make updates or adjust functionality without disrupting services.

Apart from lowering cost and power consumption, partial reconfiguration increases the effective logic density of the device because placing device functions that do not operate simultaneously is not necessary. Instead, you can store these functions in external memory and load them whenever the functions are required. This capability reduces the size of the device because it allows multiple applications on a single device—saving the board space and reducing the power consumption.

Altera simplifies the time-intensive task of partial reconfiguration by building this capability on top of the proven incremental compile and design flow in the Quartus Prime design software. With the Altera solution, you do not need to know all the intricate device architecture details to perform a partial reconfiguration.

Partial reconfiguration is supported through the FPP x16 configuration interface. You can seamlessly use partial reconfiguration in tandem with dynamic reconfiguration to enable simultaneous partial reconfiguration of both the device core and transceivers.

# **Enhanced Configuration and Configuration via Protocol**

## Table 23: Configuration Modes and Features of Arria V Devices

Arria V devices support 1.8 V, 2.5 V, 3.0 V, and 3.3 V<sup>(19)</sup> programming voltages and several configuration modes.

| Mode                                                     | Data<br>Width    | Max<br>Clock<br>Rate<br>(MHz) | Max Datal<br>Rate<br>(Mbps) | Decompression |     | Partial<br>econfiguratio<br>(20) | Remote System<br>Update |

|----------------------------------------------------------|------------------|-------------------------------|-----------------------------|---------------|-----|----------------------------------|-------------------------|

| AS through the EPCS and EPCQ serial configuration device | 1 bit, 4<br>bits | 100                           | _                           | Yes           | Yes | _                                | Yes                     |

| PS through<br>CPLD or<br>external<br>microcontroller     | 1 bit            | 125                           | 125                         | Yes           | Yes | _                                | _                       |

<sup>(19)</sup> Arria V GZ does not support 3.3 V.

<sup>&</sup>lt;sup>(20)</sup> Partial reconfiguration is an advanced feature of the device family. If you are interested in using partial reconfiguration, contact Altera for support.

| Date             | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2013        | 2013.06.03 | Removed statements about contacting Altera for SFF-8431 compliance requirements. Refer to the Transceiver Architecture in Arria V Devices chapter for the requirements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| May 2013         | 2013.05.06 | <ul> <li>Moved all links to the Related Information section of respective topics for easy reference.</li> <li>Added link to the known document issues in the Knowledge Base.</li> <li>Updated the available options, maximum resource counts, and per package information for the Arria V SX and ST device variants.</li> <li>Updated the variable DSP multipliers counts for the Arria V SX and ST device variants.</li> <li>Clarified that partial reconfiguration is an advanced feature. Contact Altera for support of the feature.</li> <li>Added footnote to clarify that MLAB 64 bits depth is available only for Arria V GZ devices.</li> <li>Updated description about power-up sequence requirement for device migration to improve clarity.</li> </ul> |

| January 2013     | 2013.01.11 | <ul> <li>Added the L optional suffix to the Arria V GZ ordering code for the – I3 speed grade.</li> <li>Added a note about the power-up sequence requirement if you plan to migrate your design from the Arria V GX A5 and A7, and Arria V GT C7 devices to other Arria V devices.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| November<br>2012 | 2012.11.19 | <ul> <li>Updated the summary of features.</li> <li>Updated Arria V GZ information regarding 3.3 V I/O support.</li> <li>Removed Arria V GZ engineering sample ordering code.</li> <li>Updated the maximum resource counts for Arria V GX and GZ.</li> <li>Updated Arria V ST ordering codes for transceiver count.</li> <li>Updated transceiver counts for Arria V ST packages.</li> <li>Added simplified floorplan diagrams for Arria V GZ, SX, and ST.</li> <li>Added FPP x32 configuration mode for Arria V GZ only.</li> <li>Updated CvP (PCIe) remote system update support information.</li> <li>Added HPS external memory performance information.</li> <li>Updated template.</li> </ul>                                                                   |

| October 2012     | 3.0        | <ul> <li>Added Arria V GZ information.</li> <li>Updated Table 1, Table 2, Table 3, Table 14, Table 15, Table 16, Table 17, Table 18, Table 19, Table 20, and Table 21.</li> <li>Added the "Arria V GZ" section.</li> <li>Added Table 8, Table 9 and Table 22.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |