Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| <b>-</b>                   |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Details                    |                                                                           |

| Product Status             | Active                                                                    |

| Core Processor             | ARM® Cortex®-M0                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 50MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, Microwire, SPI, SSI, SSP, UART/USART                    |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 28                                                                        |

| Program Memory Size        | 8KB (8K x 8)                                                              |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 512 x 8                                                                   |

| RAM Size                   | 4K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 32-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 32-HVQFN (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc11e11fhn33-101 |

## 32-bit ARM Cortex-M0 microcontroller

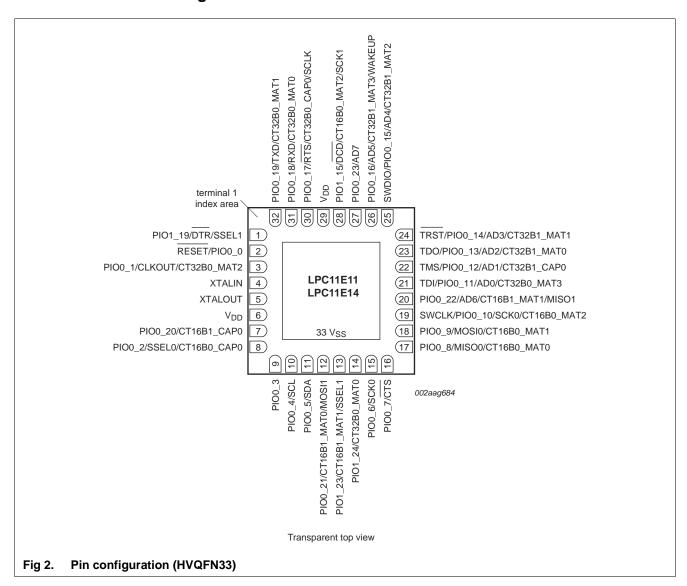

## 6. Pinning information

## 6.1 Pinning

Table 3. Pin description

| Symbol                             | HVQFN33 | LQFP48 | LQFP64 |            | Reset<br>state<br>[1] | Type | Description                                                                                                                                                                                                                                    |

|------------------------------------|---------|--------|--------|------------|-----------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO0_8/MISO0/                      | 17      | 27     | 36     | [3]        | I; PU                 | I/O  | PIO0_8 — General purpose digital input/output pin.                                                                                                                                                                                             |

| CT16B0_MAT0                        |         |        |        |            | -                     | I/O  | MISO0 — Master In Slave Out for SSP0.                                                                                                                                                                                                          |

|                                    |         |        |        |            | -                     | 0    | CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                                                                                                                                                                                               |

| PIO0_9/MOSI0/                      | 18      | 28     | 37     | [3]        | I; PU                 | I/O  | PIO0_9 — General purpose digital input/output pin.                                                                                                                                                                                             |

| CT16B0_MAT1                        |         |        |        |            | -                     | I/O  | MOSI0 — Master Out Slave In for SSP0.                                                                                                                                                                                                          |

|                                    |         |        |        |            | -                     | 0    | CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                                                                                                                                                                               |

| SWCLK/PIO0_10/SCK0/<br>CT16B0_MAT2 | 19      | 29     | 38     | <u>[3]</u> | I; PU                 | I    | <b>SWCLK</b> — Serial wire clock and test clock TCK for JTAG interface.                                                                                                                                                                        |

|                                    |         |        |        |            | -                     | I/O  | PIO0_10 — General purpose digital input/output pin.                                                                                                                                                                                            |

|                                    |         |        |        |            | -                     | 0    | SCK0 — Serial clock for SSP0.                                                                                                                                                                                                                  |

|                                    |         |        |        |            | -                     | 0    | CT16B0_MAT2 — Match output 2 for 16-bit timer 0.                                                                                                                                                                                               |

| TDI/PIO0_11/AD0/                   | 21      | 32     | 42     | [6]        | I; PU                 | I    | <b>TDI</b> — Test Data In for JTAG interface.                                                                                                                                                                                                  |

| CT32B0_MAT3                        |         |        |        |            | -                     | I/O  | PIO0_11 — General purpose digital input/output pin.                                                                                                                                                                                            |

|                                    |         |        |        |            | -                     | I    | AD0 — A/D converter, input 0.                                                                                                                                                                                                                  |

|                                    |         |        |        |            | -                     | 0    | CT32B0_MAT3 — Match output 3 for 32-bit timer 0.                                                                                                                                                                                               |

| TMS/PIO0_12/AD1/                   | 22      | 33     | 44     | [6]        | I; PU                 | I    | <b>TMS</b> — Test Mode Select for JTAG interface.                                                                                                                                                                                              |

| CT32B1_CAP0                        |         |        |        |            | -                     | I/O  | PIO_12 — General purpose digital input/output pin.                                                                                                                                                                                             |

|                                    |         |        |        |            | -                     | I    | AD1 — A/D converter, input 1.                                                                                                                                                                                                                  |

|                                    |         |        |        |            | -                     | I    | CT32B1_CAP0 — Capture input 0 for 32-bit timer 1.                                                                                                                                                                                              |

| TDO/PIO0_13/AD2/                   | 23      | 34     | 45     | [6]        | I; PU                 | 0    | <b>TDO</b> — Test Data Out for JTAG interface.                                                                                                                                                                                                 |

| CT32B1_MAT0                        |         |        |        |            | -                     | I/O  | PIO0_13 — General purpose digital input/output pin.                                                                                                                                                                                            |

|                                    |         |        |        |            | -                     | I    | AD2 — A/D converter, input 2.                                                                                                                                                                                                                  |

|                                    |         |        |        |            | -                     | 0    | CT32B1_MAT0 — Match output 0 for 32-bit timer 1.                                                                                                                                                                                               |

| TRST/PIO0_14/AD3/                  | 24      | 35     | 46     | [6]        | I; PU                 | I    | TRST — Test Reset for JTAG interface.                                                                                                                                                                                                          |

| CT32B1_MAT1                        |         |        |        |            | -                     | I/O  | PIO0_14 — General purpose digital input/output pin.                                                                                                                                                                                            |

|                                    |         |        |        |            | -                     | I    | AD3 — A/D converter, input 3.                                                                                                                                                                                                                  |

|                                    |         |        |        |            | -                     | 0    | CT32B1_MAT1 — Match output 1 for 32-bit timer 1.                                                                                                                                                                                               |

| SWDIO/PIO0_15/AD4/                 | 25      | 39     | 52     | [6]        | I; PU                 | I/O  | <b>SWDIO</b> — Serial wire debug input/output.                                                                                                                                                                                                 |

| CT32B1_MAT2                        |         |        |        |            | -                     | I/O  | PIO0_15 — General purpose digital input/output pin.                                                                                                                                                                                            |

|                                    |         |        |        |            | -                     | I    | AD4 — A/D converter, input 4.                                                                                                                                                                                                                  |

|                                    |         |        |        |            | -                     | 0    | CT32B1_MAT2 — Match output 2 for 32-bit timer 1.                                                                                                                                                                                               |

| PIO0_16/AD5/                       | 26      | 40     | 53     | [6]        | I; PU                 | I/O  | PIO0_16 — General purpose digital input/output pin.                                                                                                                                                                                            |

| CT32B1_MAT3/WAKEUP                 |         |        |        |            | -                     | I    | AD5 — A/D converter, input 5.                                                                                                                                                                                                                  |

|                                    |         |        |        |            | -                     | 0    | CT32B1_MAT3 — Match output 3 for 32-bit timer 1.                                                                                                                                                                                               |

|                                    |         |        |        |            | -                     | I    | <b>WAKEUP</b> — Deep power-down mode wake-up pin with 20 ns glitch filter. Pull this pin HIGH externally to enter Deep power-down mode. Pull this pin LOW to exit Deep power-down mode. A LOW-going pulse as short as 50 ns wakes up the part. |

- [6] 5 V tolerant pad providing digital I/O functions with configurable pull-up/pull-down resistors, configurable hysteresis, and analog input. When configured as a ADC input, digital section of the pad is disabled and the pin is not 5 V tolerant (see <u>Figure 27</u>); includes digital input glitch filter.

- [7] When the system oscillator is not used, connect XTALIN and XTALOUT as follows: XTALIN can be left floating or can be grounded (grounding is preferred to reduce susceptibility to noise). Leave XTALOUT floating.

## 32-bit ARM Cortex-M0 microcontroller

#### 7.8.1 Features

- GPIO pins can be configured as input or output by software.

- All GPIO pins default to inputs with interrupt disabled at reset.

- Pin registers allow pins to be sensed and set individually.

- Up to eight GPIO pins can be selected from all GPIO pins to create an edge- or level-sensitive GPIO interrupt request.

- Any pin or pins in each port can trigger a port interrupt.

#### 7.9 USART

The LPC11E1x contain one USART.

The USART includes full modem control, support for synchronous mode, and a smart card interface. The RS-485/9-bit mode allows both software address detection and automatic address detection using 9-bit mode.

The USART uses a fractional baud rate generator. Standard baud rates such as 115200 Bd can be achieved with any crystal frequency above 2 MHz.

#### 7.9.1 Features

- Maximum USART data bit rate of 3.125 Mbit/s.

- 16 byte receive and transmit FIFOs.

- Register locations conform to 16C550 industry standard.

- Receiver FIFO trigger points at 1 B, 4 B, 8 B, and 14 B.

- Built-in fractional baud rate generator covering wide range of baud rates without a need for external crystals of particular values.

- Fractional divider for baud rate control, auto baud capabilities and FIFO control mechanism that enables software flow control implementation.

- Support for RS-485/9-bit mode.

- Support for modem control.

- Support for synchronous mode.

- Includes smart card interface.

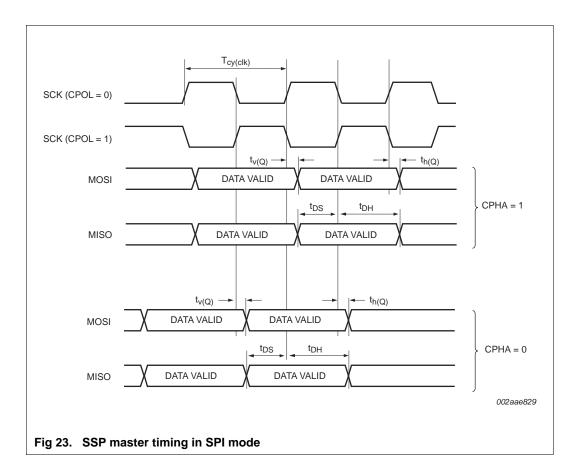

## 7.10 SSP serial I/O controller

The SSP controllers operate on a SSP, 4-wire SSI, or Microwire bus. It can interact with multiple masters and slaves on the bus. Only a single master and a single slave can communicate on the bus during a given data transfer. The SSP supports full duplex transfers, with frames of 4 bit to 16 bit of data flowing from the master to the slave and from the slave to the master. In practice, often only one of these data flows carries meaningful data.

#### 7.10.1 Features

- Maximum SSP speed of 25 Mbit/s (master) or 4.17 Mbit/s (slave) (in SSP mode)

- Compatible with Motorola SPI, 4-wire Texas Instruments SSI, and National Semiconductor Microwire buses

## 32-bit ARM Cortex-M0 microcontroller

- Synchronous serial communication

- Master or slave operation

- 8-frame FIFOs for both transmit and receive

- 4-bit to 16-bit frame

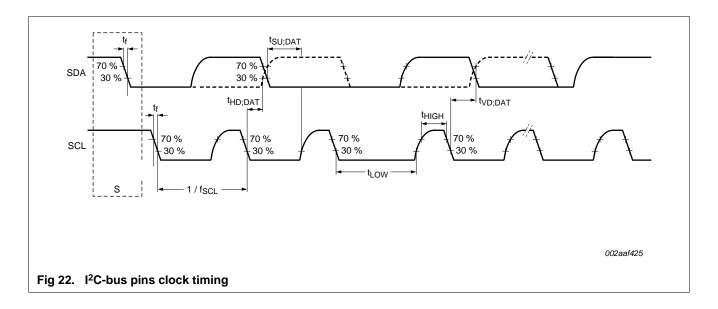

#### 7.11 I<sup>2</sup>C-bus serial I/O controller

The LPC11E1x contain one I2C-bus controller.

The I<sup>2</sup>C-bus is bidirectional for inter-IC control using only two wires: a Serial Clock line (SCL) and a Serial Data line (SDA). Each device is recognized by a unique address and can operate as either a receiver-only device (e.g., an LCD driver) or a transmitter with the capability to both receive and send information (such as memory). Transmitters and/or receivers can operate in either master or slave mode, depending on whether the chip has to initiate a data transfer or is only addressed. The I<sup>2</sup>C-bus is a multi-master bus, and more than one bus master connected to the interface can be controlled the bus.

## 7.11.1 Features

- The I<sup>2</sup>C-interface is an I<sup>2</sup>C-bus compliant interface with open-drain pins. The I<sup>2</sup>C-bus interface supports Fast-mode Plus with bit rates up to 1 Mbit/s.

- Easy to configure as master, slave, or master/slave.

- Programmable clocks allow versatile rate control.

- Bidirectional data transfer between masters and slaves.

- Multi-master bus (no central master).

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus.

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus.

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer.

- The I<sup>2</sup>C-bus can be used for test and diagnostic purposes.

- The I<sup>2</sup>C-bus controller supports multiple address recognition and a bus monitor mode.

#### 7.12 10-bit ADC

The LPC11E1x contains one ADC. It is a single 10-bit successive approximation ADC with eight channels.

#### **7.12.1 Features**

- 10-bit successive approximation ADC.

- Input multiplexing among 8 pins.

- Power-down mode.

- Measurement range 0 V to V<sub>DD</sub>.

- 10-bit conversion time ≥ 2.44 µs (up to 400 kSamples/s).

- Burst conversion mode for single or multiple inputs.

#### 32-bit ARM Cortex-M0 microcontroller

- Optional conversion on transition of input pin or timer match signal.

- Individual result registers for each ADC channel to reduce interrupt overhead.

## 7.13 General purpose external event counter/timers

The LPC11E1x include two 32-bit counter/timers and two 16-bit counter/timers. The counter/timer is designed to count cycles of the system derived clock. It can optionally generate interrupts or perform other actions at specified timer values, based on four match registers. Each counter/timer also includes one capture input to trap the timer value when an input signal transitions, optionally generating an interrupt.

#### 7.13.1 Features

- A 32-bit/16-bit timer/counter with a programmable 32-bit/16-bit prescaler.

- Counter or timer operation.

- Up to two capture channels per timer, that can take a snapshot of the timer value when an input signal transitions. A capture event can also generate an interrupt.

- Four match registers per timer that allow:

- Continuous operation with optional interrupt generation on match.

- Stop timer on match with optional interrupt generation.

- Reset timer on match with optional interrupt generation.

- Up to four external outputs corresponding to match registers, with the following capabilities:

- Set LOW on match.

- Set HIGH on match.

- Toggle on match.

- Do nothing on match.

- The timer and prescaler can be configured to be cleared on a designated capture event. This feature permits easy pulse-width measurement by clearing the timer on the leading edge of an input pulse and capturing the timer value on the trailing edge.

## 7.14 System tick timer

The ARM Cortex-M0 includes a system tick timer (SYSTICK) that is intended to generate a dedicated SYSTICK exception at a fixed time interval (typically 10 ms).

## 7.15 Windowed WatchDog Timer (WWDT)

The purpose of the WWDT is to prevent an unresponsive system state. If software fails to update the watchdog within a programmable time window, the watchdog resets the microcontroller

## 7.15.1 Features

- Internally resets chip if not periodically reloaded during the programmable time-out period.

- Optional windowed operation requires reload to occur between a minimum and maximum time period, both programmable.

#### 32-bit ARM Cortex-M0 microcontroller

- Optional warning interrupt can be generated at a programmable time before watchdog time-out.

- Software enables the WWDT, but a hardware reset or a watchdog reset/interrupt is required to disable the WWDT.

- Incorrect feed sequence causes reset or interrupt, if enabled.

- Flag to indicate watchdog reset.

- Programmable 24-bit timer with internal prescaler.

- Selectable time period from  $(T_{cy(WDCLK)} \times 256 \times 4)$  to  $(T_{cy(WDCLK)} \times 2^{24} \times 4)$  in multiples of  $T_{cy(WDCLK)} \times 4$ .

- The Watchdog Clock (WDCLK) source can be selected from the IRC or the dedicated watchdog oscillator (WDO). The clock source selection provides a wide range of potential timing choices of watchdog operation under different power conditions.

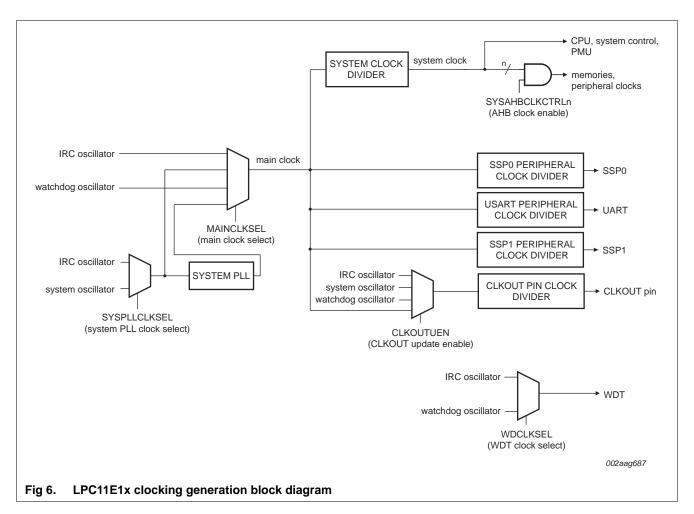

## 7.16 Clocking and power control

## 7.16.1 Integrated oscillators

The LPC11E1x include three independent oscillators: the system oscillator, the Internal RC oscillator (IRC), and the watchdog oscillator. Each oscillator can be used for more than one purpose as required in a particular application.

Following reset, the LPC11E1x operates from the internal RC oscillator until software switches to a different clock source. The IRC allows the system to operate without any external crystal and the bootloader code to operate at a known frequency.

See Figure 6 for an overview of the LPC11E1x clock generation.

#### 32-bit ARM Cortex-M0 microcontroller

#### 7.16.1.1 Internal RC oscillator

The IRC can be used as the clock source for the WDT, and/or as the clock that drives the system PLL and then the CPU. The nominal IRC frequency is 12 MHz.

Upon power-up, any chip reset, or wake-up from Deep power-down mode, the LPC11E1x use the IRC as the clock source. Software can later switch to one of the other available clock sources.

## 7.16.1.2 System oscillator

The system oscillator can be used as the clock source for the CPU, with or without using the PLL.

The system oscillator operates at frequencies of 1 MHz to 25 MHz. This frequency can be boosted to a higher frequency, up to the maximum CPU operating frequency, by the system PLL.

## 7.16.1.3 Watchdog oscillator

The watchdog oscillator can be used as a clock source that directly drives the CPU, the watchdog timer, or the CLKOUT pin. The watchdog oscillator nominal frequency is programmable between 7.8 kHz and 1.7 MHz. The frequency spread over processing and temperature is  $\pm 40$  % (see also Table 13).

Table 8. Power consumption for individual analog and digital blocks

| Peripheral                             | Typical supply current in mA |        | rrent in | Notes                                                                                                                                        |

|----------------------------------------|------------------------------|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

|                                        | n/a                          | 12 MHz | 48 MHz   |                                                                                                                                              |

| IRC                                    | 0.27                         | -      | -        | System oscillator running; PLL off; independent of main clock frequency.                                                                     |

| System oscillator at 12 MHz            | 0.22                         | -      | -        | IRC running; PLL off; independent of main clock frequency.                                                                                   |

| Watchdog<br>oscillator at<br>500 kHz/2 | 0.004                        | -      | -        | System oscillator running; PLL off; independent of main clock frequency.                                                                     |

| BOD                                    | 0.051                        | -      | -        | Independent of main clock frequency.                                                                                                         |

| Main PLL                               | -                            | 0.21   | -        | -                                                                                                                                            |

| ADC                                    | -                            | 0.08   | 0.29     | -                                                                                                                                            |

| CLKOUT                                 | -                            | 0.12   | 0.47     | Main clock divided by 4 in the CLKOUTDIV register.                                                                                           |

| CT16B0                                 | -                            | 0.02   | 0.06     | -                                                                                                                                            |

| CT16B1                                 | -                            | 0.02   | 0.06     | -                                                                                                                                            |

| CT32B0                                 | -                            | 0.02   | 0.07     | -                                                                                                                                            |

| CT32B1                                 | -                            | 0.02   | 0.06     | -                                                                                                                                            |

| GPIO                                   | -                            | 0.23   | 0.88     | GPIO pins configured as outputs and set to LOW. Direction and pin state are maintained if the GPIO is disabled in the SYSAHBCLKCFG register. |

| IOCONFIG                               | -                            | 0.03   | 0.10     | -                                                                                                                                            |

| I2C                                    | -                            | 0.04   | 0.13     | -                                                                                                                                            |

| ROM                                    | -                            | 0.04   | 0.15     | -                                                                                                                                            |

| SPI0                                   | -                            | 0.12   | 0.45     | -                                                                                                                                            |

| SPI1                                   | -                            | 0.12   | 0.45     | -                                                                                                                                            |

| UART                                   | -                            | 0.22   | 0.82     | -                                                                                                                                            |

| WWDT                                   | -                            | 0.02   | 0.06     | Main clock selected as clock source for the WDT.                                                                                             |

#### 32-bit ARM Cortex-M0 microcontroller

- [2] The typical frequency spread over processing and temperature ( $T_{amb}$  = -40 °C to +85 °C) is  $\pm$ 40 %.

- [3] See the LPC11Exx user manual.

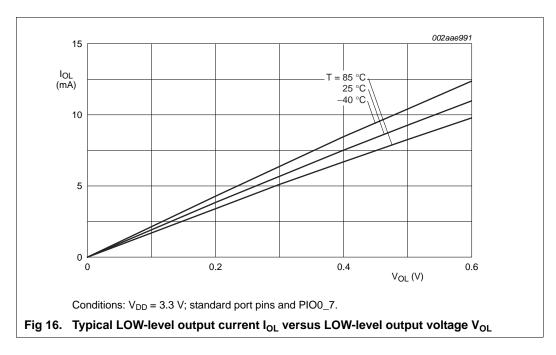

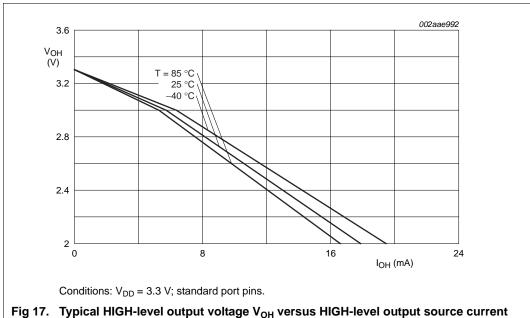

## 10.4 I/O pins

Table 14. Dynamic characteristics: I/O pins[1]

$T_{amb} = -40 \, ^{\circ}\text{C} \text{ to } +85 \, ^{\circ}\text{C}; 3.0 \, \text{V} \le \text{V}_{DD} \le 3.6 \, \text{V}.$

| Symbol         | Parameter | Conditions               | Min | Тур | Max | Unit |

|----------------|-----------|--------------------------|-----|-----|-----|------|

| t <sub>r</sub> | rise time | pin configured as output | 3.0 | -   | 5.0 | ns   |

| t <sub>f</sub> | fall time | pin configured as output | 2.5 | -   | 5.0 | ns   |

<sup>[1]</sup> Applies to standard port pins and  $\overline{RESET}$  pin.

## 10.5 I2C-bus

Table 15. Dynamic characteristic: I<sup>2</sup>C-bus pins[1]

$T_{amb} = -40 \, ^{\circ}\text{C to } +85 \, ^{\circ}\text{C.}_{\underline{[2]}}$

| Symbol              | Parameter          |                      | Conditions                  | Min                   | Max | Unit |

|---------------------|--------------------|----------------------|-----------------------------|-----------------------|-----|------|

| OOL                 | SCL clock          |                      | Standard-mode               | 0                     | 100 | kHz  |

|                     | frequency          |                      | Fast-mode                   | 0                     | 400 | kHz  |

|                     |                    |                      | Fast-mode Plus              | 0                     | 1   | MHz  |

| t <sub>f</sub>      | fall time          | [4][5][6][7]         | of both SDA and SCL signals | -                     | 300 | ns   |

|                     |                    |                      | Standard-mode               |                       |     |      |

|                     |                    |                      | Fast-mode                   | $20 + 0.1 \times C_b$ | 300 | ns   |

|                     |                    |                      | Fast-mode Plus              | -                     | 120 | ns   |

|                     | LOW period of the  |                      | Standard-mode               | 4.7                   | -   | μS   |

|                     | SCL clock          |                      | Fast-mode                   | 1.3                   | -   | μS   |

|                     |                    |                      | Fast-mode Plus              | 0.5                   | -   | μS   |

|                     | HIGH period of the |                      | Standard-mode               | 4.0                   | -   | μS   |

|                     | SCL clock          |                      | Fast-mode                   | 0.6                   | -   | μS   |

|                     |                    |                      | Fast-mode Plus              | 0.26                  | -   | μS   |

| t <sub>HD;DAT</sub> | data hold time     | ime <u>[3][4][8]</u> | Standard-mode               | 0                     | -   | μS   |

|                     |                    |                      | Fast-mode                   | 0                     | -   | μS   |

|                     |                    |                      | Fast-mode Plus              | 0                     | -   | μS   |

| t <sub>SU;DAT</sub> | data set-up time   | <u>[9][10]</u>       | Standard-mode               | 250                   | -   | ns   |

|                     |                    |                      | Fast-mode                   | 100                   | -   | ns   |

|                     |                    |                      | Fast-mode Plus              | 50                    | -   | ns   |

<sup>[1]</sup> See the I<sup>2</sup>C-bus specification *UM10204* for details.

LPC11E1X

<sup>[2]</sup> Parameters are valid over operating temperature range unless otherwise specified.

<sup>[3]</sup> tHD;DAT is the data hold time that is measured from the falling edge of SCL; applies to data in transmission and the acknowledge.

<sup>[4]</sup> A device must internally provide a hold time of at least 300 ns for the SDA signal (with respect to the V<sub>IH</sub>(min) of the SCL signal) to bridge the undefined region of the falling edge of SCL.

<sup>[5]</sup>  $C_b = \text{total capacitance of one bus line in pF.}$

<sup>[6]</sup> The maximum t<sub>f</sub> for the SDA and SCL bus lines is specified at 300 ns. The maximum fall time for the SDA output stage t<sub>f</sub> is specified at 250 ns. This allows series protection resistors to be connected in between the SDA and the SCL pins and the SDA/SCL bus lines without exceeding the maximum specified t<sub>f</sub>.

- [7] In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used, designers should allow for this when considering bus timing.

- [8] The maximum t<sub>HD;DAT</sub> could be 3.45 μs and 0.9 μs for Standard-mode and Fast-mode but must be less than the maximum of t<sub>VD;DAT</sub> or t<sub>VD;ACK</sub> by a transition time (see *UM10204*). This maximum must only be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the SCL signal. If the clock stretches the SCL, the data must be valid by the set-up time before it releases the clock.

- [9] tSU;DAT is the data set-up time that is measured with respect to the rising edge of SCL; applies to data in transmission and the acknowledge.

- [10] A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system but the requirement t<sub>SU;DAT</sub> = 250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line t<sub>r(max)</sub> + t<sub>SU;DAT</sub> = 1000 + 250 = 1250 ns (according to the Standard-mode I<sup>2</sup>C-bus specification) before the SCL line is released. Also the acknowledge timing must meet this set-up time.

## 32-bit ARM Cortex-M0 microcontroller

## 11. Application information

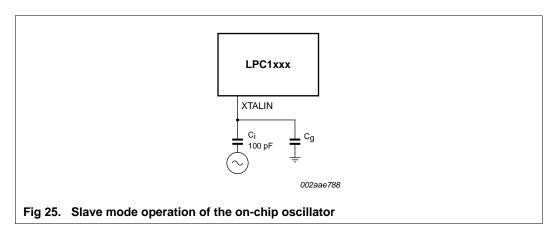

## 11.1 XTAL input

The input voltage to the on-chip oscillators is limited to 1.8 V. If the oscillator is driven by a clock in slave mode, it is recommended that the input be coupled through a capacitor with  $C_i = 100$  pF. To limit the input voltage to the specified range, choose an additional capacitor to ground  $C_g$  which attenuates the input voltage by a factor  $C_i/(C_i + C_g)$ . In slave mode, a minimum of 200 mV(RMS) is needed.

In slave mode, couple the input clock signal with a capacitor of 100 pF (<u>Figure 25</u>), with an amplitude between 200 mV(RMS) and 1000 mV(RMS). This signal corresponds to a square wave signal with a signal swing of between 280 mV and 1.4 V. The XTALOUT pin in this configuration can be left unconnected.

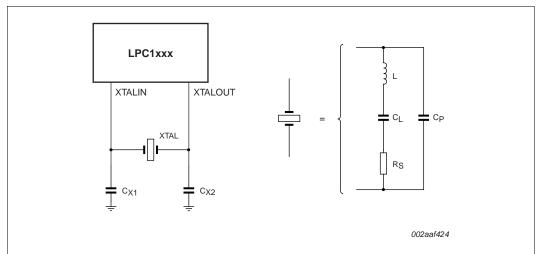

External components and models used in oscillation mode are shown in <u>Figure 26</u> and in <u>Table 17</u> and <u>Table 18</u>. Since the feedback resistance is integrated on chip, only a crystal and the capacitances  $C_{X1}$  and  $C_{X2}$  need to be connected externally in case of fundamental mode oscillation (L,  $C_L$  and  $R_S$  represent the fundamental frequency). Capacitance  $C_P$  in <u>Figure 26</u> represents the parallel package capacitance and must not be larger than 7 pF. Parameters  $F_{OSC}$ ,  $C_L$ ,  $R_S$  and  $C_P$  are supplied by the crystal manufacturer.

#### 32-bit ARM Cortex-M0 microcontroller

Fig 26. Oscillator modes and models: oscillation mode of operation and external crystal model used for  $C_{X1}/C_{X2}$  evaluation

Table 17. Recommended values for C<sub>X1</sub>/C<sub>X2</sub> in oscillation mode (crystal and external components parameters) low frequency mode

| Fundamental oscillation frequency F <sub>OSC</sub> | Crystal load capacitance C <sub>L</sub> | Maximum crystal series resistance R <sub>S</sub> | External load capacitors C <sub>X1</sub> , C <sub>X2</sub> |

|----------------------------------------------------|-----------------------------------------|--------------------------------------------------|------------------------------------------------------------|

| 1 MHz to 5 MHz                                     | 10 pF                                   | < 300 Ω                                          | 18 pF, 18 pF                                               |

|                                                    | 20 pF                                   | < 300 Ω                                          | 39 pF, 39 pF                                               |

|                                                    | 30 pF                                   | < 300 Ω                                          | 57 pF, 57 pF                                               |

| 5 MHz to 10 MHz                                    | 10 pF                                   | < 300 Ω                                          | 18 pF, 18 pF                                               |

|                                                    | 20 pF                                   | < 200 Ω                                          | 39 pF, 39 pF                                               |

|                                                    | 30 pF                                   | < 100 Ω                                          | 57 pF, 57 pF                                               |

| 10 MHz to 15 MHz                                   | 10 pF                                   | < 160 Ω                                          | 18 pF, 18 pF                                               |

|                                                    | 20 pF                                   | < 60 Ω                                           | 39 pF, 39 pF                                               |

| 15 MHz to 20 MHz                                   | 10 pF                                   | < 80 Ω                                           | 18 pF, 18 pF                                               |

Table 18. Recommended values for C<sub>X1</sub>/C<sub>X2</sub> in oscillation mode (crystal and external components parameters) high frequency mode

| Fundamental oscillation frequency F <sub>OSC</sub> | Crystal load capacitance C <sub>L</sub> | Maximum crystal series resistance R <sub>S</sub> | External load capacitors C <sub>X1</sub> , C <sub>X2</sub> |

|----------------------------------------------------|-----------------------------------------|--------------------------------------------------|------------------------------------------------------------|

| 15 MHz to 20 MHz                                   | 10 pF                                   | < 180 Ω                                          | 18 pF, 18 pF                                               |

|                                                    | 20 pF                                   | < 100 Ω                                          | 39 pF, 39 pF                                               |

| 20 MHz to 25 MHz                                   | 10 pF                                   | < 160 Ω                                          | 18 pF, 18 pF                                               |

|                                                    | 20 pF                                   | < 80 Ω                                           | 39 pF, 39 pF                                               |

## 11.2 XTAL Printed-Circuit Board (PCB) layout guidelines

Follow these guidelines for PCB layout:

- Connect the crystal on the PCB as close as possible to the oscillator input and output pins of the chip.

- Take care that the load capacitors  $C_{x1}$ ,  $C_{x2}$ , and  $C_{x3}$  in case of third overtone crystal use have a common ground plane.

LPC11E1X

## 32-bit ARM Cortex-M0 microcontroller

## 12. Package outline

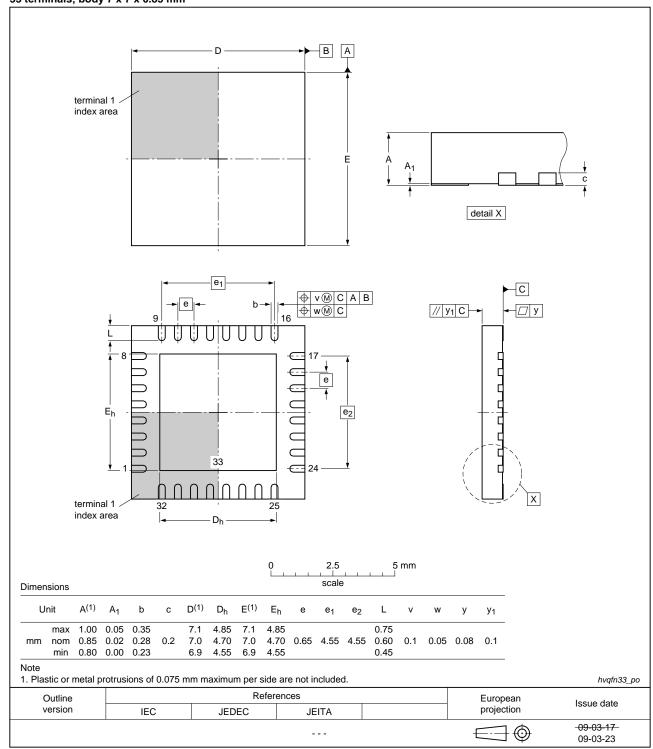

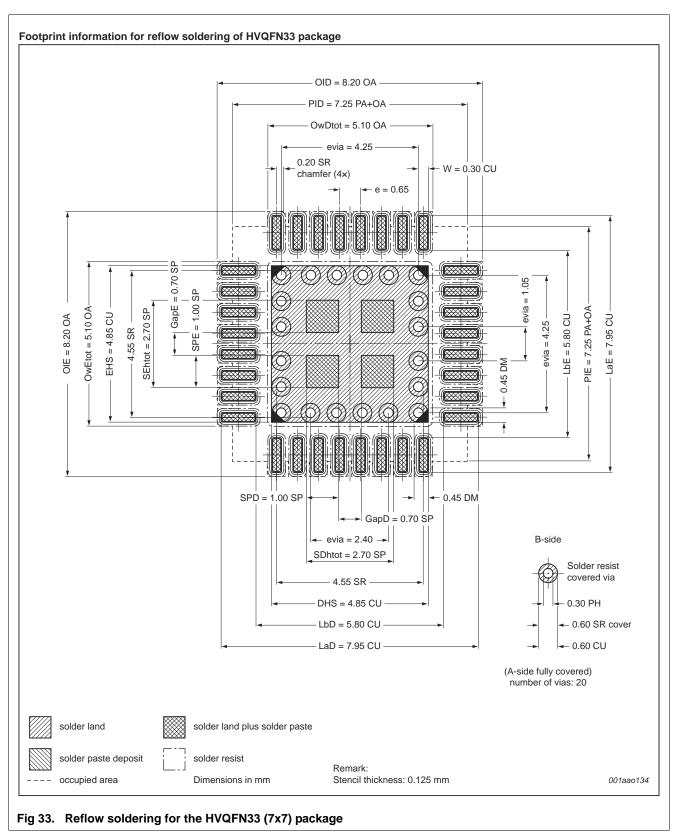

HVQFN33: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body 7 x 7 x 0.85 mm

Fig 30. Package outline HVQFN33 (7 x 7 x 0.85 mm)

## 32-bit ARM Cortex-M0 microcontroller

## 13. Soldering

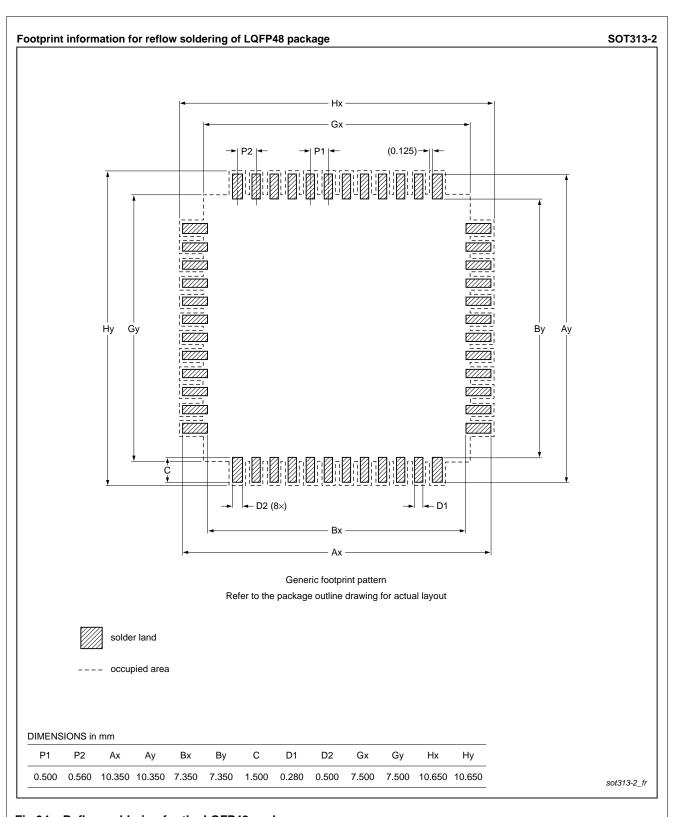

Fig 34. Reflow soldering for the LQFP48 package

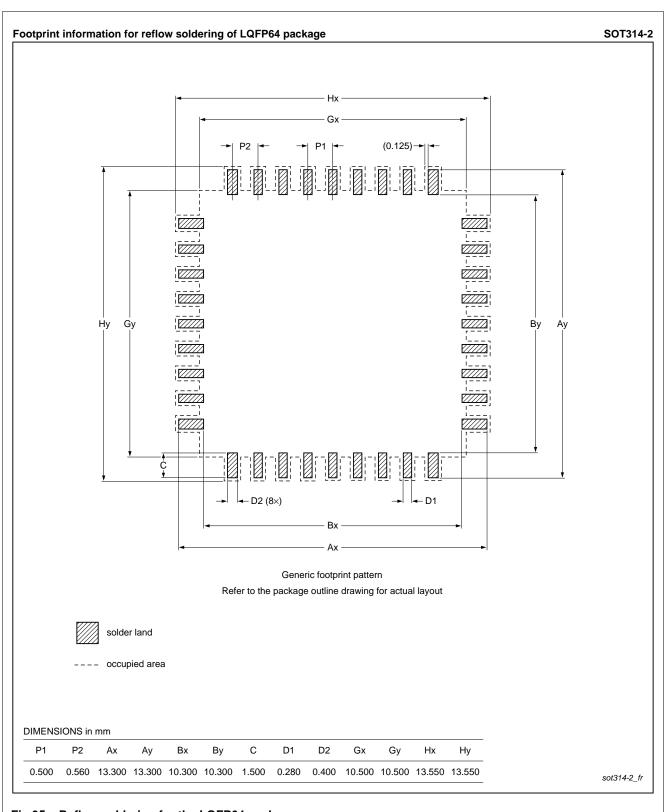

Fig 35. Reflow soldering for the LQFP64 package

## 32-bit ARM Cortex-M0 microcontroller

# 15. Revision history

## Table 20. Revision history

| Document ID                                                                                                                                                         | Release date                                                                                                                                                                                                                            | Data sheet status                                                                             | Change notice             | Supersedes   |  |  |  |                                                                                            |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------|--------------|--|--|--|--------------------------------------------------------------------------------------------|--|

| LPC11E1X v.1.1                                                                                                                                                      | 20130924                                                                                                                                                                                                                                | Product data sheet                                                                            | -                         | LPC11E1X v.1 |  |  |  |                                                                                            |  |

| Modifications:                                                                                                                                                      | <ul> <li>Parameters t</li> </ul>                                                                                                                                                                                                        | <ul> <li>Parameters t<sub>er</sub> and f<sub>clk</sub> removed in <u>Table 10</u>.</li> </ul> |                           |              |  |  |  |                                                                                            |  |

|                                                                                                                                                                     | • Table 3: Add                                                                                                                                                                                                                          | ed "5 V tolerant pad" to $\overline{RESE}$                                                    | _<br>Γ/PIO0_0 table note. |              |  |  |  |                                                                                            |  |

|                                                                                                                                                                     | • <u>Table 7</u> : Removed BOD interrupt level 0.                                                                                                                                                                                       |                                                                                               |                           |              |  |  |  |                                                                                            |  |

| <ul> <li>Added <u>Section 11.5 "ADC effective input impedance"</u>.</li> <li>Programmable glitch filter is enabled by default. See <u>Section 7.7.1</u>.</li> </ul> |                                                                                                                                                                                                                                         |                                                                                               |                           |              |  |  |  |                                                                                            |  |

|                                                                                                                                                                     |                                                                                                                                                                                                                                         |                                                                                               |                           |              |  |  |  | <ul> <li><u>Table 5</u> "Static characteristics" added Pin capacitance section.</li> </ul> |  |

|                                                                                                                                                                     | • Table 4 "Limiting values":                                                                                                                                                                                                            |                                                                                               |                           |              |  |  |  |                                                                                            |  |

|                                                                                                                                                                     | <ul> <li>Updated V<sub>DD</sub> min and max.</li> </ul>                                                                                                                                                                                 |                                                                                               |                           |              |  |  |  |                                                                                            |  |

|                                                                                                                                                                     | <ul> <li>Updated V<sub>I</sub> conditions.</li> </ul>                                                                                                                                                                                   |                                                                                               |                           |              |  |  |  |                                                                                            |  |

|                                                                                                                                                                     | <ul> <li><u>Table 10 "EEPROM characteristics"</u>: Changed the t<sub>prog</sub> from 1.1 ms to 2.9 ms; the<br/>EEPROM IAP always does an erase and program, thus the total program time is t<sub>er</sub> + t<sub>prog</sub></li> </ul> |                                                                                               |                           |              |  |  |  |                                                                                            |  |

| LPC11E1X v.1                                                                                                                                                        | 20120220                                                                                                                                                                                                                                | Product data sheet                                                                            | -                         | -            |  |  |  |                                                                                            |  |